(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для вычисления корней | 1990 |

|

SU1751777A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1980 |

|

SU940167A1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| Устройство для вычисления значений степенного ряда | 1985 |

|

SU1277100A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1388853A1 |

| Устройство для вычисления полиномов | 1985 |

|

SU1277098A1 |

| Устройство для вычисления координат | 1978 |

|

SU752350A1 |

Изобретение относится к вычислительной технике и предназначено для решения уравнений, заданных в виде степенного ряда п-го порядка при изменении свободного члена. Цель изобретения - расширение функциональных возможностей за счет отсле швания действительного значения корня поли- . нома при изменении свободного члена. Поставленная цель достигается тем, что в устройс тво для решения уравнений дополнительно введены сумматор 7 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, соединенные таким образом, что позволяют обеспечить сходимость вычислительного процесса в соответствии с методом . Ньютона решения нелинейных уравнений. 4 ил. 1 табл.

4ib

Од

iNd

ел

Изобретение относится к вычислительной технике, в частности к уст ройстваы Rstfi обработки данных, и мо™ фет быть, использовано в разлкчньпс информационно-измерительных и упраз- Л1яющих системах, в системах моделиро- $ания с аппаратурной реализацией функций, в устройствах дискретной обработки сигналов, везде, тде необко- fltHMo вычислять значение корня уравне- по заданно14у начальному прибли - ению.

Целью изобретения является растя- ение функциональны; : возможностей за чет отслеживания действительного зна корня полинома при изменении вободного члена. I На фиг, 1 представлена функцконш;: ijtaH схема устройства для решения ураз 1 ений| на фиг. 2 - функциональная схе .ka первого арифметического блокаj на фиг. 3 - функциональная схема второго Арифметического блока; на -фиг. 4 - йункциональная скема третьего арифме- .тического блока при вычислении корня цз алгебраического уравнения третьего .

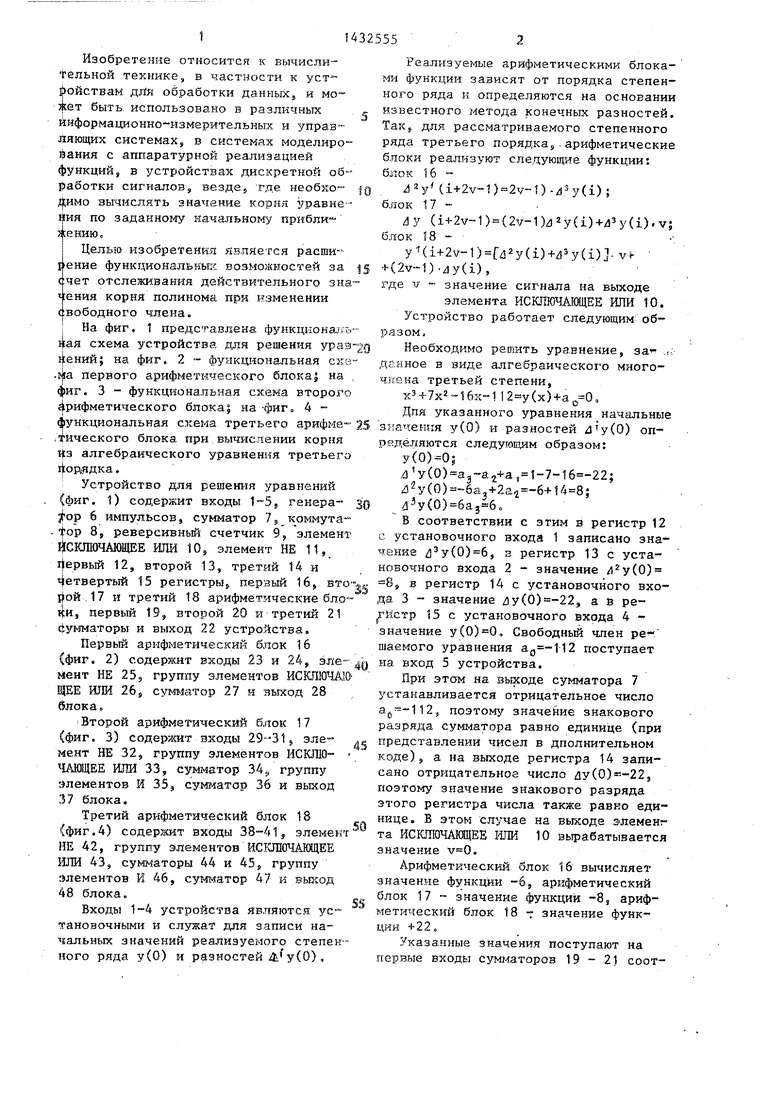

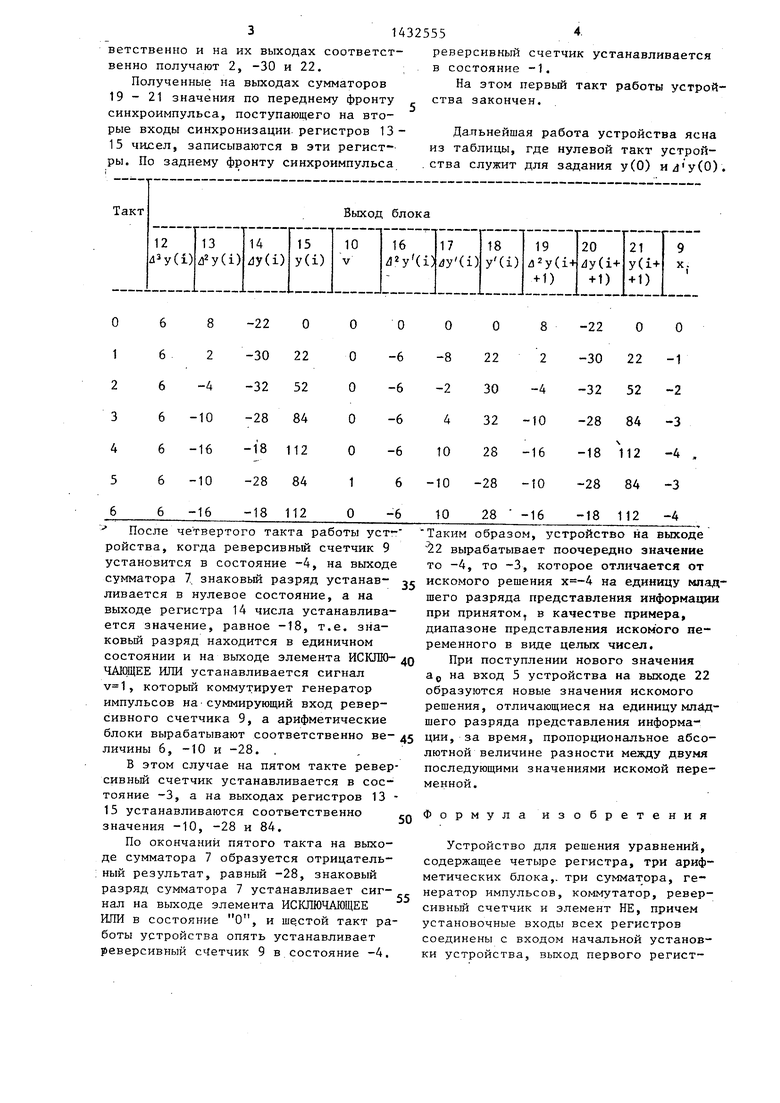

Устройство для решения уравнений (фиг. 1) содержит входы 1-5, ганера- jj-op 6 импульсов, сумматор 75 коммута-- .fop 8, реверсивньй счетчик 9, элемент 1 СКЛЮЧАНЩЕЕ ИЛИ 10 элемент НЕ 11, 1|ервый 12, второй 13, третий 14 и г|етверть Й 15 регистры первый 16, вто рой, 17 и третий 18 арифметические бло «и, первый 19, второй 20 и третий 21 сумматоры и выход 22 устройства. Первый арифметический блок 16 (фиг. 2) содержит входы 23 и 24, элемент НЕ 25, группу элементов ИСКЛЮ -Ш.{ Б1ЕЕ ШШ 26, сумматор 27 и выход 28 блока.

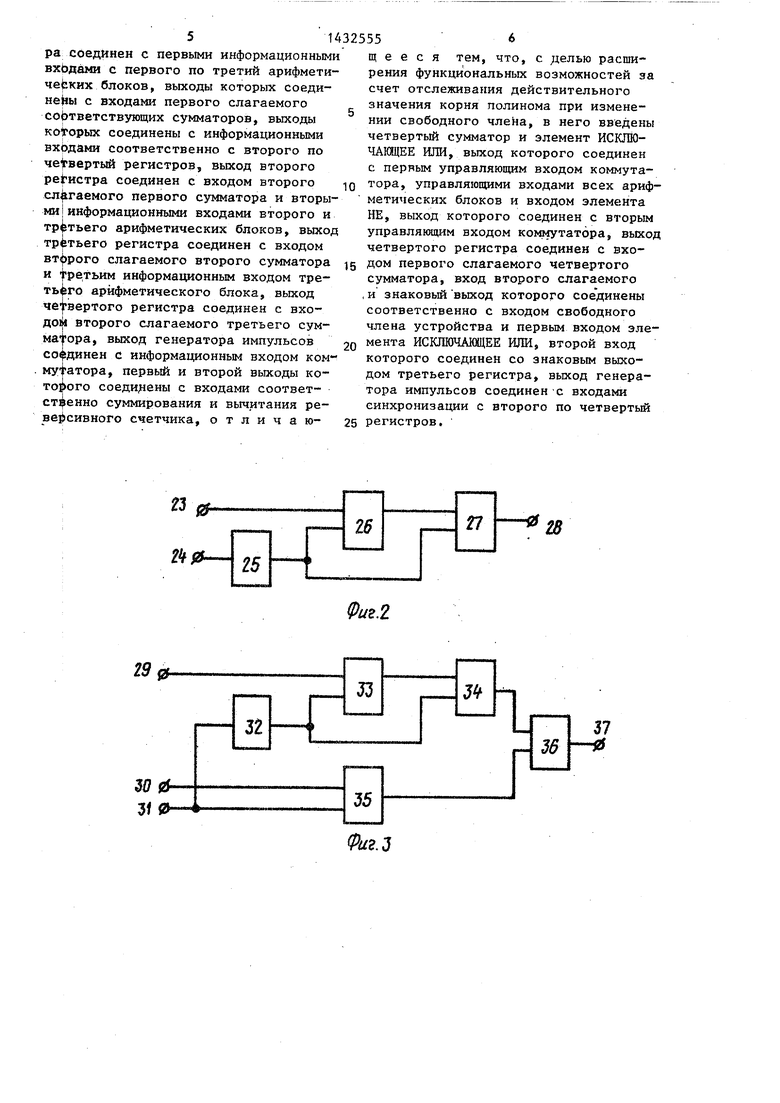

Второй арифметический блок 17 (фиг. 3) содержит входы элемент НЕ 32, группу элементов ИСКШО- ЧАМЦЕЕ ИЛИ 33, сумматор 34 группу элементов И 35, сумматор 36 и выход 37 блока.

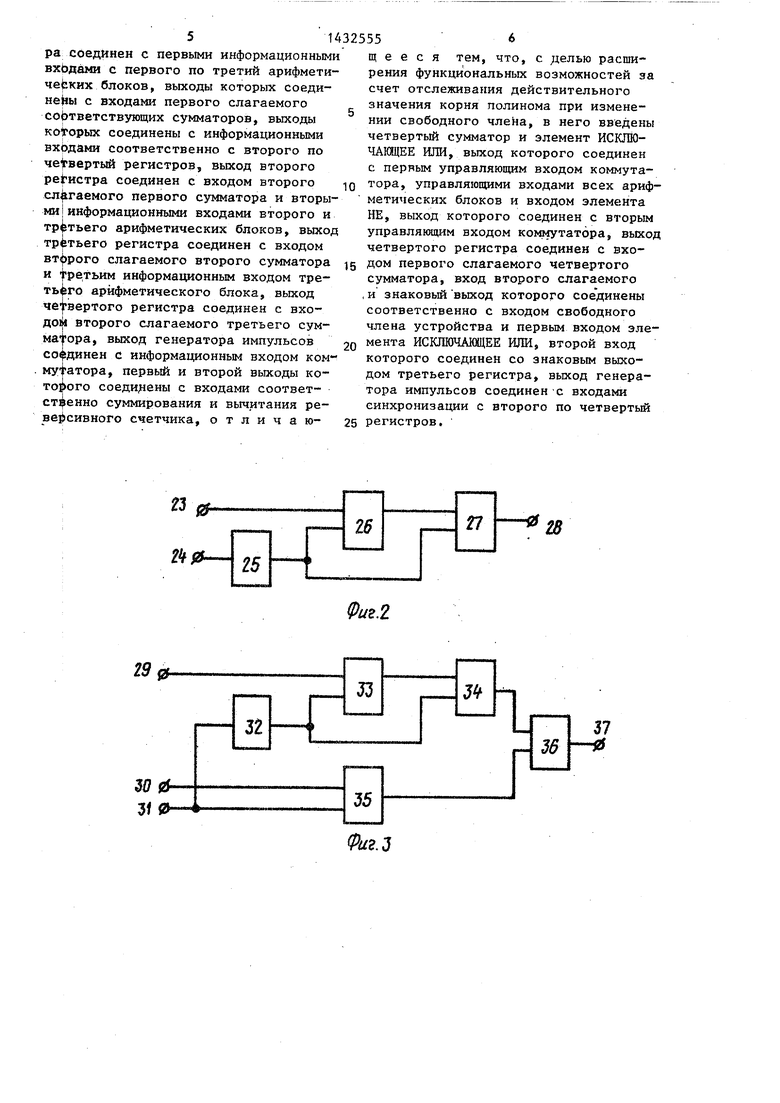

Третий арифметический блок 18 (фиг.4) содержит входы 38-41, элемент НЕ 42, группу элементов ИС1СЛЮЧАЮЩЕЕ ИЛИ 43, сумматоры 44 и 45 группу : лементов К 46, сумматор 47 и вькод 48 блока.

Входы 1-4 устройства являются установочными и служат для записи начальных значений реализуемого степен- ного ряда у(0) и разностей (0) ,

о 5

О

S

Q

0

S

Реализуемые арифметическими блоками функции зависят от порядка степенного ряда и определяются на основании известного метода конечных разностей. Так, для рассматриваемого степенного ряда третьего порядка,.арифметические блоки реализуют следующие функции:

бЛО 16

А -у ti+2v-1))(i); блок 17jy (i+2v-1) (2v-1)4Zy(i)+43y(i).v| блок 18 y- (i+2v-1)fd2y(i)(i)J- v+ ).4y(i), где V - значение сигнала на выходе

ИСКШИАЩЕЕ ИЛИ 10.

Устройство работа ет следующим образом.

Необходимо решить уравнение, за - ., данное в виде алгебраического много- Ч5гека третьей степени,

W

Дпя указанного уравнения начальные значения у(0) и разностей J y(0) определяются следующим образом:

У(0)-0;

/з у(0),1-7-16 -22;

у(0)-6аз+2а4 -6+14 8;

(0).

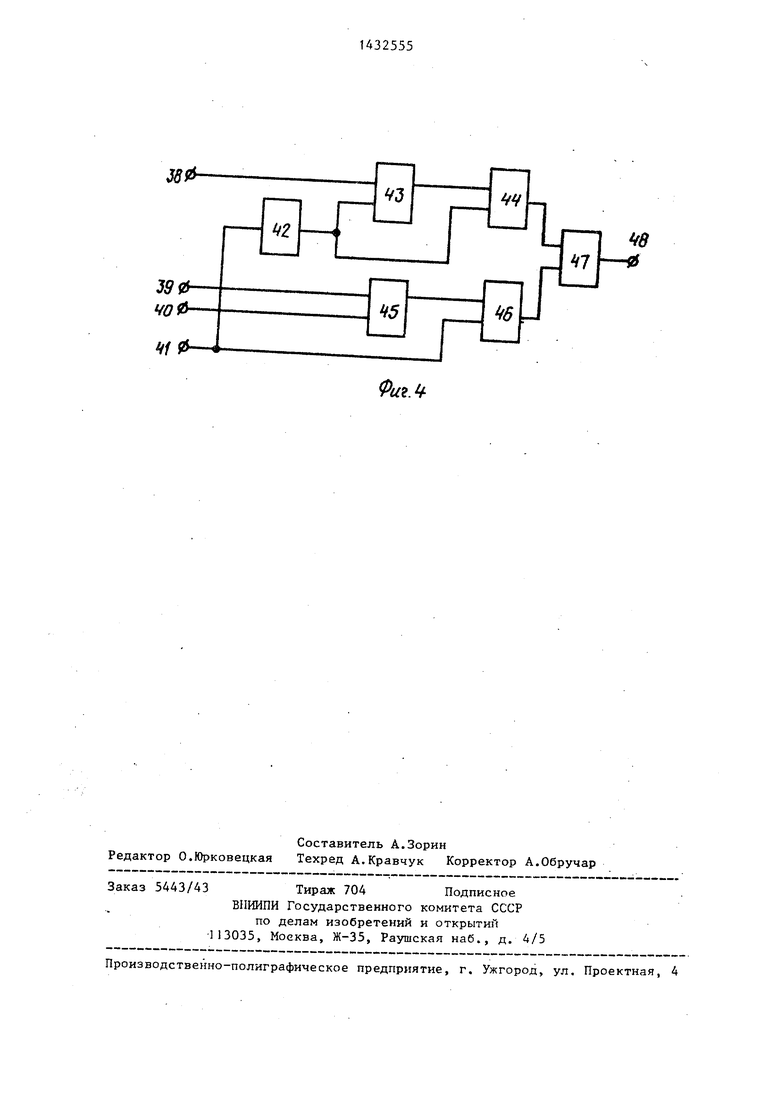

В соответствии с этим в регистр 12 с установочного входа 1 записано значение (0)6, 3 регистр 13 с установочного входа 2 - значение у(0) 8, в регистр 14 с установочного входа 3 - значение ЛУ(0)-22, а в ре- Истр 15 с установочного входа 4 - значение у(0)0„ Свободный член per шаемого уравнения поступает на вход 5 устройства.

При этом на сумматора 7 устанавливается отрицательное число ,, поэтому значение знакового разряда сумматора равно единице (при представлении чисел в дполнительном коде)5 а на выходе регистра 14 записано отрицательное число ЛУ(0)-22, поэтому значение знакового разряда этого регистра числа также равно единице. В этом случае на выходе элеменг та ИСКгаОЧАКЩЕЕ ИЛИ 10 вырабатывается значение .

Арифметический блок 16 вычисляет значение функции -6, арифметический блок 17 - значение функций -8, арифметический блок 18 - значение функции

Указанные значения поступают на первые входы сумматоров 19-21 соответственно и на их выходах соответственно получают 2, -30 и 22. ;

Полученные на выходах сумматоров 19 - 21 значения по переднему фронту синхроимпульса, поступающего на вторые входы синхронизации регистров ISIS чисел, записываются в эти регистры. По заднему фронту синхроимпульса

- После четвертого такта работы уст ройства, когда реверсивный счетчик 9 установится в состояние -4, на выходе сумматора 7 знаковый разряд устанав- ливается в нулевое состояние, а на выходе регистра 14 числа устанавливается значение, равное -18, т.е. знаковый разряд находится в единичном состоянии и на выходе элемента ИСКПЮЧА10ЩЕЕ ИЛИ устанавливается сигнал , который коммутирует генератор импульсов насуммирующий вход реверсивного счетчика 9, а арифметические блоки вырабатывают соответственно ве- личины 6, -10 и -28. ,

В этом случае на пятом такте ревер сивньш счетчик устанавливается в состояние -3, а на выходах регистров 13 15 устанавливаются соответственно значения -10, -28 и 84.

По окончаний пятого такта на выходе сумматора 7 образуется отрицательный результат, равный -28, знаковый разряд сумматора 7 устанавливает сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в состояние О, и шестой такт работы устройства опять устанавливает реверсивный сЧетчик 9 в состояние -4.

;

1432555-

реверсивный счетчик устанавливается в состояние -1.

На этом первый такт работы устройства закончен.

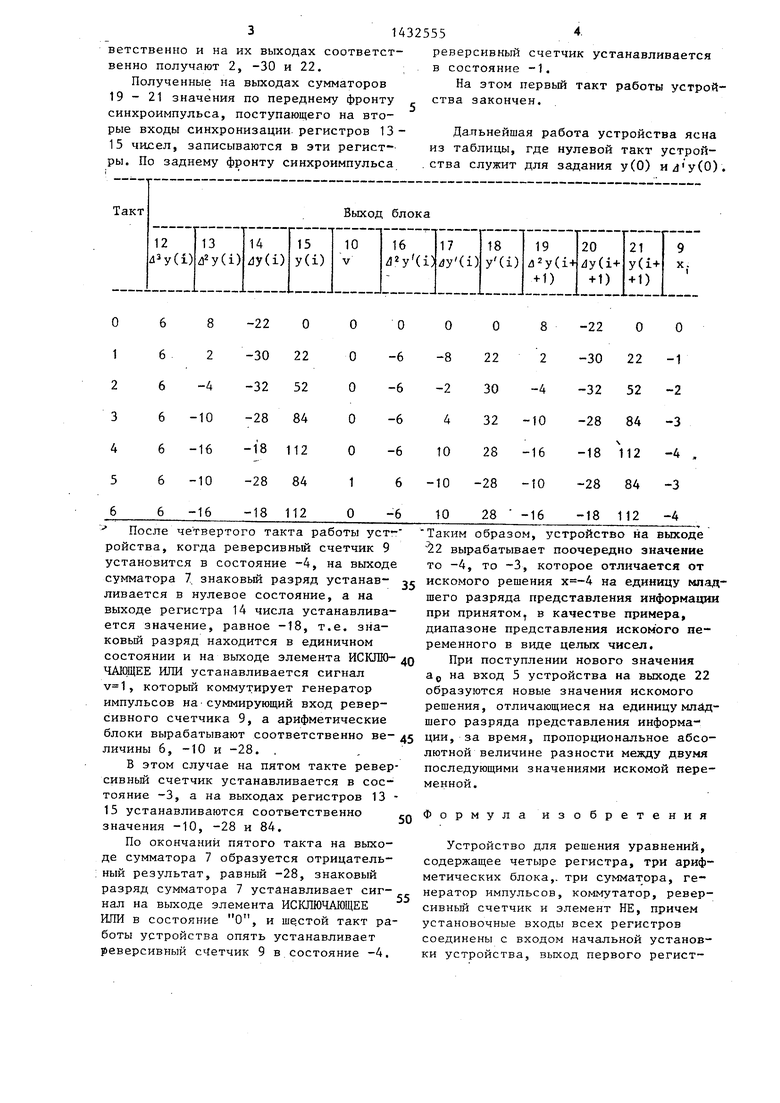

Дальнейшая работа устройства ясна из таблицы, где нулевой такт устройства служит для задания у(0) и/} у(0).

5 Q 45

0

5

Таким образом, устройство на выходе 2 вырабатывает поочередно значение то -4, то -3, которое отличается от искомого решения на единицу младшего разряда представления информации при принятом, в качестве примера, диапазоне представления искомого переменного в виде целых чисел.

При поступлении нового значения ар на вход 5 устройства на выходе 22 образуются новые значения искомого решения, отличающиеся на единицу млйд- шего разряда представления информации, за время, пропорциональное абсолютной величине разности между двумя последующими значениями искомой переменной.

Формула изобретения

Устройство для решения уравнений, содержащее четыре регистра, три арифметических блока,, три сумматора, генератор импульсов, коммутатор, реверсивный счетчик и элемент НЕ, причем установочные входы всех регистров соединены с входом начальной установки устройства, выход первого регист

pa соединен с первыми информационными вхЬдами с первого по третий арифмети- черких блоков, выходы которых соединены с входами первого слагаемого соЬтветствующих сумматоров, выходы которых соединены с информационными входами соответственно с второго по четвертый регистров, выход второго реЫстра соединен с входом второго слагаемого первого сумматора и вторыми 1 информационными входами второго и третьего арифметических блоков, выход третьего регистра соединен с входом второго слагаемого второго сумматора и третьим информационным входом тре- арифметического блока, выход четвертого регистра соединен с вхо- ДО1«1 второго слагаемого третьего сум- Mafopa, выход генератора импульсов софдинен с информационным входом коммутатора, первый и второй выходы ко соеди нены с входами соответ- суммирования и вычитания ре- ве1 сивного счетчика, отличаю-

Wf 3f 0-.

щ е е с я тем, что, с далью расширения функциональных возможностей за счет отслеживания действительного значения корня полинома при изменении свободного члейа, в него введены четвертый сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с перяым управляющим входом коммутатора, управляющими входами всех арифметических блоков и входом элемента НЕ, выход которого соединен с вторым управляющим входом ко№1утат6ра, выход четвертого регистра соединен с входом первого слагаемого четвертого сумматора, вход второго слагаемого ,и знаковый выход которого соединены соответственно с входом свободного члена устройства и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со знаковым выходом третьего регистра, выход генератора импульсов соединен с входами синхронизации с второго по четвертый регистров.

Фи.г

г г

36

37 Н-0

to.J

jy

39

Т

7

в

h-0

Фиг.1+

| Устройство для решения уравнений вида | 1978 |

|

SU792262A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления значений степенного ряда | 1985 |

|

SU1277100A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-05-22—Подача