Изобретение относится к вычислительной технике и может быть использовано при создании маломощных оперативных запоминающих устройств, в частности вентильных запоминающих устройств, время выборки и потребляемая мощность которых может варьироваться в широких пределах за счет изменения напряжения низковольтного источника питания.

Целью изобретения является упрощение запоминающего элемента и уменьшение потребляемой мощности.

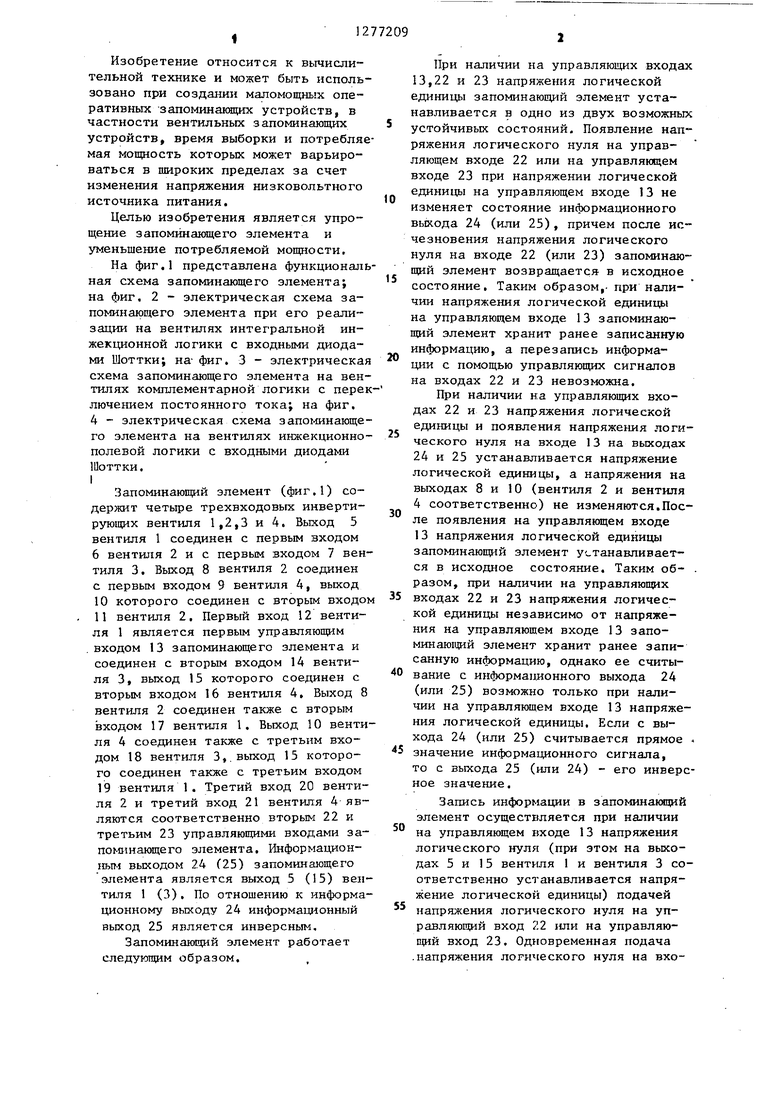

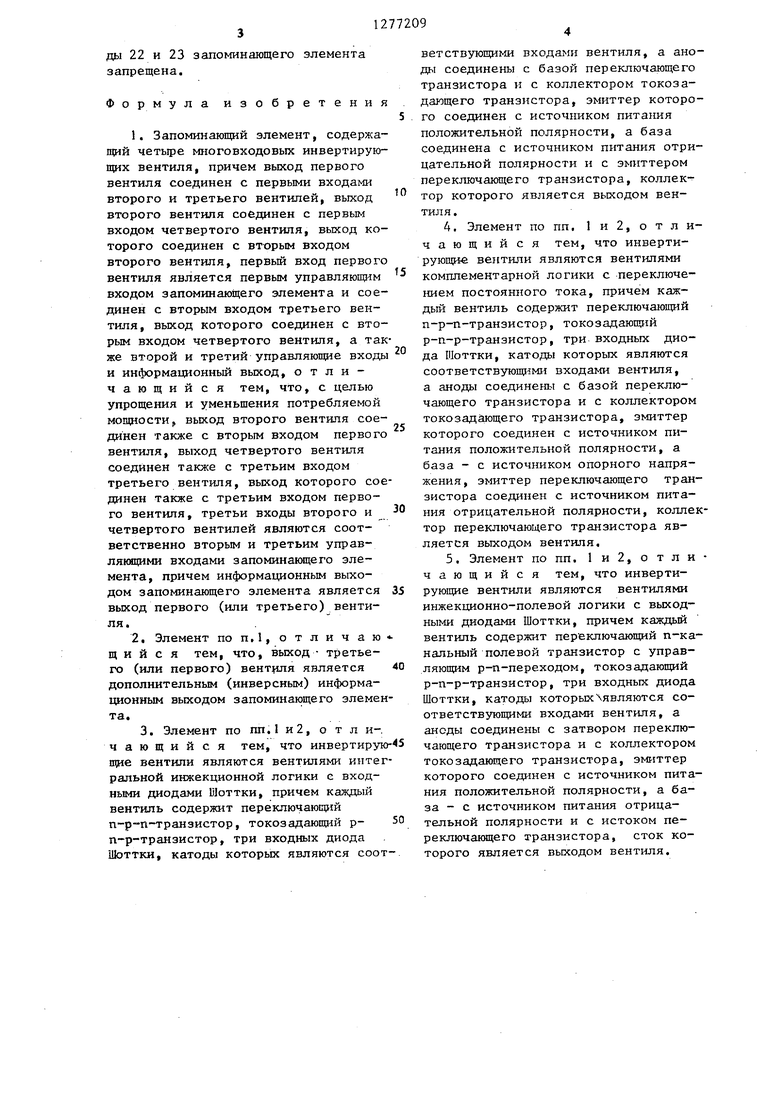

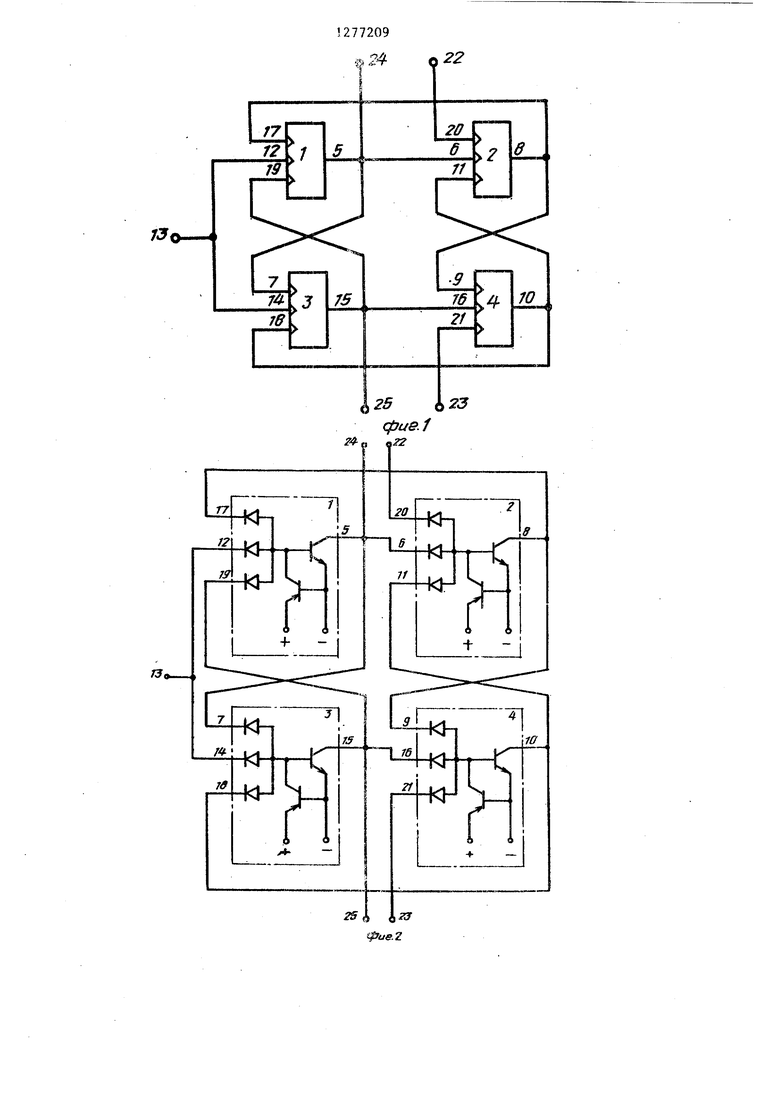

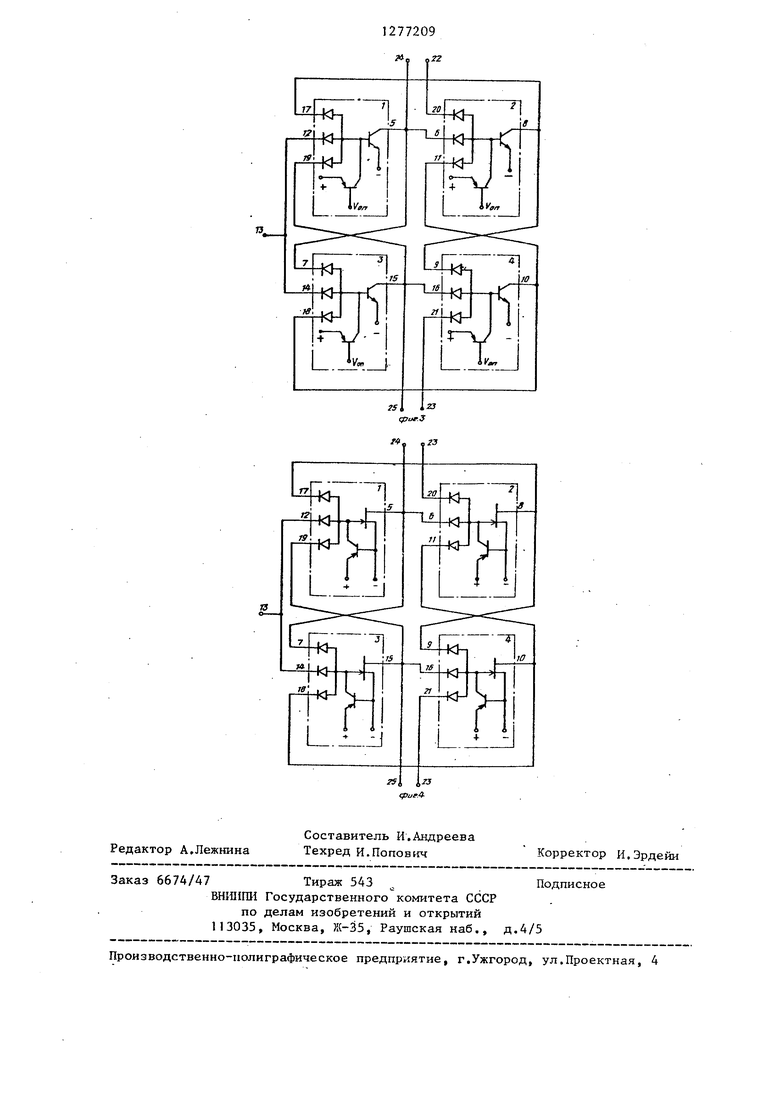

На фиг.1 представлена функциональная схема запоминающего элемента; на фиг. 2 - электрическая схема запоминающего элемента при его реализации на вентилях интегральной ин- жекционной логики с входными диодами Шоттки; на- фиг. 3 - электрическая схема запоминающего элемента на вентилях комплементарной логики с перек лючением постоянного тока; на фиг. 4 - электрическая схема запо1-шнающе- го элемента на вентилях инжекционно- полевой логики с входными диодами Шоттки. I

Запоминающий элемент (фиг.1) содержит четыре трехвходовых инвертирующих вентиля 1,2,3 и 4. Выход 5 вентиля 1 соединен с первым входом 6 вентиля 2 и с первым входом 7 вентиля 3. Выход 8 вентиля 2 соединен с первым входом 9 вентиля 4, выход

10которого соединен с вторым входо

11вентиля 2. Первый вход 12 вентиля 1 яш:яется первым управляющим входом 13 запоминающего элемента и соединен с вторым входом 14 вентиля 3, выход 15 которого соединен с вторым входом 16 вентиля 4, Выход 8 вентиля 2 соединен также с вторым входом 17 вентиля 1. Выход 10 вентиля 4 соединен также с третьим входом 18 вентиля 3,. выход 15 которого соединен также с третьим входом 19 вентиля 1. Третий вход 20 вентиля 2 и третий вход 21 вентил:я 4 являются соответственно вторьм 22 и третьим 23 управляющими входами за- пo Dшaющeгo элемента. Информационным выходом 24 (25) запоминающего

элемента является выход 5 (15) вентиля 1 (3). По отношению к информационному выходу 24 информационный выход 25 является инверсным,

Запоминакяций элемент работает следующим образом.

5

0

При наличии на управляющих входах 13,22 и 23 напряжения логической единицы запоминающий элемент устанавливается в одно из двух возможньк устойчивых состояний. Появление напряжения логического нуля на управляющем входе 22 или на управляющем входе 23 при напряжении логической единицы на управляющем входе 13 не изменяет состояние информационного выхода 24 (или 25), причем после исчезновения напряжения логического нуля на входе 22 (или 23) запоминающий элемент возвращаете в исходное состояние. Таким образом,- при наличии напряжения логической единищз на управляющем входе 13 запоминающий элемент хранит ранее записанную информацию, а перезапись информа5

30

ции с помощью управляющих сигналов на входах 22 и 23 невозможна.

При наличии на управляющих входах 22 и 23 напряжения логической единицы и появления напряжения логического нуля на входе 13 на выходах 24 и 25 устанавливается напряжение логической единицы, а напряжения на выходах 8 и 10 (вентиля 2 и вентиля 4 соответственно) не изменяются.После появления на управляющем входе 13 напряжения логической единицы запоминающий элемент у танавливает- ся в исходное состояние. Таким об- . разом, при наличии на управляющих 35 входах 22 и 23 напряжения логической единицы независимо от напряжения на управляющем входе 13 запо- минаю1ций элемент хранит ранее записанную информацию, однако ее считы- вание с информационного выхода 24 (или 25) возможно только при нгши- чии на управляющем входе 13 напряжения логической единицы. Если с выхода 24 (или 25) считывается прямое . 5 значение информационного сигнала, то с выхода 25 (или 24) - его инверсное значение.

Запись информации в запоминакяций элемент осуществляется при наличии на управляющем входе 13 напряжения логического нуля (при этом на выходах 5 и 15 вентиля 1 и вентиля 3 соответственно устанавливается напряжение логической единицы) подачей

55

напряжения логического нуля на управляющий вход 22 или на управляющий вход 23. Одновременная подача .напряжения логического нуля на вхо

ды 22 и 23 запоминающего элемента запрещена.

Формула изобретения

1. Запоминающий элемент, содержа- П1ий четыре многовходовых инвертирующих вентиля, причем выход первого вентиля соединен с первыми входами второго и третьего вентилей, выход второго вентиля соединен с первым входом четвертого вентиля, выход которого соединен с вторым входом второго вентиля, первый вход первого вентиля является первым управляющим входом запоминающего элемента и соединен с вторым входом третьего вентиля, выход которого соединен с вторым входом четвертого вентиля, а так же второй и третий управляющие входы и информационный выход, отличающийся тем, что, с целью упрощения и уменьшения потребляемой мощностиf выход второго вентиля соединен также с вторым входом первого вентиля, выход четвертого вентиля соединен также с третьим входом третьего вентиля, выход которого соединен также с третьим входом первого вентиля, третьи входы второго и четвертого вентилей являются соответственно вторым и третьим управ- лякщими входами запоминающего элемента, причем информационным выходом запоминающего элемента является вькод первого (или третьего) вентиля.

2. Элемент поп,1, отличаю щ и и с я тем, что, выход третьего (или первого) является дополнительным (инверсным) информационным выходом запоминающего элемента.

3. Элемент по пп. 1 и 2, о т л и-, чающийся тем, что инвертирую щие вентили являются вентилями интегральной инжекционной логики с входными диодами Шоттки, причем каждый вентиль содержит переключающий п-р-п-транзистор, токозадающий р- п-р-транзистор, три входных диода Шоттки, катоды которых являются соот

10

t5

0

5

5 0

0

5

0

ветствующими входами вентиля, а аноды соединены с базой переключающего транзистора и с коллектором токоза- дающего транзистора, эмиттер которого соединен с источником питания положительной полярности, а база соединена с источником питания отрицательной полярности и с эмиттером переключающего транзистора, коллек- тор которого является выходом вентиля .

4.Элемент по пп. 1 и 2, о т л и- чающийся тем, что инвертирующие вентили являются вентилями комплементарной логики с переключением постоянного тока, причем каждый вентиль содержит переключающий п-р-п-транзистор, токозадающий р-п-р-транзистор, три входных диода Шоттки, катоды которых являются соответствующ ми входами вентиля,

а аноды соединены с базой переключающего транзистора и с коллектором токозадающего транзистора, эмиттер которого соединен с источником питания положительной полярности, а база - с источником опорного напряжения, эмиттер переключающего транзистора соединен с источником питания отрицательной полярности, коллектор переключающего транзистора является выходом вентиля.

5.Элемент попп. 1и2,отличающийся тем, что инвертирующие вентили являются вентилями инжекционно-полевой логики с выходными диодами Шоттки, причем каждый вентиль содержит переключающий п-ка- нальный полевой транзистор с управляющим р-п-переходом, токозадающий р-п-р-транзистор, три входных диода Шоттки, катоды которыхХявляются соответствующими входами вентиля, а аноды соединены с затвором переключающего транзистора и с коллектором токозадающего транзистора, эмиттер которого соединен с источником питания положительной полярности, а база - с источником питания отрицательной полярности и с истоком пе- реключакщего транзистора, сток которого является выходом вентиля.

(pue. 1

24 n e

п

тз

лРедактор А.Лежнина

Составитель И.Андреева Техред И.ПопоВИЧ

Заказ 6674/47Тираж 543 Подписное

ВНШ1ПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, й(-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор И.Эрдейи

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Быстродействующий ТТЛШ-вентиль | 1987 |

|

SU1531207A1 |

| Логический вентиль | 1980 |

|

SU940308A1 |

| Многовыходной вентиль и-не | 1979 |

|

SU813790A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Логический элемент "исключительное ИЛИ | 1982 |

|

SU1045397A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании мaлoмoro ;Ь x оперативггых запоминающих устройств, в частности вентильных запоминающих устройствJ время выборки и потребляемая мощность которых может варьироваться в широких пределах за счет изменения напряж - шя низковольтного источника питания. Целью изобретения является упрощение запоминающего элемента и yMeHbraeifme потребляемой мощности. Существо предложения состоит в новой организации связей между вентилями, позволившей уменьшить их число до четырех Е запоминаю1- ;ем элементе выход первого вентиля соединен с первыми входами второго и третьего вентилей, выход второго вентиля соединен с первым входом четвертого вентиля, выход которого соединен с вторым входом второго вентиля, -первый вход первого вентиля является первым управляющим входом запоминающего элемента и соединен -с вторым входом третьего вентиля, выход которого соединен с вторым входом четвертого вентиля. Новым в запоминающем элементе является то, что выход второго вентиля соединен также с вторым входом первого вентиля, выход четвертого вентиля соединен также с третьим входом третьего вентиля, выход которого соединен также с третьим входом первого вент1-шя, третьи входы второго и четвертого вентилей являются соответственно вторым и третьим управляющими входами запоминающего элемента, причем информационным выходом запоминающего элемента является выход первого (или третьего) вентиля, благодаря че- 1 достигается упрощение элемента и уменьшение потребляемой мощности. Кроме того, представлены варианты организации структуры запоминающего элемента при использовании дополнительного инверсного выхода, при использовании вентилей интегральной инжекционной логики, комплементарной логики с переключением постоянного тока, инжекционно-полевой логики. 4 з,п,ф-лы, 4 ил. . i (Л к о ;о

| Валиев К.А., Орликовский А,А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах, М,: Советское радиоj 1979, с.296 | |||

| Авторское свидетельство СССР № 812051, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-15—Публикация

1982-12-02—Подача