1

Изобретение относится к импульс- ной технике и предназначено для использования в интегральных логических цифровых микросхемах.

Цель изобретения - увеличение быстродействия устройства и уменьшение потребляемой мощности.

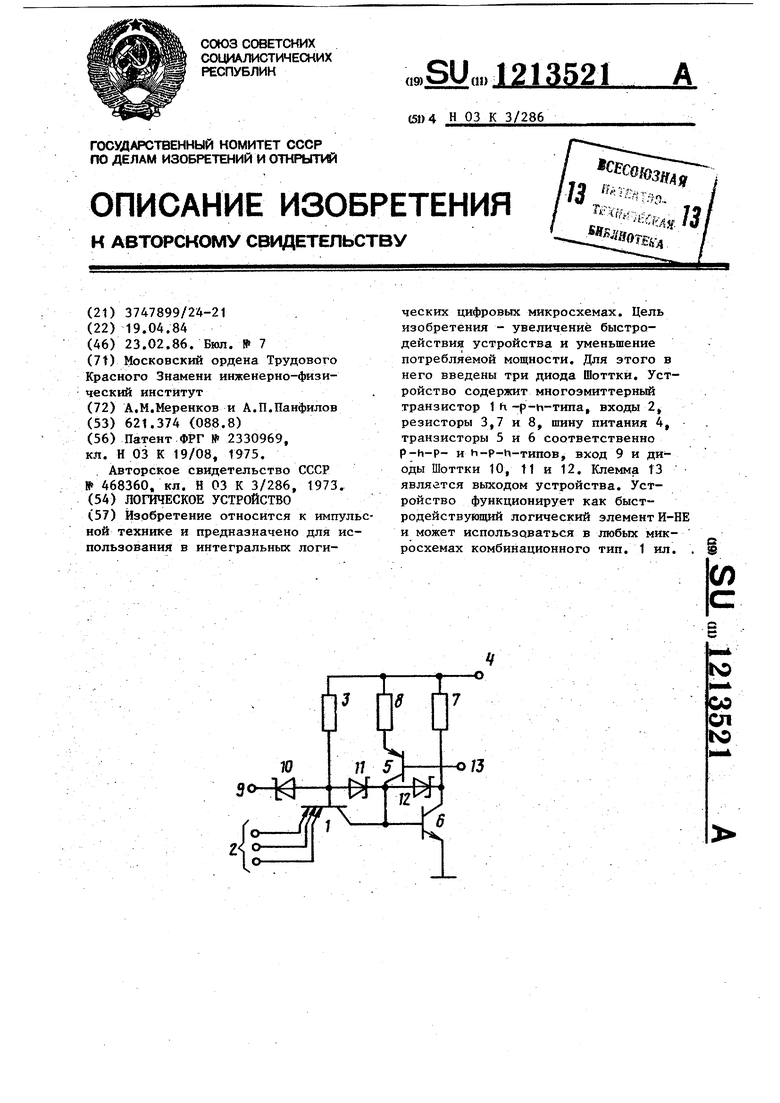

На чертеже представлена принципиальная схема предлагаемого логического устройства.

Логическое устройство содержит многоэмиттерный транзистор 1 п-р-п- типа, эмиттеры которого подключены кинформациочньм входам 2 устройства база через первый резистор 3 соединена с шиной питания 4, база и коллектор первого транзистора 5 р-п-р-типа подключены соответственно к коллектору и базе второго транзистора 6 п-р-п-типа, коллектор которого через второй резистор 7 подключен к шине питания А, эмиттер - к общей шине, эмиттер первого транзистора 5 через третий резистор соединен с вшной питания 4, управляющий вход 9 устройства через третий диод Шоттки 10 соединен с базой многоэмиттерного транзистора 1, которая через первый диод Шоттки t1 соединена с коллекторами многоэмиттерного транзистора 1 и первого тразистора 5, которые через второй диод Шоттки 12 соединены с выходом 13 устройства и коллектором второго транзистора 6,

Логическое устройство работает следующим образом.

При подаче на все информационные входы (2) и управляющий вход 9 уровней логической единицы V ток, про- текакищй через первый резистор 3, поступает на базу второго транзистора 6, вызывая отпирание тиристора выполненного на первом и втором транзисторах 5 и 6, и втором диоде Шоттки 12, Ток первого резистора 3 выбирается достаточным для насьш1е- ния второго транзистора 6, Таким образом, на выходе 13 устройства уста на вливается уровень логического нуля V , При подаче на управляющий вход 9 уровня логической единицы, а хотя бы на один из информационных . входов 2 уровня логического нуля v многоэмиттерньй транзистор 1 насыщается и напряжение на базе второго транзистора 6 падает до величины Vg V +V,, где Vn3 - напряжение между эмиттером и коллектором насы21i

щенного многоэмиттерного транзисто- ра 1, Так как где V - напряжение на открытом переходе база-эмиттер второго транзистора 6, то, следовательно, второй транзистор 6 запирается и ток, протекающий через второй резистор 7 уменьшается до нуля, что вызывает запирание первого транзистора 5, так как потенциал

на его базе поднимается почти до уровня напряжения питания. Таким образом, на выходе устройства устанавливается потенциал логической единицы v, Второй резистор 7 позволяет быстро перезарядить выходную паразитную емкость увеличивая тем самым скорость включения тиристора. При поддержании на управляющем входе 9 потенциала логической единицы V на выходе элемента реализуется логическая функция КИ-НЕ, где К - число эмиттеров многоэмиттерного транзистора 1,

Если на управляющий вход 9 поступает уровень логического нуля V , то многоэмиттерный транзистор 1 закрывается при любых потенциалах на информационных входах 2, так как потенциал на его базе V5 V +V|uo

где Ущд - падение напряжения на открытом третьем диоде Шоттки 10 в то время, как на любом эмиттере многоэмиттерного транзистора 1 потенциал не опускается ниже величины V°, поэтому падение напряжения на переходах база-эмиттер многозмиттер- ного транзистора 1 не превьш1ает величины Vmo, что недостаточно для удержания транзистора в открытом состоянии. Тиристор на первом и втором транзисторах 5 и 6 сохраняет то состояние (открытое или закрытое), которое он имел в момент запирания многоэмиттерного транзистора 1 вследствие уменьшения потенциала

на управляющем входе 9 до уровня V, Третий резистор 6 ограничивает величину тока, протекающего через тиристор в открытом состоянии, Сох- ранение исходного состояния осуществляется за счет наличия глубо- кой положительной обратной связи в первом и втором транзисторах 5 и 6,

Таким образом, предлагаемое уст- ройство позволяет записывать при подаче на управляющий вход 9 уровня логической единицы, инвертированное логическое произведение состояний

3

на информационных входах 2 и сохранять его при подаче на управляющий вход 9 уровня логического нуля и вьтолняет функцию В-григгера с . логикой И-НЕ на входе. При удержании потенциала логической единицы на информационном входе 9 или если этот вход не подключен больше ни к каким источникам сигнала, предлагаемое устройство функционирует как быстродействзпмций логический элемент И-НЕ и может быть использовано в любых микросхемах комбинационного типа.

Формула изобретени

Логическое устройство, содержащее управляющий вход, информационные входы, подключенные к эмиттерам многоэмиттерного транзистора h -p-vi- типа, база которого подключена к первому выводу первого резистора, база и коллектор первого транзисРедактор Н.Гунько Заказ 785/60

Составитель А.Янов Техред Т.Дубинчак

Корректор

Тираж 818Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

13521

тора р -ti-p-типа подключены соответственно к коллектору и базе второго транзистора п-р-п-типа, коллектор которого соединен с выходом 5 устройства и через второй резистор подключен к щине питания, а эмиттер подключен к общей шине, эмиттер первого транзистора через третий резистор подключен к шине питания.

отличающееся тем, что, с целью увеличения его быстродействия и уменьшения потребляемой мощности, в него введены три диода Шоттки, анод первого из которых

соединен с базой многоэмиттерного транзистора, катод - с его коллектором, базой второго транзистора и анодом второго диода, катод которо- го соединен с коллектором второго

транзистора, катод третьего диода соединен с управляющим входом, а анод - с первьм вьшодом первого резистора, второй вывод которого соединен с пшной питания.

Корректор Л.Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Синхронный логический элемент | 1976 |

|

SU573881A1 |

| Устройство согласования интегральных инжекционных схем с линиями передачи коллективного пользования | 1983 |

|

SU1092726A1 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

Изобретение относится к импульсной технике и предназначено для использования в интегральных логических цифровых микросхемах. Цель изобретения - увеличение быстродействия устройства и уменьшение потребляемой мощности. Для этого в него введены три диода Шоттки. Устройство содержит многоэмиттерный транзистор 1h -p-h-типа, входы 2, резисторы 3,7 и 8, шину питания 4, транзисторы 5 и 6 соответственно p-h-p- и h-p-h-типов, вход 9 и диоды Шоттки 10, 11 и 12. Клемма 13 является выходом устройства. Устройство функционирует как быстродействующий логический элемент И-БЕ и может использоваться в любых микросхемах комбинационного тип. 1 ил. , ю sH

| МНОГОКАМЕРНЫЙ ГЛУШИТЕЛЬ ШУМА ВЫХЛОПА ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2005 |

|

RU2330969C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Д-триггер | 1973 |

|

SU468360A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-23—Публикация

1984-04-19—Подача