1

Изобретение относится к вычислительной технике и может использоваться для создания дешевых и экономичных монолитных запоминающих устройств средней и большой информационной емкости с малой потребляемой мощностью, время выборки которых может варьироваться в широких пределах за счет изменения напряжения низковольтного источника питания.

Известны структурные и электрические схемы запоминающих устройств с произвольной выборкой (ЗУПВ) любого из одноразрядных слов 1-4. Известна «классическая схема ЗУПВ, содержащего блок управления, дешифраторы, матричный накопитель на основе запоминающих элементов типа ТТЛ 1. Недостатками таких схем являются сложность схем обрамления и большая потребляемая мощность. Замена в таких ЗУПВ запоминающих элементов типа ТТЛ и ЭСЛ на инжекционные запоминающие элементы практически сохраняет те же недостатки в наиболее распространенных на сегодняшний день запоминающих устройствах с информационной емкостью 64-1024 бит; по-прежнему схемы обрамления занимают в кристаллах таких ЗУПВ наибольшую часть площади кристалла и именно на них падает наибольшая доля потребляемой мощности 5 и 6.

Известно также ЗУПВ, в котором уменьшается потребляемая мощность при невыборке кристалла. Это запоминающее устройство содержит блок управления, первый,

5 второй и третий входы которого подключены соответственно к входу разрешения записи, к входу выборки устройства и к информационному входу устройства, первый выход блока управления соединен с информационным выходом устройства, второй выход блока управления подключен к первым входам блока разрядных формирователей, первые выходы которого соединены с информационными разрядными щинами матричного накопителя, словарный и разрядный дешифраторы, входы которых подключены к адресным входам устройства, а выходы соединены соответственно с адреснословарной шиной и с адресной разрядной

20 шиной 7.

К недостаткам устройства относятся, вопервых, невысокие функциональные возможности, обусловленные наличием импульсного питания, незначительным по

25 сравнению с режимом обращения, уменьшением потребляемой в режиме хранения мощности (лишь в несколько раз) и невозможностью изменения времени выборки, и, во-вторых, существенное усложнение схем

30 обрамления, что приводит к увеличению

площади кристалла и снижению надежности ЗУПВ.

Цель изобретения состоит в упрощении устройства и расщирении области его применения за счет регулирования времени выборки изменением тока нитания.

Это достигается тем, что четвертый вход блока управления соединен с выходом дополнительно введенного блока словарных формирователей, первые и вторые выходы которого подключены к адресным словарным шинам и к словарным шинам считывания матричного накопителя, третий и четвертый выходы блока управления соединены со вторым и третьим входами блока разрядных формирователей, вторые выходы которого подключены к разрядным шинам разрешения записи матричного накопителя.

Кроме того, блок управления содерлсит пять одновходовых инжекционных вентилей и шестой трехвходовой инжекциоииый вентиль И-НЕ, выход которого подключен к первому выходу блока управления, первый и второй входы которого подключены ко входам первого и второго вентилей, выход первого вентиля соединен со входом третьего вентиля, выход которого соединен с первым входом шестого вентиля и с третьим выходом блока управления, второй выход которого соединен с выходом четвертого вентиля, вход которого подключен к третьему входу блока управления, четвертый вход блока управления соедииен со вторым входом шестого вентиля, третий вход которого соединен с выходом второго и входом пятого вентилей, выход пятого вентиля соединен с четвертым выходом блока управления.

Каждый формирователь блока разрядных формирователей содержит два одновходовых инжекционных вентиля и третий двухвходовый инжекционный вентиль И-НЕ, первый и второй входы которого соединены соответственно со вторым и третьим входами формирователя, первый вход которого соединен с входом первого вентиля, выход которого соединен с первым выходом формирователя, второй выход которого соединен с выходом второго вентиля, вход которого нодключен к выходу третьего вентиля.

Каждый формирователь блока словарных формирователей содержит один двухвходовый инжекциоиный вентиль И-НЕ, выход которого соединен с выходом формирователя, первый и второй входы - с первым и вторым входами формирователя.

Матричный накопитель выполнен на запоминающих элементах, содержащих два четырехвходовых и три двухвходовых иижекционных вентиля И-НЕ, выход каждого запоминающего элемента соединен со словарной шиной считывания и подключен к выходу третьего двухвходового вентиля, первый вход которого соединен с выходом второго и со вторым входом первого двухвходовых вентилей, выход первого двухвходового вентиля соединен со вторым входом второго двухвходового вентиля, первые входы первого и второго двухвходовых вентилей соединены соответственно с выходом первого и первым входом второго и с выходом второго четырехвходовых вентилей, четвертые входы которых соединены со вторым входом третьего двухвходового вентиля и подключены к четвертому входу запоминающего элемента, третьи входы четырехвходовых вентилей соединены с третьим входом запоминающего элемента, первые входы - с первым входом заноминающего элемента, а второй вход первого четырехвходового вентиля соединен со вторым входом запоминающего элемента, и первый, второй, третий и четвертый входы каждого запоминающего элемента подключены соответственно к разрядной шине заниси, к информационной разрядной шине, к адресной словарной шине и к адресной разрядной шине.

Каждый дешифратор содержит одновходовые инжекционные инверторы, повторители, выходные вентили и многовходовые вентили И-НЕ, выходы выходных вентилей подключены к -выходам дешифратора, а входы - к выходам многовходовых вентилей, входы которых соединены с выходами соответствующих инверторов и повторителей, входы которых подключены к выходам соответствующих инверторов, входы которых подключеиы к входам дешифратора.

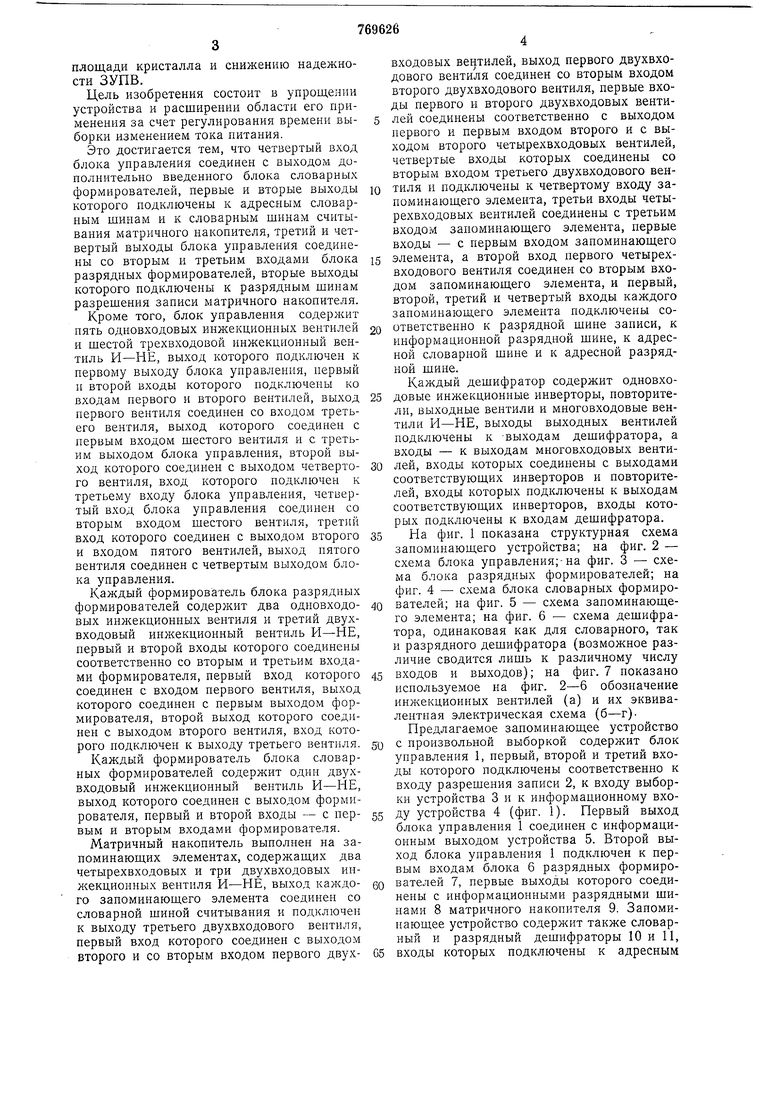

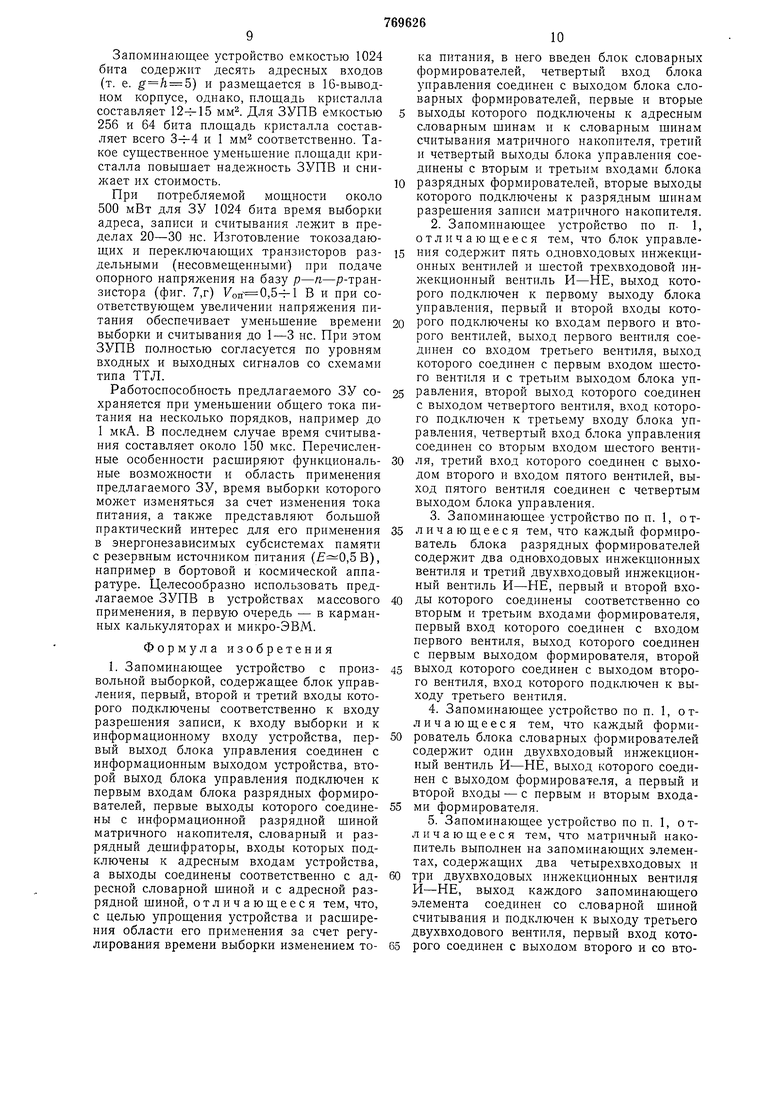

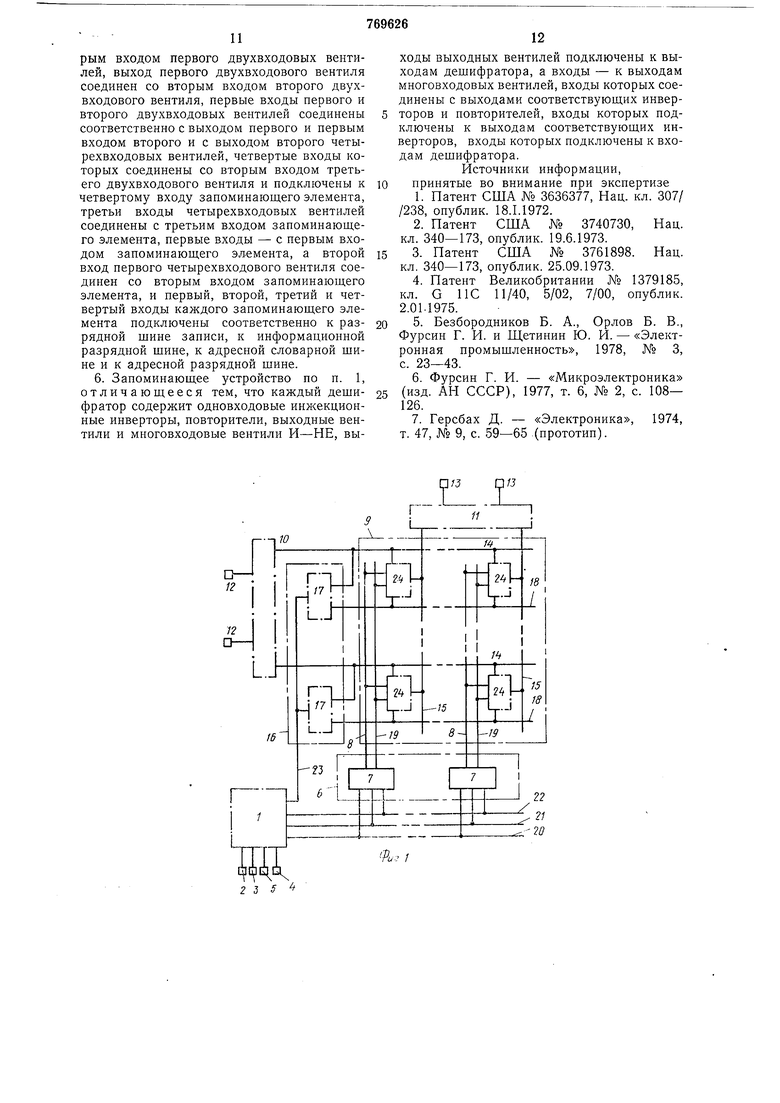

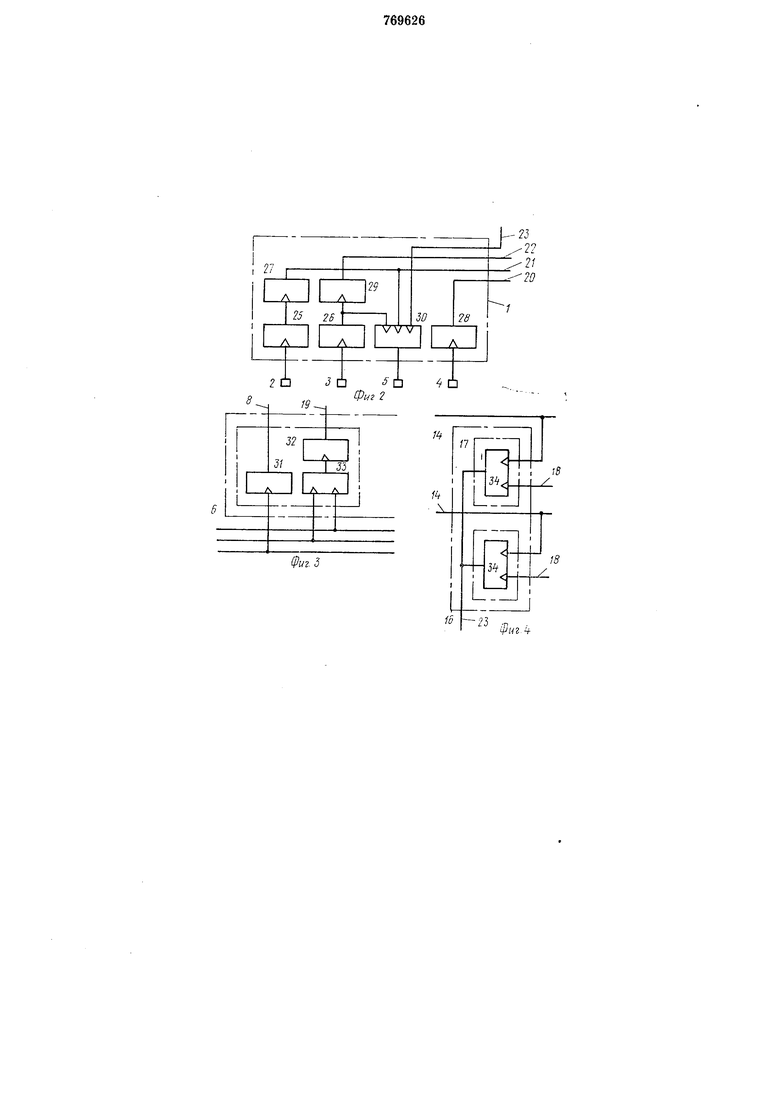

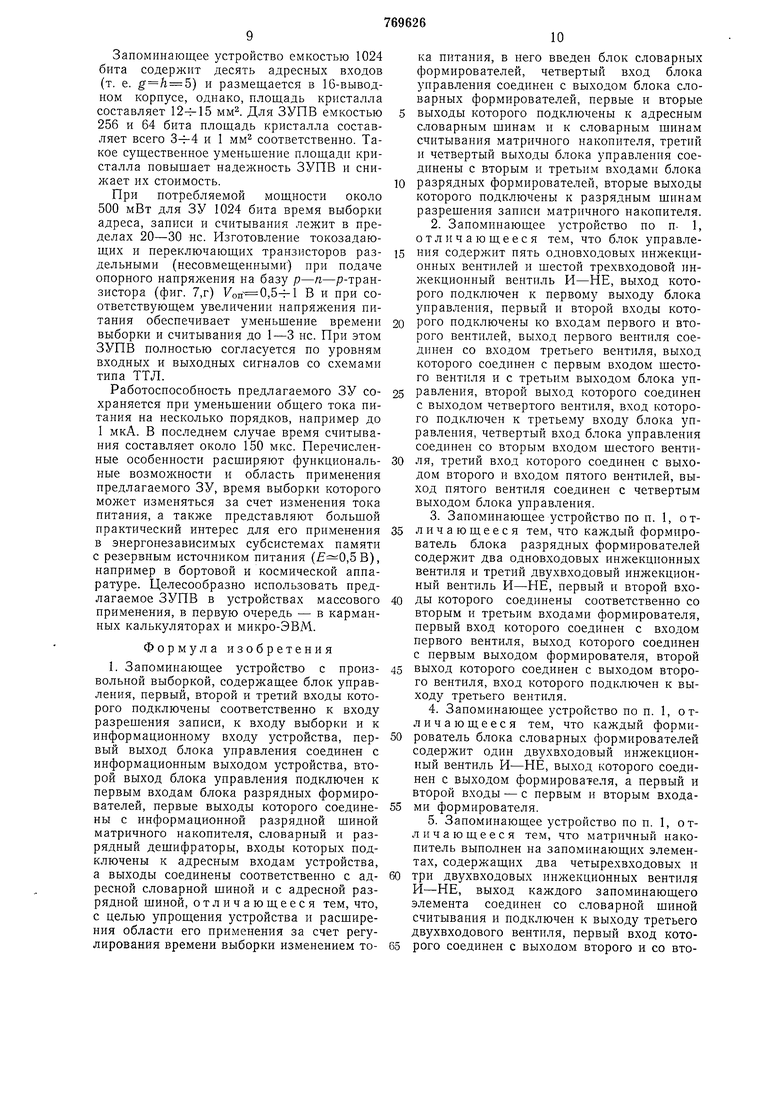

На фиг. 1 показана структурная схема запоминающего устройства; на фиг. 2 - схема блока управления;-на фиг. 3 - схема блока разрядных формирователей; на фиг. 4 - схема блока словарных формирователей; иа фиг. 5 - схема запоминающего элемента; на фиг. 6 - схема дешифратора, одинаковая как для словарного, так и разрядного дешифратора (возможное различие сводится лишь к различному числу входов и выходов); на фиг. 7 показано используемое на фиг. 2-6 обозначение инжекционных вентилей (а) и их эквивалентная электрическая схема (б-г)Предлагаемое запоминающее устройство с произвольной выборкой содержит блок управления 1, первый, второй и третий входы которого подключены соответственно к входу разрешения записи 2, к входу выборки устройства 3 и к информационному входу устройства 4 (фиг. 1). Первый выход блока управления 1 соединен с информационным выходом устройства 5. Второй выход блока управления 1 подключен к первым входам блока 6 разрядных формирователей 7, первые выходы которого соединены с информационными разрядными шинами 8 матричного накопителя 9. Запомипающее устройство содержит также словарный и разрядный дешифраторы 10 и II, входы которых подключены к адресным

входам устройства 12 и 13, а выходы соединены соответственно с адресной словарной шиной 14 и с адресной разрядной шиной 15.

Четвертый вход блока уиравления 1 соединен с выходом дополнительного блока 16 словарных формирователей 17, иервые и вторые выходы которого иодключены к адресным словарным шинам 14 н к словарным шинам считывания 18 матричного наконителя 9 с разрядными шинами заниси 19. Второй, третий и четвертый выходы блока управления 1 соединены с помошью первой, второй и третьей шин управления 20. 21 и 22 соответственно с первым, втооым и третьим входами формирователей 7. Четвертый вход блока управления 1 соединен с помошьго четвертой шины управления 23 с выходами формирователей 17, которые подключены шииами 14 и 18 к выходам запоминающих элементов 24.

В предлагаемом запоминающем устройстве все схемы обрамления и матричный накопитель информации выполнены на инжекционных вентилях с входными диодами Шоттки, допускающими объединение их входов, в отличие от всех других известных инжекнионных вентилей (без диодов Шоттки, либо с выходными коллекторными диодами Шоттки), и позволяющими реализовывать логические функции в иаиболее гибком и удобном для разработчиков базиса И-ИЛИ-НЕ. При этом одновходовые вентили выполняют функцию инвертора, т. е. реализуют логическую функцию НЕ, а двухвходовые и многовходовые вентили реализуют логическую функцию И-НЕ без проводного объединения выходов переключающих транзисторов и логическую функцию И-ИЛИ-НЕ ири объединении выходов транзисторов.

Блок управления 1 содержит пять одиовходовых инжекционных вентилей 25-29 и шестой трехвходовый инжекциониый вентнль И-НЕ 30, выход которого подключен к первому выходу блока уиравлення (фиг. 2). Первый и второй входы последнего подключены ко входам первого и второго вентилей 25, 26. Выход первого веитиля 25 соединен со входом третьего вентиля 27, выход которого соединен с первым входом шестого вентиля и с третьим выходом блока уцравлеиия, второй выход которого соединен с выходом четвертого вентиля 28, вход которого подключен к третьему входу блока управления 1. Четвертый вход последнего соединен со вторым входом шестого вентиля 30, третий вход которого соединен с выходом второго 26 и входом пятого вентилей 29. Выход пятого соединен с четвертым выходом блока управления.

Каждый формирователь 7 блока 6 разрядных формирователей содержит два одновходовых инжекционных вентиля 31, 32 и третий двухвходовый иижекционный вентиль И-НЕ 33, первый и второй входы которого соединены соответственно со вторым и третьим входами формирователя 7 (фиг. 3). Первый вход последнего соединен с входом первого вентиля 31, выход которого соедииен с иервым выходом формирователя, второй выход которого соединен с выходом второго вентиля 32, вход последнего подключен к выходу третьего вентиля 33.

Каждый формирователь 17 блока 16 словарных формирователей содержит один двухвходовый инжекционный вентиль И-НЕ 34, выход которого соединен с выходом формирователя 17, первый и второй

входы веитиля 34 соединены с первым и вторым входами формирователя (фиг. 4).

Матричный накопитель 9 выиолнен на запоминающих элементах 24 (фттг. 5), содержащих три двухвходовых инжекционных

вентиля И-НЕ 35-37 и два четырехвходовых 38 и 39. Выход элемеита 24 соединен со словарной шиной считывания 18 и подключен к выходу третьего двухвходового веитиля 37, первый вход КОТОРОГО

соединен с выходом второго 36 и со вторым входом первого двухвходовых вентилей 35. Выход первого вентиля 35 соедииен со вторым входом второго двухвходового ветттля 36. Пспл1,тс входы первого и второго веитилей 35 и 36 соединеиы соотвстственио с выходом первого и первым входом второго тт с Т5ьтхолом второго четырехвходовых вентилей 38 и 39, четвертые входы КОТОРЫХ соедииены со вторым входом третьего двухвходовогО вентиля 37 и подключены к четвертому Bxo.v запоминаю1иего элемента. Третьи входы четьтрехчходовых вентилей 38 и 39 соединены с третьим входом заиомииаютнего элемента, первые входы - с

нервым входом запоминающего элемента, второй вхол первого четыпехвходового веитиля 38 соединен со ВТОРЫМ входом запоминающего элемента, а первый, второй, третий и чотвептый входы каждого зпиоминающего элемеита подключены соответственно к разрядной шиие записи 19, к ипформациочиой разрядной шиие 8. к адресной словарной итине 14 и к адресной разрядной шиие 15.

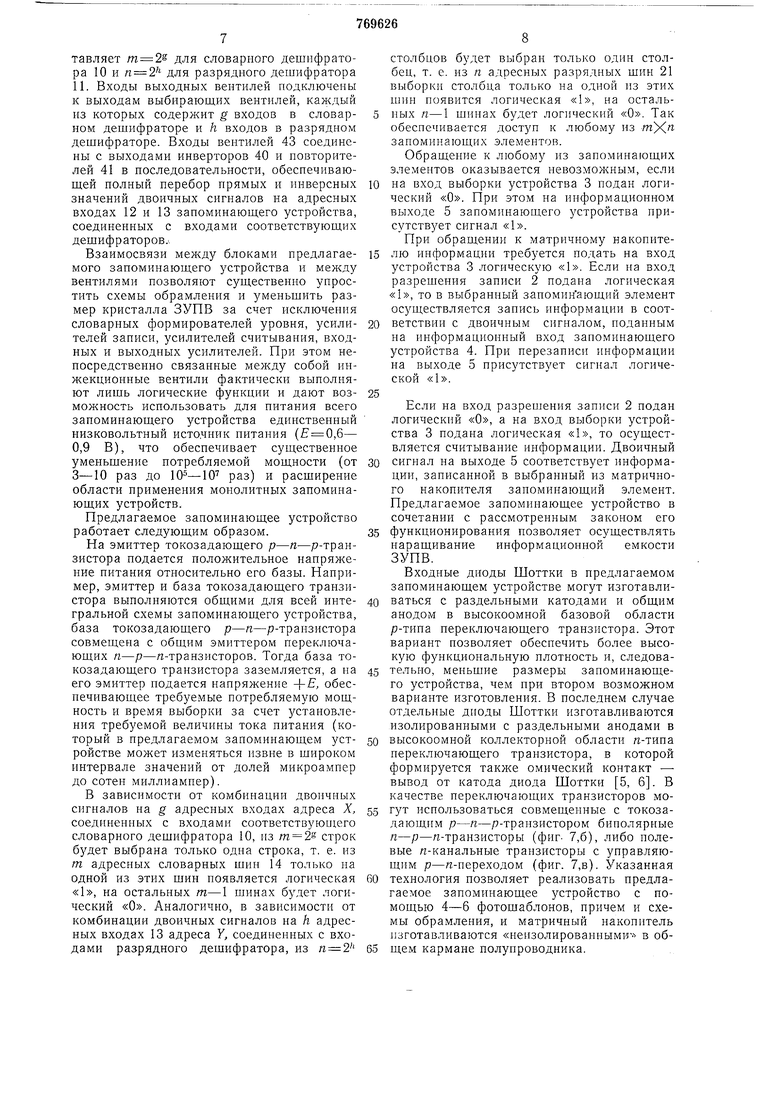

Каждый дешифратор 10 или 11 (фиг. 6) содержит одновходовые ттижекииониые инверторы 40. повторители 41. выходные вентили 42 и многовходовые вентили И-НЕ 43. Выходы вентилей 42 подключены к выходам нтины 14 (или 15V а входы - к выходам многовходовых вентилей 43, входы которых соединены с выходами соответствующих инверторов 40 и повторителей 41, входы которых подк.тючены к выходам соответствуюшпх инверторов 40, входы которых подключены к входам устройства 12 (или 13).

Число выходов дешифраторов, соединяемых с адресными словарными шинами 14 и

с адреснымн разрядными шинами 15, соетавляет т 2 для словарного дешифратора 10 и п Т для разрядного дешифратора И. Входы выходных вентилей подключены к выходам выбнраюш,нх вентилей, канадый из которых содержит g входов в словарном дешифраторе и h входов в разрядном дешифраторе. Входы вентилей 43 соединены с выходами инверторов 40 и иовторителей 41 в последовательности, обеспечивающей полный перебор прямых и инверсных значений двоичных сигналов на адресных входах 12 и 13 заноминаюшего устройства, соединенных с входами соотБетствуюш,их дешифраторов..

Взаимосвязи мелсду блоками предлагаемого запоминаюш,его устройства и между вентилями позволяют сушественно упростить схемы обрамления и уменьшить размер кристалла ЗУПВ за счет исключения словарных формирователей уровня, усилителей записи, усилителей считывания, входных и выходных усилителей. При этом непосредственно связанные между собой инжекционные вентили фактически выполняют лишь логические функции и дают возможность использовать для питания всего запоминаюш,его устройства единственный низковольтный исто.чник нитания (0,6- 0,9 В), что обеспечивает существенное уменьшение потребляемой мощности (от 3-10 раз до раз) и расширение области применения монолитных запоминающих устройств.

Предлагаемое запоминающее устройство работает следующим образом.

На эмиттер токозадающего р-п-р-транзистора подается положительное напряжение питания относительно его базы. Например, эмиттер и база токозадающего транзистора выполняются общими для всей интегральной схемы запоминаюи1его устройства, база токозадающего р-п-р-транзистора совмещена с общим эмиттером переключающих п-р-л-транзисторов. Тогда база токозадающего транзистора заземляется, а на его эмиттер подается напряжение , обеспечивающее требуемые потребляемую мощность и время выборки за счет установления требуемой величины тока нитания (который в предлагаемом запоминающем устройстве изменяться извне в щироком интервале значений от долей микроампер до сотен миллиампер).

В зависимости от комбинации двоичиых сигналов на g адресных входах адреса X, соединенных с входами соответствуюн1его словарного дешифратора 10, из m 2s строк будет выбрана только одна строка, т. е. из т адресных словарных шин 14 только на одной из этих щин появляется логическая «1, на остальных т-1 шинах будет логический «О. Аналогично, в зависимости от комбинации двоичных сигналов на h адресных входах 13 адреса Y, соединенных с входами разрядного дешифратора, из

столбцов будет выбран только один столбец, т. е. из п адресных разрядных шин 21 выборки столбца только на одной из этих тин появится логическая «1, на остальиых п-1 шниах будет логический «О. Так обеспечивается доступ к любому из запоминающих элементов.

Обращение к любому из запомииающих элемеитов оказывается невозможным, если

на вход выборки устройства 3 подан логический «О. При этом иа информационном выходе 5 запоминающего устройства присутствует сигнал «1. При обращении к матричному накопнтелю информации требуется подать на вход устройства 3 логическую «1. Если на вход разрешения записи 2 подана логическая «1, то в выбранный запоминающий элемент ос)ществляется запись информации в соответствии с двоичным сигналом, поданным на информационный вход заноминаюшего устройства 4. При перезаписи информации иа выходе 5 присутствует сигнал логической «1.

Если на вход разреоления записи 2 подан логический «О, а на вход выборки устройства 3 подана логическая «1, то осуществляется считываиие ннформации. Двоичный

сигнал на выходе 5 соответствует информации, записанной в выбранный из матричного накопителя запоминающий элемент. Предлагаемое запоминающее устройство в сочетании с рассмотреиным законом его

функцнонирования позволяет осуществлять наращивание информационной емкости ЗУПВ.

Входные диоды Шоттки в предлагаемом запоминающем устройстве могут изготавливаться с раздельными катодами и общим анодом в высокоомной базовой области р-типа переключающего транзистора. Этот вариант иозволяет обеспечить более высокую функциональную плотность и, следовательио, меньшие размеры заномииаюшего устройства, чем при втором возможном варианте изготовления. В последнем случае отдельиые диоды Шоттки изготавливаются изолированными с раздельиыми анодами в

высокоомной коллекторной области п-типа иереключающего транзистора, в которой формируется также омический контакт - вывод от катода диода Шоттки 5, 6. В качестве переключающих транзисторов могут использоваться совмещенные с токозадающим р-п-р-транзистором биполяриые п-р-и-транзисторы (фиг- 7,6), либо полевые rt-канальные транзисторы с управляющим р-и-переходом (фиг. 7,в). Указанная

технология позволяет реализовать предлагаемое запоминающее устройство с помощью 4-6 фотошаблонов, причем и схемы обрамления, и матричный накопитель изготавливаются «нензолированными-- в общем кармане полупроводника.

Запоминающее устройство емкостью 1024 бита содержит десять адресных входов (т. е. 5) и размещается в 16-выводном кориусе, однако, площадь кристалла составляет 124-15 мм. Для ЗУПВ емкостью 256 и 64 бита площадь кристалла составляет всего и 1 мм соответственно. Такое существенное уменьшение площади кристалла повышает надежность ЗУПВ и снижает их стоимость.

При потребляемой мощности около 500 мВт для ЗУ 1024 бита время выборки адреса, записи и считывания лежит в пределах 20-30 НС. Изготовление токозадающих и переключающих транзисторов раздельными (несовмещенными) при нодаче опорного напрял ения на базу р-п-р-транзистора (фиг. 7,г) , В и при соответствующем увеличении напряжения питания обеспечивает уменьшение времени выборки и считывания до 1-3 не. При этом ЗУПВ полностью согласуется по уровням входных и выходных сигналов со схемами типа ТТЛ.

Работоспособность предлагаемого ЗУ сохраняется при уменьшении общего тока нитания на несколько порядков, нанример до 1 мкА. В последнем случае время считывания составляет около 150 мкс. Перечисленные особенности расширяют функциональные возможности и область применения предлагаемого ЗУ, время выборки которого может изменяться за счет изменения тока питания, а также представляют большой практический интерес для его применения в энергонезависимых субсистемах памяти с резервным источником питания (,5В), нанример в бортовой и космической аппаратуре. Целесообразно использовать предлагаемое ЗУПВ в устройствах массового применения, в первую очередь - в карманных калькуляторах и микро-ЭВМ.

Формула изобретения

1. Запоминающее устройство с произвольной выборкой, содержащее блок управления, нервый, второй и третий входы которого подключены соответственно к входу разрешения записи, к входу выборки и к информационному входу устройства, нервый выход блока управления соединен с информационным выходом устройства, второй выход блока управления подключен к первым входам блока разрядных формирователей, первые выходы которого соединены с информационной разрядной шиной матричного накопителя, словарный и разрядный дешифраторы, входы которых подключены к адресным входам устройства, а выходы соединены соответственно с адресной словарной шиной и с адресной разрядной шиной, отличающееся тем, что, с целью упрощения устройства и расширения области его применения за счет регулирования времени выборки изменением тока питания, в него введен блок словарных формирователей, четвертый вход блока унравления соединен с выходом блока словарных формирователей, первые и вторые

выходы которого подключены к адресным словарным шинам и к словарным шинам считывания матричного наконнтеля, третий и четвертый выходы блока управления соединены с вторым и третьим входами блока

разрядных формирователей, вторые выходы которого подключены к разрядным шинам разрешения записи матричного наконителя.

2.Запоминающее устройство по п. 1, отличающееся тем, что блок управлення содержит пять одновходовых ннжекционных вентилей и шестой трехвходовой инжекционный вентиль И-НЕ, выход которого подключен к первому выходу блока унравления, первый и второй входы которого подключены ко входам первого и второго вентилей, выход первого вентиля соединен со входом третьего вентиля, выход которого соединен с первым входом шестого вентиля и с третьим выходом блока унравления, второй выход которого соединен с выходом четвертого вентиля, вход которого подключен к третьему входу блока управления, четвертый вход блока унравления соединен со вторым входом шестого вентиля, третий вход которого соединен с выходом второго и входом пятого вентилей, выход пятого вентиля соединен с четвертым выходом блока управления.

3.Запоминающее устройство но п. 1, отличающееся тем, что каждый формирователь блока разрядных формирователей содержит два одновходовых инжекционных вентиля и третий двухвходовый инжекционный вентиль И-ПЕ, первый и второй входы которого соединены соответственно со вторым и третьим входами формирователя, первый вход которого соединен с входом первого вентиля, выход которого соединен с нервым выходом формирователя, второй

выход которого соединен с выходом второго вентиля, вход которого подключен к выходу третьего вентиля.

4.Запоминающее устройство по п. 1, отличающееся тем, что каждый формирователь блока словарных формирователей содержит один двухвходовый инжекционный вентиль И-НЕ, выход которого соединен с выходом формирователя, а первый и второй входы - с первым и вторым входами формирователя.

5.Запоминающее устройство по н. 1, отличающееся тем, что матричный накопитель выполнен на запоминающих элементах, содержащих два четырехвходовых и

три двухвходовых инжекционных вентиля И-НЕ, выход каждого запоминающего элемента соединен со словарной шиной считывания и подключен к выходу третьего двухвходового вентиля, нервый вход которого соединен с выходом второго и со вто11

рым входом первого двухвходовых вентилей, выход первого двухвходового вентиля соединен со вторым входом второго двухвходового вентиля, первые входы первого и второго двухвходовых вентилей соединены соответственно с выходом первого и первым входом второго и с выходом второго четырехвходовых вентилей, четвертые входы которых соединены со вторым входом третьего двухвходового вентиля и подключены к четвертому входу запоминающего элемента, третьи входы четырехвходовых вентилей соединены с третьим входом запоминающего элемента, первые входы - с первым входом запоминающего элемента, а второй вход первого четырехвходового вентиля соединен со вторым входом запоминающего элемента, и первый, второй, третий и четвертый входы каждого запоминающего элемента подключены соответственно к разрядной щине записи, к информационной разрядной шине, к адресной словарной шине и к адресной разрядной щине.

6. Запоминающее устройство по п. 1, отличающееся тем, что каждый дешифратор содержит одновходовые инжекционные инверторы, повторители, выходные вентили и многовходовые вентили И-НЕ, вы12

ходы выходных вентилей подключены к выходам дешифратора, а входы - к выходам многовходовых вентилей, входы которых соединены с выходами соответствующих инверторов и повторителей, входы которых подключены к выходам соответствующих инверторов, входы которых подключены к входам дешифратора.

Источники информации, принятые во внимание при экспертизе

1.Патент США JYo 3636377, Нац. кл. 307/ /238, опублик. 18.1.1972.

2.Патент США № 3740730, Нац. кл. 340-173, опублик. 19.6.1973.

3. Патент США № 3761898. Нац. кл. 340-173, опублик. 25.09.1973.

4. Патент Великобритании N° 1379185, кл. G ПС 11/40, 5/02, 7/00, опублик. 2.01.1975.

5. Безбородников Б. А., Орлов Б. В., Фурсин Г. И. и 1Детипин Ю. И. - «Электронная промыщленность, 1978, № 3, с. 23-43.

6.Фурсин г. И. - «Микроэлектроника (изд. АН СССР), 1977, т. 6, № 2, с. 108-

126.

7.Герсбах Д. - «Электроника, 1974, т. 47, № 9, с. 59-65 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

| Запоминающее устройство | 1986 |

|

SU1417036A1 |

| Полупроводниковое запоминающее устройство с произвольной выборкой | 1984 |

|

SU1215135A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

2 3 f

ФигЗ

8

5

L

Авторы

Даты

1980-10-07—Публикация

1977-01-27—Подача