Изобретение относится к электросвязи и может быть использовано для тактовой синхронизации приемников дискретной информации систем передачи данных.

Цель изобретения - повышение точности синхронизации.

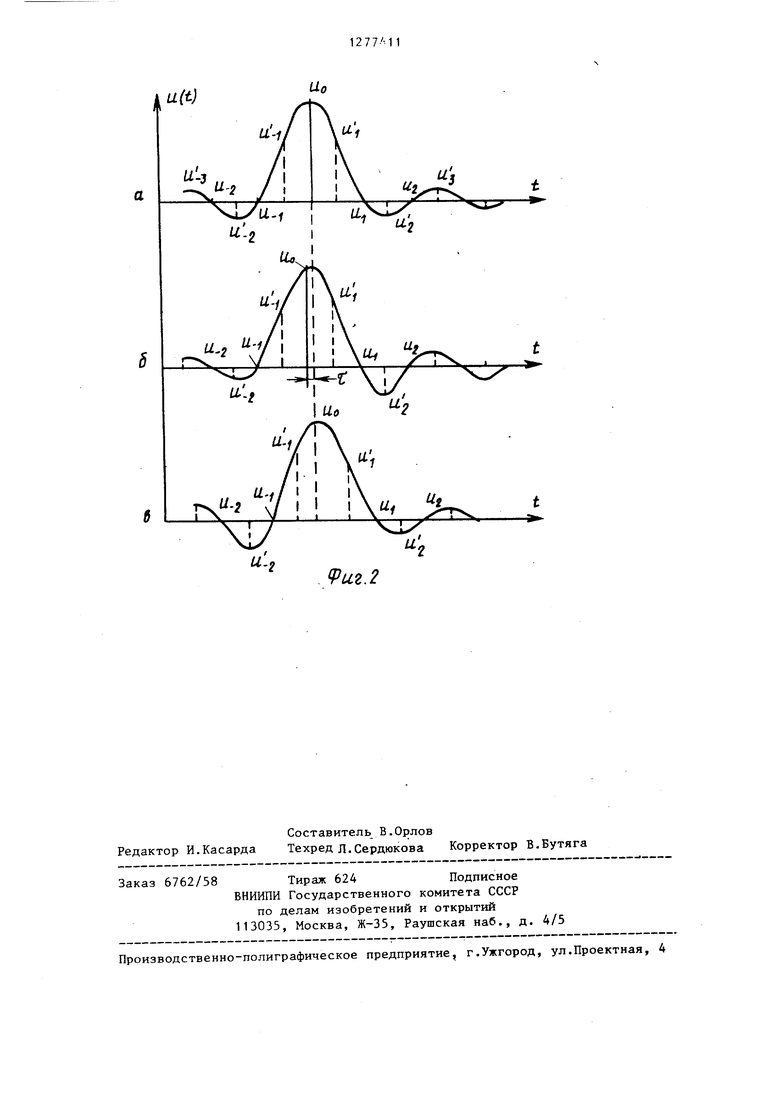

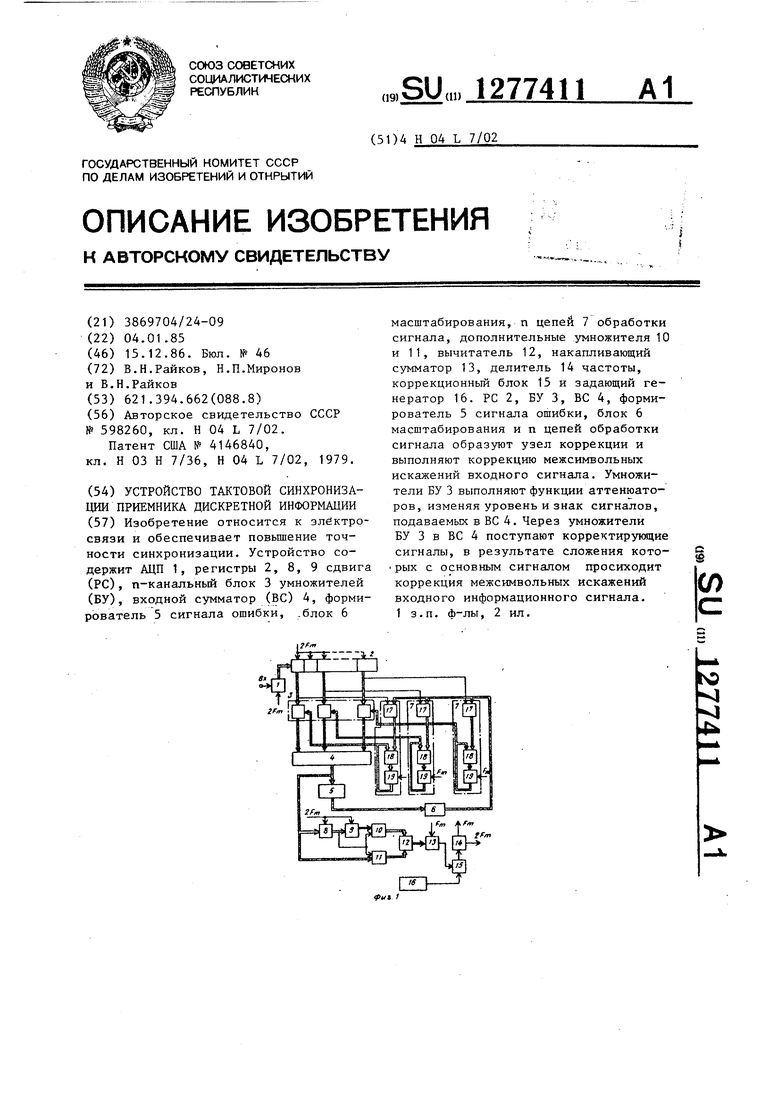

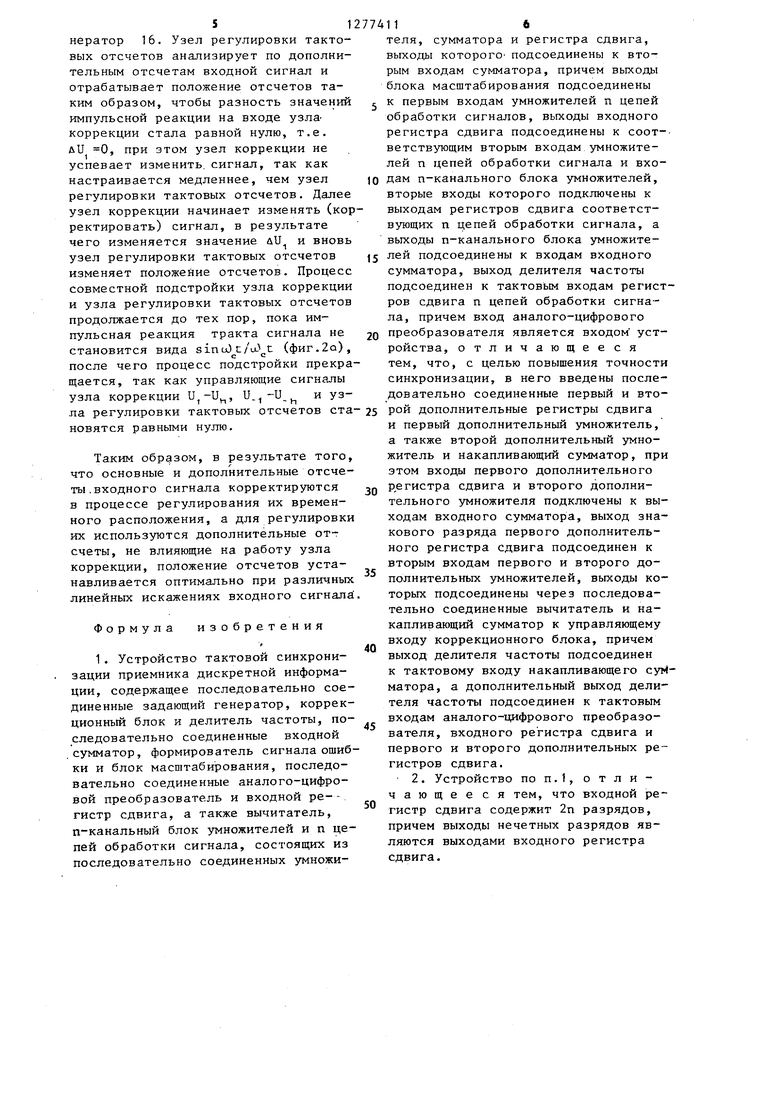

На фиг.1 представлена структурная электрическая схема устройства.тактовой синхронизации приемника дискретной информации; на фиг,2 - эпюры импульсной реакции канала связи при оптимальном положении отсчетов (фиг. 2ц) и при сдвинутых отсчетах соответственно в сторону опережения и отставания (фиг. 2S,&),

Устройство тактовой синхронизации приемника.дискретной информации содержит аналого-цифровой преобразова,тель (АЦП) 1, первый регистр 2 сдви- 20 матической (адаптивной) коррекции,

га, п-канальный блок 3 умножителей.

Через умножители п-канального блока 3 умножителей во входной сумматор 4 поступают корректирующие сигналы, в .результате сложения которых и основ 25 ного сигнала происходит коррекция межсимвольных искажений входного ин формационного сигнала,

входной сумматор 4, формирователь 5 сигнала ошибки, блок 6 масштабирования, п цепей 7 обработки сигнала, первый и второй дополнительные регистры 8 и 9 сдвига, первый и второй дополнительные умножители 10 и 11, вычитатель 12, накап/тивающий сумматор 13, делитель 14 частоты, коррек- ционный блок 15 и задающий генератор 16, п цепей 7 обработки сигнала содержат умножители 17, сумматоры 18 и регистры 19 сдвига.

Устройство тактовой синхронизации приемника дискретной информации работает следующим образом.

Входной информационный (аналоговый) сигнал в полосе частот 0-f поступает на АЦП 1 (фиг.1), в котором вьщеляются путем стробирования мгновенные значения (отсчеты) данного сигнала с частотой 2F 4f (основные и дополнительные отсчеты). Отсчеты в АЦП 1 преобразуются в многоразрядные числа в двоичном коде,

С выхода АЦП 1 числа с частотой .2F поступают во входной регистр 2 сдвига, имеющий 2п разрядов и п отводов от них. Входной регистр 2 сдв и га, а также п-канальньй блок 3 умножителей, входной сумматор 4, формирователь 5 сигнала ошибки, блок 6 масштабирования и п цепей обработки сигнала, составляя узел коррекции, выполняют коррекцию межсимвольных искажений входного сигнала. Отводы входного регистра 2 сдвига через п-канальньй блок 3 умножителей подключены к входам 1входного сумматора 4.

.Умножители п-канального блока 3 умножителей выполняют функции аттенюаторов, изменяя уровень и знак сигналов, подаваемых во входной сумматор 4. Коэффициент передачи каждого умножителя п-канального блока 3 умножителей определяется величиной и знаком сигналов (коэффициентов), подаваемых на вторые входы п-канального

блока 3 умножителей. Коэффициент передачи одного из умножителей п-канального блока 3 умножителей (среднего) близок к 1 и является коэффициентом передачи центрального отвода,

Через него поступает во входной сумматор 4 основной сигнал. Остальные умножители п-канального блока 3 ум- .ножителей имеют коэффициенты передачи меньше 1, изменяемые в процессе автоЧерез умножители п-канального блока 3 умножителей во входной сумматор 4 поступают корректирующие сигналы, в результате сложения которых и основ- ного сигнала происходит коррекция межсимвольных искажений входного информационного сигнала,

В формирователе 5 сигнала ошибки вырабатывается сигнал ошибки е(с), который определяется из выражения

e(c,)f(t)-f(t),

где f(t) - сигнал с линейными искажениями;

f(t) - восстановленный из f (t) сигнал без искажений (с приближением). Дпя формирования коэффициентов передачи умножителей п-канального блока 3 умножителей сигнал ошибки е (t) перемножается с сигналом знака каждого отвода входного регистра 1 в умножителях 17, в результате чего вырабатываются сигналы управления в виде постоянной составляющей, величина которой пропорциональна значениям

импульсной реакции U

и„, и.

U-f, (фиг, 2а,( , б) .

С выходов умножителей 17 сигналы управления поступают на входы сумма-, торов 18, которые вместе с подклю- ченньми к их выходам регистрами 19 сдвига выполняют функции накапливающих сумматоров, усредняя сигналы с умножителей 17 и осуществляя их хранение, С выходов регистров 19 сдвига сигналы коэффициентов передачи подаются в умножители п-канального блока 3 умножителей и изменяют передаваемые с отводов входного регистра 2

312

сдвига сигналы таким образом, что на выходе входного сумматора 4 искажения уменьшаются. Процесс коррекции искажений происходит автоматически и непрерывно до подавления искажений. При этом на выходах умножителей 17 среднее значение сигналов становится близким к нулевому, и изменения коэффициентов передачи умножителей п-ка- нального блока 3 умножителей пре- кращаются.

Регулировка моментами стробирова- ния сигнала в АЦП 1 осуществляется в процессе автоматической коррекции искажений входного сигнала.

В качестве сигнала рассогласования фазы тактовых импульсов используется разность отсчетов импульсной реакции (фиг. 2а, 5,6) uU,.,, при этом значения U, и U получают- ся путем корреляции сигнала знака основных отсчетов с амплитудой и знаком дополнительных отсчетов

.K.,

-.45V..-где и,, U3...U2, -дополнительные

отсчеты входного информаци- 30

д нного сигнала; ч.

и , и . . .и -знаки основных

отсчетов. Для получения сигнала &U с выхода входного сумматора 4 сигнал ос- ионных и дополнительных отсчетов поступает на последовательно соединенные первый и второй дополнительные регистры 8 и 9 сдвига, в каждом из которых цифровой сигнал задерживает- ся на один тактовый интервал частоты 2F , в результате чего образуются три цифровых сигнала, отличающиеся сдвигом во времени на . От цифрового сигнала с выходов первого до- полнительного регистра 8 сдвига берется только знаковьш разряд и подается на вторые входы первого и второго дополнительных умножителей

10и 11. На первые входы последних подаются многоразрядные числа, причем на вход первого дополнительного умножителя 10 - отстающие, а на вход второго дополнительного умножителя

11- опережающие относительно знака. В первом и втором дополнительных умножителях перемножаются числа цифрового сигнала с сигналом знака.

Q

5

0

0 5

0

5

причем на их выходах формируются сигналы, соответствующие произведениям й„ и и и и

2 к 2к 2К-1

С ВЫХОДОВ первого и второго дополнительных умножителей 10 и 11 числа с частотой 2F поступают в вычита- тель 12, в котором определяется разность каждой пары входных чисел. С выхода вычитателя 12 цифровой сигнал подается в накапливающий сумматор 13, в котором среднее значение поступающих чисел, пропорциональное MJ,, преобразуется в частоту путем периодического переполнения его. Накапливающий сумматор 13 тактируется синхросигналом с частотой F , при этом

tT

синхросигнал выделяет из входных чисел только те, которые получаются от перемножения со знаком основных отсчетов. При переполнении накапливающего сумматора 13 формируются сигнал переполнения (импульс) и сигнал знака входных чисел, вызвавших его переполнение, при этом частота сигнала переполнения пропорциональна величине, а знак соответствует знаку

, .

Импульсы и сигнал знака переполнения подаются в коррекцнонный блок 15, выполняющий функции добавления или исключения импульсов из последовательности импульсов, поступающей от задающего генератора 16. В делителе 14 частоты из сигнала, поступающего от коррекционного блока 15, формируются последовательности импульсов с частотами F и 2F, первая из которых подается в качестве синхросигнала в накапливающий сумматор 13 и .регистры 19 сдвига, а вторая после- . довательность имупльсов с частотой 2F - в АЦП 1, первый и второй дополнительные регистры 8 и 9 сдвига и во входной регистр 2 сдвига.

Совместный процесс автоматической коррекции и регулировки тактовых отсчетов сигнала осуществляется следующим образом.

В начальный момент полученные произвольно в АЦП 1 отсчеты (фиг.25,б) .поступают через узел коррекции в узел регулировки тактовых отсчетов, включающий первый и второй дополнительные регистры 8 и 9 сдвига, первый и второй дополнительные умножители 10 и 11, вычитатель 12, накапливающий сумматор 13, делитель 14 частоты, корреккционный блок 15, задающий генератор 16. Узел регулировки тактовых отсчетов анализирует по дополнительным отсчетам входной сигнал и отрабатывает положение отсчетов таким образом, чтобы разность значений импульсной реакции на входе узла коррекции стала равной нулю, т.е. ди 0, при этом узел коррекции не успевает изменить, сигнал, так как настраивается медленнее, чем узел регулировки тактовых отсчетов. Далее узел коррекции начинает изменять (корректировать) сигнал, в результате чего изменяется значение uU и вновь узел регулировки тактовых отсчетов изменяет положение отсчетов. Процесс совместной подстройки узла коррекции и узла регулировки тактовых отсчетов продолжается до тех пор, пока импульсная реакция тракта сигнала не становится вида sinu) (фиг.2а), после чего процесс подстройки прекращается, так как управляющие сигналы узла коррекции , U.-U и узла регулировки тактовых отсчетов ста новятся равными нулю.

Таким образом, в результате того, что основные и дополнительные отсчеты, входного сигнала корректируются в процессе регулирования их временного расположения, а для регулировки их используются дополнительные отсчеты, не влияющие на работу узла коррекции, положение отсчетов устанавливается оптимально при различных линейных искажениях входного сигнала:

Формула изобретения

1 . Устройство тактовой синхронизации приемника дискретной информации, содержащее последовательно соединенные задающий генератор, коррек- ционный блок и делитель частоты, последовательно соединенные входной сумматор, формирователь сигнала ошибки и блок масштабирования, последовательно соединенные аналого-цифровой преобразователь и входной ре-- гистр сдвига, а также вычитатель, п-канальный блок умножителей и п цепей обработки сигнала, состоящих из последовательно соединенных умножию 5 20 25

Q

5

Q

5

0

теля, сумматора и регистра сдвига, выходы которого- подсоединены к вторым входам сумматора, причем выходы блока масштабирования подсоединены к первым входам умножителей п цепей обработки сигналов, выходы входного регистра сдвига подсоединены к соот-- ветствующим вторым входам умножителей п цепей обработки сигнала и входам п-канального блока умножителей, вторые входы которого подключены к выходам регистров сдвига соответствующих п цепей обработки сигнала, а выходы п-канального блока умножителей подсоединены к входам входного сумматора, выход делителя частоты подсоединен к тактовым входам регистров сдвига п цепей обработки сигнала, причем вход аналого-цифрового преобразователя является входом устройства, отличающееся тем, что, с целью повышения точности синхронизации, в него введены последовательно соединенные первый и второй дополнительные регистры сдвига и первый дополнительный умножитель, а также второй дополнительный умножитель и накапливающий сумматор, при этом входы первого дополнительного р егистра сдвига и второго дополнительного умножителя подключены к выходам входного сумматора, выход знакового разряда первого дополнительного регистра сдвига подсоединен к вторым входам первого и второго дополнительных умножителей, выходы которых подсоединены через последовательно соединенные вычитатель и накапливающий сумматор к управляющему входу коррекционного блока, причем выход делителя частоты подсоединен к тактовому входу накапливающего суМ- матора, а дополнительный выход делителя частоты подсоединен к тактовым входам аналого-цифрового преобразователя, входного регистра сдвига и первого и второго дополнительных регистров сдвига.

2. Устройство по П.1, отличающееся тем, что входной ре гистр сдвига содержит 2п разрядов, причем выходы нечетных разрядов являются выходами входного регистра сдвига.

а

fPu2.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный цифровой корректор | 1975 |

|

SU519869A1 |

| Нелинейный корректор многолучевого сигнала | 1984 |

|

SU1197096A2 |

| Цифровой нелинейный корректор сигнала | 1982 |

|

SU1075423A1 |

| Адаптивный корректор фазомодули-рованных сигналов | 1974 |

|

SU508944A1 |

| Способ коррекции межсимвольной интерференции и устройство для его осуществления | 1985 |

|

SU1300646A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Адаптивный цифровой корректор | 1987 |

|

SU1506558A2 |

| Цифровой фильтр | 1988 |

|

SU1566471A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2701059C1 |

| ЦИФРОВОЙ КОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННОГО СИГНАЛА С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2656577C1 |

Изобретение относится к электросвязи и обеспечивает повьшение точности синхронизации. Устройство содержит АЦП 1, регистры 2, 8, 9 сдвига (РС), п-канальный блок 3 умножителей (БУ), входной сумматор (ВС) 4, формирователь 5 сигнала ошибки, .блок 6 масштабирования, п цепей 7 обработки сигнала, дополнительные умножителя 10 и 11, вычитатель 12, накапливающий сумматор 13, делитель 14 частоты, коррекционный блок 15 и задающий генератор 16. PC 2, БУ 3, ВС 4, формирователь 5 сигнала ошибки, блок 6 масштабирования и п цепей обработки сигнала образуют узел коррекции и выполняют коррекцию межсимвольных искажений входного сигнала. Умножители БУ 3 выполняют функции аттенюаторов, изменяя уровень и знак сигналов, подаваемых в ВС 4. Через умножители БУ 3 в ВС 4 поступают корректирующие сигналы, в результате сложения кото- рых с основным сигналом просиходит коррекция межсимвольных искажений входного информационного сигнала. 1 3.п. ф-лы, 2 ил. СЛ ,ff 1

| Способ дискретной автоподстройки фазы тактовых импульсов и устройство для его осуществления | 1976 |

|

SU598260A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент США № 4146840, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-15—Публикация

1985-01-04—Подача