fO

15

20

Изобретение относится к вычислительной технике и может быть использовано в вычислительных комплексах для обмена информацией между ЭВМ и микропроцессорными внешними устройствами.

Целью изобретения является расширение класса решаемых задач за счет обеспечения возможности обмена группы микропроцессорных внешних устройств с ЭВМ.

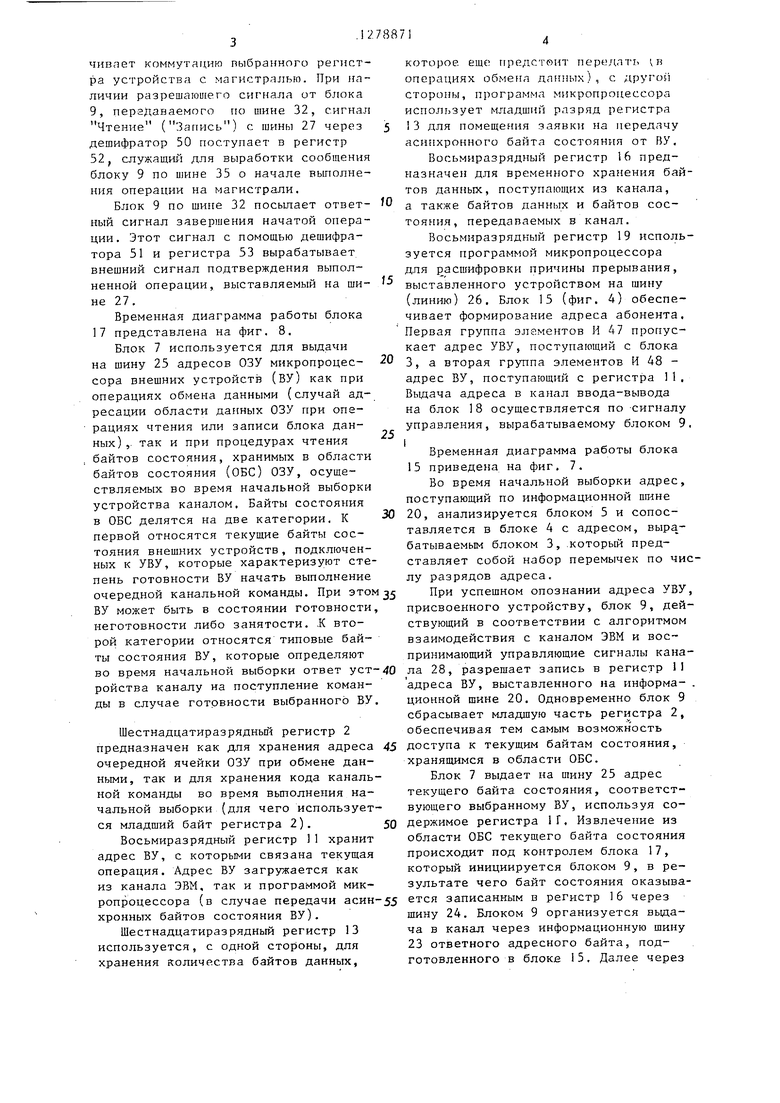

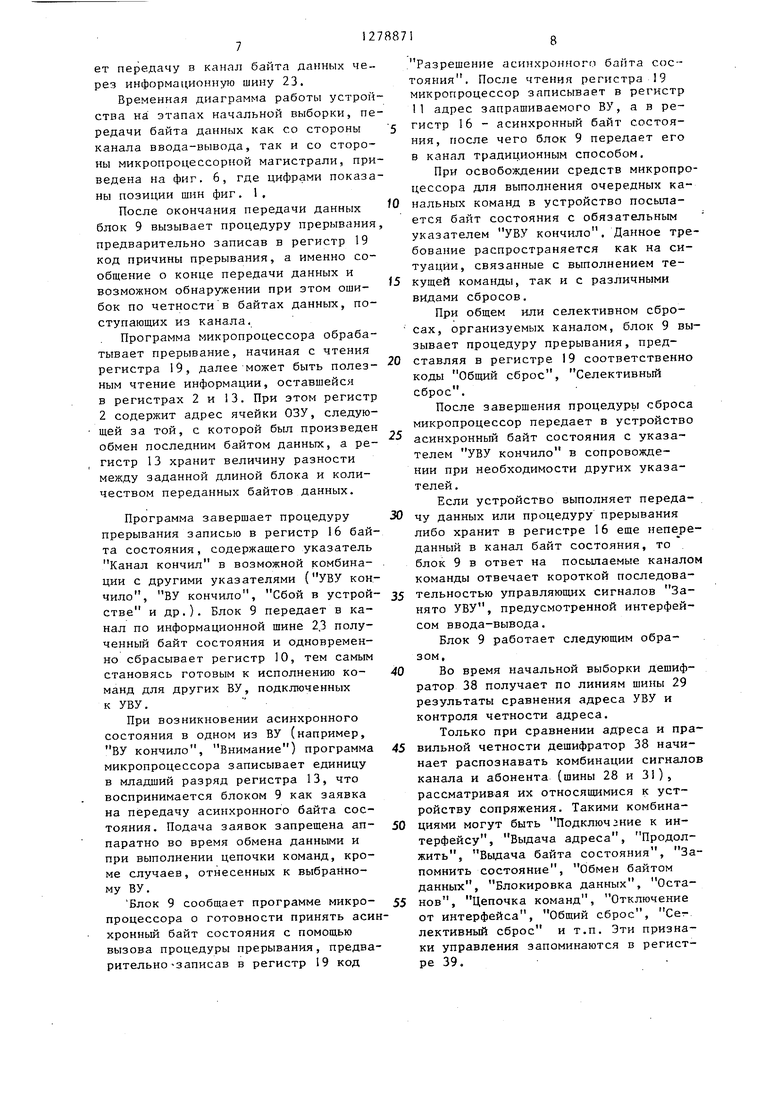

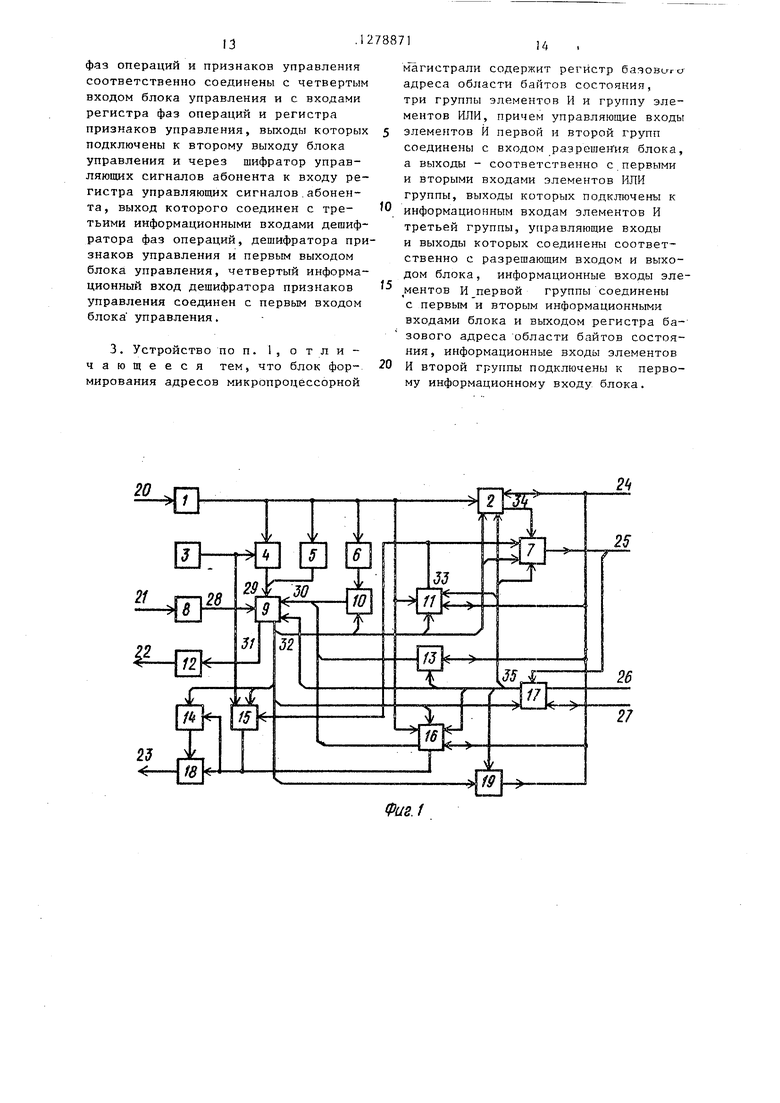

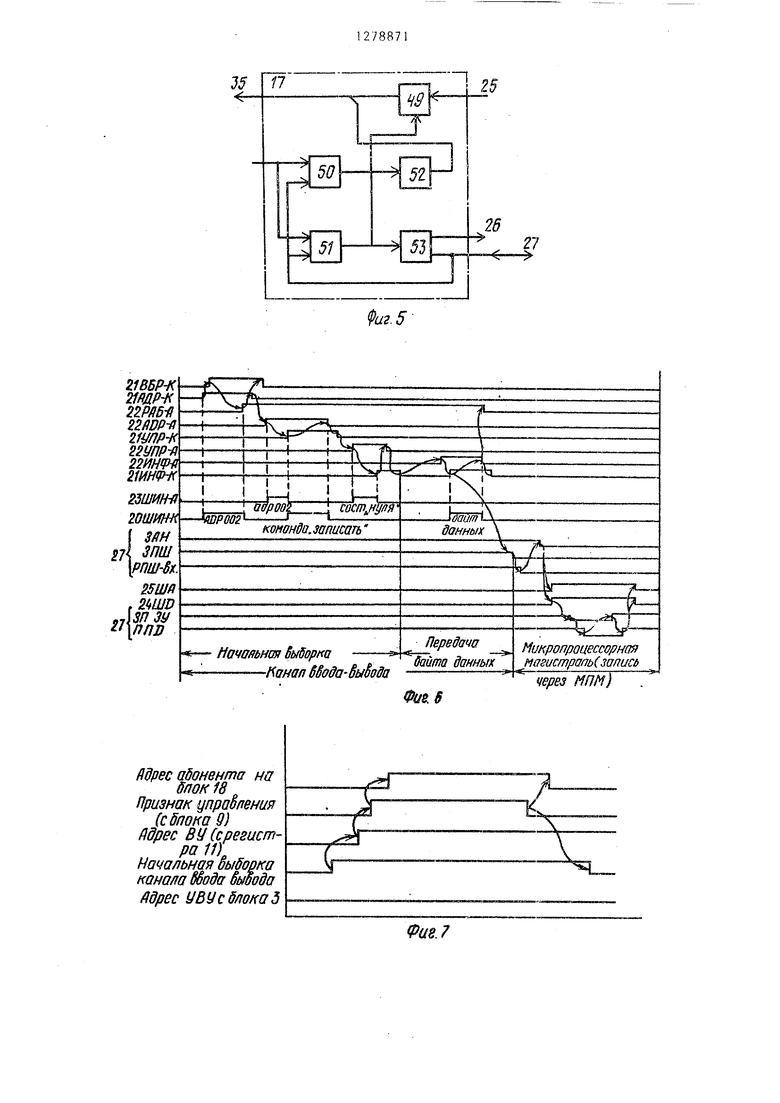

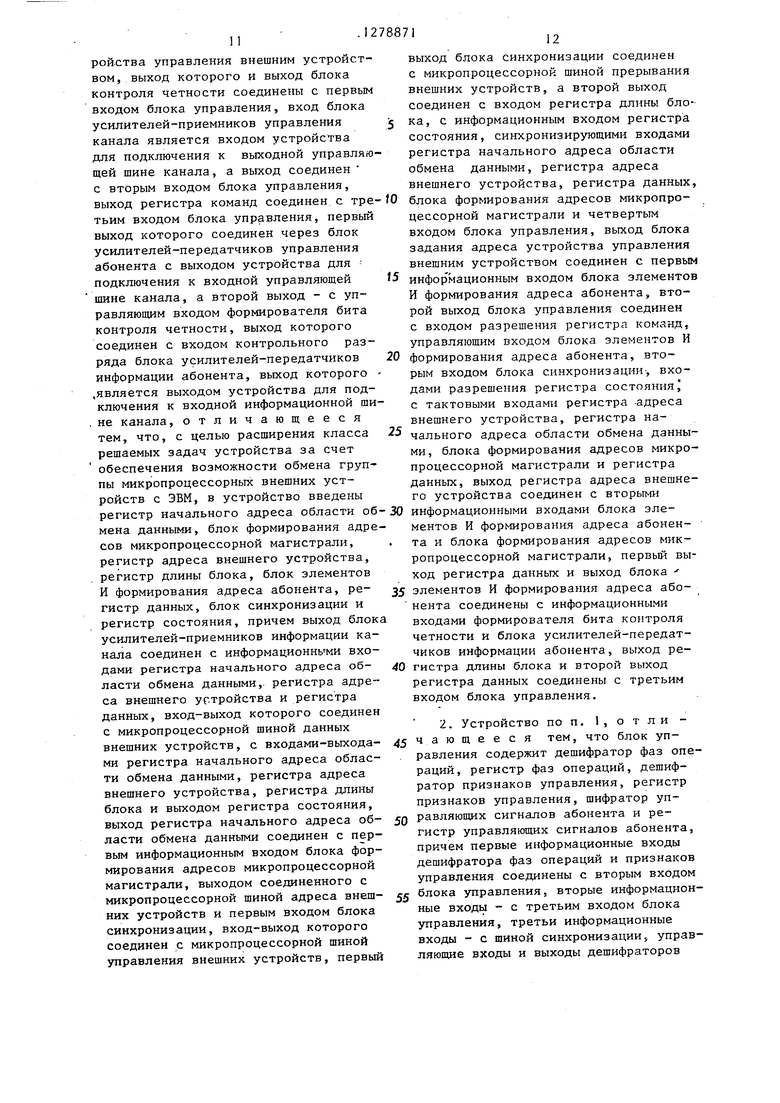

На фиг. 1 представлена блок-схема устройства; на фиг. 2-5 г функциональные схемы блока управления, блока формирования адресов микропроцессорной магистрали, блока элементов И формирования адреса абонента и блока синхронизации; на фиг, 6 - временная диаграмма работы устройства на этапе начальной выборки; на Фиг. 7 - ; , временная диаграмма работы блока элементов И формирования адреса абонентов; на фиг. 8 - временная диаграмма

работы блока синхронизации.

25

Устройство (фиг. 1) содержит блок 1 усилителей-приемников информации канала, регистр 2 начального адреса области обмена данными, блок 3 задания адреса устройства управления 30 внешним устройством (УВУ), блок 4 сравнения адреса устройства управления внешним устройством, блок 5 контроля четности, дешифратор 6 команд, блок 7 формирования адресов микропроцессорной магистрали, блок 8 усилителей-приемников управления канала, блок 9 управления,регистр 10

. команд, регистр П. адреса внешнего устройства, блок 12 усилителей-передатчиков управления абонента, регистр 13 длины блока, формирователь 14 бита контроля четности, блок 15 элементов И нормирования адреса абонента, регистр 16 данных, блок 17 синхрониза- 45 ции, блок 18 усилителей-передатчиков информации абонента, регистр 19 состояния , выходные информационную 20 и управляющую 21 шины канала, входные управляющую 22 и информационную 50

. 23 шины канала, микропроцессорную шину 24 данных, микропроцессорную шину 25 адреса, микропроцессорную шину 26 прерывания, микропроцессорную шину

35

40

10, 13 и 16, тину 31 управляющих сигналов абонента, внутреннюю управляющую шину 32, выходную шину 33 адреса внешнего устройства, выходную шину 34 начального адреса области обмена данными и шину 35 синхронизации микропроцессорной магистрали.

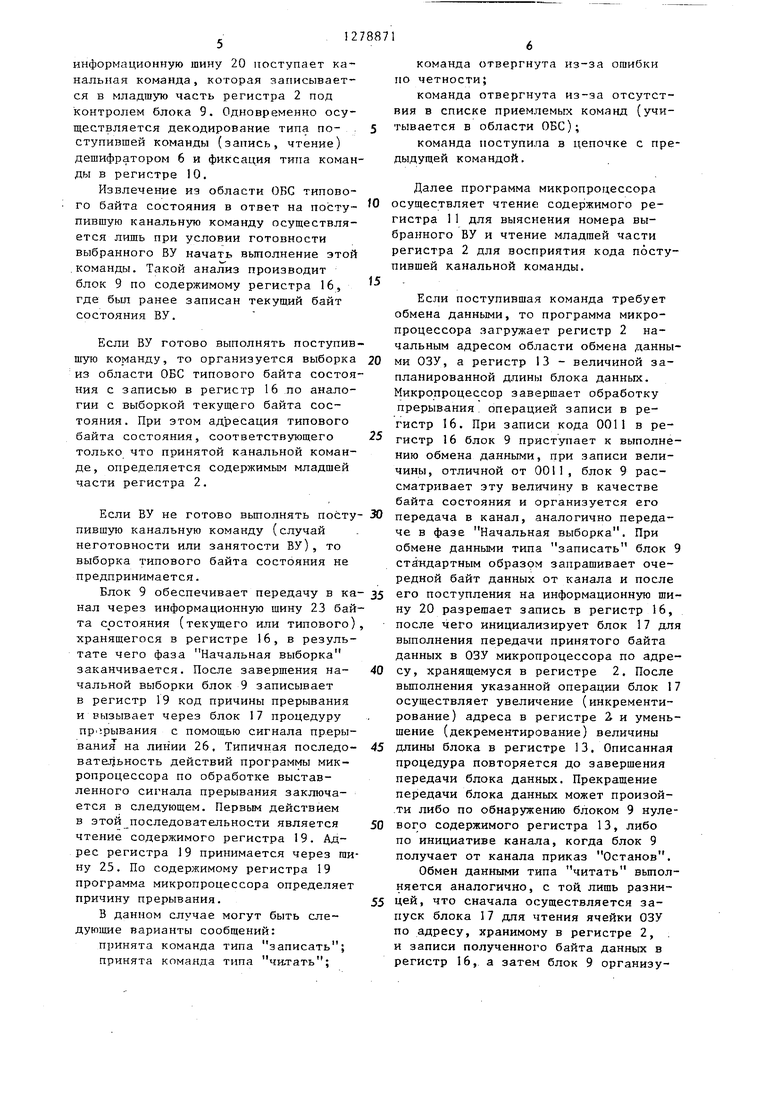

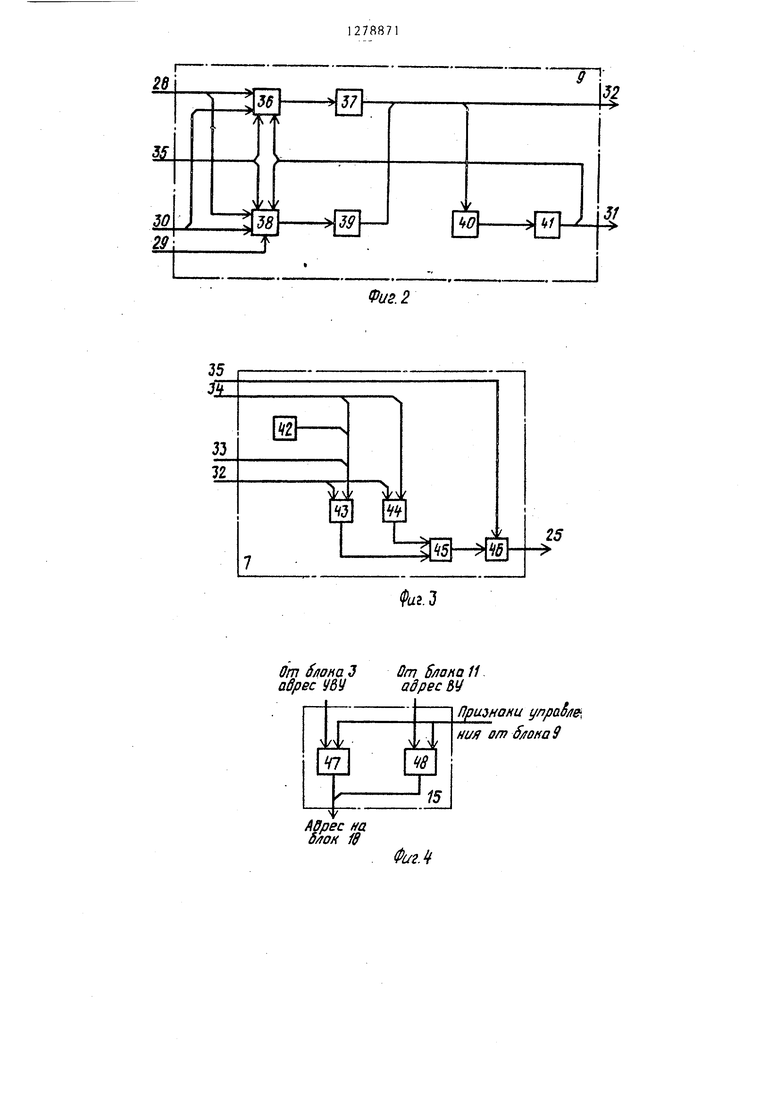

Блок 9 управления (фиг. 2) содержит дешифратор 36 фаз операций, регистр 37 фаз операций, дешифратор 38 признаков управления, регистр 39 признаков управления, шифратор 40 управляющих сигналов абонента, регистр 41 управляющих сигналов абонента.

Блок 7 формирования адресов микропроцессорной магистрали (фиг. 3) содержит регистр 42 базового адреса области байтов состояния (ОБС), группы элементов И 43 и 44, группу элементов ИЛИ 45, группу элементов И 46.

Блок 15 элементов И формирования адреса абонента (фиг. 4) содб:ржит группы элементов И 47 и 48.

Блок 17 синхронизации (фиг. 5) содержит-дешифратор 49 адреса, дешиф ратор 50 состояния, дешифратор 51 фа регистр 52 состояния микропроцессорной магистрали и регистр 53 фаз.

Устройство работает следующим образом.

Регистры 2,11,13,16 и 19 непосред ственно взаимодействуют с двунаправленной шиной 24 микропроцессорной магистрали, так что микропроцессор имеет возможность как записывать,так и считывать данные этих регистров всо ответствии с присвоенными им адресами Для управления процессами обмена информации через шины 25, 27 и шину 26 прерывания служит блок 17 синхронизации. Блок 17 анализирует обращения к названным регистрам устройства путем анализа адресов регистров на шине 25, сопровождаемых сигналами.на шине 27 в соответствии с алгоритмом работы.

Пример алгоритма работы блока 17 следующий.

Сигнал выполнения операции Чтение (Запись), выставленный на шине 27, распознается дешифратором 51, с которого управляюш.ее воздействие направляется к дешифратору 49, чем 27 управления внешних устройств, ши- 55 обеспечивается разрешение расшиф- ну 28 управляющих сигналов канала, ровки адреса на шине 25. Выставленный на шине 25 адрес распознается дешифратором 49, после чего активилинии 29 сравнения адреса управления внешним устройством и контроля четности, выходную шину 30 регистров

зируется линия шины 35, что обеспе

5

0

5

0

5 0

5

0

10, 13 и 16, тину 31 управляющих сигналов абонента, внутреннюю управляющую шину 32, выходную шину 33 адреса внешнего устройства, выходную шину 34 начального адреса области обмена данными и шину 35 синхронизации микропроцессорной магистрали.

Блок 9 управления (фиг. 2) содержит дешифратор 36 фаз операций, регистр 37 фаз операций, дешифратор 38 признаков управления, регистр 39 при- знаков управления, шифратор 40 управляющих сигналов абонента, регистр 41 управляющих сигналов абонента.

Блок 7 формирования адресов микропроцессорной магистрали (фиг. 3) содержит регистр 42 базового адреса области байтов состояния (ОБС), группы элементов И 43 и 44, группу элементов ИЛИ 45, группу элементов И 46.

Блок 15 элементов И формирования адреса абонента (фиг. 4) содб:ржит группы элементов И 47 и 48.

Блок 17 синхронизации (фиг. 5) содержит-дешифратор 49 адреса, дешифратор 50 состояния, дешифратор 51 фаз, регистр 52 состояния микропроцессорной магистрали и регистр 53 фаз.

Устройство работает следующим образом.

Регистры 2,11,13,16 и 19 непосредственно взаимодействуют с двунаправленной шиной 24 микропроцессорной магистрали, так что микропроцессор имеет возможность как записывать,так и считывать данные этих регистров всо- ответствии с присвоенными им адресами. Для управления процессами обмена информации через шины 25, 27 и шину 26 прерывания служит блок 17 синхронизации. Блок 17 анализирует обращения к названным регистрам устройства путем анализа адресов регистров на шине 25, сопровождаемых сигналами.на шине 27 в соответствии с алгоритмом работы.

Пример алгоритма работы блока 17 следующий.

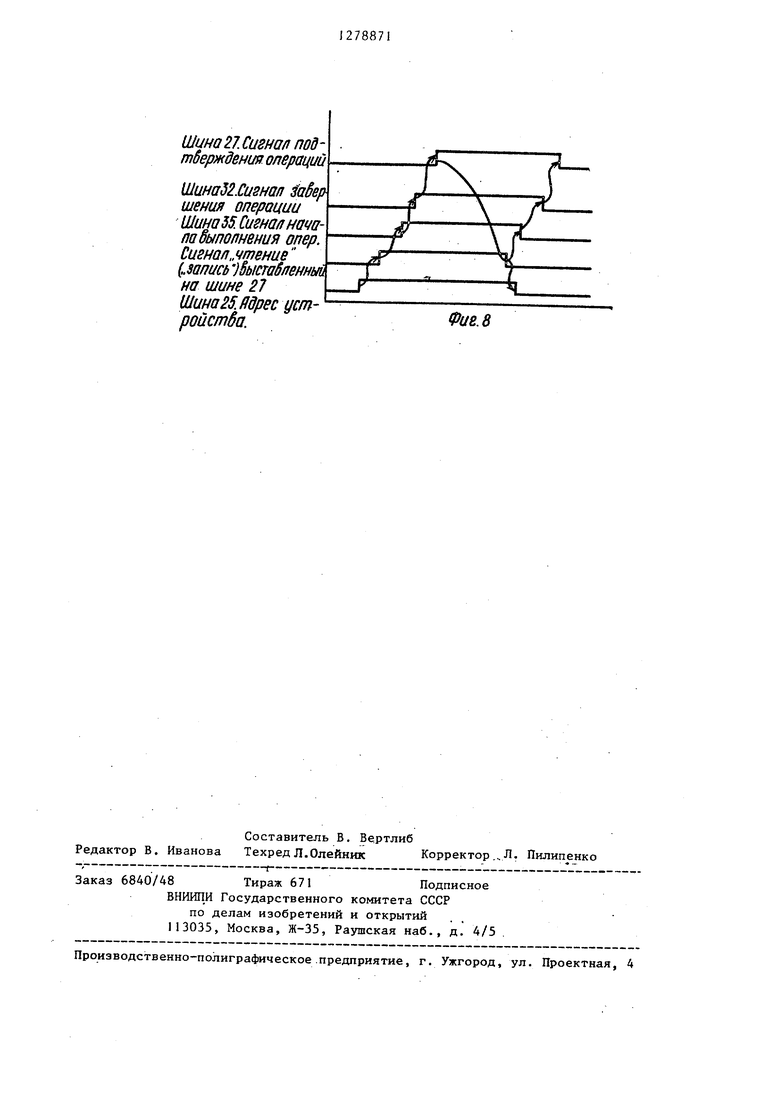

Сигнал выполнения операции Чтение (Запись), выставленный на шизируется линия шины 35, что обеспечнвает коммутацию выбранного регистра устройства с магистралью. При наличии разрешающего сигнала от блока 9, перэданаемого по шине 32, сигнал Чтение (Занись) с шины 27 через дешифратор 50 поступает в регистр 52, служащий для выработки сообщения блоку 9 по шине 35 о начале выполнения операции на магистрали.

Блок 9 по шине 32 посылает ответный сигнал завершения начатой операции. Этот сигнал с помощью дешифратора 51 и регистра 53 вырабатывает внешний сигнал подтверждения выполненной операции, выставляемый на шине 27.

Временная диаграмма работы блока 17 представлена на фиг. 8.

Блок 7 используется для выдачи на шину 25 адресов ОЗУ микропроцессора внешних устройств (ВУ) как при операциях обмена данными (случай адресации области данных ОЗУ при операциях чтения или записи блока данных) ,, так и при процедурах чтения байтов состояния, хранимых в области байтов состояния (ОБС) ОЗУ, осуществляемых во время начальной выборки устройства каналом. Байты состояния в ОБС делятся на две категории, К первой относятся текущие байты состояния внешних устройств, подключенных к УВУ, которые характеризуют степень готовности ВУ начать выполнение очередной канальной команды. При это ВУ может быть в состоянии готовности неготовности либо занятости. .К второй категории относятся типовые байты состояния ВУ, которые определяют во время начальной выборки ответ устройства каналу на поступление команды в случае готовности выбранного ВУ

Шестнадцатиразрядньш регистр 2 предназначен как для хранения адреса очередной ячейки ОЗУ при обмене данными, так и для хранения кода канальной команды во время вьтолнения начальной выборки (для чего используется младший байт регистра 2).

Восьмиразрядный регистр 11 хранит адрес ВУ, с которыми связана текущая операция. Адрес ВУ загружается как из канала ЭВМ, так и программой микропроцессора (в случае передачи асинхронных байтов состояния ВУ).

Шестнадцатиразрядный регистр 13 используется, с одрюй стороны, для хранения количества байтов данных.

5

которое еще предстоит передать и операциях обмена данных), с другоГ стороны, программа микропроцессора испол1)3ует младший разряд регистра 5 13 для помещения заявки на передачу асинхронного байта состояния от f$y. Восьмиразрядный регистр 16 предназначен для временного хранения байтов данных, поступающих из канала,

а также байтов данных и байтов состояния, передаваемых в канал.

Восьмиразрядный регистр 19 используется программой микропроцессора для расшифровки причины прерывания, выставленного устройством на шину (линию) 26. Блок 15 (фиг. 4) обеспечивает формирование адреса абонента. Первая группа элементов И 47 пропускает адрес УВУ5 поступающий с блока

3, а вторая группа элементов И 48 - адрес ВУ, поступающий с регистра 11. Выдача адреса в канал ввода-вывода на блок 18 осуществляется по сигналу управления, вырабатываемому блоком 9.

Временная диаграмма работы блока 15 приведена на фиг. 7.

Во время начальной выборки адрес, поступающий по информационной шине

0 20, анализируется блоком 5 и сопоставляется в блоке 4 с адресом, вырабатываемым блоком 3, который представляет собой набор перемычек по числу разрядов адреса.

5 При успешном опознании адреса УВУ, присвоенного устройству, блок 9, действующий в соответствии с алгоритмом взаимодействия с каналом ЭВМ и воспринимающий управляющие сигналы кана0 ла 28, разрешает запись в регистр И адреса ВУ, выставленного на информа- . ционной шине 20. Одновременно блок 9 сбрасывает младшую часть регистра 2, обеспечивая тем самым возможность

5 доступа к текущим байтам состояния, хранящимся в области ОБС.

Блок 7 выдает на шину 25 адрес текущего байта состояния, соответствующего выбранному ВУ, используя со0 держимое регистра 1Г. Извлечение из области ОБС текущего байта состояния происходит под контролем блока 17, который инициируется блоком 9, в результате чего байт состояния оказыва5 ется записанным в регистр 16 через шину 24. Блоком 9 организуется выдача в канал через информационную шину 23 ответного адресного байта, подготовленного в блоке 15, Далее через

информационную шину 20 поступает канальная команда, которая записывается в младшую часть регистра 2 под контролем блока 9. Одновременно осуществляется декодирование типа по- ступившей команды (запись, чтение) дешифратором 6 и фиксация типа команды в регистре 10.

Извлечение из области ОБО типового байта состояния в ответ на посту- пившую канальную команду осуществляется лишь при условии готовности выбранного ВУ начать вьтолнение этой .команды. Такой анализ производит блок 9 по содержимому регистра 16, где бьш ранее записан текущий байт состояния ВУ.

Если ВУ готово выполнять поступившую ко манду, то организуется выборка из области ОБС типового байта состояния с записью в регистр 16 по аналогии с выборкой текущего байта состояния. При этом адресация типового байта состояния, соответствующего только что принятой канальной команде, определяется содержимым младшей части регистра 2.

Если ВУ не готово выполнять посту пившую канальную команду (случай неготовности или занятости БУ), то выборка типового байта состояния не предпринимается.

Блок 9 обеспечивает передачу в ка нал через информационную шину 23 байта состояния (текущего или типового) хранящегося в регистре 16, в результате чего фаза Начальная выборка заканчивается. После завершения на- чальной выборки блок 9 записывает в регистр 19 код причины прерывания и вызывает через блок 17 процедуру пр рывания с помощью сигнала прерывания на линии 26. Типичная последо- вате4ьность действий программы микропроцессора по обработке выставленного сигнала прерывания заключается в следующем. Первым действием в этой последовательности является чтение содержимого регистра 19. Адрес регистра 19 принимается через гаи ну 25. По содержимому регистра 19 программа микропроцессора определяет причину прерывания.

В данном случае могут быть следующие варианты сообщений:

принята команда типа записать ;

принята команда типа чи,

команда отвергнута из-за ошибки по четности;

команда отвергнута из-за отсутствия в списке приемлемых команд (учитывается в области ОБС);

команда поступила в цепочке с предыдущей командой.

Далее программа микропроцессора осуществляет чтение содержимого регистра 11 для выяснения номера выбранного ВУ и чтение младшей части регистра 2 для восприятия кода поступившей канальной команды.

Если поступившая команда требует обмена данными, то программа микропроцессора загружает регистр 2 начальным адресом области обмена данными ОЗУ, а регистр 13 - величиной запланированной длины блока данных. Микропроцессор завершает обработку прерывания, операцией записи в регистр 16. При записи кода ООП в регистр 16 блок 9 приступает к выполнению обмена данными, цри записи величины, отличной от ООП, блок 9 рассматривает эту величину в качестве байта состояния и организуется его передача в канал, аналогично передаче в фазе Начальная выборка. При обмене данными типа записать блок 9 стандартным образом запрашивает очередной байт данных от канала и после его поступления на информационную шину 20 разрешает запись в регистр 16, после чего инициализирует блок 17 для выполнения передачи принятого байта данных в ОЗУ микропроцессора по адресу, хранящемуся в регистре 2. После вьшолнения указанной операции блок 17 осуществляет увеличение (инкременти- рование) адреса в регистре 2 и уменьшение (декрементирование) величины длины блока в регистре 13, Описанная процедура повторяется до завершения передачи блока данных. Прекращение передачи блока данных может произой- .ти либо по обнаружению блоком 9 нулевого содержимого регистра 13, либо по инициативе канала, когда блок 9 получает от канала приказ Останов.

Обмен данными типа читать вьтол- няется аналогично, с той лишь разницей, что сначала осуществляется запуск блока I7 дпя чтения ячейки ОЗУ по адресу, хранимому в регистре 2, . и записи полученного байта данных в регистр 16, а затем блок 9 организует передачу в канал байта данных через информационную шину 23.

Временная диаграмма работы устройства на этапах начальной выборки, передачи байта данных как со стороны канала ввода-вывода, так и со стороны микропроцессорной магистрали, приведена на фиг. 6, где цифрами показаны позиции шин фиг. 1 ,

После окончания передачи данных блок 9 вызывает процедуру прерывания предварительно записав в регистр 19 код причины прерывания, а именно сообщение о конце передачи данных и возможном обнаружении при этом ошибок по четности в байтах данных, поступающих из канала.

Программа микропроцессора обрабатывает прерывание, начиная с чтения регистра 19, далее может быть полезным чтение информации, оставшейся в регистрах 2 и 13. При этом регистр 2 содержит адрес ячейки ОЗУ, следующей за той, с которой был произведен обмен последним байтом данных, а регистр 13 хранит величину разности между заданной длиной блока и количеством переданных байтов данных.

Программа завершает процедуру прерывания записью в регистр 16 байта состояния, содержащего указатель Канал кончил в возможной комбина- ции с другими указателями (УВУ кончило, ВУ кончило, Сбой в устрой- стве и др.). Блок 9 передает в канал по информационной шине 2,3 полученный байт состояния и одновременно сбрасывает регистр 10, тем самым становясь готовым к исполнению команд для других ВУ, подключенных к УВУ.

При возникновении асинхронного состояния в одном из ВУ (например, ВУ кончило, Внимание) программа микропроцессора записывает единицу в младший разряд регистра 13, что воспринимается блоком 9 как заявка на передачу асинхронного байта состояния. Подача заявок запрещена ап- паратно во время обмена данными и при выполнении цепочки команд, кроме случаев, отнесенных к выбранному ВУ.

Блок 9 сообщает программе микропроцессора о готовности принять асинхронный байт состояния с помощью вызова процедуры прерывания, предварительно -записав в регистр 19 код

Разрешение асинхронного байта состояния. После чтения регистра 9 микропроцессор записывает в регистр 11 адрес запрашиваемого ВУ, а в регистр 16 - асинхронный байт состояния, после чего блок 9 передает его в канал традиционным способом.

При освобождении средств микропроцессора для выполнения очередных канальных команд в устройство посылается байт состояния с обязательным указателем УВУ кончило. Данное требование распространяется как на ситуации, связанные с выполнением те- кущей команды, так и с различными видами сбросов.

При общем или селективном сбро- сах, организуемых каналом, блок 9 вы0

0

0 5

зывает процедуру прерывания, представляя в регистре 19 соответственно коды Общий сброс, Селективный сброс.

После завершения процедуры сброса микропроцессор передает в устройство асинхронный байт состояния с указателем УВУ кончило в сопровождении при необходимости других указателей.

Если устройство выполняет передачу данных или процедуру прерывания либо хранит в регистре 16 еще непереданный в канал байт состояния, то блок 9 в ответ на посылаемые каналом команды отвечает короткой последовательностью управляющих сигналов Занято УВУ, предусмотренной интерфейсом ввода-вывода.

Блок 9 работает следующим образом,

Во время начальной выборки дешифратор 38 получает по линиям шины 29 результаты сравнения адреса УВУ и контроля четности адреса.

Только при сравнении адреса и пра- 5 вильной четности дешифратор 38 начинает распознавать комбинации сигналов канала и абонента (шины 28 и 31), рассматривая их относящимися к устройству сопряжения. Такими комбина- 0 циями могут быть Подключение к интерфейсу, Выдача адреса, Продолжить, Выдача байта состояния, Запомнить состояние, Обмен байтом данных, Блокировка данных, Останов, Цепочка команд, Отключение от интерфейса, Общий сброс, Сет- лективный сброс и т.п. Эти признаки управления запоминаются в регистре 39.

5

Дешифратор 36 распознает такие фазы операций, как Начальная выборка, Обмен блоком данных, Разрешение асинхронных байтов состояния, Процедура прерывания, Хранение нереа- лизованного байта состояния, Инициализация блока синхронизации. Фазы операций фиксируются в регистре 37, Шина 35, управляющая работой дешифраторов 36 и 38, обеспечивает упорядочение процедур, вьшолняемых устройством сопряжения совместно с каналом и магистралью.

Шина 30 обеспечивает блок 9 информацией о направлении обмена данными, о необходимости выборки типового байта состояния, о заявке на передачу асинхронного байта состояния, о завершении обмена блоком данных.

Совокупность сигналов абонентаJ определяемая стандартом и выдаваемая в канал по шине 31, вырабатывается шифратором АО в зависимости от теку- ш:ей фазы операции и установленных признаков управления и фиксируется в регистре 41. Совокупность сигналов на шине 32, представляющих фазы операций и признаки управления, используется для координации работы основных блоков устройства. Блок 7 работает следующим образом В зависимости от текущей фазы управления, передаваемой по шине 32, адрес абонента формируется на элементах И 43 и 44 и далее через эле- менты ИЛИ 45 и И 46 поступает на шин 25 при наличии сигнала Выставить адрес, передаваемого по шине 35.

При наличии фазы операции Обмен блоком данных адрес формируется на элементах И 44 и определяется содержимым регистра 2, к которому блок 7 подключен через шину 34. В данном случае регистр 2 хранит адрес облас- ти обмена данными.

При наличии фазы Начальная выборка адрес формируется на элементах И 43 из трех компонент/ Младшие разряды определяются содержимым младшей половины регистра 2. На первом этапе начальной выборки внешнего устройства младшая часть регистра 2 содержит код ООН, обеспечивая тем самым доступ к текущим байтам состояния ВУ хранимым в области ОБС с адресами типа ХХООН. На втором этапе начальной выборки младшая часть регистра 2 хранит код поступившей канальной коман5

5

0 5

0 5

ды, обеспечивая доступ к типовым байтам состояния, соответствующим принятой команде.

Старшие, разряды адреса разбиваются на два поля с плавающей границей между ними - в зависимости от числа подключенных ВУ.

Поле со старшими разрядами определяется содержимым регистра 42, который представляет собой набор перемычек (максимальное количество - восемь , для случая подключения единственного внешнего устройства). Это поле определяет расположение области ОБС в адресном пространстве ОЗУ микропроцессора .

Второе поле определяется номером ВУ, храняпшмся в регистре II, который подключен к блоку 7 через шину 33, Длина этого поля зарисит от коли чества подключенных ВУ. Фиксированному значению данного поля соответствует совокупность ячеек области ОБС для выбранного адреса внешнего устройства.

Формула изобретения

1. Устройство для сопряжения микропроцессорных внешних устройств с каналом ввода-вывода ЭВМ, содержащее |блок усилителей-приемников информации канала, блок задания адреса устройства управления внешним устройством, блок сравнения адреса устройства управления внешним устройством, блок контроля четности, дешифратор команд, блок усилителей-приемников управления канала, блок управления, регистр команд, блок усилителей-передатчиков управления абонента, формирователь бита контроля четйости, блок усилителей-передатчиков информации абонента, причем вход блока уси- лителей-приемников информации канала является входом устройства для подключения к выходной информационной шине канала, а выход соединен с первым информационным входом блока сравнения адреса устройства управления внешним устройством, входами блока контроля четности и дешифратора ко- м.анд, эыход которого соединен с информационным входом регистра команд, выход блока задания адреса устройства управления внешним устройством соединен с вторым информационным входом блока сравнения адреса устройства управления внешним устройством, выход которого и выход блока контроля четности соединены с первым входом блока управления, вход блока усилителей-приемников управления канала является входом устройства для подключения к выходной управляющей шине канала, а выход соединен с вторым входом блока управления,

выход регистра команд соединен с тре-tO блока формирования адресов микропро20

тьим входом блока управления, первый выход которого соединен через блок усилителей-передатчиков управления абонента с выходом устройства для подключения к входной управляющей шине канала, а второй выход - с управляющим входом формирователя бита контроля четности, выход которого соединен с входом контрольного разряда блока усилителей-передатчиков информации абонента, выход которого .является выходом устройства для подключения к входной информационной ши, не канала, отличающееся тем, что, с целью расширения класса 25 решаемых задач устройства за счет обеспечения возможности обмена группы микропроцессорных внешних устройств с ЭВМ, в устройство введены регистр начального адреса области об- 30 информационными входами блока эле- мена данными, блок формирования адре- ментов И формирования адреса абоненцессорнои магистрали и четвертым входом блока управления, выход блока задания адреса устройства управления внешним устройством соединен с первы 5 информационным входом блока элементо И формирования адреса абонента, второй выход блока управления соединен с входом разрешения регистра команд, управляющим входом блока элементов И формирования адреса абонента, вторым входом блока синхронизации-, входами разрешения регистра состоянияJ с тактовыми входами регистра -адреса внешнего устройства, регистра начального адреса области обмена данны ми, блока формирования адресов микро процессорной магистрали и регистра данных, выход регистра адреса внешне го устройства соединен с вторыми

сов микропроцессорной магистрали, регистр адреса внешнего устройства, регистр длины блока, блок элементов И формирования адреса абонента, регистр данных, блок синхронизации и регистр состояния, причем выход блок усилителей-приемников информации канала соединен с информационными входами регистра начального адреса области обмена данными, регистра адреса внешнего устройства и регистра данных, вход-выход которого соединен с микропроцессорной шиной данных внешних устройств, с входами-выходами регистра начального адреса области обмена данными, регистра адреса внешнего устройства, регистра длины блока и выходом регистра состояния, выход регистра начального адреса области обмена данными соединен с первым информационным входом блока формирования адресов микропроцессорной магистрали, выходом соединенного с микропроцессорной шиной адреса внешних устройств и первым входом блока синхронизации, вход-выход которого соединен с микропроцессорной шиной управления внешних устройств, первый

выход блока синхронизации соединен с микропроцессорной шиной прерывания внешних устройств, а второй выход соединен с входом регистра длины блока, с информационным входом регистра состояния, синхронизирующими входами регистра начального адреса области обмена данными, регистра адреса внешнего устройства, регистра данных.

нформационными входами блока эле- ентов И формирования адреса абоненцессорнои магистрали и четвертым входом блока управления, выход блока задания адреса устройства управления внешним устройством соединен с первым информационным входом блока элементов И формирования адреса абонента, второй выход блока управления соединен с входом разрешения регистра команд, управляющим входом блока элементов И формирования адреса абонента, вторым входом блока синхронизации-, входами разрешения регистра состоянияJ с тактовыми входами регистра -адреса внешнего устройства, регистра начального адреса области обмена данными, блока формирования адресов микропроцессорной магистрали и регистра анных, выход регистра адреса внешнего устройства соединен с вторыми

та и блока формирования адресов микропроцессорной магистрали, первый выход регистра данных и выход блока

35 элементов И формирования адреса абонента соединены с информационными входами формирователя бита контроля четности и блока усилителей-передатчиков информации абонента, выход ре40 гистра длины блока и второй выход регистра данных соединены с третьим входом блока управления.

45

50

2. Устройство по п. 1, о т ли - чающееся тем, что блок управления содержит дешифратор фаз операций, регистр фаз операций, дешифратор признаков управления, регистр признаков управления, шифратор управляющих сигналов абонента и регистр управляющих сигналов абонента, причем первые информационные входы дешифратора фаз операций и признаков управления соединены с вторым входом блока управления, вторые информационные входы - с третьим входом блока управления, третьи информационные входы - с шиной синхронизации, управляющие входы и выходы дешифраторов

фаз операций и признаков управления соответственно соединены с четвертым входом блока управления и с входами регистра фаз операций и регистра признаков управления, выходы которых подключены к второму выходу блока управления и через шифратор управляющих сигналов абонента к входу регистра управляющих сигналов.абонента , выход которого соединен с тре- тьими информационными входами дешифратора фаз операций, дешифратора признаков управления и первым выходом блока управления, четвертый информационный вход дешифратора признаков управления соединен с первым входом блока управления.

3. Устройство по п. 1, о т л и - чающееся тем, что блок фор- мирования адресов микропроцессорной

магистрали содержит регистр баяовигсг адреса области байтов состояния, три группы элементов И и группу элементов ИЛИ, причем управляющие входы элементов И первой и второй групп соединены с входом раэрешен ия блока, а выходы - соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых подключены к информационным входам элементов И третьей группы, управляющие входы и выходы которых соединены соответственно с разрешающим входом и выходом блока, информационные входы эле ментов И первой группы соединены с первым и вторым информационными входами блока и выходом регистра базового адреса области байтов состояния , информационные входы элементов И второй группы подключены к первому информационному входу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с внешними устройствами | 1981 |

|

SU1013939A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Селекторный канал | 1982 |

|

SU1053096A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство управления для мультиплексного канала | 1984 |

|

SU1265787A1 |

| Многоканальный адаптер | 1987 |

|

SU1495806A1 |

| Устройство для контроля передачи информации между каналом и процессором | 1980 |

|

SU960824A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных комплексах для обмена информацией между ЭВМ и микропроцессорньми внешними устройствами. Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности обмена группы микропроцессорных внешник устройств с ЭВМ. Цель достигается тем, что в .-устройство, содержащее блоки усилителей-приемттиков информации и управления канала, блоки усилителей-передатчиков информации и управления абонента, блоки задания И сравнения адреса устройства управления внешним устройством, блок контроля четности, дешифратор команд, блок управления, регистр коьшнд и формирователь бита контроля четности, введены регистр начального адреса области-обмена данными, блок формирования адресов микропро ессорной магистрали, регистр адреса внешнего устрой- g ства, регистр длины блока, блок элементов И формирования адреса абонента, регистр данных, регистр состояния и блок синхронизации. 2 з.п. ф-лы, 8 ил. «

2в

yjs

Т1

2

дО

2L

Pus.2

ffm flOHu J Dm блока 11 адрес У6Уадрес 5У

л/

П

АВрвс на 6/10Н 18

Признаки упра5/1&,

1

i

ниа от 6/1она9

15

Фиг.

2fB5P-/(

2fflMP-ff -f Л . ..|.

22/fffPiJ -Hh- fCZ E

-I--т-r i

лл/глл /I . ..- 1.

f.tifHOTI

22йОР-а

г1улрч

22УЛР-Д 22ИНЧН) (

2тини

lOUlHWi SffH

зпш

pnUf-Sx.

25ШЯ .miHD

sn ЗУ

- Начальная SbfSoptfQ э

-l oHOf} ббода-ды оЗа

Фи.в

fidpec абонента на

SnoK 18 Признак цпр00пения

(сбпока 9) йдрес В У (срегистра 11 f

Начальная выборка канала Seoda быоода

йдрес УВУсдпока5

X

Фав. 7

UJuHQ27.Cu8Hafl под- тберждения операций

Шинад2.Сигна/г Мр шения операции Шина 5. Сигнал Havana выполнения опер. Сигнал,.чтение („запись )§ысга6пенныи на шине 27 Шина25.йдрес уст- ройстба.

гх

Фи&.8

| Устройство для сопряжения | 1982 |

|

SU1043619A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Насос | 1917 |

|

SU13A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-04—Подача