Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства в системах обработки информации и системах передачи информации.

Цель изобретения - повышение надежности устройства.

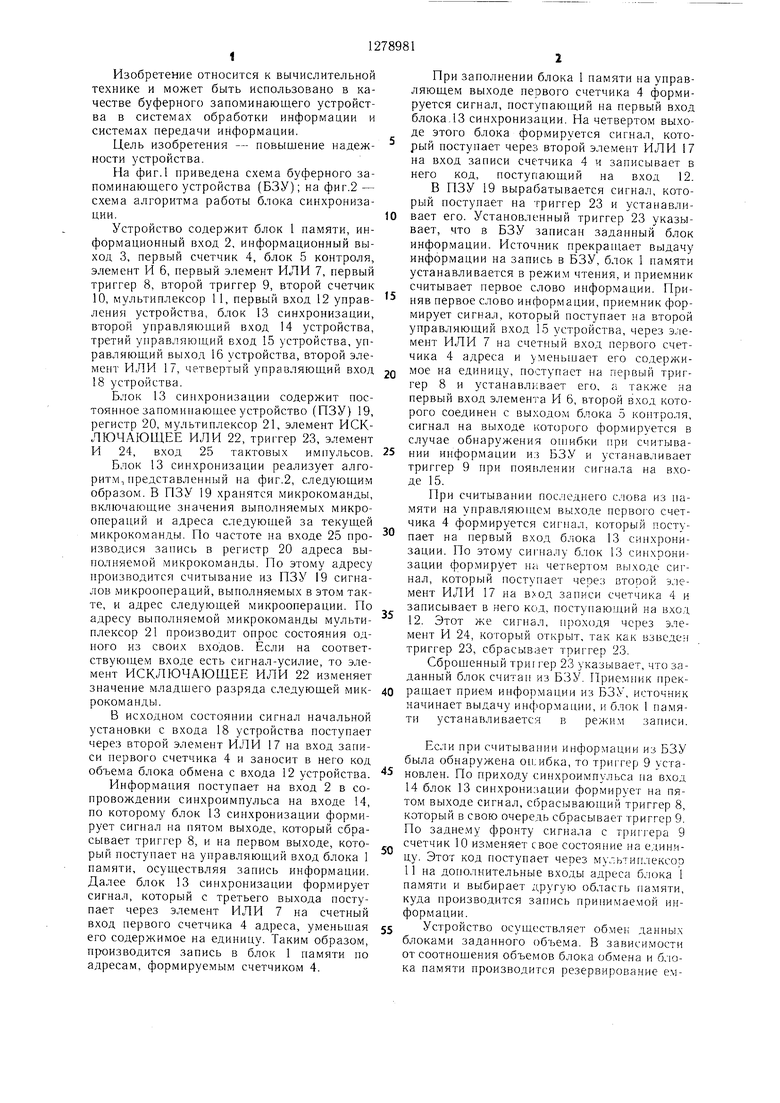

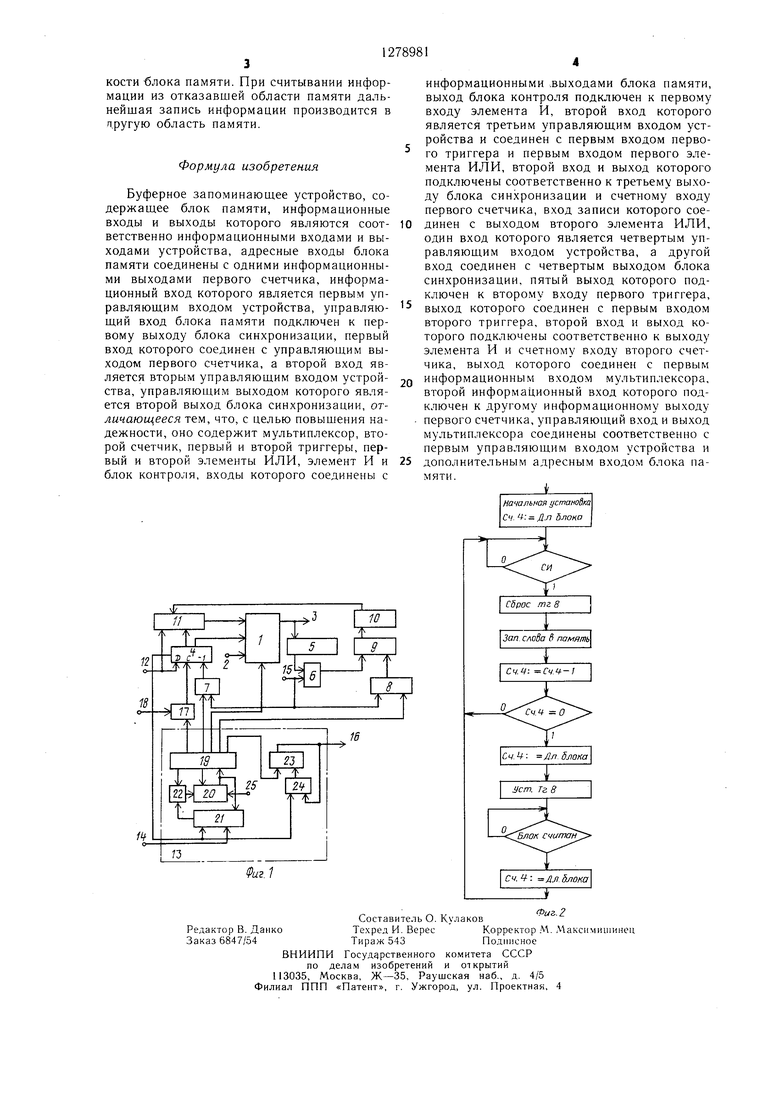

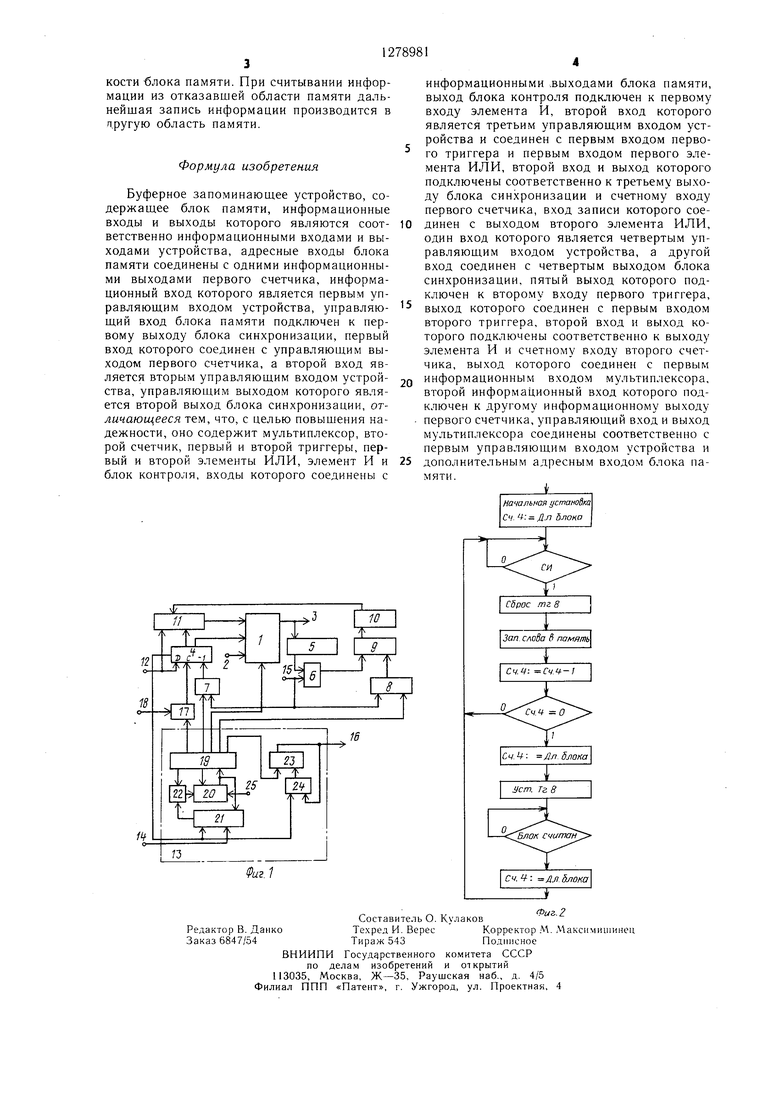

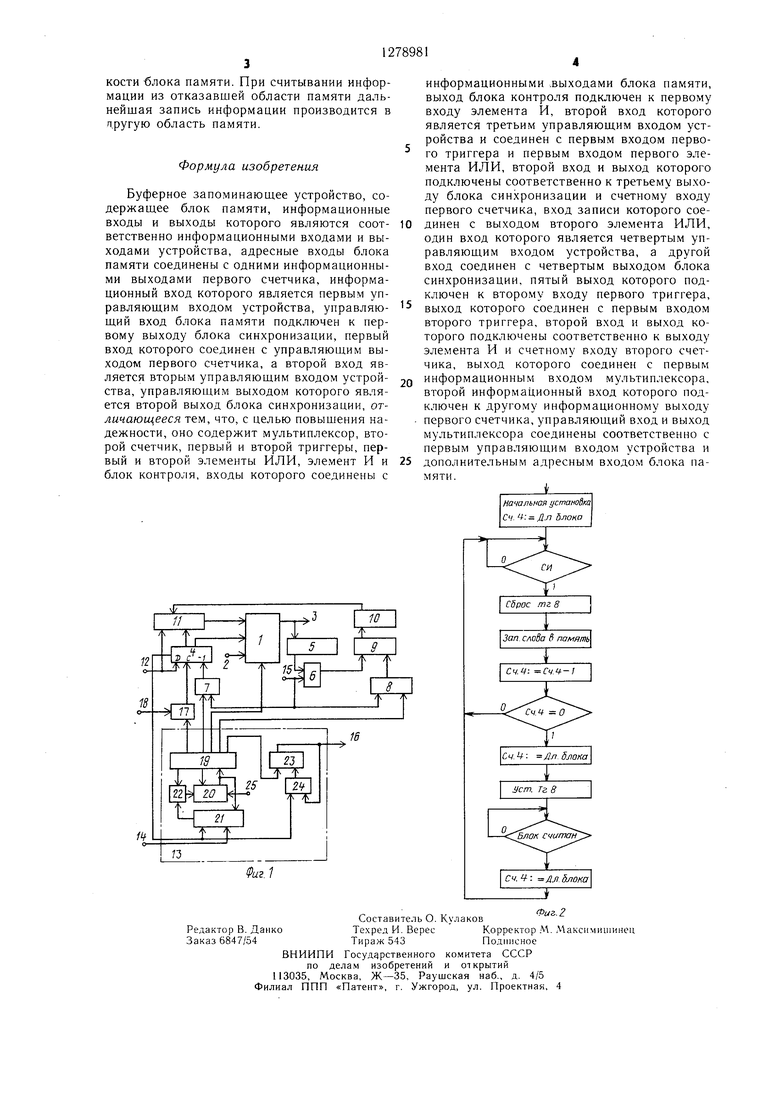

На фиг.1 приведена схема буферного запоминающего устройства (БЗУ); на фиг.2 - схема алгоритма работы блока синхронизации.

Устройство содержит блок 1 памяти, информационный вход 2, информационный выход 3, первый счетчик 4, блок 5 контроля, элемент И 6, первый элемент ИЛИ 7, первый триггер 8, второй триггер 9, второй счетчик 10, мультиплексор 11, первый вход 12 управ- ления устройства, блок 13 синхронизации, второй управляющий вход 14 устройства, третий управляющий вход 15 устройства, управляющий выход 16 устройства, второй элемент ИЛИ 17, четвертый управляющий вход 18 устройства.

Блок 13 синхронизации содержит постоянное запоминающее устройство (ПЗУ) 19, регистр 20, мультиплексор 21, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22, триггер 23, элемент И 24, вход 25 тактовых импульсов.

Блок 13 синхронизации реализует алгоритм, представленный на фиг.2, следующим образом. В ПЗУ 19 хранятся микрокоманды, включающие значения выполняемых микроопераций и адреса следующей за текущей микрокоманды. По частоте на входе 25 про- изводися запись в регистр 20 адреса выполняемой микрокоманды. По этому адресу производится считывание из ПЗУ 19 сигналов микроопераций, выполняемых в этом такте, и адрес следующей микрооперации. По адресу выполняемой микрокоманды мультиплексор 21 производит опрос состояния одного из своих входов. Если на соответствующем входе есть сигнал-усилие, то элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22 изменяет значение младщего разряда следующей микрокоманды.

В исходном состоянии сигнал начальной установки с входа 18 устройства поступает через второй элемент ИЛИ 17 на вход записи первого счетчика 4 и заносит в него код объема блока обмена с входа 12 устройства.

Информация поступает на вход 2 в сопровождении синхроимпульса на входе 14, по которому блок 13 синхронизации формирует сигнал па пятом выходе, который сбрасывает триггер 8, и на первом выходе, который поступает на управляющий вход блока 1 памяти, осуществляя запись информации. Далее блок 13 синхронизации формирует сигнал, который с третьего выхода поступает через элемент ИЛИ 7 на счетный вход первого счетчика 4 адреса, уменьшая его содержимое на единицу. Таким образом, производится запись в блок 1 памяти по адресам, формируемым счетчиком 4.

5

5

0

0

5

При заполнении блока 1 памяти па управляющем выходе первого счетчика 4 формируется сигнал, поступающий на первый вход блока.13 синхронизации. На четвертом выходе этого блока формируется сигнал, который поступает через второй элемент ИЛИ 17 на вход записи счетчика 4 и записывает в него код, поступающий на вход 2.

В ПЗУ 19 вырабатывается сигнал, который поступает на триггер 23 и устанавливает его. Установленный триггер 23 указывает, что в БЗУ записан задапный блок информации. Источник прекращает выдачу информации на запись в БЗУ, блок 1 памяти устанавливается в режим чтения, и приемник считывает первое слово информации. Приняв первое слово информации, приемник формирует сигнал, который поступает на второй управляющий вход 15 устройства, через элемент ИЛИ 7 на счетный вход первого счетчика 4 адреса и уменьшает его содержимое на единицу, поступает па первый триггер 8 и устанавливает его. ;-; также на первый вход элемента И 6, второй вход которого соединен с выходом блока 5 контроля, сигнал на выходе которого фор.мируется в случае обнаружения ошибки при считывании информации из БЗУ и устанавливает триггер 9 при пояЕ лении сигнала па входе 15.

При считывании последнего слова из памяти на управляюп|см в.ыходе первого счетчика 4 формируется сиг}1ал, который поступает на первый вход блока 13 синхронизации. По этому сигналу б. юк 13 сипхрони- зации формирует па четвертом выходе сигнал, который поступает через второй э;1е- мент ИЛИ 17 на записи счетчика 4 и записывает в него код, поступающий на вход 12. Этот же сигпал, проходя через эле- мепт И 24, который открыт, так как взводе} триггер 23, сбрасывает триггер 23.

Сброшенный трИ1 гер 23 указывает, что заданный блок считан из БЗУ. Приемник прекращает прием информации из БЗУ, источник начинает выдачу инфор.мапии, и блок 1 памяти устанавливается в режим записи.

Если при считывании информации из БЗУ была обнаружепа , то триггер 9 установлен. По приходу синхроимпульса на вход 14 блок 13 синхронизации формирует на пятом выходе сигнал, сбрасываюц.1ий триггер 8, который в свою очередь сбрасывает триггер 9. По заднему фронту сигнала с триггера 9 счетчик 10 изменяет свое состояние на единицу. Этот код поступает через мультиплексор 11 на дополнительные входы адреса блока 1 памяти и выбирает другую область памяти, куда производится запись принимаемой информации.

Устройство осуществляет обмеь: данных блоками заданного объема. В зависимости от соотношения объемов блока обмена и блока памяти производится резервирование емкости блока памяти. При считывании информации из отказавшей области памяти дальнейшая запись информации производится в п.ругую область памяти.

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, адресные входы блока памяти соединены с одними информационными выходами первого счетчика, информационный вход которого является первым управляющим входом устройства, управляющий вход блока памяти подключен к первому выходу блока синхронизации, первый вход которого соединен с управляющим выходом первого счетчика, а второй вход является вторым управляющим входом устройства, управляющим выходом которого является второй выход блока синхронизации, отличающееся тем, что, с целью повышения надежности, оно содержит мультиплексор, второй счетчик, первый и второй триггеры, первый и второй элементы ИЛИ, элемент И и блок контроля, входы которого соединены с

;

Фиг.1

0

5

0

информационными .выходами блока памяти, выход блока контроля подключен к первому входу элемента И, второй вход которого является третьим управляющим входом устройства и соединен с первым входом первого триггера и первым входом первого элемента ИЛИ, второй вход и выход которого подключены соответственно к третьему выходу блока синхронизации и счетному входу первого счетчика, вход записи которого соединен с выходом второго элемента ИЛИ, один вход которого является четвертым управляющим входом устройства, а другой вход соединен с четвертым выходом блока синхронизации, пятый выход которого подключен к второ.му входу первого триггера, выход которого соединен с первым входом второго триггера, второй вход и выход которого подключены соответственно к выходу элемента И и счетному входу второго счетчика, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого подключен к другому информационному выходу первого счетчика, управляющий вход и выход мультиплексора соединены соответственно с первым управляющим входом устройства и дополнительным адресным входом блока памяти.

J

Редактор В. Данко Заказ 6847/54

Составитель О. Кулаков

Техред И. ВересКорректор .М. AlaKciiMiuiinnen

Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патеит, г. Ужгород, ул. Проектиак, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для цифровой магнитной записи | 1989 |

|

SU1647634A2 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1280629A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Изобретение относится к области вычислительной те.хники и может быть использовано в качестве буферного, запоминающего устройства в системах сбора, регистрации и обработки измерительной инфорации. Цель изобретения состоит в повышении надежности устройства за счет обеспечения резервирования блока памяти в тех случаях, когда величина блока обмена информацией по крайней мере в два раза меньше используемого в устройстве блока памяти. Устройство содержит блок памяти, счетчики, блок контроля, элементы И, ИЛИ, триггеры, мультиплексор, блок синхронизации. 2 ил. го 00 ;о 00

| Буферное запоминающее устройство | 1978 |

|

SU767836A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3992699, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-21—Подача