Изобретение относится к вычислительной технике и может быть использовано в качестве управляющей подсистемы в высо- коимпедансных системах контроля и управления сбором и обработкой информации.

Целью изобретения является повышение отказоустойчивости системы, за счет

восстановления работоспособности блоков микропрограммного управления при сбоях и отказах.

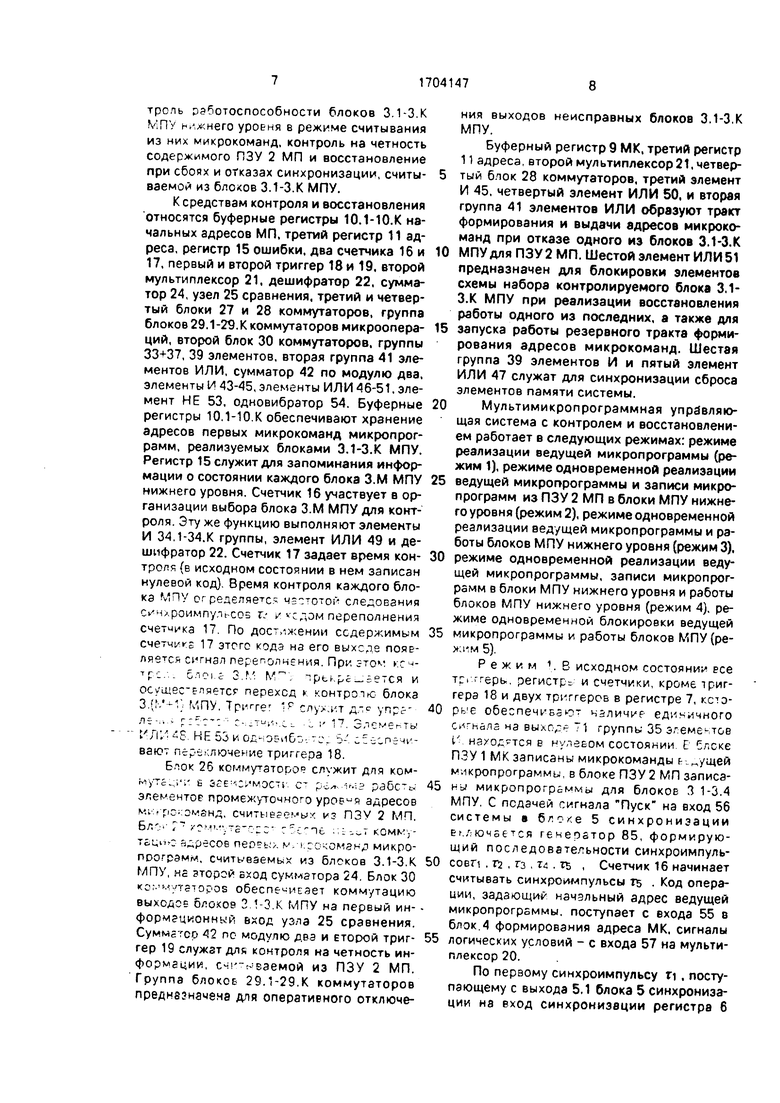

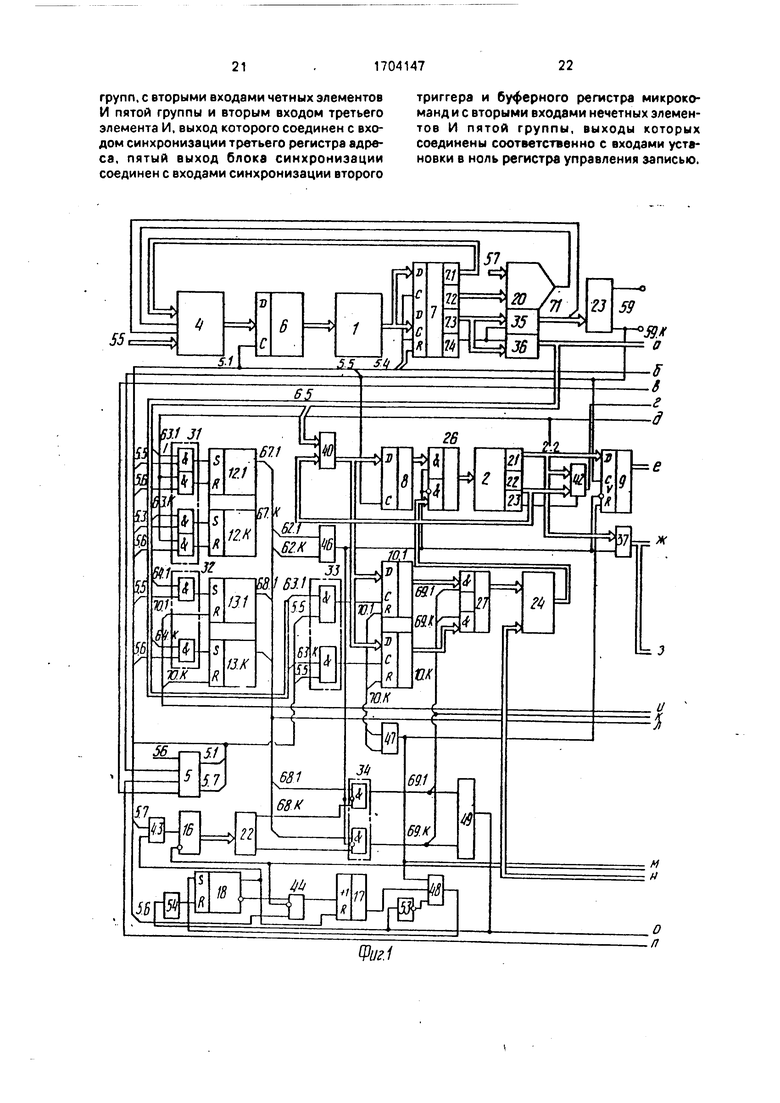

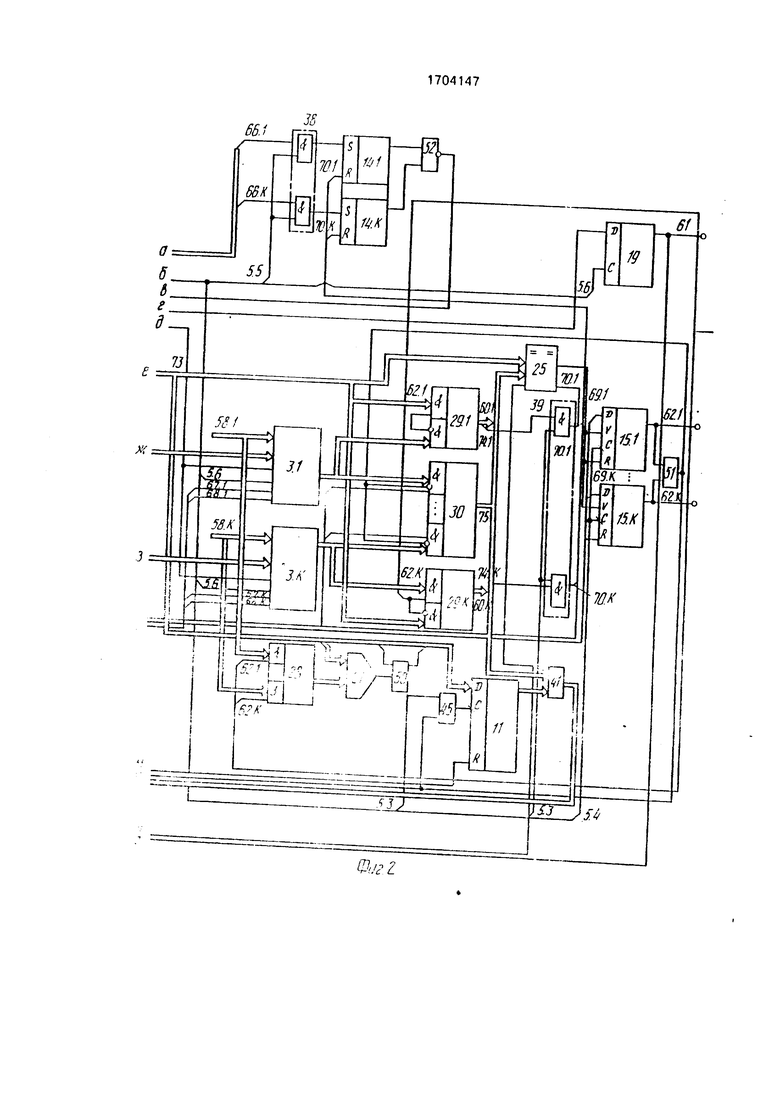

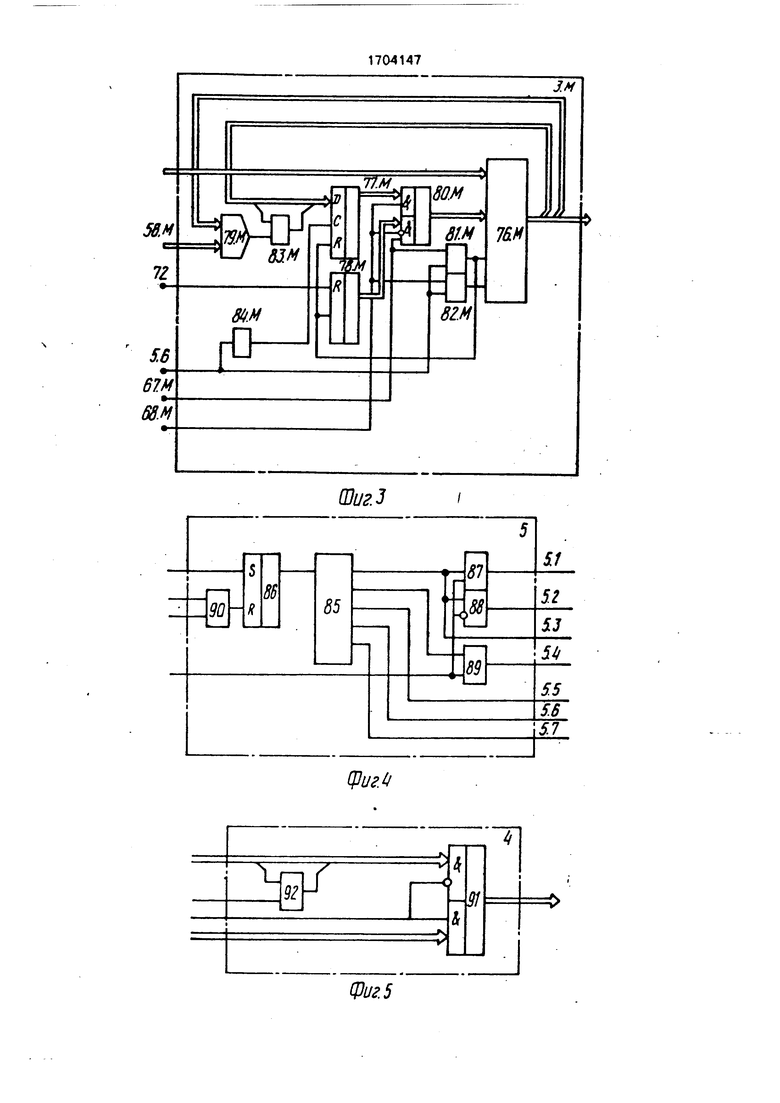

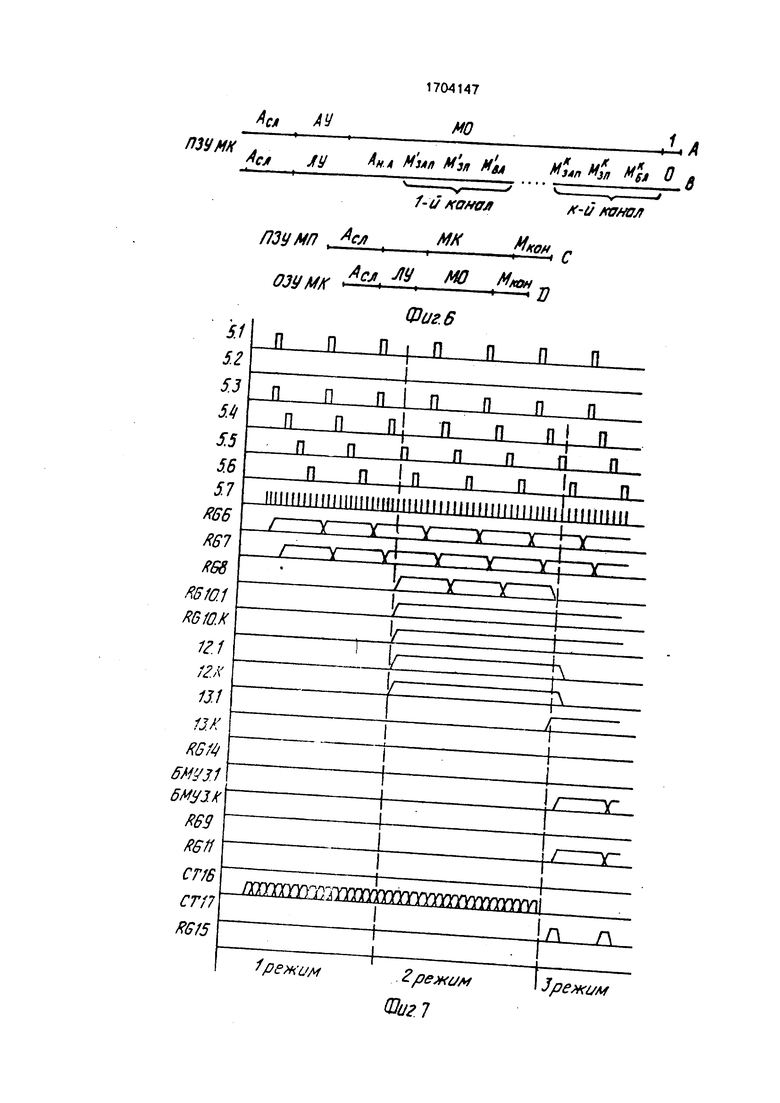

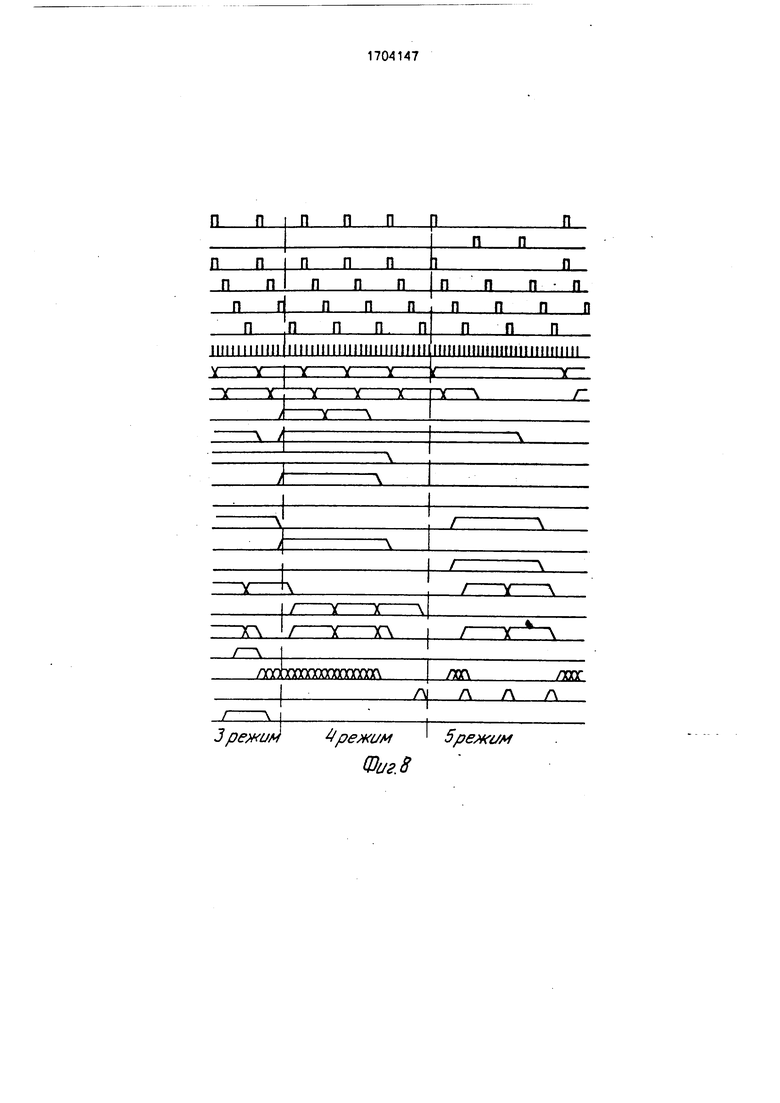

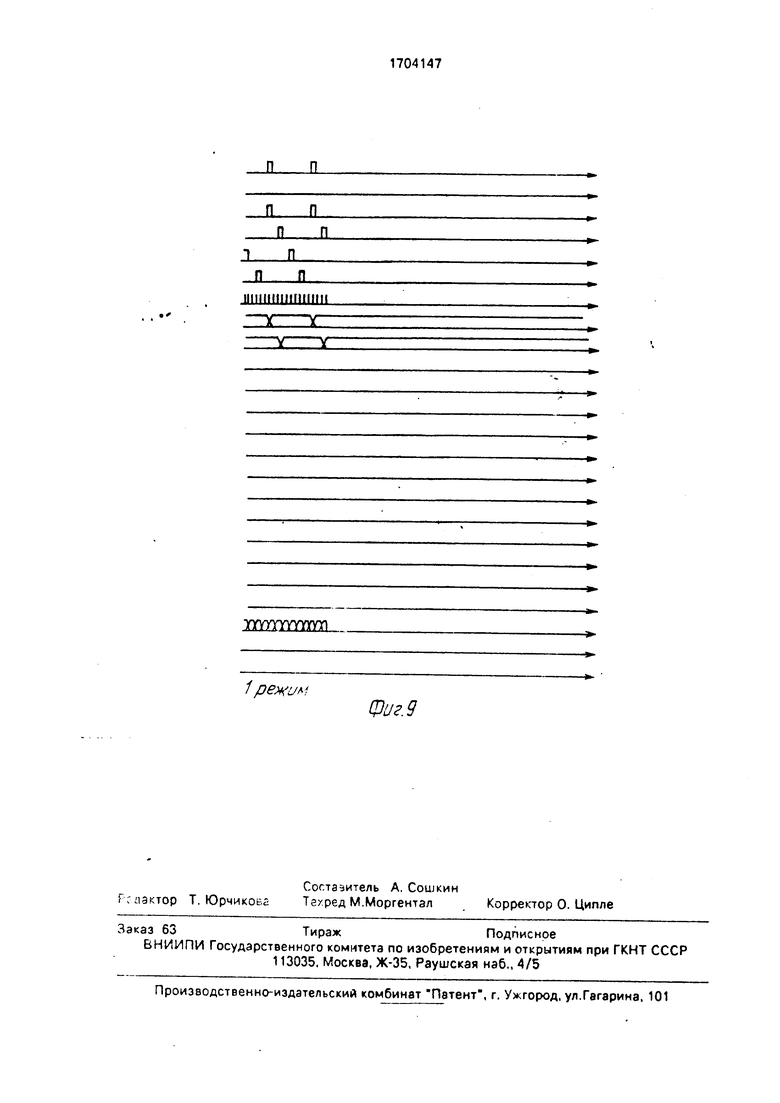

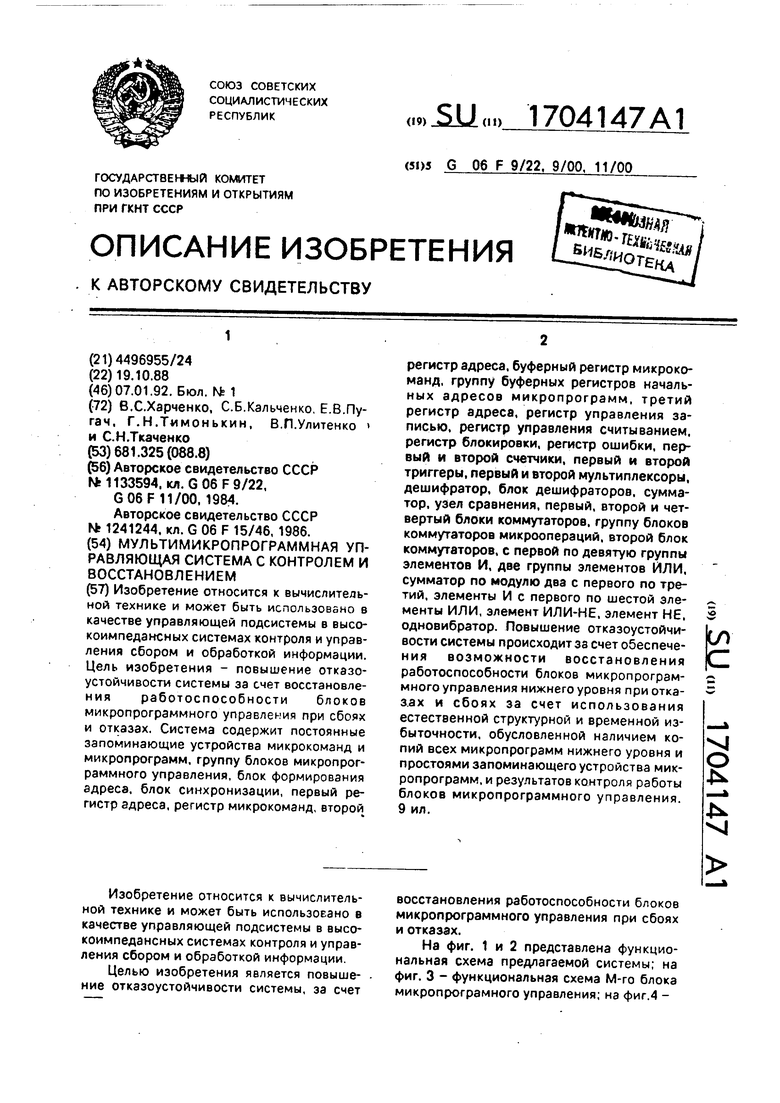

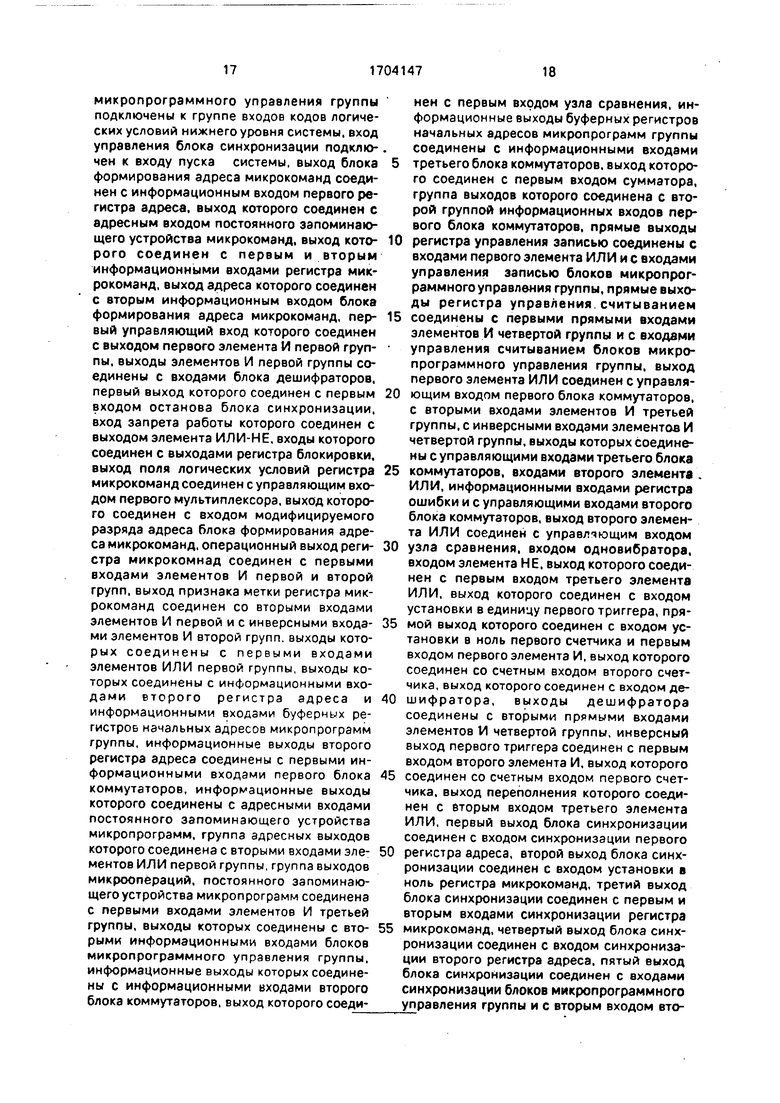

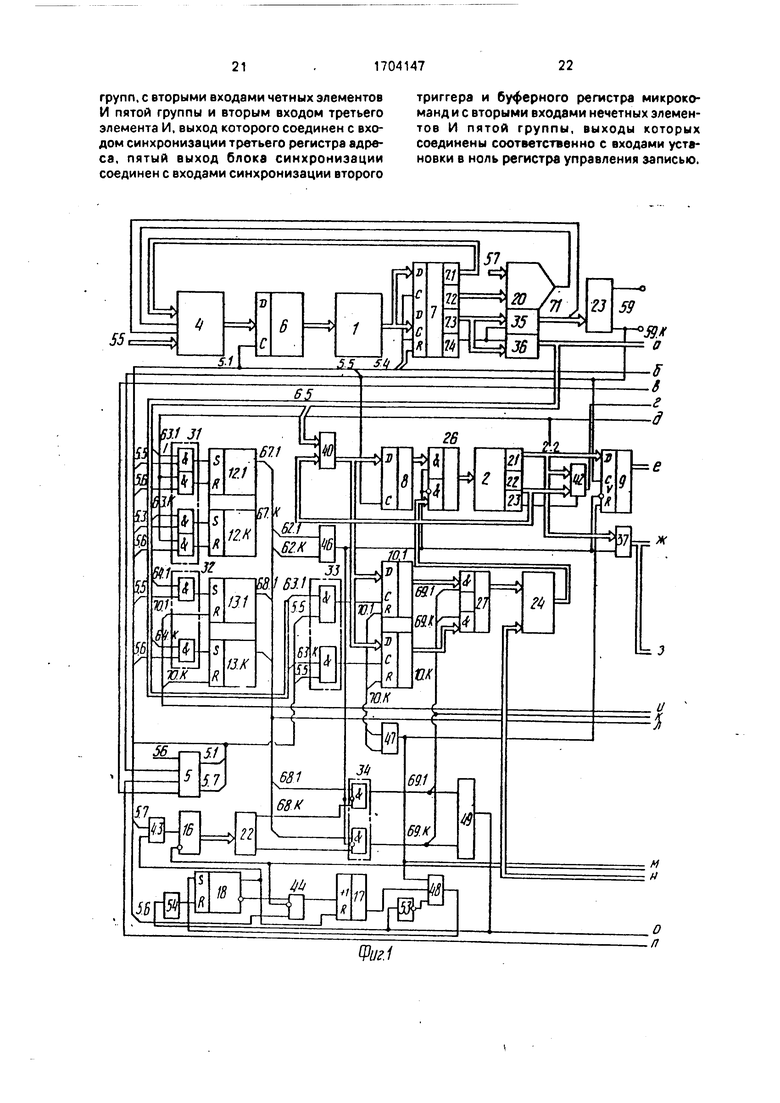

На фиг. 1 и 2 представлена функциональная схема предлагаемой системы; на фиг. 3 - функциональная схема M-го блока микропрограмного управления; на фиг.4 функциональная схема блока синхронизации; на фиг. 5 - функциональная схема блока формирования адреса; на фиг. 6 показаны форматы микрокоманд, используемых в системе; на фиг. 7-9 - временная диаграмма работы системы.

Мультимикропрограммная управляющая система с контролем и восстановлением (фиг. 1 и 2) содержит постоянное запоминающее устройство 1 микрокоманд (ПЗУ МК). ПЗУ 2 микропрограмм (МП), группу блоков 3.1-3.К микропрограммного управления (МПУ), блок 4 формирования адреса МК, блок 5 синхронизации, первый регистр 6 адреса, регистр 7 МК с полем 7.1 адреса, полем 7.2 кода логических условий, операционным полем 7.3 и полем 7.4 метки, второй регистр 8 адреса, буферный регистр 9 МК, группу буферных регистров 10.1-10.К начальных адресов МП, третий регистр 11 адреса, регистр 12 управления записью, регистр 13 управления считыванием, регистр 14 блокировки, регистр 154 ошибки, два счетчика 16 и 17, первый и второй триггер 18 и 19, первый и второй мультиплексоры 20 и 21, дешифратор 22. блок 23 дешифраторов, сумматор 24. узел 25 сравнения, первый, третий и четвертый блоки 27 и 28 коммутаторов, трупу блоков 29.1-29.К коммутаторов микроопераций, второй блок 30 коммутаторов, с первой по девятую группы 31-29 элементов И, первую и вторую группь; 40 и 41 элементов ИЛИ, суматор 42 по модулю два. с первого по третий элементы И 43-45, с первого по шестой элементы ИЛИ 45-51, элемент ИЛИ-НЕ 52, элемент Ч Б 5С одновибс тор 54.

Кром: того, система содержит вход 55 кода операции вход 56 пуска, вход 57 логических усг-сеий верхнего уровня, сходы 58.1-58.К г.С ических условий нижнего уровня, выход 59 микроопераций серхнегоурос- ня, вход 59.К микрооперации конца работы, выходы 60.1-60.К микроопераций нижнего уровня, выход 61 отказа, выходы 62.1-62.К ошибки, выходы 63.1-63.К сигналое управления записью группы 36 элементов И, выходы 64.1-64,К с: гналов управления считыванием группы 35 элементов И. выход 65 сигналое начального адреса группы 36 элементов И, выходы 66.1-66.К сигналов блокировки группы 36 элементов И, прямые выходы 67.1-67,К регистра управления записью, прямые выходы 68.1-69.К регистра управления считыванием, выходы 69.1-69.К группы 34 элементов, выходы 70.1-70.К группы 39 элементов И. выход 71 конца опе- рации группы 35 элементов И, выход 72 конца записи группы операционных выходов ПЗУ 2 МП, выходы 73 разрядов адреса

информационных выходов регистра 9, выходы 74.1-74.К микроопераций конца операции группы блоков 29.1-29.К коммутаторов, выходы 75 разрядов адреса блока 30 коммутаторов.

Блок З.М (фиг.З) МПУ содержит оперативную память 76.М (ОЗУ МК) регистр 77.М, счетчик 78.М, мультиплексор 79.М, коммутатор 80.М. два элемента И 81.М, 82.М. эле0 мент ИЛИ 83.М, элемент 84.М задержки.

Блок 5 (фиг.4) синхронизации содержит генератор 85, триггер 86. три элемента И 87-89, элемент ИЛИ 30.

Блок 4 (фиг.5) формирования адреса со5 держит коммутатор 91 и элемент ИЛИ 92.

На фиг. 6 представлены форматы микрокоманд системы. Форматами А и В задаютсямикрокоманды ведущей микропрограммы. Идентификация форма0 тов (А или В) осуществляется по значению поля метки микрокоманды: в формате А последний разряд равен единице, в формате В - нулю. Микрокоманды формата А содержат адресное поле (Асл), после логических

5 условий (ЛУ), поле микроопераций (МО) и поле метки (признак формата микрокоманды). Микрокоманды формата В содержат поле Асл, поле ЛУ, поле адреса первой микрокоманды1 микропрограммы, переза0 писывэемой из ПЗУ 2 МП (промежуточного уровня) в блоке 3. М МПУ нижнего уровня. (Ан.у.). К-поле управления работой блоков 3.1-3.К МПУ нижнего уровня (Мзап, М3п, Мб,-) и поле метки.

5 Блокам МПУ нижнего уровня адресуются три типа меток: М3апм - метка записи микропрограмм Е блок З.М МПУ; М3пм- метка запуска блока З.М МПУ нижнего уровня; Мблм - метка блокировки ведущей микро0 прсгр ы

. манды Формата С хранятсг в ПЗУ 2 МП и содержат поле АПл. поле микрокоманд (МК), переписываемых из ПЗУ 2 МП в блоки З.М МПУ, а также метку конца мик5 ропрогрзммы (M.oi-). Микрокоманды формата D формируются в блоке З.М МПУ нижнего уровня v содержат поле Асл, поле ЛУ. поле МО и метку Мкон.

Мул ьтим икре программная управляю0 щая система (фиг. 1 и 2) имеет три уровня управления. Внешний уровень предназначен для реализации ведущей микропрограммы. К средствам высшего уровня относится ПЗУ 1 МК, блок 4 формирования

5 адреса МК, первый регистр 6 адреса, регистр 7 МК, мультиплексор 20 и блок 23 дешифраторов. ПЗУ 1 МК предназначено для хранения микрокоманд ведущей микропрограммы. Блок 4 формирования адреса МК формирует исполнительный адрес очередкой микрокоманды. На вход 55 блока офрмирования адреса МК поступает код операций, который задает адрес первой микрокоманды ведущей микропрограммы. Код операции, а также адрес следующей микрокоманды проходят через коммутатор 91. Элемент ИЛИ 92 модифицирует разряд адресе следующей микрокоманды в соответствии со значением проверяемого логического условия. Первый регистр 6 адреса предназначен для записи сформированного адреса по переднему фронту синхроимпульса первой последовательности. Регистр 7 МК служит для записи считанной из ПЗУ 1 МК микрокоманды. Блок 23 дешифраторов формирует управляющие сигналы в соответствии с входными кодами микроопераций. Число дешифраторов в блоке 23 равно числу полей несовместимых микроопераций. Входы каждого дешифратора подключены к выходам соответствующего поля несовместимых микроопераций выходов группы 35 элементов И.

Средний уровень управления предназначен для бесповоротного хранения всех микропрограмм управления параллельными операционными устройствами, которое реализуется на нижнем уровне, а также для формирования адреса микрокоманды при считывании микропрограмм в блоки З.М МПУ. К средствам среднего уровня относятся группа 40 элементов ИЛИ, регистр 8 адреса и ПЗУ 2 МП.

Нижний уровень управления служит для реализации параллельного управления однотипными операционными устройствами. К средствам нижнего уровня относятся блоки 3.1-З.К МПУ.

Средства управления и синхронизации системы предназначены для синхронной работы всех ее узлов и для организации правильности функционирования всей системы в целом. К средствам управления и синхронизации относятся блок 5 синхронизации, регистр 12 управления записью микропрограмм верхнего уровня в блоки З.М МПУ нижнего уровня, регистр 13 управления считыванием микрокоманд из блоков 3.1-3.К МПУ нижнего уровня, регистр 14 блокировки ведущей микропрограммы и элемент ИЛИ-НЕ 52.

Блок синхронизации (фиг.4) обеспечивает синхронность работы всех узлов и блоков системы. Генератор 85 формирует импульсы первой-пятой последовательностей - синхроимпульсы. Триггер 86 обеспечивает включение генератора 85 синхроимпульсов. В исходном состоянии триггер 86 находится в нулевом состоянии, на управляющий вход генератора 85 подается нулевой сигнал и генератор не функционирует. При поступлении сигнала пуска на вход 56 системы триггер 86 переходит в единичное состояние, тем самым включается генератор 85. Элементы И 87-89 управляют выдачей синхроимпульсов различным узлам и блокам мультимикропрограммной управляющей системы в зависимости от режимов ее работы. Блоки З.М МПУ работают

в двух режимах: в режиме записи микропрограмм из ПЗУ 2 МП и в режиме реализации параллельных микропрограмм.

В режиме записи микропрограмм управляющими сигналами для блока З.М МПУ

являются четвертая последовательность импульсов Г4 с выходов 5.6 генератора 85 и сигнал записи, поступающий с выходов 67.М регистра 12 на управляющие входы коммутатора 80.М и элемента И 81.М. Счет- чик 78.М служит для задания адресов, по которым записываются мкрокоманды. В исходном состоянии счетчик 78.М находится в нулевом состоянии. С приходом синхроимпульса и сигнала записи импульсы с выхода

элемента И 81.М поступают на вход счетчика 78.М и на вход записи ОЗУ МК 76.М. Запись первой микрокоманды в ОЗУ МК 76.М осуществляется по нулевому адресу. С выхода счетчика 78.М через коммутатор

80.М при записи поступают адреса, по которым производится запись микрокоманд в ОЗУ МК 76.М. С приходом каждой новой микрокоманды содержимое счетчика 78.М увеличивается на единицу. После прихода

на нулевой вход счетчика 78.М метки конца цикла записи происходит его обнуление и прекращается подача импульсов записи на ОЗУМК76.М.

В режиме реализации параллельных

микропрограмм блок З.М МПУ работаетана- логично средствам высшего уровня при реализации ведущей микропрограммы. Сигналом перевода в данный режим работы является единичный сигнал запуска, который поступает с соответствующего выхода 68.М регистра 13. После прихода этого сигнала по нулевому адресу, записанному в регистре 13 М, из ОЗУ МК 76.М считывается первая микрокоманда формата D (фиг. 6).

Считывание происходит по переднему фронту импульса с выхода элемента И 82.М, который подается на вход считывания ОЗУ МК76.М. Этим же импульсом, задержанным элементом 84.М задержки, происходит управление записью адреса следующей микрокоманды в регистр 77.М.

Средства контроля и восстановления мультимикропрограммной управляющей системы обеспечивают периодический контроль работоспособности блоков 3.1-3.К МПУ нижнего уровня в режиме считывания из них микрокоманд, контроль на четность содержимого ПЗУ 2 МП и восстановление при сбоях и отказах синхронизации, считываемой из блоков 3.1-3.К МПУ.

К средствам контроля и восстановления относятся буферные регистры 10.1-10Ж начальных адресов МП, третий регистр 11 адреса, регистр 15 ошибки, два счетчика 16 и 17, первый и второй триггер 18 и 19, второй мультиплексор 21, дешифратор 22, сумматор 24,узел 25 сравнения, третий и четвертый блоки 27 и 28 коммутаторов, группа блоков 29.1-29.К коммутаторов микроопераций, второй блок 30 коммутаторов, группы 33+37, 39 элементов, вторая группа 41 элементов ИЛИ, сумматор 42 по модулю два, элементы И 43-45, элементы ИЛИ 46-51, элемент НЕ 53, одновибратор 54. Буферные регистры 10.1-10.К обеспечивают хранение адресов первых микрокоманд микропрограмм, реализуемых блоками 3.1-3.К МПУ. Регистр 15 служит для запоминания информации о состоянии каждого блока З.М МПУ нижнего уровня. Счетчик 16 участвует в организации выбора блока З.М МПУ для контроля. Эту же функцию выполняют элементы И 34.1-34.К группы, элемент ИЛИ 49 и дешифратор 22. Счетчик 17 задает время контроля (в исходном состоянии в нем записан нулевой код). Время контроля каждого блока МПУ определяется частотой следования синхроимпульсов т- v, v-сдэм переполнения счетчика 17. По достижении содержимым счетчиц 17 этого кода на его выходе появляется сигнал переполнения. При, этом кс ТРС/. . С Л СМ. с З.Г, : 1 pt К рЈ - i 6ТСЯ И

осуществляете переход к. контролю блока 3.( МПУ. Трите: 1 служит ДЛР упргле-:.

,

ИЛ И 5. НЕ 53 и одноБи6. с. 5-. cf -:/ печи- вают переключение триггера 18.

Блок 26 коммутаторов служит для ком- мутЈ: ;;;: е 3ЈЕ О мост1 . ст р.тмз эяементоЕ1 промежуточного уровня адресов микрокоманд, считываемых из ПЗУ 2 МП. Б/к.- м - утЁ-о-с rf.-c-ne :,:--..;, т комму- тйцио адресов пеоеых макрокоманд микропрограмм, считываемых из блоков 3.1-3.К МПУ, на зторой вход сумматора 24. Блок 30 ког- мутгторов обеспечивает коммутацию выходсе блоков 3.1-3.К МПУ на первый ин- формгционный вход узла 25 сравнения. Сумматор 42 по модулю два и еторой триггер 19 служат для контроля на четность информации, счг- ваемой из ПЗУ 2 МП. Группа блоков 29.1-29.К коммутаторов предназначена для оперативного отключе

ния выходов неисправных блоков 3.1-3.К МПУ.

Буферный регистр 9 МК, третий регистр 11 адреса, второй мультиплексор 21, четвер5 тый блок 28 коммутаторов, третий элемент И 45, четвертый элемент ИЛИ 50. и вторая группа 41 элементов ИЛИ образуют тракт формирования и выдачи адресов микрокоманд при отказе одного из блоков 3.1-3.К

10 МПУ для ПЗУ 2 МП. Шестой элемент ИЛИ 51 предназначен для блокировки элементов схемы набора контролируемого блока 3,1- З.К МПУ при реализации восстановления работы одного из последних, а также для

15 запуска работы резервного тракта формирования адресов микрокоманд. Шестая группа 39 элементов И и пятый элемент ИЛИ 47 служат для синхронизации сброса элементов памяти системы.

20 Мультимикропрограммная управляющая система с контролем и восстановлением работает в следующих режимах: режиме реализации ведущей микропрограммы (режим 1), режиме одновременной реализации

25 ведущей микропрограммы и записи микропрограмм из ПЗУ 2 МП в блоки МПУ нижнего уровня (режим 2), режиме одновременной реализации ведущей микропрограммы и работы блоков МПУ нижнего уровня (режим 3),

30 режиме одновременной реализации ведущей микропрограммы, записи микропрограмм в блоки МПУ нижнего уровня и работы блоков МПУ нижнего уровня (режим 4), режиме одновременной блокировки ведущей

35 микропрограммы и работы блоков МПУ (режим 5).

Режим 1. В исходном состоянии все трг.ггерь, регистр-; и счетчики, кроме триггера 18 и двух триггеров в регистре 7, кстз40 рь е обеспечивают наличие единичного сигнала ча выходе 71 группы 35 элементов И. находится в нулевом состоянии. Е блоке ПЗУ 1 МК записаны микрокоманды ь-.ущей микропрограммы, в блоке ПЗУ 2 МП записа45 ну микропрограммы для блоков 3 1-3.4 МПУ. С подачей сигнала Пуск на вход 56 системы в блохе 5 синхронизации Ег.,г;ючается генератор 85, формирующий последовательности синхроимпуль50 совГ1 , Г2 , гз , т, . is , Счетчик 16 начинает считывать синхроимпульсы Т5 . Код операции, задающий начальный адрес ведущей микропрограммы, поступает с входа 55 в блок.4 формирования адреса МК, сигналы

55 логических условий - с входа 57 на мультиплексор 20.

По первому синхроимпульсу ri. поступающему с выхода 5,1 блока 5 синхронизации на вход синхронизации регистра 6

адреса, происходит запись в него адреса первой микрокоманды микропрограммы, который проходит по единичному сигналу на вхыоде 71 через блок 4 формирования адреса МК (фиг.5) с входа 55 системы на входы регистра б адреса. По синхроимпульсу Т2 с выхода 5.4 блока 5 синхронизации происходит считывание из ПЗУ 1 МК первой микрокоманды ведущей микропрограммы. В данном режиме функционирования из ПЗУ 1 МК считываются микрокоманды формата А (фиг.б). При этом в регистр 7 МК записываются в поле 7.1 код адреса следующей микрокоманды, в поле 7,2 код проверяемого логического условия, в поле 7.3 операционная часть микрокоманды, в поле 7.4 единица. Код адреса следующий микрокоманды с регистра 7 поступает на блок 4 формирования адреса МК. Код проверяемого логического условия с регистра 7 поступает на адресный вход мультиплексора 20, который выделяет значение проверяемого логического условия. Выбранный сигнал логического условия с выхода мультиплексора 20 поступает в блок 4 формирования адреса МК. С выхода 71 конца операции группы 35 элементов И на блок 4 формирования адреса М К подается нулевой сигнал. Адрес следующей микрокоманды с выхода блока 4 формирования адреса МК поступает на информационный вход регистра 6 и записывается в нем по заднему фронту синхроимпульса ri . Операционная часть микрокоманды с регистра 7 через группу 35 элементов И поступает на вход блока 23 дешифраторов микроопераций. С выходов блокэ 23 дешифраторов микрооперации поступают через выход 59 системы на опера- ционныеустройства. Далее функционирование системы по реализации микрокоманд формата А аналогично описанному алгоритму. При появпении на выходе 71 единичного значения управляющего сигнала Конец операции система начинает работать по новому коду операции, который проходит с входов 55 системы через блок 4 формирования адреса МК на информационные входы регистра 6. Работа систе- мы прекращается при появлении единичного сигнала на выходе 59.К конца работы блока 23 дешифраторов. По этому сигналу происходит обнуление триггера 86 в блоке 5 синхронизации (фиг.4) и прекращается выдача синхроимпульсов п - г$ генератором 85.

Режим 2. Работа мультимикропрог- раммной управляющей системы с контролем и восстановлением в данном режиме начинается с момента считывания из блока

ПЗУ 1 МК микрокоманды формата В (фиг.б). Микрокоманда в этом случае содержит код адреса следующей микрокоманды, код проверяемого логического условия, начальный адрес Ан.а. микропрограммы, предназначенной для записи в блоки З.М МПУ, сигнал метки Мзап и сигнал в разряде признака формата микрокоманд. Если запись должна производитсья в несколько блоков З.М МПУ,

то сигналы меток Мзап находятся в поле, отведенном для каждого блока З.М МПУ.

Когда микрокоманда данного формата по заднему фронту синхроимпульса Тг запишется в регистр 7, происходит следующее: открывается группа 36 элементов И и начальный адрес Ан.а. микропрограммы с выхода 65 группы 36 элементов И через группу 40 элементов ИЛИ поступает на информационный вход регистра 8 и на информационные входы буферных регистров 10.1-10.К. метки Мзап - на выходы групп 31 и-33 элементов И с выходов 63.1-63.К группы 36 элементов И. По заднему фронту синхро- импульсагз с выхода 5.5 блока 5 синхронизации начальный адрес Ан.а. микропрограммы заносится в регистр 8: открываются группы 31 и 33 элементов И по входам 63.1, на которых имеются единичные сигналы метки Мзап. При этом устанавливаются в единицу соответствующие триггеры регистра 12 и происходит запись начального адреса Ам.а. в регистры 10.1-10.К. На выходе элемента ИЛИ 46 формируется единичный сигнал, который коммутирует

выход регистра 8 с входом ПЗУ 2 МП.

По заднему фронту синхроимпульса ТА с выхода 5.6 блока 5 синхронизации через группу 37 элементов И происходит считывание из ПЗУ 2 МП и запись в ОЗУ МК 76.М

первой микрокоманды записываемой микропрограммы формата С (фиг.б). С выхода поля 2.2 блока ПЗУ 2 МП адрес следующей микрокоманды подается через группу 40 элементов ИЛИ на информационный вход

регистра 8. Затем по очередному синхроимпульсу Г| адрес следующей микрокоманды с выхода блока 4 формирования адреса МК записывается в регистр 6. Далее работа узлов верхнего уровня аналогична работе в

режиме 1. По заднему фронту синхроимпульса гз адрес очередной микрокоманды считываемой микропрограммы заносится регистр 8 и по задне.му фронту синхроимпульса Гз происходит запись в ОЗУ МК

76.М новой микрокоманды. Далее работа узлов и блоков среднего и нижнего уровней аналогична описанной и продолжается до тех пор, пока на выходе 72,ПЗУ 2 МП не появится единичный сигнал Конец записи.

По этому сигналу происходит обнуление счетчика 78.М в блоке З.М МПУ, и по синхроимпульсу тл с выхода 5.6 блока 5 синхронизации через блок 31 элементов И проводятся в нулевое состояние триггеры регистра 12.

Режим 3. Данный режим начинается после того, как окончена запись микропрограмм в блоки 3.1-3.К МПУ и на выходе 64.М группы 36 элементов И появляется единичный сигнал метки Мзп. Сигнал с выхода 64.М группы 36 элементов И по синхроимпульсу Гз с выхода 5.5 блока 5 синхронизации проходит через группу 32 элементов И и переводит триггеры 13.М регистра 13 в единичное состояние. Единичный сигнал выходов 68.М этих триггеров поступает на управляющие входы коммутатора 80.М блока 3.I МПУ (фиг.З) и на управляющий вход элемента И 82.М, разрешая тем самым прохождение адресов микрокоманд с выхода регистра 77.М на адресный вход и синхроимпульсов тз на вход считывания ОЗУ МК 76.М, На выход ОЗУ МК 76.М поступают микрокоманды формата О (фиг.6). С выхода блока З.М микрооперации проходят через блок 29.М коммутаторов на выходы 60.М системы. Код проверяемого логического условия с выхода ОЗУ МК 76.М поступает на вход мультиплексора 79.1, на информационный вход которого поступают сигналы логических условий с входа 58.М системы. Сигнал с выхода мультиплексора 79.М поступает на вход элемента ИЛ И 83.М, на котором происходит модификация адреса следующей микрокоманды. Промодифици- роеанный адрес записывается по заднему Фронту задержанного синхроимпульса TVJ в регистр 77.. Далее бпсп М МПУ продолжается аналогично описанному до появления на выходе 74.М блохг 2S.M коммутаторов сггнгп ко1- -: снега J-, V:.

Контроль v &о:-т 1 ч.; i С. -ОКОБ f/ПУ в это режиме заключаются Е следующем.

В момент переключения триггеров 13.М регистра 13 в единично- начинается поиск контролируемого блока 3.1-3.К МПУ, так как послг завериения записи на выходе элема - -Ј 46 присутству-:-- - -е- вой сигнал. Сигналом окончание поиска контролируемого блока 3.1-3.К является появление единичного сигнала на одном из выходов 60.1-69.К группу 34 элементов И. При эток; на выходе элемента ИЛИ 49 появляется единичный сигнал и возбуждается одновибратор 54. Сигнал с выхода одновиб- ратора устанавливает в нулевое состояние триггер 18. Нулевым сигналом с единичного выхода триггера 18 закрывается элементИ 43 и переводится в нулевое состояние счетчик 17. Синхроимпульсы с выхода 5.7 блока 5 синхронизации не проходят на счетный вход счетчика 16. В этом счетчике фиксируется код номера проверяемого блока З.М

МПУ, а счетчик 17 начинает считать количество синхроимпульсов г . Кроме того, единичный сигнал с выхода 69.М группы 34 элементов И разрешает прохождение кода адреса первой микрокоманды микропрограммы, реализуемой блоком З.М МПУ, с выхода регистра 10.М на первый вход сумматора 24. На второй вход сумматора 24 поступает с выхода 75 блока 30 коммутаторов через группу 41 элементов ИЛИ адрес

следующей микрокоманды блока З.М МПУ. Сумматор 24 определяет адрес микрокоманды в ПЗУ 2 МП, который с выхода последнего через блок 26 коммутаторов поступает на вход ПЗУ 2 МП. Микрокоманда. считываемая из ПЗУ 2 МП по синхроимпульсу с выхода 5.6 блока 5 синхронизации, заносится в регистр 9, так как на его управляющем входе присутствует нулевой потенциал с выхода элемента ИЛИ 46. С выхода

регистра 9 микрокоманда ПЗУ 2 МП поступает на первый вход узла 25 сравнения, на второй вход которого поступает микрокоманда, считываемая из ОЗУ МК 76.М, через блок 30 коммутаторов по разрешающему

единичному сигналу на выходе 69.М группы 34 элементов И., Разрешающим сигналом для работы узла 25 сравнения является наличие единицы на выходе элемента ИЛИ 49. При неравенстве кодов микрокоманд на выходе узла 25 сравнения появляется единичный сигнал Этот сигнал поступает на управляющие ВХОДУ тритеров регистра 15, разрешая их работу. По очередному синхрс- импульсу с выхс-да 5.4 блока 5 синхронизации единичный сигнал с выхода 6.М группы 34 элементов И заносится в триггер 15.М pen-j:-. ID. ЕЈ,-.-----;-:УЙ сигнал ои- иО- ки с выход .р 15.М регистра 15 поступает на упраьляющтй вход блока 29.№

коммутаторов. При этом на выход 60.М системы преходят кеды микроопераций с выхода регистра 9. Тем же сигналом с выхода триггера 15.М регистра 15 блок 28 коммутаторов коммутирует наличие условия, которое поступает на вход 58.М блока З.М МПУ, на вход мультиплексора 21. Одновременно единичный сигнал с выхода триггера 15.М регистра 15 проходит через элемент ИЛИ 51, блокирует блок 30 коммутаторов, открывает элемент И 45, закрывает элемент И 44 и запрещает работу счетчика 16. По очередному синхроимпульсу с выхода 5.5 блока 5 синхронизации в регистр 11 заносится адрес очередной микрокоманды блока З.М

МПУ с выходов 73 регистра 9. С выхода регистра 11 через группу 41 элементов ИЛИ адрес очередной микрокоманды микропрог раммы поступает на второй вход сумматора 24. Далее сформированный адрес микрокоманды ПЗУ 2 МП проходит с выхода сумматора 24 через блок 26 коммутаторов на адресные входы ПЗУ 2 МП, откуда по очередному синхроимпульсу Г4 микрокоманда формата О заносится в регистр 9. При этом микрооперации проходят с выхода регистра 9 через блок 29.М коммутаторов на выходы 60.М микроопераций системы. Адресная часть микрокоманды с выхода 73 регистра 9 поступает на информационный вход регистра 11. Выход кода логических условий адресного выхода 73 регистра 9 поступает на управляющие входы мультиплексора 21. Модифицируемый разряд адреса совместно с результатом ветвления,формируемым на выходе мультиплексора 21, поступает на вход элемента ИЛИ 50. С выхода последнего модифицированный разряд адреса посту- . пает на информационный вход регистра 11. По очередному синхроимпульсу Гз софрми рованный адрес микрокоманды заносится в регистр 11 и цикл работы повторяется. По окончании реализации микропрограммы на выходе 74.М блока 29.М коммутаторов формируется единичный сигнал Конец операции, который поступает на M-й вход группы 39 элементов И. По очередному синхроимпульсу ri с выхода 5.3 блока 5 синхронизации на выходе 70.М группы 39 элементов И формируется единичный сигнал, которым переводятся в нулевое состояние триггер 13.М регистра 13, триггер 15.М регистра 15 и регистр 10.М. Кроме того, этот единичный сигнал проходит через элемент ИЛИ 47 на R-вход регистра 9, переводя его в нулевое состояние, и на вход элемента ИЛИ 48. Единичный сигнал с выхода последнего переводит в единичное состояние триггер 18. Нулевой сигнал с выхода элемента ИЛИ 51 закрывает элемент И 45, открывает элемент И 44 и разрешает работу счетчика 16. На обоих информационных входах узла 25 сравнения присутствуют нулевые сигналы которые формируют на его выходе нулевой потенциал. При появлении на выходе 69.М группы 34 элементов И единичного сигнала, который означает выбор нового контролируемого блока З.М МПУ, работа системы повторяется. Одновременно происходит реализация микрокоманд ведущей микропрограммы аналогично первому режиму работы. Кроме того, происходит контроль на четность информации, считываемой из ПЗУ 2 МП, путем суммирования разрядов полей

2.1 и 2.2 и поля 2.3 контрольного разряда ПЗУ 2 МП на сумматоре 42 по модулю два. Результат сложения с выхода сумматора по модулю два поступает на информационный

вход триггера 19. Если на выходе сумматора 42 по модулю два формируется нулевой сигнал, то система исправна, если единичный, то нет. В последнем случае по синхроимпульсу г с выхода 5.6 блока 5 синхронизации единичный сигнал заносится в триггер 19. При этом на выходе 61 системы формируется сигнал отказа и переводится в нулевое состояние триггер 86 блока 5 синхронизации. Система прекращает свою

работу.

Если в процессе контроля блока З.М МПУ сигнал ошибки не появляется, то выбранный для контроля блок З.М МПУ контролируется в течение времени контроля,

определяемого кодом переполнения счетчика 17. Сигнал с выхода переполнения счетчика 17 переводит триггер 18 в единичное состояние. Переключившись в единичное состояние, триггер 18 разрешает прохождение через элемент И 43 синхроимпульсов с выхода 5.7 блока 5 синхронизации на счетный вход счетчика 16, устанавливает в нулевое состояние счетчик 18 и запрещает прохождение синхроимпульсов Г4 через

элемент И 44 на вход счетчика 17. Далее работа системы продолжается аналогично описанному.

После появления на выходе 74.М блока 29.М коммутаторов единичного сигнала Конец операции M-го блока МПУ по очередному синхроимпульсу с выхода 5.3 блока 5 синхронизации на выходе 70.М группы 39 элементов И формируется единичный импульс, который переводит в исходное состояние триггер 13.М регистра 13, регистр 10,М, проходит через элемент ИЛИ 47, на его выходе формируется единичный сигнал. Единичный сигнал с выхода элемента ИЛИ 47 переводит в нулевое состояние регистр

9, проходит через элемент ИЛИ 48 и переводит в единичное состояние триггер 18. Начинается поиск нового блока 3.1-3.К МПУ для контроля.

Режим 4. Данный режим является

частным случаем предыдущего режима. Пусть система работает в режиме 3. Началом режима 4 является появление единичного сигнала на одном из выходов 63.1-63.К группы 36 элементов И. При этом происходит следующее. Соответствующий триггер 12.М регистра 12 переходит в единичное состояние, на выходе элемента ИЛИ 46 появляется единичный сигнал, на всех выходах группы 34 элементов И устанавливается

ноль. Это приводит к записи микропрограмм в блоки МПУ нижнего уровня аналогично описанному алгоритму. Появление на вхыоде элемента ИЛИ 49 нулевого сигнала вызывает установку триггера 18 в единим- ное состояние. Счетчик 16 начинает считать поступающие на вход синхроимпульсы Т5 . счетчик 17 устанавливается в ноль. При этом прекращается контроль блоков 3.1-3.К МПУ. Работа блоков 3.1-3.К МПУ не изменяется. Если при переходе в режим записи в системе реализовался режим восстановления, то счетчик 16 остается в прежнем состоянии. Это обусловлено наличием единичного запрещающего сигнала на выходе элемента ИЛИ 51, который поступает на инверсный вход управления счетчика 16 и вход запрета элемента И 44. Концом работы в данном режиме является появление на выходе 72 единичного сигнала Конец записи. По это- му сигналу триггеры 12.1-12.К регистра 12 устанавливаются в нулевое состояние. Если продолжается к этому времени работа хотя бы одного из блоков 3.1-3. К МПУ либо если система перешла в режим записи, прервав восстановление работы одного из блоков 3.1-3.К МПУ, то с появлением на выходе элемента ИЛИ 46 нулевого сигнала и единичного на выходе элемента ИЛИ 49 система переходит в режим 3.

Режим 5. В данный режим система переходит при работе в режиме 3 или 4. Пусть система Функционирует в режиме 4. Система переходит в режим 5 при появлении на одном из выходов 66.1-66.К группы 36 элементов И единичного сигнала. В результате этог соответствующий триггер K.I регистре 1- переходит е единичное состояние. На выходе элемента ИЛИ-НЕ 52 появляется нулевой сигнал. Этот сигнал по- „-.етс я РГ гхог- б/, о к с 5 синхронизации. Пр;- это запрещается прохождение через элементы И 87, 8о блока 5 синхронизации синхроимпульсов ri на входы синх- ронизэг-.--- регистру 5 здресг v, регистра 7 МК. разрешается прохождение синхроимпульсов г/1 через элемент И 88 на первый БХО.Г регистра 7 МК. Работе узлов верхнего УРОЕНЯ системы блокируется. Работа блоков и узлов среднего и нижнего уровней не из- меняется. Концом работы Е данном режиме является появление на соответствующем выходе 70.1-70.К группы 39 элементов И единичного сигнала Конец операции блока З.М МПУ. По этому сигналу происходит обнуление регистра 10.М, триггера 13.М регистра 13 и триггера 14.М регистра 14. После обнуления триггера 14.М на выходе элемента ИЛИ-НЕ 52 появляется единичный сигнал. Этот сигнал подается чере вход запрета блока 5 синхронизации на уг равляющие входы элементов И 87, 86, №. разрешая прохождение синхроимпульсе Л на вход синхронизации регистра 6, запре щая прохождение синхроимпульсов n Hi нулевой вход регистра 7 и разрешая про хождение синхроимпульсов гг на вход син хронизации регистра 7.

По заднему фронту синхроимпульса TZ в регистр 7 записывается считанная из блока ПЗУ 1 МК микрокоманда, а по заднему фронту синхроимпульса т в регистр б записывается адрес следующей микрокоманды. Далее работа системы продолжается по режиму 4.

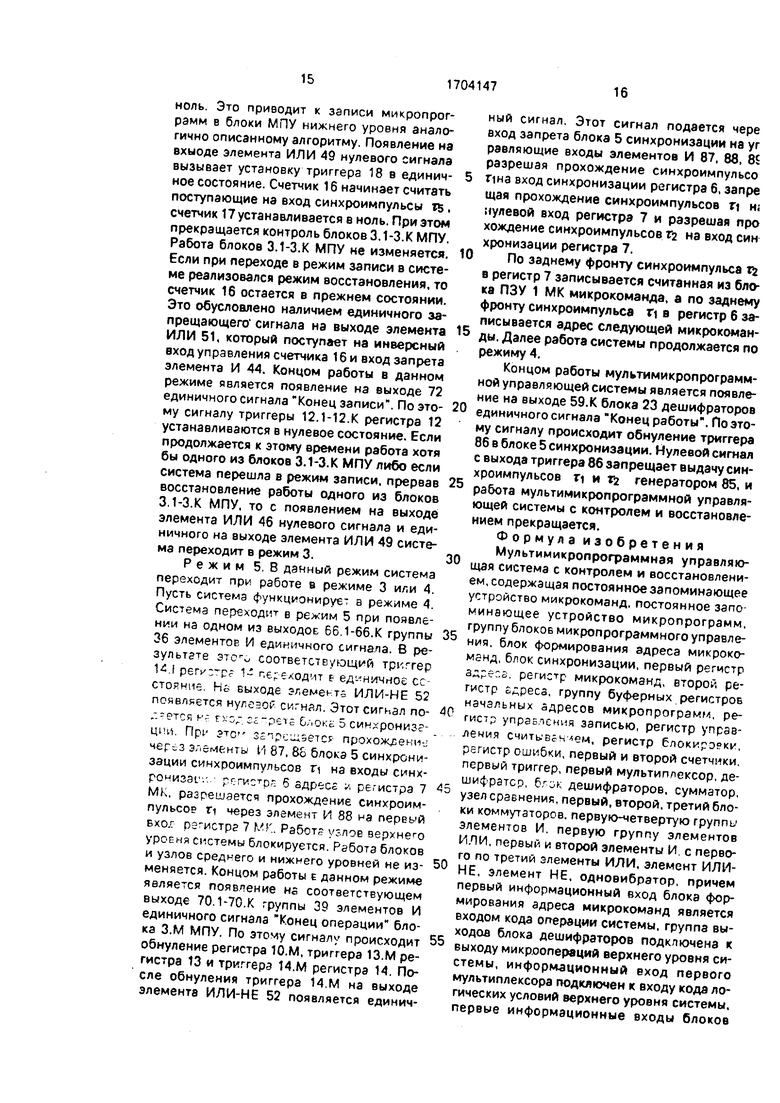

Концом работы мультимикропрограмм- ной управляющей системы является появление на выходе 59.К блока 23 дешифраторов единичного сигнала Конец работы. Поэтому сигналу происходит обнуление триггера 86 в блоке 5 синхронизации. Нулевой сигнал с выхода триггера 86 запрещает выдачу синхроимпульсов TI и TZ генератором 85, и работа мультимикропрограммной управляющей системы с контролем и восстановлением прекращается.

Формула изобретения

Мультимикропрограммная управляющая система с контролем и восстановлением, содержащая постоянное запоминающее устройство микрокоманд, постоянное запоминающее устройство микропрограмм, группу блоков микропрограммного управления, блок формирования адреса микрокоманд, блок синхронизации, первый регистр адрег.3, регистр микрокоманд, второй регистр еАресз, группу буферных регистров начальных адресов микропрограмм, регистр управления записью, регистр управления считыванием, регистр блокироеки, регистр ошибки, первый и второй счетчики, первый триггер, первый мультиплексор, дешифратор, б,г 0к дешифраторов, сумматор, узел сравнения, первый, второй, третий блоки коммутаторов, первую-четвертую группы элементов И. первую группу элементов ИЛИ, первый и второй элементы И. с первого по третий элементы ИЛИ, элемент ИЛИ- НЕ, элемент НЕ. одновибрэтор, причем первый информационный вход блока формирования адреса микрокоманд является входом кода операции системы, группа выходов блока дешифраторов подключена к выходу микроопераций верхнего уровня системы, информационный вход первого мультиплексора подключен к входу кода логических условий верхнего уровня системы, первые информационные входы блоков

микропрограммного управления группы подключены к группе входов кодов логических условий нижнего уровня системы, вход управления блока синхронизации подключен к входу пуска системы, выход блока формирования адреса микрокоманд соединен с информационным входом первого регистра адреса, выход которого соединен с адресным входом постоянного запоминающего устройства микрокоманд, выход которого соединен с первым и вторым информационными входами регистра микрокоманд, выход адреса которого соединен с вторым информационным входом блока формирования адреса микрокоманд, первый управляющий вход которого соединен с выходом первого элемента И первой группы, выходы элементов И первой группы соединены с входами блока дешифраторов, первый выход которого соединен с первым входом останова блока синхронизации, вход запрета работы которого соединен с выходом элемента ИЛИ-НЕ, входы которого соединен с выходами регистра блокировки, выход поля логических условий регистра микрокоманд соединен с управляющим входом первого мультиплексора, выход которого соединен с входом модифицируемого разряда адреса блока формирования адреса микрокоманд, операционный выход регистра микрокомнад соединен с первыми входами элементов И первой и второй групп, выход признака метки регистра микрокоманд соединен со вторыми входами элементов И первой и с инверсными входами элементов И второй групп, выходы которых соединены с первыми входами элементов ИЛИ первой группы, выходы которых соединены с информационными входами второго регистра адреса и информационными входами буферных регистров начальных адресов микропрограмм группы, информационные выходы второго регистра адреса соединены с первыми информационными входами первого блока коммутаторов, информационные выходы которого соединены с адресными входами постоянного запоминающего устройства микропрограмм, группа адресных выходов которого соединена с вторыми входами элементов ИЛИ первой группы, группа выходов микроопераций, постоянного запоминающего устройства микропрограмм соединена с первыми входами элементов И третьей группы, выходы которых соединены с вторыми информационными входами блоков микропрограммного управления группы, информационные выходы которых соединены с информационными входами второго блока коммутаторов, выход которого соединен с первым входом узла сравнения, информационные выходы буферных регистров начальных адресов микропрограмм группы соединены с информационными входами 5 третьего блока коммутаторов, выход которого соединен с первым входом сумматора, группа выходов которого соединена с второй группой информационных входов первого блока коммутаторов, прямые выходы

0 регистра управления записью соединены с входами первого элемента ИЛИ и с входами управления записью блоков микропрограммного управления группы, прямые выходы регистра управления, считыванием

5 соединены с первыми прямыми входами элементов И четвертой группы и с входами управления считыванием блоков микропрограммного управления группы, выход первого элемента ИЛИ соединен с управля0 ющим входом первого блока коммутаторов, с вторыми входами элементов И третьей группы, с инверсными входами элементов И четвертой группы, выходы которых соединены с управляющими входами третьего блока

5 коммутаторов, входами второго элемента . ИЛИ, информационными входами регистра ошибки и с управляющими входами второго блока коммутаторов, выход второго элемента ИЛИ соединен с управляющим входом

0 узла сравнения, входом одновибратора, входом элемента НЕ. выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом установки в единицу первого триггера, пря5 мой выход которого соединен с входом установки в ноль первого счетчика и первым входом первого элемента И, выход которого соединен со счетным входом второго счетчика, выход которого соединен с входом де0 шифратора, выходы дешифратора соединены с вторыми прямыми входами элементов И четвертой группы, инверсный выход первого триггера соединен с первым входом второго элемента И, выход которого

5 соединен со счетным входом первого счетчика, выход переполнения которого соединен с вторым входом третьего элемента ИЛИ, первый выход блока синхронизации соединен с входом синхронизации первого

0 регистра адреса, второй выход блока синхронизации соединен с входом установки в ноль регистра микрокоманд, третий выход блока синхронизации соединен с первым и вторым входами синхронизации регистра

5 микрокоманд, четвертый выход блока синхронизации соединен с входом синхронизации второго регистра адреса, пятый выход блока синхронизации соединен с входами синхронизации блоков микропрограммного управления группы и с вторым входом егорого элемента И, шестой выход блока синхронизации соединен с вторым входом первого элемента И, выход признака конца записи постоянного запоминающего устройства микропрограмм соединен с входами признаков конца записи блоков микропрограммного управления группы, отличающаяся тем, что. с целью повышения отказоустойчивости, в нее введены буферный регистр микрокоманд, третий регистр адреса, второй триггер, второй мультиплексор, четвертый блок коммутаторов, группа блоков коммутаторов микроопераций, с пятой по девятую группы элементов И; сумматор по модулю два, третий элемент И четвертый-шестой элементы ИЛИ, причем выход признака конца записи постоянного запоминающего устройства микропрограмм соединен с первыми входами элементов И пятой группы, выход микрокоманд постоянного запоминающего устройства микропрограмм соединен с первым входом сумматора по модулю два и с информационным входом буферного регистра микрокоманд, выход которого соединен с вторым входом узла сравнения и с первым входом блоков коммутаторов микроопераций группы, выход поля адреса буферного регистра микрокоманд соединен с информационными входами третьего регистра адреса, выход поля логических условий буферного регистра микрокоманд соединен с управляющим входом второго мультиплексора, выход которого соединен с первым входом четвертого элемент ИЛМ, второй вход которого соединен с вь хост модифицируемого разряда адреса п:; Я адреса буферного регистра микрскс ; -д. выход четвертого элемента ИЛИ соединен с информационным входом модифицированного разряда третьего регис-рг гдресг, информационна ; еь- ход соединен с первым входом элементе ИЛИ второй группы, выходы которых соединены с вто- РУМ входом сумматора, еторьте зходы элементов ИЛИ второй группы соединены с первым выходом второго блока коммутаторов, вход логических условий нижнего уровня спермы соединен с информационным входов четвертого блока коммутаторов, выход которого соединен с информационным г ходом второго мультиплексоре, выход поля ;реса и выход контрольного разряда по- wiosHHorc запоминающего устройства микропрограмм соединены соответственно с ьторым и третьим входами сумматора по модулю два. выход которого соединен с информационным входом второго триггера, прямой выход которой является выходом отказа системы и соединен с вторым входом

останова блока синхронизации. седьм выход которого соединен с первыми вход ми элементов И шестой группы, выходы к торой соединены с входами остановки ноль регистра управления считыванием, pi гистра блокировки, буферных регистров н чальных адресов микропрограмм , регистр ошибки и с входами пятого элемента ИЛ1/ выход которого соединен с входами уста новки в ноль буферного регистра микроко манд, третьего регистра адреса и с третье входом третьего элемента ИЛИ, выход пер вого элемента ИЛИ соединен с инверсным управляющим входом буферного регистра микрокоманд, вход узла сравнения соединен с управляющим входом буферного регистра микрокоманд, выход узла сравнения соединен с управляющим входом регистра ошибки, выход которого является выходом ошибки системы и соединен с управляющим входом четвертого блока коммутаторов, управляющими входами блоков коммутаторов микроопераций группы и с входами шестого элемента ИЛИ, выход которого соединен с инверсным управляющим входом второго блока коммутаторов, первым входом третьего элемента И, инверсным входом второго элемента И и инверсным управляющим входом второго счетчика, выходы блоков коммутаторов микроопераций группы являются выходами микроопераций нижнего уровня системы, выходы групп разрядов блоков коммутаторов микроопераций группы соединены с первыми входами элементов И шестой группы, выходы элементов И второй трупы соединень с переыми входами элементов И седс - Си группы, выходы которых соединены с Блсдами установки в единицу регистра блокировки, выходы элементов И второй соединены с первыми входами четных элементов И пятой группы, выхо- дь- которых соединены с входами установки в единицу регистра управления записью, выходы элементов V tторой группы соединены с первыми входами элементов И восьмой и девятой групп, выходы элементов И восьмой груг.лы соединены с входами установки в единицу регистра управления считыванием, РЫХОДЫ элементов И девятой трупы соединены с входами синхронизации буферных регистров начальных адресов микропрограмм трупы, информационные выходы блоков микропрограммного управления группы соединены с вторыми информационными входами блоков коммутаторов микроопераций гурппы. третий выход блока синхронизации соединен с входами синхронизации регистра ошибки, четвертый выход блока синхронизации соединен с вторыми входами элементов И с седьмой по девятую

групп, с вторыми входами четных элементов И пятой группы и вторым входом третьего элемента И, выход которого соединен с входом синхронизации третьего регистра адреса, пятый выход блока синхронизации соединен с входами синхронизации второго

триггера и буферного регистра микрокоманд и с вторыми входами нечетных элементов И пятой группы, выходы которых соединены соответственно с входами установки в ноль регистра управления записью.

r- т

«т о

гts Чэ «V Па

16

L

я

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве управляющей подсистемы в высо- коимпедансных системах контроля и управления сбором и обработкой информации. Цель изобретения - повышение отказоустойчивости системы за счет восстановле- ния работоспособности блоков микропрограммного управления при сбоях и отказах. Система содержит постоянные запоминающие устройства микрокоманд и микропрограмм, группу блоков микропрограммного управления, блок формирования адреса, блок синхронизации, первый регистр адреса, регистр микрокоманд, второй регистр адреса, буферный регистр микрокоманд, группу буферных регистров начальных адресов микропрограмм, третий регистр адреса, регистр управления записью, регистр управления считыванием, регистр блокировки, регистр ошибки, первый и второй счетчики, первый и второй триггеры, первый и второй мультиплексоры, дешифратор, блок дешифраторов, сумматор, узел сравнения, первый, второй и четвертый блоки коммутаторов, группу блоков коммутаторов микроопераций, второй блок коммутаторов, с первой по девятую группы элементов И, две группы элементов ИЛИ, сумматор по модулю два с первого по третий, элементы И с первого по шестой элементы ИЛИ, элемент ИЛИ-НЕ, элемент НЕ. одновибратор. Повышение отказоустойчивости системы происходит за счет обеспечения возможности восстановления работоспособности блоков микропрограммного управления нижнего уровня при отказах и сбоях за счет использования естественной структурной и временной избыточности, обусловленной наличием копий всех микропрограмм нижнего уровня и простоями запоминающего устройства микропрограмм, и результатов контроля работы блоков микропрограммного управления. 9 ил. Ј 1 О N Ј vj

tj trifb

Ј M(D

ifrltrOZ.1

u..&§

355а§|;з 5

Ј

ig

ix

j 2

/remmmmmx

3 У режим5режим

®иг.8

ял

/та

-4

АЛЛ

ПП

ПП

П П ТП

П П НШПШМПШШ

УГУУГУШУУШ

1 режим

Фи г. 9

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-07—Публикация

1988-10-19—Подача