Изобретение относится к аналоговой и аналого-цифровой (гибридной) вычислительной технике и может быть применено при моделировании систем автоматического управления

Целью изобретения является повышение быстродействия

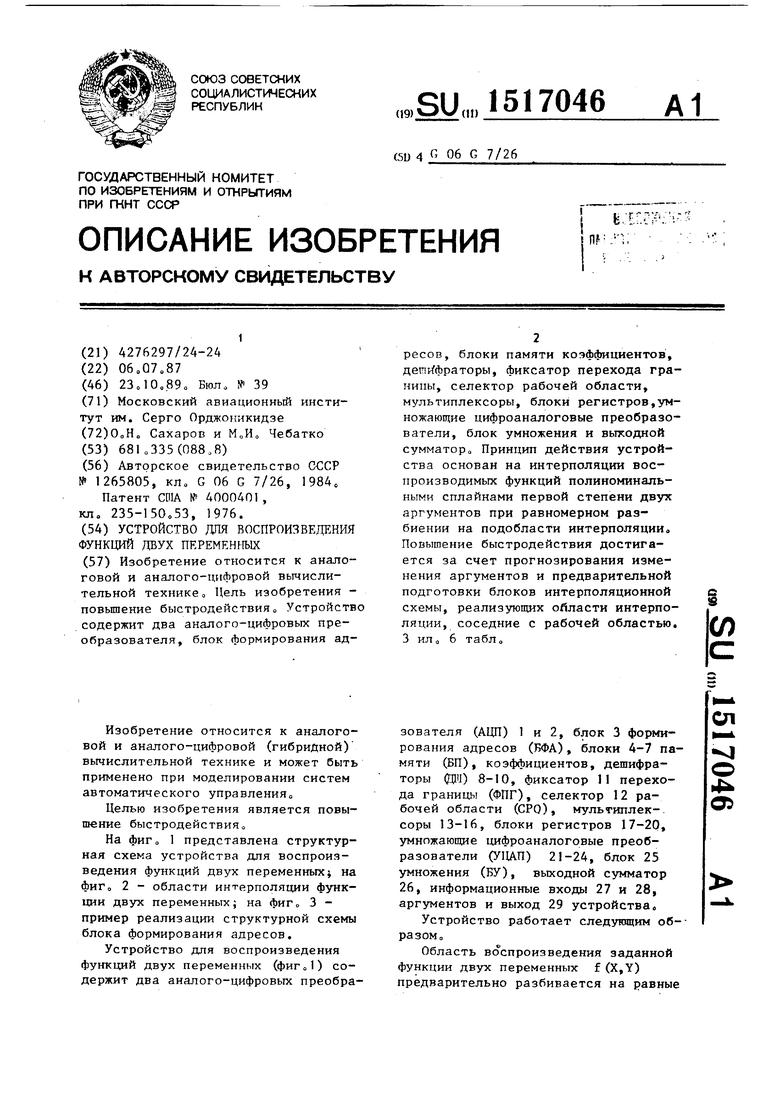

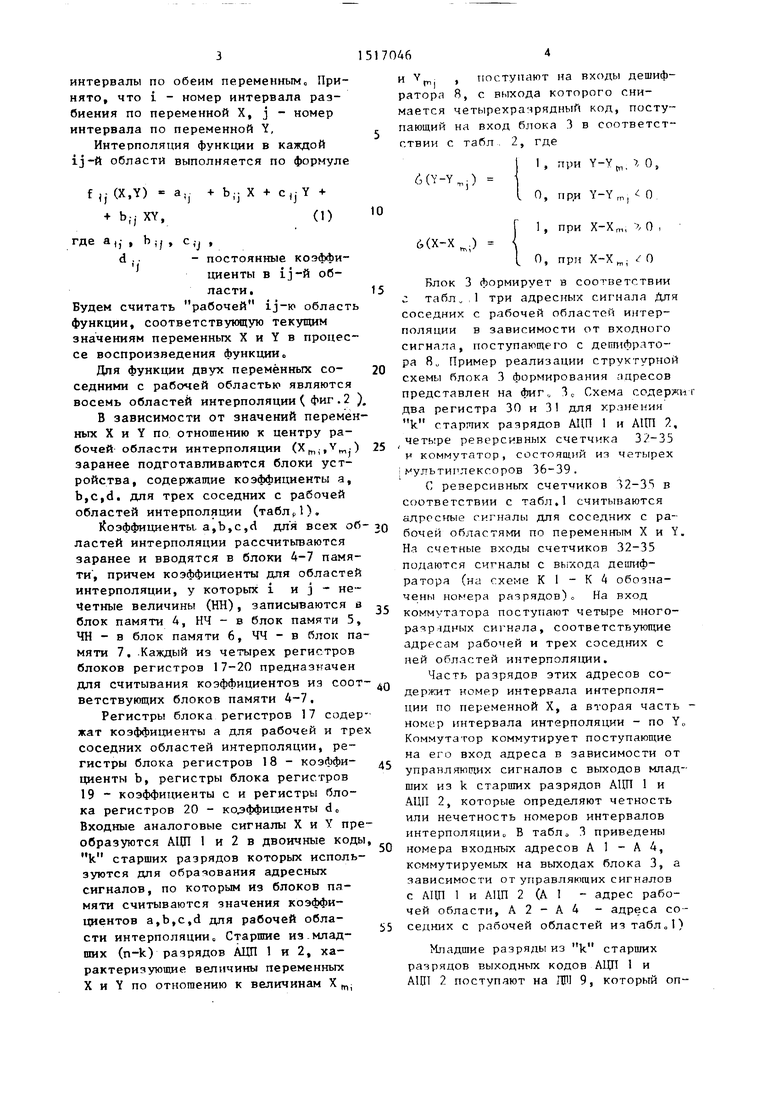

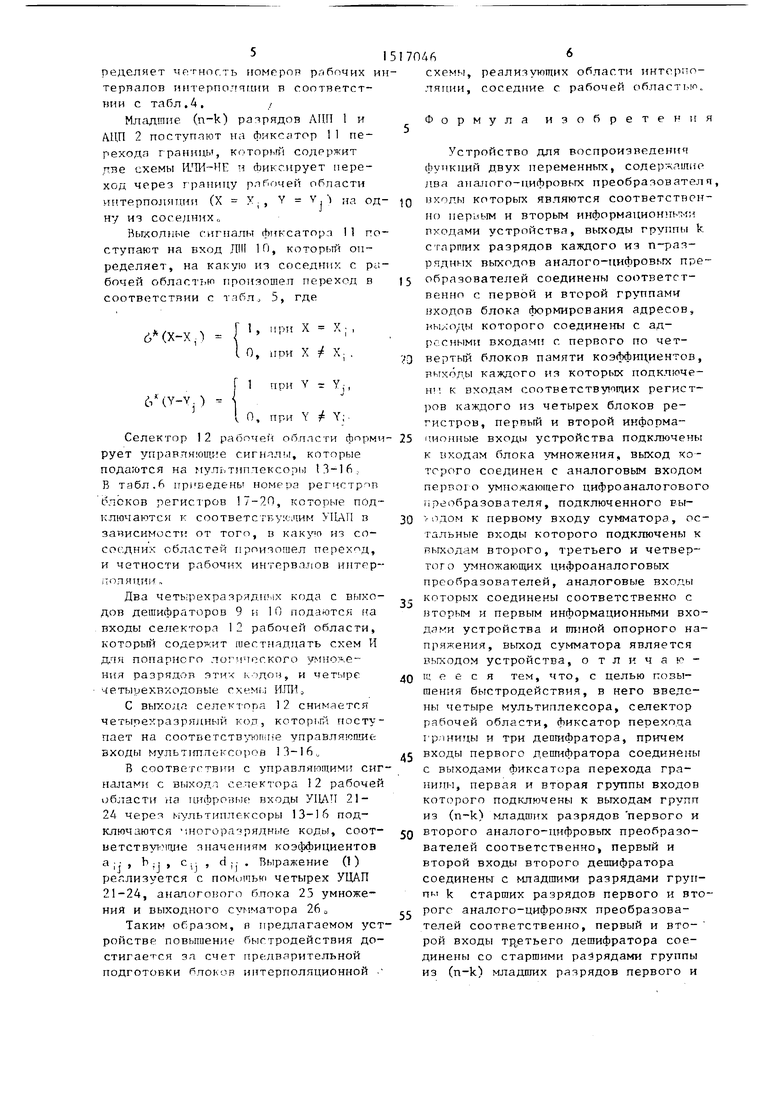

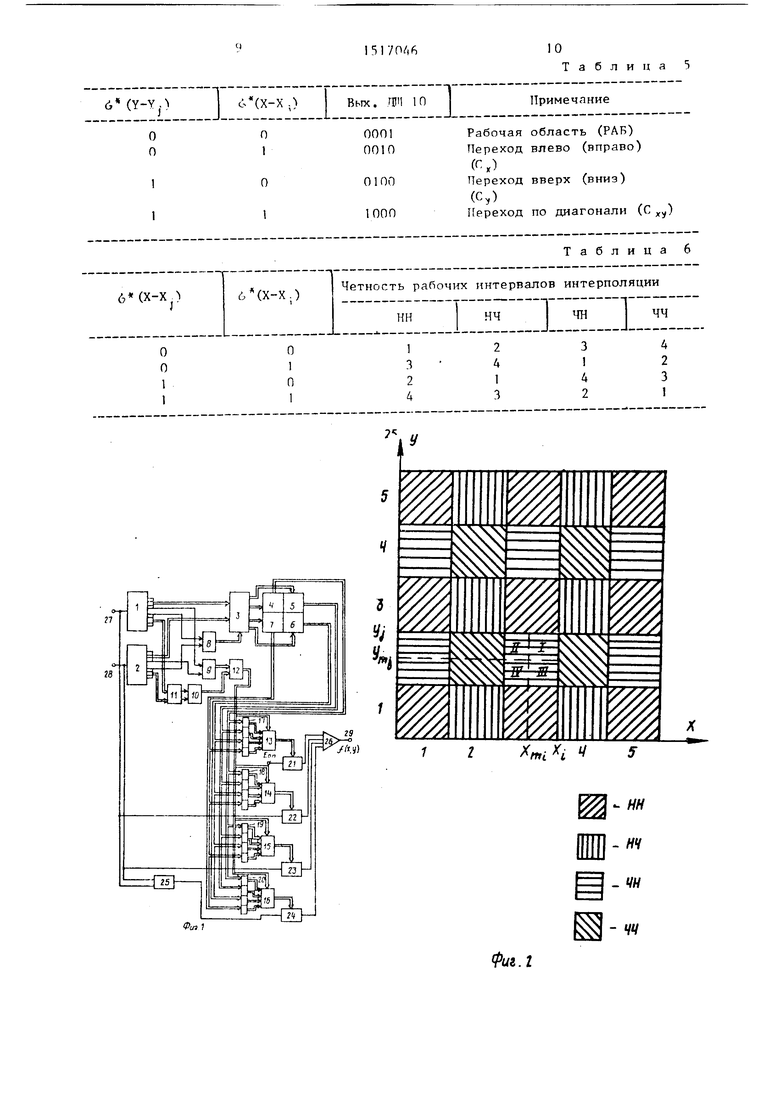

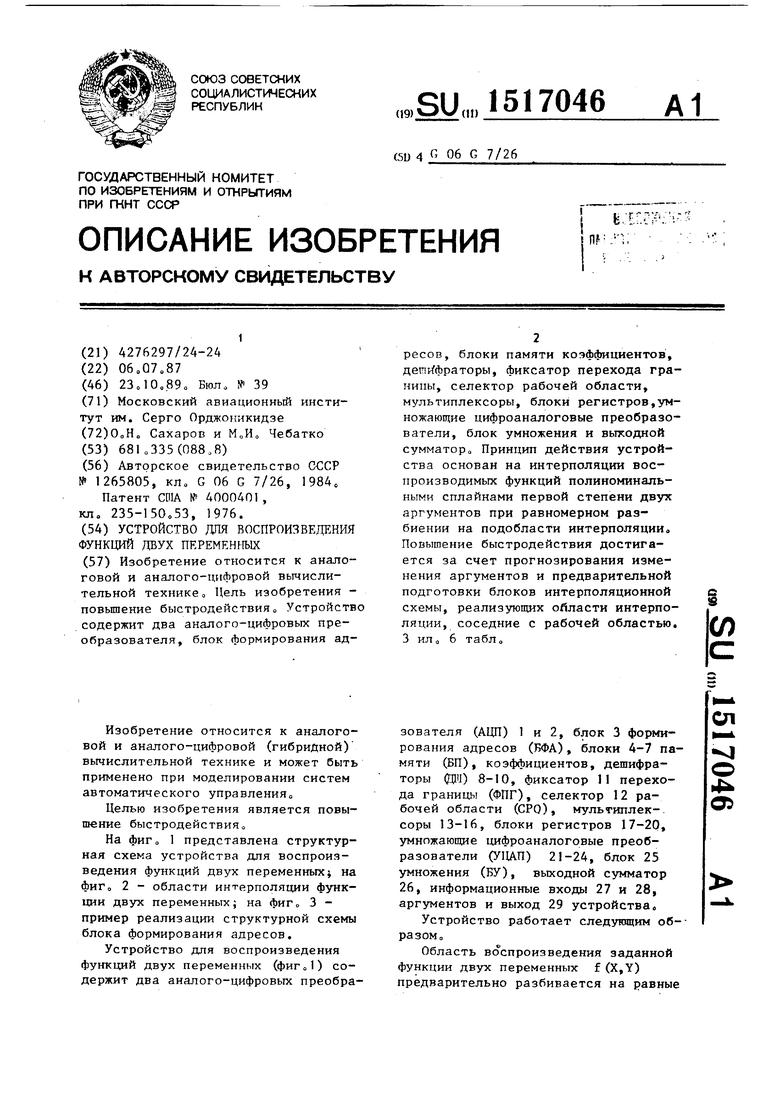

На фиг о 1 представлена структурная схема устройства дпя воспроизведения функций двух переменных; на фиг о 2 - области интерполяции функции двух переменных; на фиг 3 - пример реализации структурной схемы блока формирования адресов.

Устройство для воспроизведения функций двух переменных (фиг) содержит два аналого-цифровых преобразователя (АЦП) 1 и 2, блок 3 формирования адресов (БФА), блоки 4-7 памяти (БП), коэффициентов, дешифраторы (ДШ) 8-10, фиксатор 11 перехода границы (ФПГ), селектор 12 рабочей области (СРО), мультиплек-- соры 13-16, блоки регистров 17-20, умножающие цифроаналоговые преобразователи (УЦАП) 21-24, блок 25 умножения (БУ), выходной сумматор 26, информационные входы 27 и 28, аргументов и выход 29 устройства

Устройство работает следунлцим об-- разомо

Область воспроизведения заданной функции двух переменных f (X,Y) предварительно разбивается на равные

СЛ

О 4 05

интервалы по обеим переменным,, Принято, что i - номер интервала разбиения по переменной X, j - номер интервала по переменной Y,

Интерполяция функции в каждой ij-й области выполняется по формуле

f ,.(X,Y) а., -h Ъ.. X + c,jY

+ b.-jXY,(1)

Ч

где а,- , hjj , с ,.j ,

- постоянные коэффициенты в ij-й области. Будем считать рабочей ij-ю область функции, соответствующую текущим значениям переменных X и Y в процессе воспроизведения функции о

Для функции двух переменных со- седними с рабочей областью являются восемь областей интерполяции ( фиг.2 ) В зависимости от значений переменных X и Y по, отношению к центру рабочей области интерполяции (,V.) заранее подготавливаются блоки устройства, содержащие коэффициенты а, b,c,d. для трех соседних с рабочей областей интерполяции (.

Коэффициенты. a,b,c,d для всех об ластей интерполяции рассчитьтаются заранее и вводятся в блоки 4-7 памяти , причем коэффициенты для областей интерполяции, у которых i и j - нечетные величины (НН), записываются в блок памяти 4, НЧ - в блок памяти 5, ЧН - в блок памяти 6, ЧЧ - в блок памяти 7, .Каждый из четырех регистров блоков регистров 17-20 предназначен для считывания коэффициентов из соот ветствующих блоков памяти 4-7,

Регистры блока регистров 17 содержат коэффициенты а для рабочей и тре соседних областей интерполяции, регистры блока регистров 18 - коэффи- циенты Ь, регистры блока регистров 19 - коэффициенты с и регистры блока регистров 20 - коэффициенты d Входные аналоговые сигналы X и Y преобразуются АЦП 1 и 2 в двоичные коды k старших разрядов которых используются для образования адресных сигналов, по которым из блоков памяти считываются значения коэффи- Щ1ентов a,b,c,d для рабочей области интерполяции о Старшие из.младших (n-k) разрядов АЦП 1 и 2, характеризующие величины переменных X и Y по отношению к величинам X

и Y , поступают на входы дешифратора 8, с выхода которого снимается четырехразрядный код, поступающий на вход блока 3 в соответст- ствии с табл , 2, где

6a-Y.)

1. при Y-Y,0, при Y-Y,,, i О,

О

1 , при Х-Х„„ / О ,

с Q

0

5

6(Х-Х.)

О, при Х-Х„; го

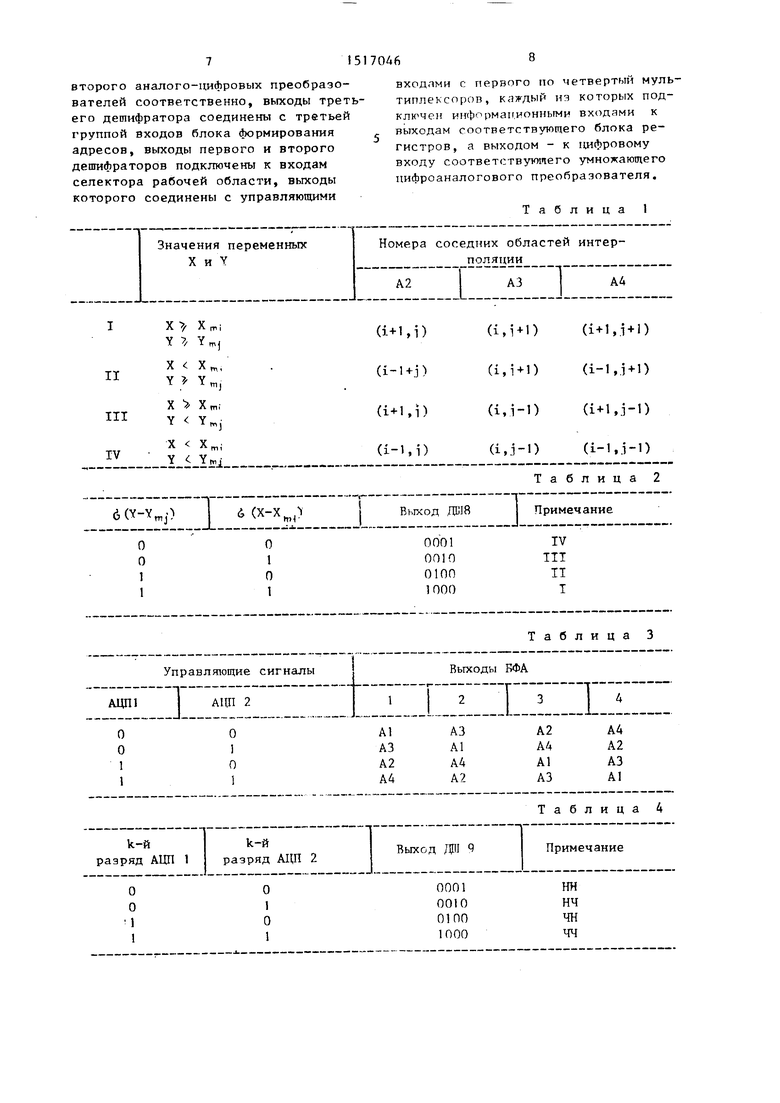

Влок 3 формирует в соответствии с табл„ ,1 три адресных сигнала Для соседних с рабочей областей И1{тер- поляции в зависимости от входного сигнала, поступающего с дешифратора 8„ Пример реализации структурной схемы блока 3 формирования адресов представлен на фиг„ 3 Схема содержит два регистра 30 и 31 для хранения k стартяих разрядов АЦП 1 и А1Ш ., четьфе реверсивных счетчика 32-35 и коммутатор, состоящутй из четырех мультигътексоров 36-39.

С реверсивных счетчиков 32-3S в соответствии с табл,1 считываются адресные сигналы для соседних с рабочей областями по переменным X и Y. На счетные входы счетчиков 32-35 подаются сигналы с выхода дешифратора (на схеме К 1 - К 4 обозначены разрядов) На вход коммутатора поступают четыре много- разр-щных сигнала, соответствующие адресам и трех соседних с ней областей интерполяции.

Часть разрядов этих адресов содержит номер интервала интерполяции по переменной X, а вторая часть номер интервала интерполяции - по Y,, Коммутатор коммутирует поступающие на его вход адреса в зависимости от управляющих сигналов с выходов младших из k старших разрядов А1Щ 1 и АЦП 2, которые определяют четность или нечетность номеров интервалов интерполяции с, В табл 3 приведены номера входных адресов А 1 - А 4, коммутируемых на выходах блока 3, а зависимости от управляющих сигналов с АЦП 1 и АПП 2 (А I - адрес рабочей области, А 2 - А 4 - адреса соседних с рабочей областей из табЛо)

Младшие разряды из k старших разрядов выходных кодов АЦП 1 и АЩТ 2 поступают на ЯП 9, который определяет четность (гомеров рабочих териалов интерполяции в соответст- нии с табл.4, /

Младшие (n-k) разрядов ЛИП 1 и АЦП 2 поступают на фиксатор I1 перехода границы, который содержит две схемы и Ликсирует переход через т ранипу рабочей области

на од-

иг терполяпии (X Х, V vp ну из соседних,,

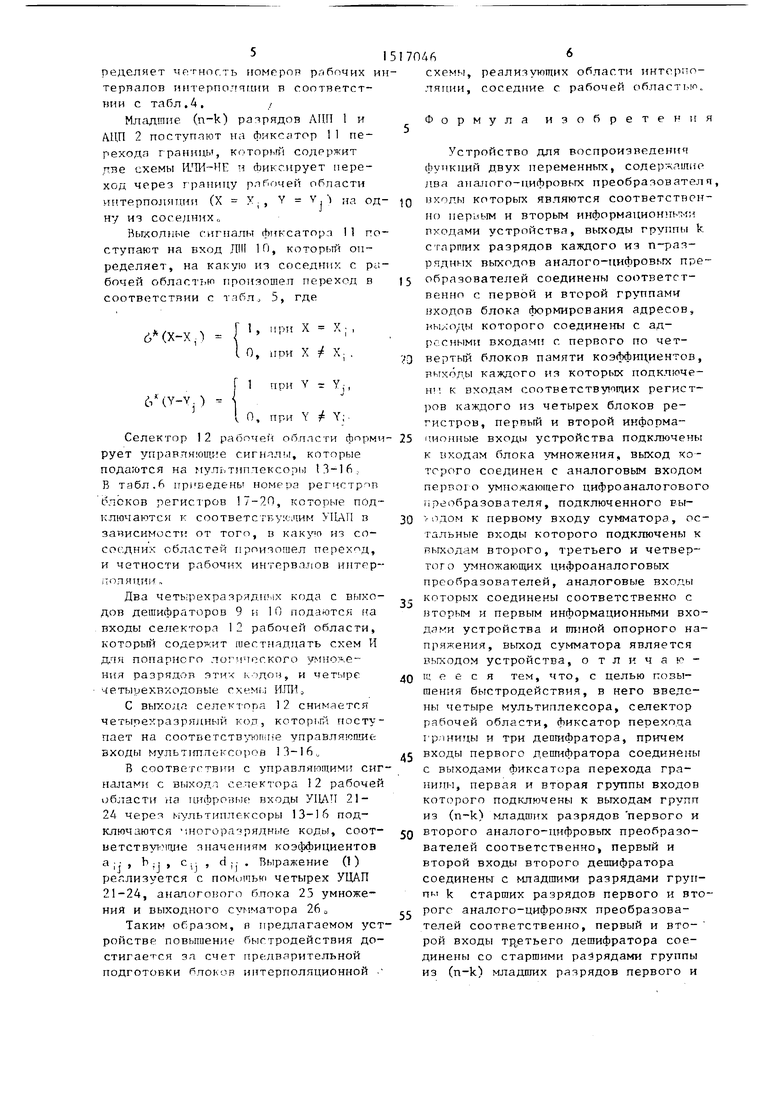

Выходные фиксатора I 1 поступают на вход ДШ 1Г), который определяет, на какую из соседних с pii- бочей областью произошел переход в соответствии с тлбл, 5, где

- V

1 , при X

О, при X У.1 пои Y - У;,

6(Y-Vj)

I О, при Y У;.

Селектор 12 рабочей области фпрми рует управляющие сигналы, которые подаются на мультиплексоры 13-16; В табл.6 пр)шедены номера регистрпв L iOKOB регистров 17-20, которые подключаются к соответстБу; - Лим УИАП в зависимости от того, в из со- соедних областей произошел переход, и четности рабочих интервалов ннтерП 1ЛЯТП И „

Два четь;рехразряд,1ых кода с BFJKO- дов дешифраторов 9 и 10 подаютс ; на входы селектора 12 рабочей области, которьш содержит шестнадцать схем PI для попарного логического ,e- нпя разрядов этих кодой, и четыре четыиехвходовые схемг, ИЛИ

С выхода селектора 12 снимается четырехразрядный код, который поступает на cooTDeTCTB- jjTiiriJlie управляюпше входр мульт1тлексоров 13-16„

В соответствии с управляющими сигналами с выходл селектора 12 рабочей области на uncbpOHtiie входы УЦАП 21- 24 через мультиплексоры 13-16 подключаются многоразрядные коды, соот- ветствун щце значениям коэффициентов а - , Ь ;j , Cjj , d;j , Выражение (1) реализуется с помишью четырех УЦАП 21-24, аналогового блока 25 умноже26.

НИИ и выходного сумматора

Таким образом, в предлагаемом устройстве повышение быстродействия достигается за счет прелварительной подготовки блоков интерполяционной .

Q

5

O

0

5

5

схемы, реализующих области интерпо- лягшн, соседние с рабочей областт-ю,.

Формула изобретения

Устройство для воспроизведения функций двух переменных, содержащие два аналого-цифровых преобразователя, входы которых являются соответственно периым и вторым информационпь ми пходами устройства, выходы группы k старптх разрядов каждого из п-раз- рядных выходов аналого-цифровых преобразователей соединены соответственно с первой и второй группами входов блока формирования адресов, выходы которого соединены с адресными входами с первого по четвертый блоков памяти коэффициентов, выходы каждого из которых подключе- н к входам соответствующих регист- ров каждого из четырех блоков регистров, первый и второй информа- пиорп1ые входы устройства подключены к входам блока умножения, выход которого соединен с аналоговым входом первого умножающего цифроаналогового преобразователя, подключенного ЕЫ- одом к первому входу сумматора, остальные входы которого подключены к выходам второго, третьего и четвертого yмнoжaюш x цифроаналоговых преобразователей, аналоговые входы которых соединены соответственно с вторым и первым информационными входами устройства и шшой опорного напряжения, выход сумматора является вьгходом устройства, о тличаю- 1 е е с я тем, что, с целью повышения быстродействия, в него введены четыре мультиплексора, селектор рабочей области, фиксатор перехода грпницы и три деп51фратора, причем 5 входы первого дешифратора соединены с выходами фиксатора перехода гра- пип.ы, первая и вторая группы входов которого подключены к выходам групп из (n-k) младших разрядов первого и второго аналого-цифровых преобразователей соответственно, первый и второй входы второго дешифратора соединены с младшими разрядами груп- пм k Старших разрядов первого и второго аналого-цифровгах преобразователей соответственно, первый и вто- рой входы тр етьего дешифратора соединены со старшими разрядами группы из (n-k) младших разрядов первого и

0

0

5

второго аналого-цифровых преобразователей соответственно, выходы третьего дешифратора соединены с третьей группой входов блока формирования адресов, выходы первого и второго дешифраторов подключены к входам селектора рабочей области, выходы которого соединены с управляющими

входпмн с первого по четвертый мультиплексоров, каждый нз которых под- ключе}) информап.ионными входами к выходам соответствующего блока ре гистров, а выходом - к 1Ц1фровому входу соответствуютего умножающего пифроаналогового преобразователя.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1509955A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для воспроизведения функций табличным методом | 1983 |

|

SU1153320A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1429139A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

Изобретение относится к аналоговой и аналого-цифровой вычислительной технике. Цель изобретения - повышение быстродействия. Устройство содержит два аналого-цифровых преобразователя, блок формирования адресов, блоки памяти коэффициентов, дешифраторы, фиксатор перехода границы, селектор рабочей области, мультиплексоры, блоки регистров, умножающие цифроаналоговые преобразователи, блок умножения и выходной сумматор. Принцип действия устройства основан на интерполяции воспроизводимых функций полиномиальными сплайнами первой степени двух аргументов при равномерном разбиении на подобласти интерполяции. Повышение быстродействия достигается за счет прогнозирования изменения аргументов и предварительной подготовки блоков интерполяционной схемы, реализующих области интерполяции, соседние с рабочей областью. 3 ил., 6 табл.

I

6(Y-Yn,p

Управляющие сигналы

Выход ДиШ

Примечание

Таблица 3

Выходы ВФА

Таблица 4

Таблица

1 ч 5- нн

- НЧ

. чн

- W

Фия.г

Фаг З

| Устройство для воспроизведения функций двух переменных | 1984 |

|

SU1265805A1 |

| Патент США № 4000401, кло 235-15а«53, 1976. | |||

Авторы

Даты

1989-10-23—Публикация

1987-07-06—Подача