счетчика, управляющий и счетный входы которого соединены соответственно с выходами второго сумматора по модулю два и второго управляемого делителя частоты, второй вход блока суммирования соединен с входом уменьшаемого пятого блока вычитания и выходом пятого реверсивного счетчика, управляющий и счетный входы которого соединены соответственно с выходом первого сумматора по модулю два и выходом третьего управляемого делителя частоты, входы разрешения записи коэффициента и счетные входы второго и третьего управляемых делителей частоты соединены соответственно с выходом обнуления второго блока вычитания и выходом элемента И, выход первого реверсивного счетчика соединен с входом уменьшаемого первого блока вычитания, выход обнуления которого соединен с управляющими входами первого и второго входных регистров, выходы старших разрядов которых соединены соответственно с адресными вхОхи.ами первого и второго блоков памяти, адресный вход третьего блока

памяти соединен с выходом дешифратора, второй вход которого соединен с выходом старших разрядов второго входного регистра, входы стробирования всех блоков памяти соединены с выходом обнуления второго блока вычитания, выход знака первого блока вычитания соединен с управляющим входом первого реверсивного счетчика и первыми входами второго и третьего сумматоров по модулю два, второй вход и выход последнего соединены соответственно с выходом знака второго блока вычитания и управляющим входом второго реверсивного счетчика, выход второго блока памяти соединен с входом вычитаемого пятого блока вычитания и входом уменьшаемого шестого блока вычитания, вход вычитаемого которого соединен с выходом третьего блока памяти, вторые входы первого и второго сумматоров по модулю два соединены с выходами знака соответственно пятого и шестого блоков вычитания, кодовые выходы которых соединены с входами коэффициента соответственно третьего и второго управляемых делителей частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Устройство для функционального преобразования цифровых сигналов | 1979 |

|

SU864293A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВУХ ПЕРЕМЕННЫХ, содержащий первый входной регистр, два блока вычитания, первый делитель частоты, первый управляемый делитель частоты, дешифратор, первый блок памяти, элемент И, элемент ИЛИ, два реверсивных счетчика и генератор импульсов, выход которого соединен с первым входом элемента И, выход которого соединен со счетным входом первого управляемого делителя частоты и через первый делитель частоты - со ечетным входом первого реверсивного счетчика, информационный вход, разрядный выход и выход старших разрядов первого входного регистра соединены соответственно с входом первого аргумента преобразователя, входом вычитаемого первого блока вычитания и первым входом дешифратора, выход первого блока вычитания и первым входом дешифратора, выход первого блока памяти соединен с входом вычитаемого второго блока вычитания, выход обнуления которого соединен с первым входом элемента ИЛИ и входом разрешения записи коэффициента первого управляемого делителя частоты, вход коэффициента и выход которого соединены соответственно с кодовым выходом второго блока вычитания и счетным входом второго реверсивного счетчика, выход которого соединен с входом уменьшаемого второго блока вычитания, второй вход элемента И соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом обнуления первого блока вычитания, отличающийся тем, что, с целью повышения точности путем возможности получения значений функции от двух аргументов методом двойной линейной интерполяции, в него введены блок суммирования, с третьего по шестой блоки вычитания, второй делитель частоты, второй и третий управляемые делители частоты, второй и третий блоки памяти, три сумматора по модулю два, с третьего по пятый реверсивные счетчики, второй входной регистр, два цифроаналоговых преобразователя, суммирующий усилитель и умножающий цифроаналоговы-й преобразователь, причем информационный вход и выход второго входного регистра соединены соответственно с входом второго аргумента преобразователя и входом уменьс шаемого третьего блока вычитания, вход S вычитаемого которого соединен с выходом ел третьего реверсивного счетчика, счетный вход которого соединен через второй делитель частоты с выходом элемента И, выход знака третьего блока вычитания соединенс первым входом первого сумматора по модулю два и управляющим входом третьего реверсивного счетчика, выход младших разрядов которого соединен с входом младших разрядов первого цифроаналогового преобраО5 зователя, вход старших разрядов и выход 00 которого соединены соответствено с входом со логического нуля устройства и аналоговым входом умножающего цифроаналогового Oi преобразователя, вход задания полярности, 4;: цифровой вход и выход которого соединены соответственно с выходом знака и кодовым выходом четвертого блока вычитания и первым входом суммирующего усилителя, выход и второй вход которого соединены соответственно с выходом преобразователя и выходом второго цифроаналогового преобразователя, вход которого соединен с выходом блока суммирования, первый вход которого соединен с выходом второго реверсивного счетчика и входом уменьшаемого четвертого блока вычитания, вход вычитаемого которого соединен с выходом четвертого реверсивного

1

Изобретение относится к автоматике и вычислителыюй технике и может быть использовано Е цифровых и аналого-цифровых вычислительных системах для воспроизведения функций двух переменных.

Цель изобретения - повышение точности путем возможности получения значений функции от двух аргументов методом двойной линейной интерполяции.

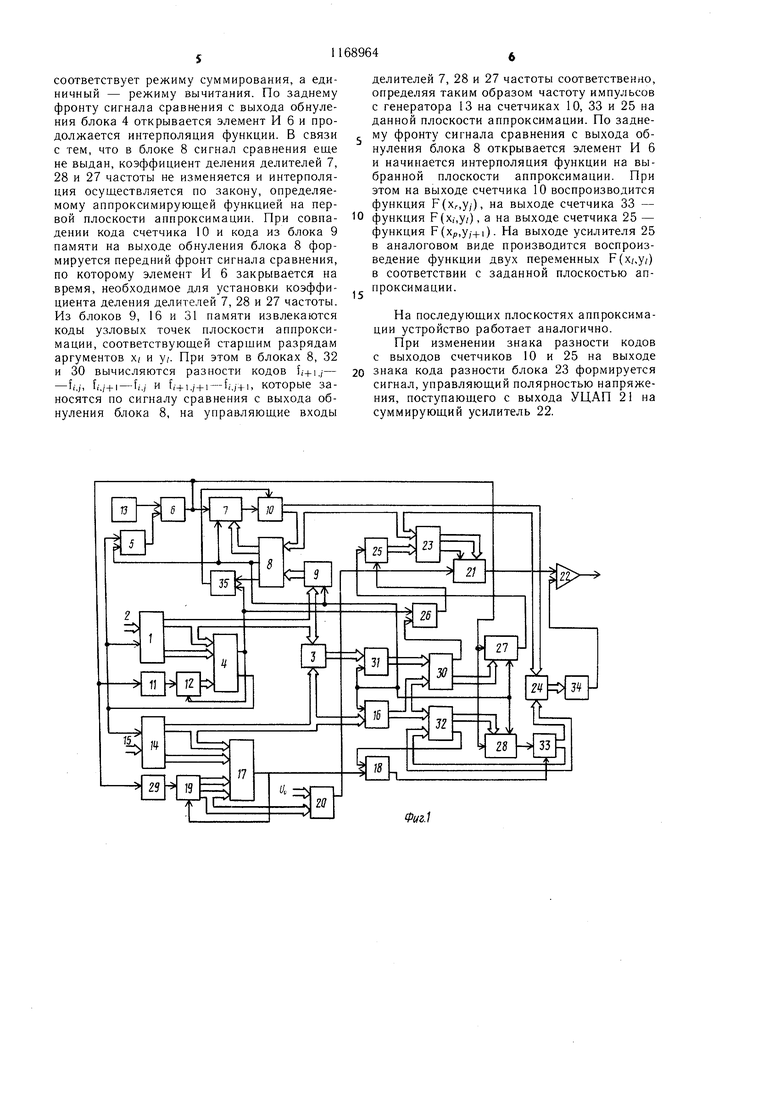

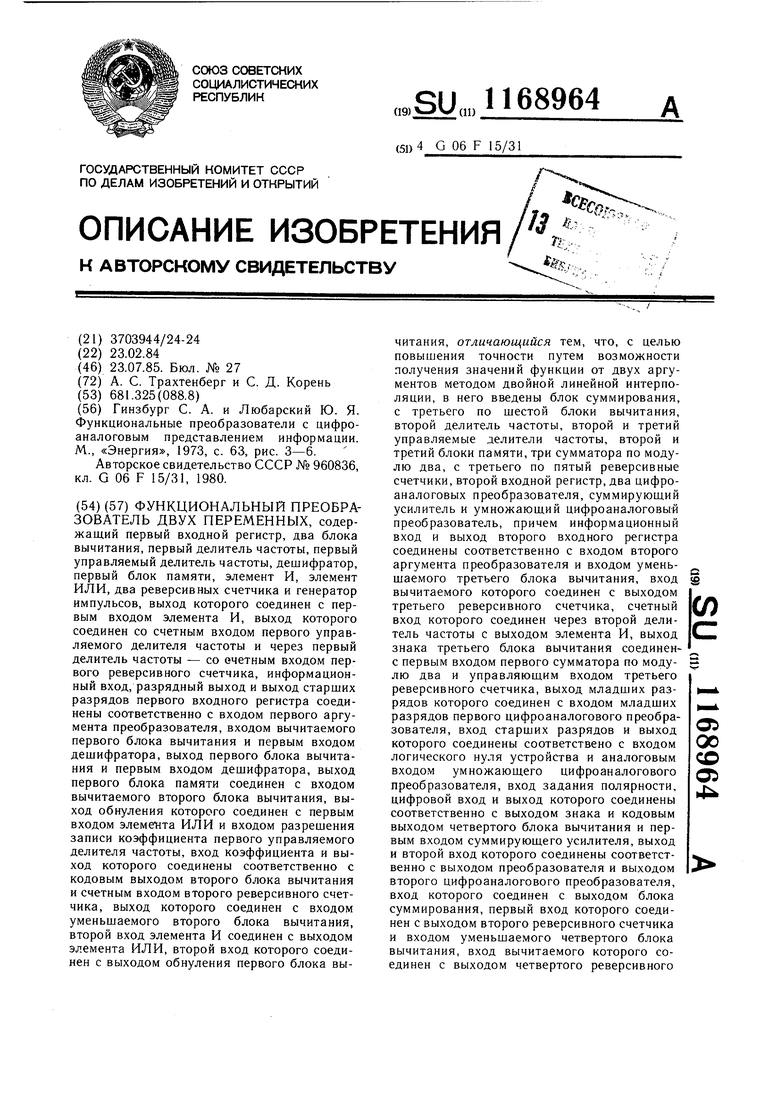

На фиг. 1 представлена блок-схема функционального преобразователя двух переменных; на фиг. 2 - интерполирующая поверхность для функции двух переменных на ij-M участке аппроксимации.

Функциональный преобразователь содержит входной регистр 1, шину 2 ввода первого аргумента, дешифратор 3, блок 4 вычитания, элемент ИЛИ 5, элемент И 6, управляемый делитель 7 частоты, блок 8 вычитания, блок 9 памяти, реверсивный счетчик 10, делитель 11 частоты, реверсивный счетчик 12, генератор 13 импульсов, входной регистр 14, шину 15 ввода второго аргумента, блок 16 памяти, блок 17 вычитания кодов, сумматор 18 по модулю два, реверсивный счетчик 19, цифроаналоговый преобразователь (ЦАП) 20, умножающий ЦАП (УЦАП) 21, суммирующий усилитель 22, блок 23 вычитания, блок 24 суммирования, реверсивный счетчик 25, сумматор 26 по модулю два, управляемые делители 27 и 28 частоты, делитель 29 частоты, блок 30 вычитания, блок 31 памяти, блок 32 вычитания, реверсивный

счетчик 33, второй ЦАП 34 и сумматор 35 по модулю два.

Устройство работает следующим образом.

Функциональный преобразователь восJ производит функции, которые приближаются следующей зависимостью:

Z,(X, y)P,(f,.+ ,.-f,.),-.;+,+

+ PI (,-+,,,+,-f,y+,)-Pi(f,-+.,/-f,M)-f.(1)

гдеPI - интерполирующий множи0тель по переменной х;

Р2 - интерполирующий множитель по переменной у;

fi,/, f,+ i,/,fi,y+i,f,-+i.;+i-КОДЫ узловых точвк аппроксимирующей поверхности.

Преобразуем формулу (1( следующим образо.м:

Z,,,(x,y) P,(f,+ ,,-f,)+p2(f,,/+,-- f/,) + Р2 Р 1 ( f,-+ I .у+ , - f/,,+ , ) -р-, ( f ,+ , j-f.-/)(2)

При этом Pi(f;+i,/-f,7) F(x,y/ - функция одной переменной х при на участке X(-f-Xi-)-i;

Pi(b+i.,-+,-f,j+i) F(x,y,-+i) - функция одной переменной х при ,ч.| на участке х,---x,-+i;

P2(f/,j-M-fi;) F(x;,y) - функция одной переменной у при , на участке ,ч-ь С учетом этого формула (2( примет вид: Z,(x,y) F(x,yy)-fF(x,,f) + (x,yy+,)-F)x,y,-).(3) Формула (3) описывает двойную линейную интерполяцию при которой, во-первых, производится интерполяция между узловыми точками fi+i./+i и f;,j+i, fi+1./ и f,-.,- по переменной X и между узловыми точками f;,;+i и f,/ по переменной у, а, во-вторых, интерполяция между результатами интерполяции по переменной х в зависимости от переменной у. Результатом интерполяции является линейчатая поверхность второго порядка, проходящая через все узлы области аппроксимации. В блоки 9, 16 и 31 памяти заносятся коды узловых точек fj+i,,-, f,,/-i-i и fi-M.y+i соответственно, причем в первую ячейку заносится нулевой код. Результаты преобразования функции двух переменных в соответствии с формулой (3) воспроизводятся на выходе суммирующего усилителя 22. При этом интерполяция между узловыми точками f,+i,/ и f,,y осуществляется с помощью блока 9 памяти, блока 8 вычитания, управляемого делителя 7 частоты и реверсивного счетчика 10, на выходе которого воспроизводится функция Р(х,у;). Интерполяция между узловыми точками f/,j+i и f, у осуществляется с помощью блока 16 памяти, блока 32 вычитания, управляемого делителя 28 частоты и реверсивного счетчика 33, на выходе которого воспроизводится функция F(x,-,y). Интерполяция между узловыми точками .,-)i и f;,j+i осуществляется с помощью блока 31 памяти, блока 30 вычитания, управляемого делителя 27 частоты и реверсивного счетчика 25, на выходе которого воспроизводится функция F(x,y/+i). На выходе блока 24 суммирования производится воспроизведение функции F(x,y,-)-|-F(x/,y). В блоке 23 вычитания осуществляется вычисление разности кодов F(x,y/+i)-F(x,y/), поступающих на цифровые входы УЦАП 21, на аналоговый вход которого поступает интерполирующий множитЁль Р2 с выхода ЦАП 20. Интерполирующий множитель Р2 в цифровом виде формируется на выходе младших разрядов реверсивного счетчика 19. На старщие разряды ЦАП 20 подается нулевой код для приведения его в соответствие с разрядностью УЦАП 21. Таким образом, на выходе УЦАП 21 воспроизводится функция (x,)-F(x,yj). Коэффициент деления делителей 11 и 29 частоты определяется числом интервалов по осям аргументов X и у. В исходном состоянии счетчики 10, 12, 19, 33 и 25, входные регистры 1 и 14 установлены в нуль, и нулевые коды с выходов регистров 1 и 14 поступают на входы дешифратора 3 и на адресные входы блоков 9 и 16 памяти. По нулевому адресному коду из первой ячейки блока 9 памяти извлекается нулевой код и на выходе обнуления блока 8 вычитания формируется передний фронт сигнала сравнения. Сигнал сравнения поступает через элемент ИЛИ 5 на вход элемента И 6, закрывая его на время установки коэффициентов деления делителей 7, 27 и 28 частоты, на вход разрешения записи управляемых делителей 7, 27 и 28 частоты, разрешая установку коэффициентов деления, на вход стробирования блоков 9, 16 и 31 памяти, разрешая прием адресных кодов из регистров 1 и 14 и дешифратора 3 соответственно. На выходе обнуления блока 4 вычитания формируется сигнал сравнения нулевых кодов реверсивного счетчика 12 и входного регистра 1 первого аргумента х, разрешающий прием аргументов в регистры 1 и 14. При поступлении на входы регистров 1 и 14 первого значения аргументов х и у из блоков 9 и 16 памяти по старшим разрядам кодов Xk и у аргументов извлекаются коды узловых точек f,o и fo, соответственно, а из блока 31 памяти с помощью дешифратора 3 - код узловой точки f,,. На выходе обнуления блока 4 формируется задний фронт сигнала сравнения, задержанный на время установки знака реверса счетчиков 10, 12, 19, 25 и 33. После поступления из блока 9 памяти в блок 8 вычитания значения функции f,o на выходе обнуления последнего вырабатывается задний фронт сигнала сравнения, задержанный на время, необходимое для установки коэффициента деления делителей 7, 27 и 28 частоты. По заднему фронту сигнала сравнения открывается элемент И 6 и импульсы с выхода генератора 13 поступают на счетные входы счетчиков 10, 12, 19, 33 и 25. Таким образом, начинается интерполяция функции на выбранной плоскости аппроксимации, причем частота импульсов с выхода генератора 13, поступающая на счетчики 10, 33 и 25, определяется коэффициентами деления делителей 7, 27 и 28 частоты. При этом коэффициент деления делителя 7 определяется разностью кодов f/o-foo сформированной на выходе кода разности блока 8; делителя 28 - разностью кодов fo/-In с выхода блока 32; а делителя 27 - разностью кодов f, с выхода блока 30. На выходе суммирующего усилителя 22 осуществляется воспроизведение функции двух переменных F(,k) соответствующих первой плоскости аппроксимации. При достижении счетчиком 12 кода аргумента Xk на выходе обнуления блока 4 формируется передний фронт сигнала сравнения, по которому закрывается элемент И 6 и разрешается прием очередных аргументов в регистры 1 и 14. При поступлении следующих кодов аргументов х/ и у/ в регистры 1 и 14 на выходе знака кода разности блоков 4 и 17 формируются сигналы, управляющие реверсом счетчиков 12 и 19 соответственно, и через сумматоры 35, 18 и 26 по модулю два - реверсом счетчиков 10, 33 и 25, причем нулевой код на выходе элементов 35, 26 и 18

соответствует режиму суммирования, а единичный - режиму вычитания. По заднему фронту сигнала сравнения с выхода обнуления блока 4 открывается элемент И 6 и продолжается интерполяция функции. В связи с тем, что в блоке 8 сигнал сравнения еще не выдан, коэффициент деления делителей 7, 28 и 27 частоты не изменяется и интерполяция осуществляется по закону, определяемому аппроксимирующей функцией на первой плоскости аппроксимации. При совпадении кода счетчика 10 и кода из блока 9 памяти на выходе обнуления блока 8 формируется передний фронт сигнала сравнения, по которому элемент И 6 закрывается на время, необходимое для установки коэффициента деления делителей 7, 28 и 27 частоты. Из блоков 9, 16 и 31 памяти извлекаются коды узловых точек плоскости аппроксимации, соответствующей старщим разрядам аргументов х/ и у/. При этом в блоках 8, 32 и 30 вычисляются разности кодов fi+i.y- -f;,/, f,-,/+i-f,,/ и f;+,,/+i -fi./4-i, которые заносятся по сигналу сравнения с выхода обнуления блока 8, на управляющие входы

делителей 7, 28 и 27 частоты соответственно, определяя таким образом частоту импульсов с генератора 13 на счетчиках 10, 33 и 25 на данной плоскости аппроксимации. По заднему фронту сигнала сравнения с выхода обнуления блока 8 открывается элемент И 6 и начинается интерполяция функции на выбранной плоскости аппроксимации. При этом на выходе счетчика 10 воспроизводится функция Р(Хл,у/), на выходе счетчика 33 - функция Р(х,-,у;), а на выходе счетчика 25 - функция F(xp,y|+i). На выходе усилителя 25 в аналоговом виде производится воспроизведение функции двух переменных F(x;,y/) в соответствии с заданной плоскостью аппроксимации.

На последующих плоскостях аппроксимации устройство работает аналогично.

При изменении знака разности кодов с выходов счетчиков 10 и 25 на выходе знака кода разности блока 23 формируется сигнал, управляющий полярностью напряжения, поступающего с выхода УЦАП 21 на суммирующий усилитель 22.

| Гинзбург С | |||

| А | |||

| и Любарский Ю | |||

| Я | |||

| Функциональные преобразователи с цифроаналоговым представлением информации | |||

| М., «Энергия, 1973, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-23—Подача