Изобретение относится к вычислительной технике и может быть использовано при создании полупроводниковых схем памяти.

Цель изобретения - упрощение схемы и повьшение быстродействия.

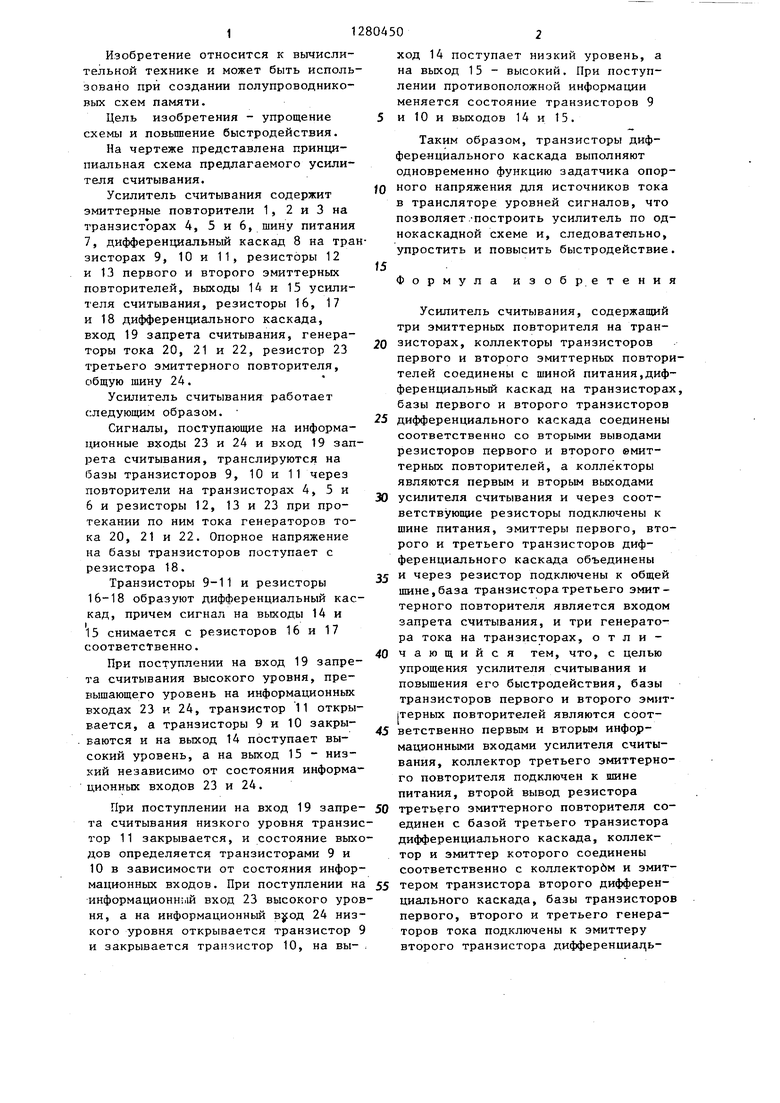

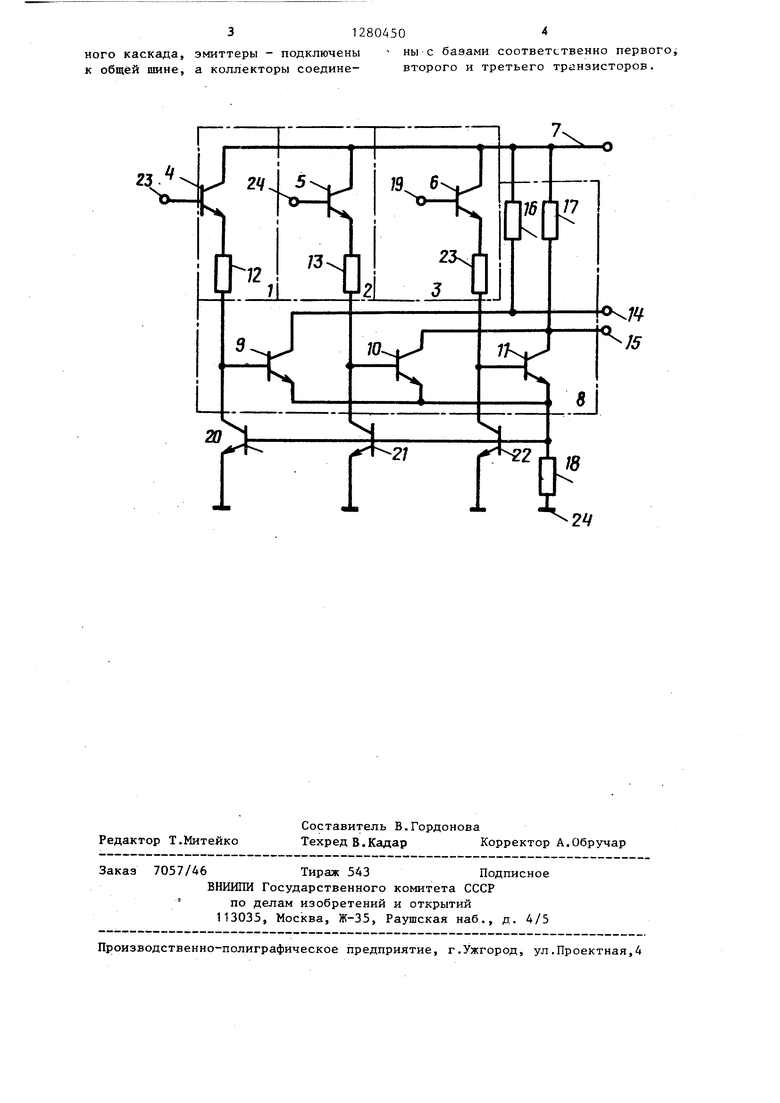

На чертеже представлена принципиальная схема предлагаемого усилителя считывания.

Усилитель считывания содержит эмиттерные повторители 1, 2 и 3 на транзисторах 4, 5 и 6, шину питания 7, дифференциальный каскад 8 на тра зисторах 9, 10 и 11, резисторы 12 и 13 первого и второго эмиттерных повторителей, выходы 14 и 15 усилителя считывания, резисторы 16, 17 и 18 дифференциального каскада, вход 19 запрета считывания, генераторы тока 20, 21 и 22, резистор 23 третьего эмиттерного повторителя, общую шину 24.

Усилитель считывания работает следующим образом.

Сигналы, поступающие на информационные входы 23 и 24 и вход 19 запрета считывания, транслируются на базы транзисторов 9, 10 и 11 через повторители на транзисторах 4, 5 и 6 и резисторы 12, 13 и 23 при протекании по ним тока генераторов тока 20, 21 и 22. Опорное напряжение на базы транзисторов поступает с резистора 18.

Транзисторы 9-11 и резисторы 16-18 образуют дифференциальный каскад, причем сигнал на выходы 14 и 15 снимается с резисторов 16 и 17 соответственно.

При поступлении на вход 19 запрета считывания высокого уровня, превышающего уровень на информационных входах 23 и 24, транзистор 11 открывается, а транзисторы 9 и 10 закрываются и на выход 14 поступает высокий уровень, а на выход 15 - низкий независимо от состояния информационных входов 23 и 24.

При поступлении на вход 19 запрета считывания низкого уровня транзитор 11 закрывается, и состояние выхдов определяется транзисторами 9 и

50 третьего эмиттерного повторителя соединен с базой третьего транзистора дифференциального каскада, коллектор и эмиттер которого соединены соответственно с коллекторбм и эмит10 в зависимости от состояния информационных входов. При поступлении на 55 тером транзистора второго дифферен- информационнмй вход 23 высокого уров- циального каскада, базы транзисторов ня, а на информационный 24 низкого уровня открывается транзистор 9 и закрывается транзистор 10, на вы- ;

первого, второго и третьего генераторов тока подключены к эмиттеру второго транзистора дифференциадь

ход 14 поступает низкий уровень, а на выход 15 - высокий. При поступлении противоположной информации меняется состояние транзисторов 9 и 10 и выходов 14 и 15.

Таким образом, транзисторы дифференциального каскада выполняют одновременно функцию задатчика опорного напряжения для источников тока в трансляторе уровней сигналов, что позволяет .-построить усилитель по од- нокаскадной схеме и, следовательно, упростить и повысить быстродействие.

Формула изобретения

Усилитель считывания, содержащий три эмиттерных повторителя на транзисторах, коллекторы транзисторов

первого и второго эмиттерных повторителей соединены с шиной питания,дифференциальный каскад на транзисторах, базы первого и второго транзисторов

дифференциального каскада соединены соответственно со вторыми выводами резисторов первого и второго вмит- терных повторителей, а коллекторы являются первым и вторым выходами

усилителя считывания и через соответствующие резисторы подключены к шине питания, эмиттеры первого, второго и третьего транзисторов дифференциального каскада объединены

и через резистор подключены к общей шине,база транзистора третьего эмиттерного повторителя является входом запрета считывания, и три генератора тока на транзисторах, о т л и чающийся тем, что, с целью упрощения усилителя считывания и повышения его быстродействия, базы транзисторов первого и второго эмиттерных повторителей являются соответственно первым и вторым информационными входами усилителя считывания, коллектор третьего эмиттерного повторителя подключен к шине питания, второй вывод резистора

третьего эмиттерного повторителя соединен с базой третьего транзистора дифференциального каскада, коллектор и эмиттер которого соединены соответственно с коллекторбм и эмиттером транзистора второго дифферен- циального каскада, базы транзисторов

тером транзистора второго дифферен- циального каскада, базы транзисторов

первого, второго и третьего генераторов тока подключены к эмиттеру второго транзистора дифференциадь312804504

ного каскада, эмиттеры - подключены ны с базами соответственно первого, к общей шине, а коллекторы соедине- второго и третьего транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1986 |

|

SU1368918A1 |

| Усилитель считывания | 1988 |

|

SU1580441A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Формирователь логических перепадов | 1987 |

|

SU1531157A1 |

| Операционный усилитель | 1981 |

|

SU1084960A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Операционный усилитель с защитой выхода от перегрузки | 1981 |

|

SU1020971A1 |

| Устройство выборки и хранения | 1980 |

|

SU963131A1 |

| Двухполупериодный выпрямитель | 1980 |

|

SU1001382A1 |

| Формирователь уровней напряжения для записи-считывания информации | 1985 |

|

SU1247945A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании полупроводниковых схем памяти. Отличие предлагаемого технического решения от известных состоит в том, что, с целью упрощения схемы и повышения быстродействия, усилитель считывания построен по однокаскадной схеме, причем транзисторы дифференциального каскада выполняют одновременно функцию задатчика опорного напряжения для источников .тока в трансляторе уровней сигналов. 1 ил. (Л с tc 00 о сд

Редактор Т.Митейко

Составитель В.Гордонова

Техред В.Кадар Корректор А.Обручар

Заказ 7057/46Тираж 543Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

Авторы

Даты

1986-12-30—Публикация

1985-06-12—Подача