Изобретение относится к вычислительной- технике и может быть применено при создании усилителей считывания для запоминающих устройств.

Целью изобретения является по-- вышение быстродействия усилителя считывания.

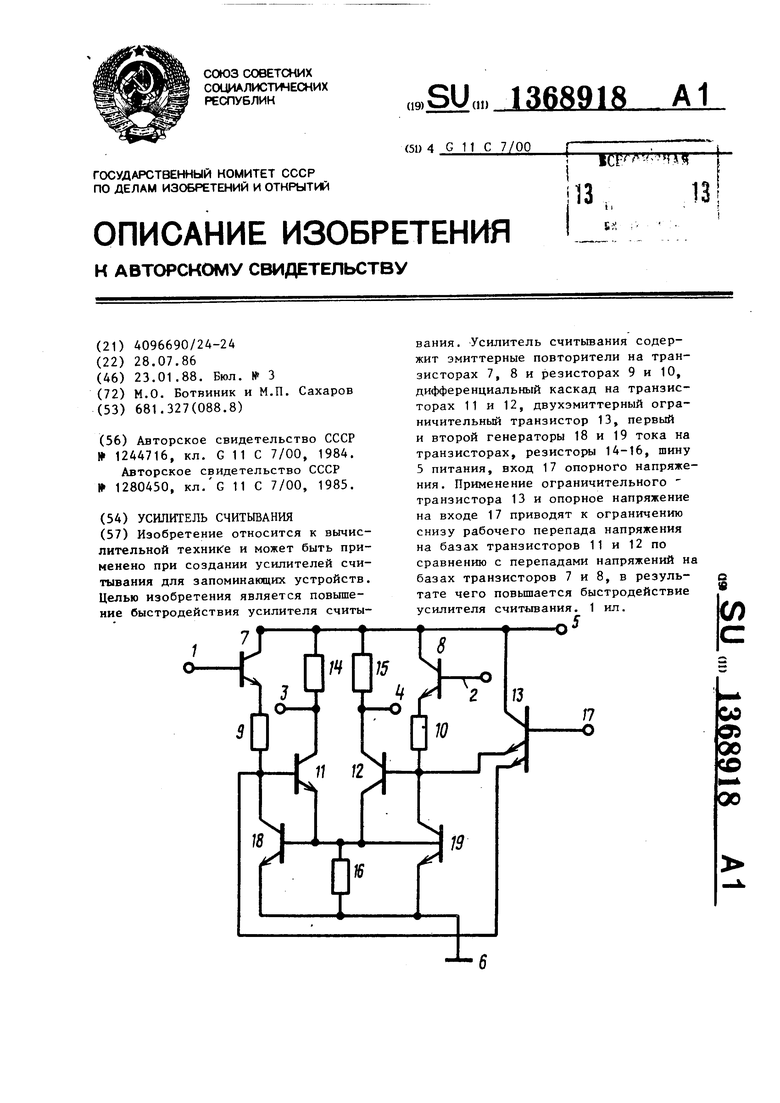

На чертеже представлена принципиальная схема предлагаемого усили- теля считывания.

На схеме обозначены первый и второй 2 информационные входы, первый 3 и второй 4 выходы усилителя считывания, шина 5 питания и шина 6 нуле-г вого потенциала.

Усилитель считывания содержит первый 7 и второй 8 транзисторы эмиттер- ньгх повторителей, первый 9 и второй 10 резисторы, первый 11 и второй 12 транзисторы дифференциального каскада, двухэмиттерный ограничительный транзистор 13, с третьего по пятый резисторы 14-16. .

На чертеже обозначен вход 17 опор- ного напряжения усилителя. Усилитель считывания содержит также транзисторы 18 и 19 первого и второго генераторов тока.

мым повышают быстродействие усилителя.

Для обеспечения этого величину опорного напряжения на выходе 17 необходимо выбрать в соответствии с условием

и,.

Зч.,и„„

Uc + и

э5

и,8 де Uf - напряжение на базе транзистора 11 (или 12) при логической 1 на входе 1 (или 2);

падение напряжения на переходе база-эмиттер транзистора 13;

- температурный потенциал;

Ujf, - опорное напряжение на вхоо д 17;

Vf- напряжение на базе транзистора 12 (или 11) при логическом О на входе 2 (или 1) относительно шины 6.

ормула изобретения Усилитель считывания, содержащий

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1988 |

|

SU1580441A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Усилитель считывания | 1985 |

|

SU1280450A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1492381A1 |

| Формирователь логических перепадов | 1987 |

|

SU1531157A1 |

| Усилитель считывания | 1989 |

|

SU1658209A1 |

| Усилитель считывания | 1986 |

|

SU1316045A1 |

| Эмиттерно-связанный элемент | 1988 |

|

SU1629985A1 |

| Запоминающее устройство | 1985 |

|

SU1310896A1 |

Изобретение относится к вычислительной технике и может быть применено при создании усилителей считывания для запоминающих устройств. Целью изобретения является повьше- ние быстродействия усилителя считывания. Усилитель считьшания содержит эмиттерные повторители на транзисторах 7, 8 и резисторах 9 и 10, дифференциальный каскад на транзисторах 11 и 12, двухэмиттерный ограничительный транзистор 13, первый и второй генераторы 18 и 19 тока на транзисторах, резисторы 14-16, шину 5 питания, вход 17 опорного напряжения. Применение ограничительного транзистора 13 и опорное напряжение на входе 17 приводят к ограничению снизу рабочего перепада напряжения на базах транзисторов 11 и 12 по сравнению с перепадами напряжений на базах транзисторов 7 и 8, в результате чего повышается быстродействие усилителя считьшания. 1 ил. § (Л

Усилитель считывания работает еле- 30 первый и второй эмиттерные повторидующим образом.

Сигналы, поступающие на входы 1 и 2, транслируются на базы транзисторов 11 и 12 соответственно через транзисторы 7 и 8 и резисторы 9 и 10 при протекании по ним тока от транзисторов 18 и 19, на базы которых поступает с резистора 16 опорное напряжение.

Транзисторы 11 и 12 и резисторы 14 и 15 образуют дифференциальный каскад, причем сигнал на выходы 3 и 4 снимается соответственно с резисторов 14 и 15.

При поступлении на вход 1 сигнала высокого уровня, а на вход 2 - низкого уровня открывается транзистор 11 и закрьтается транзистор 12, на выходе 3 - низкий уровень, а на выходе 4 - высокий. При поступлении противоположной информации соответственно меняется состояние транзисторов 11 и 12 и выходов 3 и 4.

Опорное напряжение на входе 17 и транзистор 13 снижают рабочий перепад напряжения на базах транзисторов 11 и 12 по сравнению с перепадами напряжений на входах 1 и 2 и тем сатели на транзисторах, эмиттеры кото- , рых подключены к первым вьшодам первого и второго резисторов, дифференциальный каскад на транзисторах, первый и второй генераторы тока на транзисторах и с третьего по пятый резисторы, причем коллекторы транзисторов первого и второго эмиттерных повторителей и первые выводы третьего и

четвертого резисторов соединены с

иной питания, базы транзисторов первого и второго эмиттерных повторителей являются информационными входами устройства, вторые вьтоды первого и второго резисторов соединены соответственно с базами первого и второго транзисторов дифференциального каскада,коллекторы которых подключены соответственно к вторым выводам третьего и четвертого резисторов и являются соответственно первым и вторым выходами усилителя, эмиттеры первого и второго транзисторов дифференциального каскада соединены с первым выводом пятого транзистора и базами транзисторов первого и второго генераторов тока, коллекторы которых подключены соответственно к базам первого и второго

13689184

транзисторов дифференциального кас-транзистор, база которого является

када, эмиттеры транзисторов первоговходом опорного напряжения усилителя,

и второго генераторов тока и второйа коллектор соединен с шиной питЪния,

вывод пятого резистора соединены спричем первый и второй эмиттеры огшиной нулевого потенциала, о т л й-раничительного транзистора подключечающийся тем, что, с цельюны соответственно к базе первого и

повышения быстродействия, в него вве-к базе второго транзисторов диффе-

ден двухэмиттерный ограничительныйренциального каскада.

| Преобразователь сигналов для усилителя считывания | 1984 |

|

SU1244716A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Усилитель считывания | 1985 |

|

SU1280450A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-01-23—Публикация

1986-07-28—Подача