Изобретение относится к радиотехнике и электросвязи и может использоваться в системах передачи дискретной информации для приема избыточных сигналов в целом, использующих коды большой мощности.

Цель изобретения - упрощение устройства.

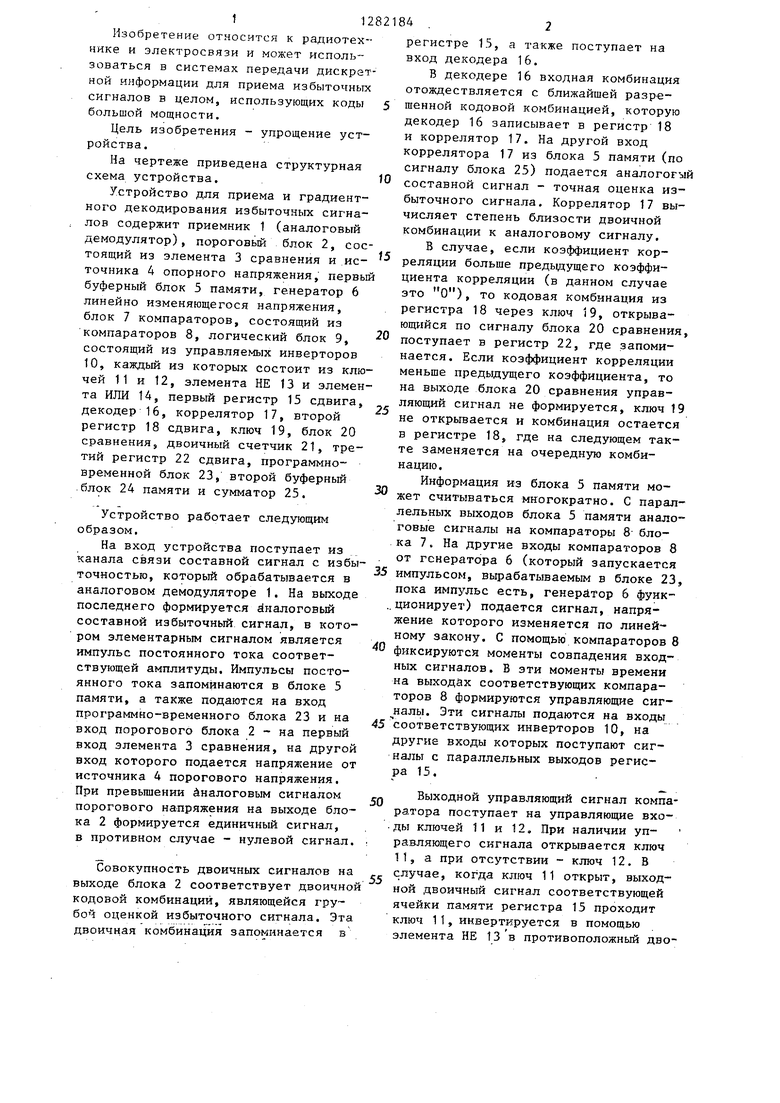

На чертеже приведена структурная схема устройства.

Устройство для приема и градиентного декодирования избыточных сигналов содержит приемник 1 (аналоговый демодулятор), пороговьш блок 2, состоящий из элемента 3 сравнения и ис точника 4 опорного напряжения, первы буферный блок 5 памяти, генератор 6 линейно изменяющегося напряжения, блок 7 компараторов, состоящий из компараторов 8, логический блок 9, состоящий из управляемых инверторов 10, каждый из которых состоит из ключей 11 и 12, элемента НЕ 13 и элемента ИЛИ 14, первый регистр 15 сдвига, декодер 16, коррелятор 17, второй регистр 18 сдвига, ключ 19, блок 20 сравнения, двоичный счетчик 21, третий регистр 22 сдвига, программно- временной блок 23, второй буферньш блок 24 памяти и сумматор 25.

Устройство работает следующим образом.

На вход устройства поступает из канала связи составной сигнал с избыточностью, который обрабатывается в аналоговом демодуляторе 1. На выходе последнего формируется Аналоговый составной избыточный сигнал, в котором элементарным сигналом является импульс постоянного тока соответствующей амплитуды. Импульсы постоянного тока запоминаются в блоке 5 памяти, а также подаются на вход программно-временного блока 23 и на вход порогового блока 2 - на первый вход элемента 3 сравнения, на другой вход которого подается напряжение от источника 4 порогового напряжения. При превышении Аналоговым сигналом порогового напряжения на выходе блока 2 формируется единичный сигнал, в противном случае - нулевой сигнал.

Совокупность двоичных сигналов на выходе блока 2 соответствует двоично кодовой комбинаций, являющейся грубой оценкой избыточного сигнала. Эта двоичная комбинация запоминается в

15

10

регистре 15, а также поступает на вход декодера 16.

В декодере 16 входная комбинация отождествляется с ближайшей разрешенной кодовой комбинацией, которую декодер 16 записывает в регистр 18 и коррелятор 17. На другой вход коррелятора 17 из блока 5 памяти (по сигналу блока 25) подается аналогогый составной сигнал - точная оценка избыточного сигнала. Коррелятор 17 вычисляет степень близости двоичной комбинации к аналоговому сигналу.

В случае, если коэффициент корреляции больше предьщущего коэффициента корреляции (в данном случае это О), то кодовая комбинация из регистра 18 через ключ 19, открывающийся по сигналу блока 20 сравнения, поступает в регистр 22, где запоминается. Если коэффициент корреляции меньше предыдущего коэффициента, то на выходе блока 20 сравнения управляющий сигнал не формируется, ключ 19 не открывается и комбинация остается в регистре 18, где на следующем такте заменяется на очередную комбинацию.

Информация из блока 5 памяти может считываться многократно. С параллельных выходов блока 5 памяти аналоговые сигналы на компараторы 8 блока 7 . На другие входы компараторов 8 от генератора 6 (который запускается импульсом, вырабатываемым в блоке 23, пока импульс есть, генератор 6 функционирует) подается сигнал, напряжение которого изменяется по линейному закону. С помощью компараторов 8 фиксируются моменты совпадения входных сигналов. В эти моменты времени на выходах соответствующих компараторов 8 формируются управляющие сиг- налы. Эти сигналы подаются на входы 45 соответствующих инверторов 10, на другие входы которых поступают сигналы с параллельных выходов регис- ра 15.

20

25

30

35

40

Выходной управляющий сигнал компаратора поступает на управляющие вхо- ды ключей 11 и 12. При наличии управляющего сигнала открывается ключ 11, а при отсутствии - ключ 12. В случае, когда ключ 11 открыт, выходной двоичный сигнал соответствующей ячейки памяти регистра 15 проходит ключ 1 1, инвертируется в помощью элемента НЕ 13 в противоположный двоичный сигнал и через элемент ИЛИ 14 ,записывается в соответствующую ячейку памяти блока 24. Если открыт ключ 12, то. соответствующий двоичный сигнал записывается в определенную ячей ку памяти регистра блока 24 без изменения. Каждое срабатывание компараторов блока 7 фиксируется сумматором 25 и подается в блок 23, в котором формируется управляющий сигнал и сформированная на выходах блока 9 двоичная кодовая комбинация переписывается в блоке 24 из первого параллельного- буферного регистра во вто- рой, потом в третий и Т.д. Количеств регистров в блоке 24 определяется скоростью обработки информации устройством, быстродействием элементов и т.п. По мере появления управляющих сигналов на выходах блока 7 двоичные комбинации продвигаются по регистрам блока 24 и.в определенный момент времени (он определяется количеством сработавших компараторов 8 блока 7 и емкостью блока 24 памяти) на выхо- дах блока 24 появляется двоичная ко- .довая комбинация. Эта комбинация подается на входы декодера 16, в котором преобразуется в ближайшую разрешенную кодовую комбинацию. Данная разрешающая кодовая комбинация записывается в регистр 18, поступает на вход коррелятора 17 и обрабатывается в соответствии с описанным алгоритмом. Если для нее коэффициент корреляции больше коэффициента корреляции предыдушей комбинации,то она записывается в регистр 22,в противном слушав остается в регистре 18.

Аналогичным образом обрабатываются все двоичные комбинации с выхода блока 24 памяти.

Когда выходное напряжение генера

тора б достигает своего максимального значения, снимается управляющий сигнал блока 23, включая генератор б.

При поступлении на вход коррелятора 17 последней комбинации (а значит и на вход счетчика 21, в котором подсчитывается количество выxoдныk комбинаций детектора 16) счетчик 21 ;выдает сигнал, по которому кодовая комбинация из регистра 22 поступает на выход устройства. После этого все блоки устройства приводятся в исходное состояние по управляющему сигна лу программно-временного блока 23.

5 Ю 520 25 о

5

5

0

Техническое преимущество устройства по сравнению с известным заключается в исключении из схемы известного части блоков, снижающих его надежность, т.е. в упрощении устроит ства.

Формула изобретения

Устройство для приема и градиентного декодирования избыточных сигналов, содержащее приемник, вход которого является входом устройства, ВЫХОД приемника соединен с входами первого блока памяти и порогового блока, выход порогового блока соединен с информационным входом первого регистра и первым информационным входом декодера,, выходы первого регистра соединены с информационными входами соответствующих инверторов, управляющие входы которых подключены к выходам соответствующих компараторов, выход декодера соединен с информационным входом второго регистра и первым информационным входом коррелятора, второй информационный вход коррелятора подключен к первому выходу первого блока памяти, выход коррелятора соединен с информа ион- ными входами блока сравнения и счетчика, выход блока сравнения и выход второго регистра соединены соответственно с управляющими и информ ци- онными входами ключа, выход ключа и выход счетчика соединены соответственно с информационным и первым управляющим входами третьего регистра, выход которого является выходом устройства, программно-временной блок, второй блок памяти и генератор линейно изменяющегося напряжения, отличающееся тем, что, с целью упрощения устройства, в негр введен сумматор, вторые выходы первого блока памяти соединены с первыми входами соответствующих компараторов, выход генератора линейно изменяющегося напряжения соединен с вторыми входами компараторов, выходы инверторов соединены соответственно с информационными входами сумматора и второго блока памяти, выходы второго блока памяти соединены с соответствующими вторыми информационными входами декодера, выход сумматора соединен с первым входом программно-временного блока, второй вход которого подключен к выходу приемника, первый, второй, третий, четвер512821846

, ПЯТЫЙ,, шестой,, седьмой, восьмой,дера, коррелятора, второго регистра;

девятый и дегятьгй вьгходы програт-шно-блока сравнения , счетчика , втовременного блока соединены соответ-рым управляющим входом третьественно с входом генератора линей-го регистра , управляющими вхоао изменяющегося напряжения, управля™ 5дами второго: блока памяти к

ющики входами первого регистра, деко-сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152020A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1101873A1 |

| Устройство для приема и обработки избыточной информации | 1983 |

|

SU1140141A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1001145A1 |

Изобретение относится к радио- технике и электросвязи и может использоваться в системах передачи дис- ,кретных сигналов, использующих коды большой мощности. Изобретение позволяет упростить устройство. Устройство осуществляет прием избыточных сигналов в целом, декодирование кодовой комбинации и выдачу декодированной комбинации, наиболее близкой к входному сигналу. Устройство содержит приемник, пороговый блок, блоки памяти, генератор линейно изменяющегося напряжения, компараторы, инверторы, регистры, декодер, коррелятор, .ключ, .блок сравнения, счетчик и сумматор. 1 ил.

I 5 л«1Г Аи аДь-1 j |я..„.„.,„..«

,,r

Редактор Н. Бобкова

Составитель М. Нйкуленков

Л.Олейашх Корректор С. Черни

Заказ 7272/50

Тираж 542

ВНИИПИ Государственного комитета СССР ,

по делам изобретений и открытий 113035, Москва,, Ж-35р Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152020A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-01-07—Публикация

1985-07-08—Подача