Изобретение относится к электросвязи и может быть использовано в приемных устройствах систем передачи информации, использующих избыточные коды большой мощности.

Целью изобретения является повышение помехоустойчивости приема избыточных сигналов, передаваемых по каналам высокого качества.

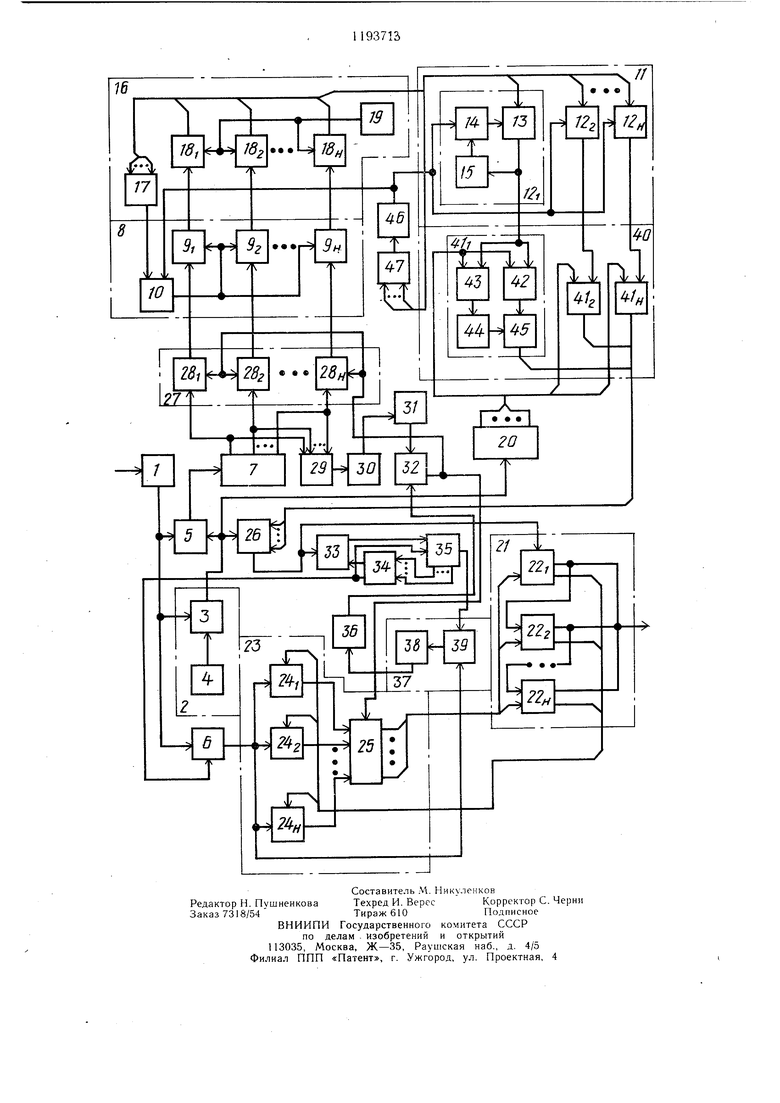

На чертеже представлена структурная схема устройства.

Устройство для приема и обработки избыточных сигналов содержит приемник 1 (аналоговый демодулятор), пороговый блок 2, состоящий из элемента 3 сравнения и источника 4 порогового напряжения, вычитатель 5, блок 6 н 7 буферной памяти,, блок 8 усилителей, состоянгий из усилителей 9 с регулируемым коэффициентом усиления и генератора 10 линейно изменяющегося напряжения, блок 1 1 дискриминаторов, состояший из дискриминаторов 12, выполненных на ключах 13, триггерах 14 и элементах 5 задержки, Юроговый блок 16, состояший из элемента ИЛИ 17, элементов 18 сравнения и источника 19 nopoiOBoro напряжения, блок 20 регистров, блок 21 регистров, состоящий из регистров 22, блок 23 управления выдачей информации, состояший из корреляторов 24 и детектора 25 максимального сигнала, декодер 26, блок 27 ключей, состояший из ключей 28, сумматор 29, пороговый блок 30, элемент 31 задержки, ключи 32 и 33, формирователь 34 импульсов (логический блок), регистр 35 сдвига, пороговый блок 36, блок 37 оценки качества решения, состоящий из сумматора 38 и умножителя 39, блок 40 управляющих инверторов, состояший из управляемых инвенторов41, выполненных на ключах 42 и 43, элементе НЕ 44 и элементе ИЛИ 45, элемент 46 задержки и элемент И 47.

Устройство работает следуюши.м образом.

На в.ход аналогового демодулятора 1 поступает сложный избыточный . На выходе аналогового демодулятора 1 появляется совокупность аналоговых сигналов, соответствующих элементам входного сигнала. Каждый аналоговый сигнал подается на вход элемента 3 сравнения, на другой вход которого поступает пороговое напряжение от источника 4 порогового напряжения. Если величина входного аналогового сигнала меньше величины порогового напряжения, то на выходе элемента 3 сравнения появляется сигнал «О, в противном случае - сигнал«1. Таки.м образом, аналоговый сигнал преобразуется в двоичный сигнал.

В вычитателе 5 из величины аналогового сигнала вычитают величину двоичного сигнала. В декадере 26 последовательно записывается двоичная кодовая комбинация, соответствующая посимвольному грубому решению по входному сиг11а..чу. Декодер

26 записывает в регистр 22i двоичную разрешенную кодовую комбинацию, являющуюся ближайшей к двоичной посимвольной. В блок 20 регистров также записывается эта двоичная кодовая комбинация. В блок 7 буферной намяти записывается и хранится совокупность аналоговых сигналов, сформированных в вычитателе 5.

Из блока 7 эти сигналы параллельно подаются на информационные входы закрытых в исходном положении ключей 28 и на входы многовходового сумматора 29, в котором вычисляют сумму абсолютных величин выходных сигналов блока 7.

Выходной сигнал сумматора 29 подается па вход порогового блока 30, где он сравнивается с величиной порогового напряжения. Если входной сигнал блока 30 равен или болыпе величины порогового напряжения, то закрывающий ключ 28 блока 27 выходной сигнал блока 30 не отключается, а при наличии этого сигнала в соответствующий момент времени из блока 23 в блок 21 поступает управляющий сигнал, считывающий на выход устройства хранящуюся в нем разрещенпую кодовую комбинацию (или ее информационную часть). Если входной сигнал блока 30 окажется меньп1е величины порогового напряжения, то сигнал запрета с выхода блока 30 отключается. При этом он снимается и с входов блока 23 и 27, вследствие чего ключи 28 блока 27 открываются и из блока 7 сигналы также подаются на усилители 9 блока 8.

Выходной сигнал порогового блока 30 подается на управляющие входы блока 28 ключей и блока 23 управления выдачей

информации через элемент 31 задержки и открытый в исходном состоянии ключ 32. В дополнение к выщеописанному (т. е. к случаю, когда ключ 32 открыт) рассмотрим случай, когда ключ 32 закрывается. Первая разре1пенная двоичная кодовая комбинания с выхода декодера 26 через открытый в исходном состоянии ключ 33 последовательно записывается в двоичный регистр 35 сдвига. После заполнения всех ячеек памяти регистра 35 на выходе логическо|о блока 34, соединенном с блоком 6 и регистром 35, формируется сигнал считывания. Синхронно из блока 6 и регистра 35 на выходы умножителя 39 считываются соответственно первая разрешенная кодовая комбинация и аналоговый составной сигнал с

избыточностью. Результаты перемножения накапливаются в сумматоре 38. По окончании обработки входных составных сигналов на выходе блока 37 формируется сигнал, который сравнивается в блоке 36 с пороговым сигналом. Если выходной сигнал

блока 37 меньше порогового, то на выходе блока 36 формируется управляющий сигнал, закрывающий ключ 32.. В противном случае ключ 32 открыт.

После того как из блока 7 сигналы параллельно поданы на усилители 9, запускается генератор 10 линейно изменяюп1егося напряжения 10 и коэффициент усиления усилителей 9 увеличивается (его начальное значение равно 1). Выходные сгналы усилителей 9 подаются на элементы 18 сравнения, к другим входам которых подключен источник 19 порогового напряжения. Как только в каком-нибудь элементе 18 сравнения выходной сигнал усилителя 9 превысит величину порогового напряжения, срабатывает элемент ИЛИ 17 и генератор 10 «останавливается, т. е. прекращается уве: личение выходного напряжения, на выходах элементов 18 сравнения сформирована двоичная комбинация единичного веса. Единичный символ находится в том разряде, номер которого определяется наименее надежным аналоговым сигналом.

С выходов блока 16 параллельная кодовая комбинация поступает на входы блока 11 дискриминаторов. Каждый двоичный символ поступает на вход соответствующего дискриминатора 12. Рассмотрим прохожде.ние через дискриминатор 12 единичного сигнала.

Этот сигнал проходит через открытый в исходном состоянии ключ 13 на выход дискриминатора, а также через элемент 15 задержки поступает на вход триггера 14, который изменяет свое состояние на противоположное, вследствие чего ключ 13 закрывается, и последующие сигналы с входа дискриминатора 12 на его выход не проходят (до тех пор, пока триггер не будет приведен в исходное состояние).

Нулевой входной сигнал дискриминатора 12 состояние ключа 13 не изменяет.

Таким образом, на выходе блока 1 1 дискриминаторов формируется двоичная кодовая комбинация единичного веса.

Выходная комбинация блока 1 1 дискриминатора поступает на входы блока 40 правляемых инверторов, на другие входы которого с параллельных выходов блока 20 поступает двоичная кодовая комбинация - грубая посимвольная оценка входного сигнала. Сигналы эти двоичных комбинаций подаются на управляемые инверторы 41 блока 40.

Двоичный сигнал с выхода блока 1 1 поступает на управляющие входы ключей 42 и 43. Если этот двоичный сигнал является нулевым, то открыт ключ 42, а ключ 43 закрыт. Если сигнал является единичным, то ключ 42 закрывается на время действия сигнала, а ключ 43 открывается. При нулевом сигнале информационные сигналы с соответствующего выхода блока 20 через ключ 42 и элемент ИЛИ 45 проходят на выход блока 40 без изменения. При единичном сигнале информационные сигналы проходят через соответствующий ключ 43, инвертируются с. помощью элемента НЕ

44 и через элемент ИЛИ 45 проходят на выход блока 40.

Таким образом, выходная комбинация блока 40 отличается от комбинации блока 13 тем разрядом, номер которого совпадает с номером единичного символа в выходной комбинации блока 11. Выходная комбинация блока 40 в параллельном коде поступает в декодер 26.

Оформленная декодером 26 разрешенная

0 двоичная кодовая комбинация записывается в регистр 22|, сдвигая первую разрешенную комбинацию в регистр 22о.

После этого опять запускается генератор 10 блока 8, вследствие чего его выходное напряжение продолжает нара5 ехать. Срабатывает второй элемент сравнения, отчего генератор 10 опять «останавливается. На выходе блока 16 формируется двоичная кодовая комбинация с двумя единичными символами. Она подается на

Q входы блока 1 1 дискриминаторов. Первая единица на выход соответствующего дискриминатора 12 не проходит, так как ключ 13 закрьгг. Вторая единица проходит на выход своего дискриминатора 12, ключ 13 этого дискриминатора закрывается. На

5 выходе блока 1 1 формируется двоичная кодовая комбинация единичного веса. Она рование всех символов двоичной комбинацию блока 20. В результате на выходе блока 40 формируется двоичная кодовая комбинация, которая отличается от комбинации блока 20 тем одним разрядом, номер которого совпадает с номером следующего наименее надежного символа сложного аналогового сигнала на выходе демодулятора 1.

5 Таки.м образом, осуществляется инвертирование всех символов двоичной комбинации б.юка 20 в порядке, определяемом надежностя.ми аналоговых сигналов.

Выходные комбинации блока 40 с гю мощью декодера 26 преобразуются в разрещенные комбинации, которые записываются в регистры блока 21.

Когда все символы выходной комбинации блока 16 будут единичными,на выходе элемента И 47 появляется сигнал. Этот сигнал проходит через элемент 46 задержки и устанавливает генератор 10 в исходное состояние, при котором коэффициенты усиления усилителей 9 равны единице, устанав- . ливает триггеры 14 дискриминаторов 12 в состояние, при котором ключи 13 открыты.

0 Далее детектор 25 максимального сигнала считывает из регистров 22 разрещенные комбинации в корреляторы 24, на другие входы которых подается комбинация аналоговых величин из блока 6 буферной памяти. Величины выходных сигналов корреляторов 24 соответствуют коэффициентам корреляции соответствующих комбинаций. Эти сигналы поступают в детектор 25, в котором опреде.1яется максимальный из них.

Разрешеную комбинацию, соответствующую максимальному сигналу, считывают по управляющему сигналу из детектора 25 на соответствующий регистр 22. Далее все элементы памяти приводятся в исходное состояние и устройство готово к работе - обработке следующего избыточного сигнала.

Предлагаемое устройство обладает более высоким технико-экономическими показателями по сравнению с известным устройством.

Техническое преимущество предлагаемого устройства заключается в том, что в нем формируются вектора только единичного веса и с их помощью осуществляется коррекция комбинации грубой посимвольной оценки избыточного сигнала.

Положительный эффект, который может быть достигнут в результате использования изобретения, заключается в повыщении помехоустойчивости приема избыточных сигналов в каналах высокого качества вследствие того, что в таких каналах наиболее вероятными ошибками являются однократные ощибки единичного веса.

Рассчитаем ориентировочный выигрыш вероятности правильного приема, которая и определяет помехоустойчивость приема избыточных сигналов.

Известное устройство исправляет ощибки различной кратности, поэтому вероятность правильного приема Рпра этого устройства пропорциональна сумме вероятностей появления вектора ошибок указанных кратностей

-Ьр-(

Fnpaii «jp(l-р) -f р |р(1-рр-

где р - вероятность искажения элементарного сигнала;

Н - количество элементарных сигналов в составном избыточном сигнале. Вероятность правильного приема предлагаемого устройства пропорциональна сумме вероятностей появления однократных векторов ошибок

P(i-pf-4...+ P(i-pf

pHos

г прав

Нр(1-р)- Исключим общие члены и найдем отношение

р

(н-1)Р(1-рГ;

Глрав

р()+рЗ(...+ р« .

рлзв прлв

Обозначим

а.-1-р

тогда

у (Н-1)(а-1)

О -F-ranп

15

а а- -1

Пусть Р 1 10 тогда

--i-JO

/

1 - 1- 10

20

(н-1) 1 lo

Пусть ,5, тогда

.1

25 1-0,5

Y«(H-1) .

Пусть ,8, тогда

30

а 0-S .4 1 -0,8

Н

Тг

Таким образом, если исходный канал связи хорошего качества, т.е. ,5, то помехоустойчивость предлагаемого устройства выше помехоустойчивости известного устройства. В каналах низкого качества Р 0,5, предпочтительнее использовать известное устройство. Преимущества предлагаемого устройства тем выще, чем длиннее используемый код (больше величина Н) и выше качество канала связи (меньше значение Р). ...U 28 H .r-F J3/ / 1/ J Y 0 /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и обработки избыточной информации | 1983 |

|

SU1140141A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152020A1 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

УСТРОЙСТВО ДЛЯ ПРИЕМА И ОБРАБОТКИ ИЗБЫТОЧНЫХ СИГНАЛОВ, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом первого порогового блока и первыми входами вычитателя и первого блока памяти, выход которого соединен с входом первого блока регистров, вторым входом вычитателя и первым входом декодера, выход которого соединен с первым входом второго блока регистров и первым входом первого ключа, .выход которого соединен с первым входом регистра, первый выход которого соединен с первым входом блока оценки качества решения, выход которого соединен через второй пороговый блок с первым входом второго ключа, вторые выходы регистра соединены с соответствующими входами формирователя импульсов, первый выход которого соединен с вторым входом первого ключа, второй выход - с вторыми входами регистра и первого блока памяти, выход которого соединен с первым входом блока управления и вторым входом блока оценки качества решения, выходы и вторые входы блока управления подключены соответственно к вторым входам и первым выходам второго блока регистров, второй выход которого является выходом устройства, выход вычитателя соединен с входом второго блока памяти, выходы которого соединены соответственно с первым входами блока ключей и входами сумматора, выход которого подключен через последовательно соединенные третий пороговый блок и первый элемент задержки к второму входу второго ключа, выход которого соединен с третьим входом блока управления и вторым входом блока ключей, выходы которого соединены с соответствующими первыми входами блока усилителей, выходы и второй вход которого подключены соответственно к входам и первому выходу четвертого порогового блока, отличающееся тем, что, с целью повышения i помехоустойчивости устройства, в него введены элемент И, второй элемент задерж(Л ки, инверторы и дискриминаторы, каждый из которых выполнен на триггере, ключе и элементе задержки, выход триггера соединен с первым входом ключа, выход которого соединен через элемент задержки с первым входо.м триггера, выходы первого блока регистров соединены с первыми входами соответствующих инверторов, выходы инверторов соединены с соответствующими оо рыми входами декодера, вторые выходы четвертого порогового блока соединены с соответствующи.ми в,ходами элемента И и вторыми входами ключей соответствующих дискриминаторов, выходы ключей дискримиоо наторов соединены с вторыми входами соответствующих инверторов, выход элемента И соединен через второй элемент задержки с третьим входом блока усилителей и вторыми входами триггеров дискрими наторов.

| Бородин Л | |||

| Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М.: Советское радио, 1968,с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-15—Подача