ляюпщх команд, первый и второй выхо ды регистра интерфейса подключены соответственно к входу блока, первым входам элементов И первой группы и первому входу генератора синхросигналов, второй вход, первый, второй, третий, четвертый и пятый выходы : которого соединены соответственно с входом блока, вторыми входами элементов И первой группы, первыми входами элементов И второй группы, управляющим входом регистра управляющих команд, управляющим входом регистра микрокоманд и выходом блока, информационный вход, первый и второй выходы регистра управляю1цих команд подключены соответственно к выходу памяти управляющих команд, входу памяти микрокоманд и вторым входам элементов И второй группы, информационный вход и выходы регистра микрокоманд соединены соответст-. венно с выходом памяти микрокоманд и выходом блока.

3.Процессор поп. 2,отлич ающийс я тем, что второй блок управления содержит дешифратор, вход Которого подключен к выходу регистра микрокоманд а выходы дешифратора соединены с выходом блока.

4.Процессор по п. 1, отличающийся тем, что операцион ный блок содержит сумматор, три триггера, коммутатор, элемент И и элемент ИЛИ, первый и второй иход и Ъыход которого соединены с выходом второго триггера, управляющим входом и третьим выходом блока, вход переноса, первый и второй информационный вход,

управляющий вход, выход результата и выход переноса сумматора подключены соответственно к выходу первого триггера, первому и второму информационным входам блока, управляющему

,входу блока, первому входу элемента Ни информационному входу первого триггера, -синхровход и выход первого триггера соединены соответственно с управляющим входом и первым выходом блока, второй вход и выход элемента И подключены соответственно к выходуэлемента ИЛИ и информационному входу второго триггера, управляющий вход которого соединен с управляющим входом блока, управляющий

I вход, первый, второй и третий входы и выход коммутатора подключены соответственно к управляющ« му входу блока, первому входу-выходу сдвига бло ка, выходу элемента И, второму входу-выходу сдэига блока и информационному входу третьего триггера, управляю1101Й вход которого соединен с управлякицим входом блока, а выход этого триггера подключен к второму выходу и второму входу-выходу сдвига блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1200288A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

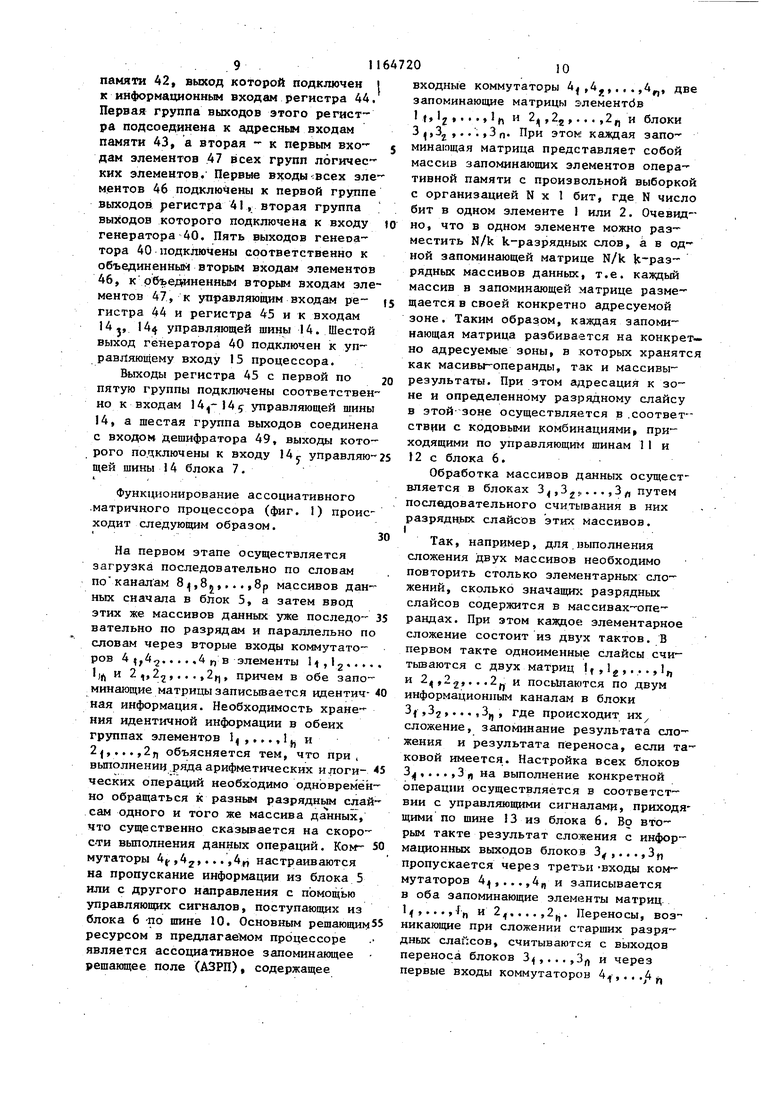

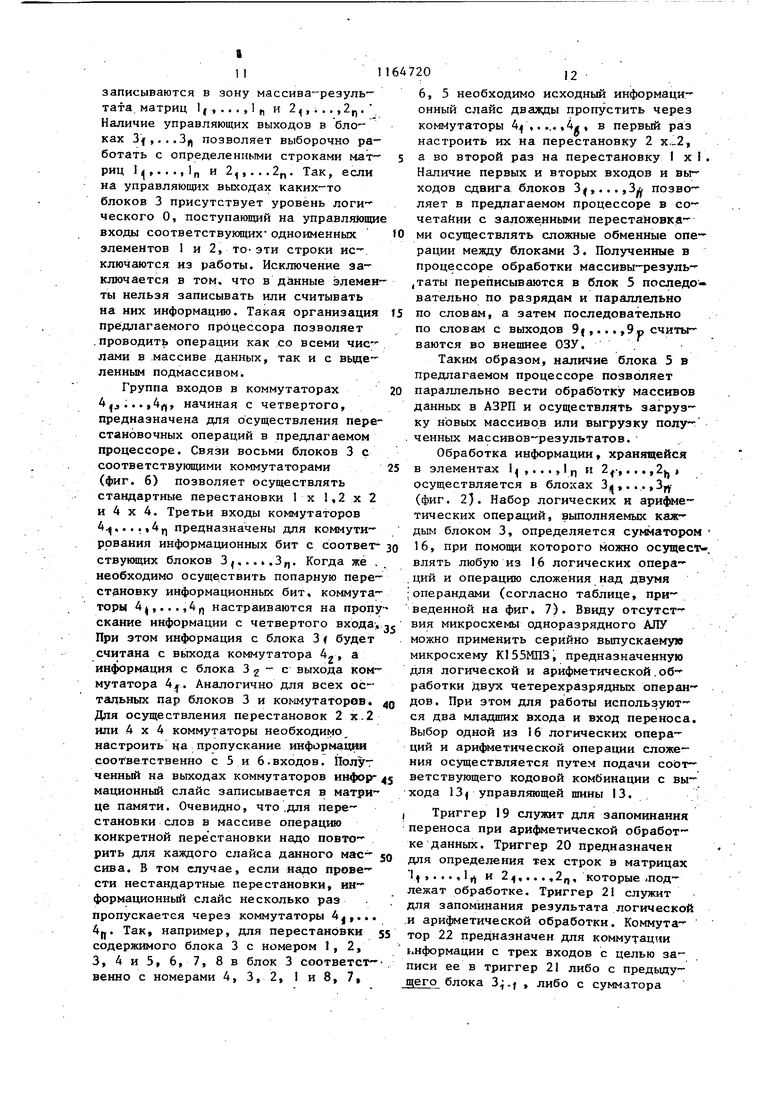

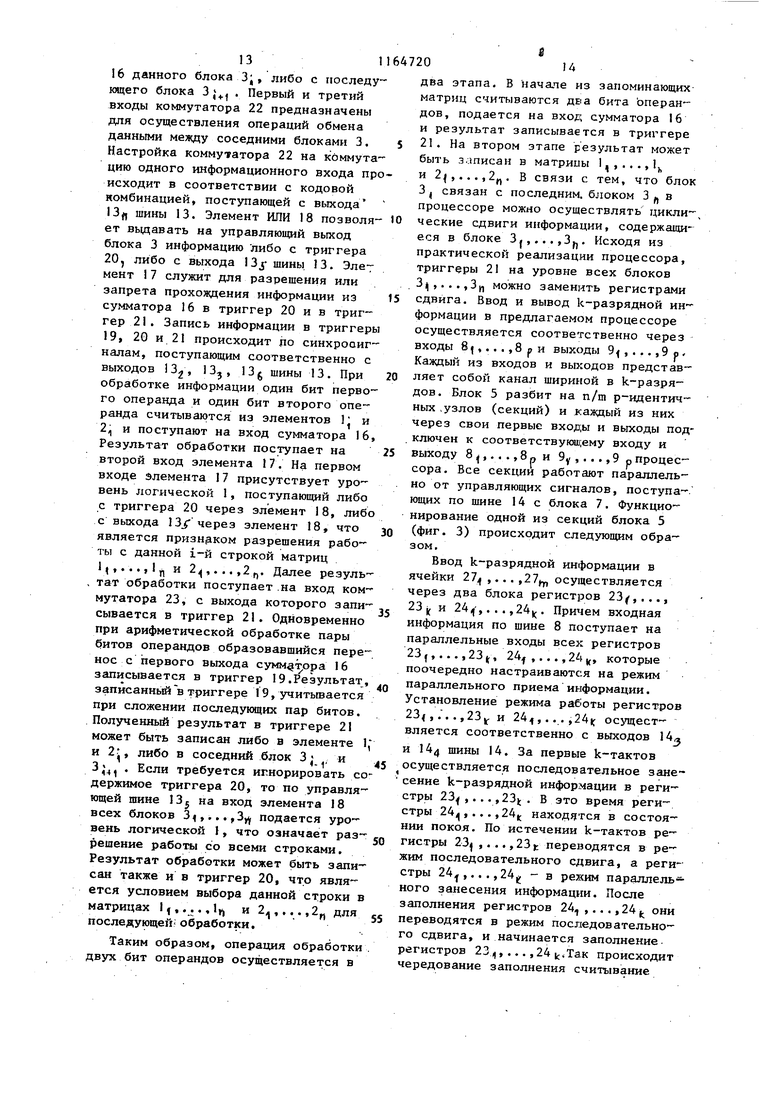

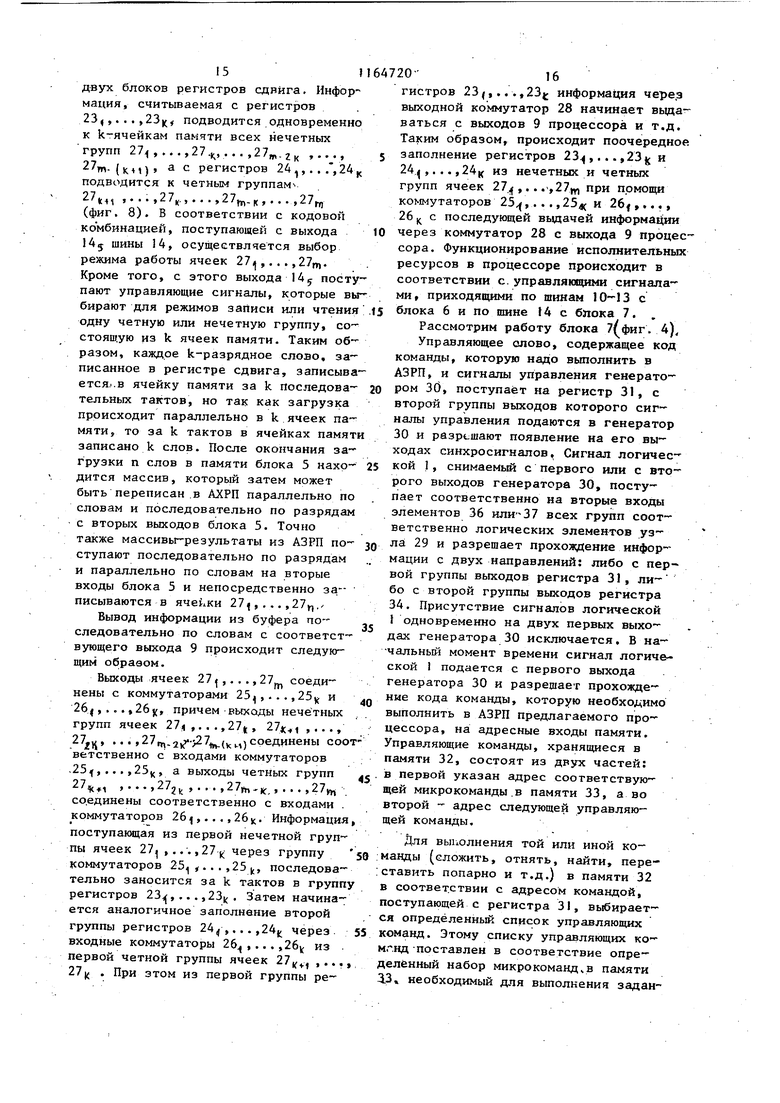

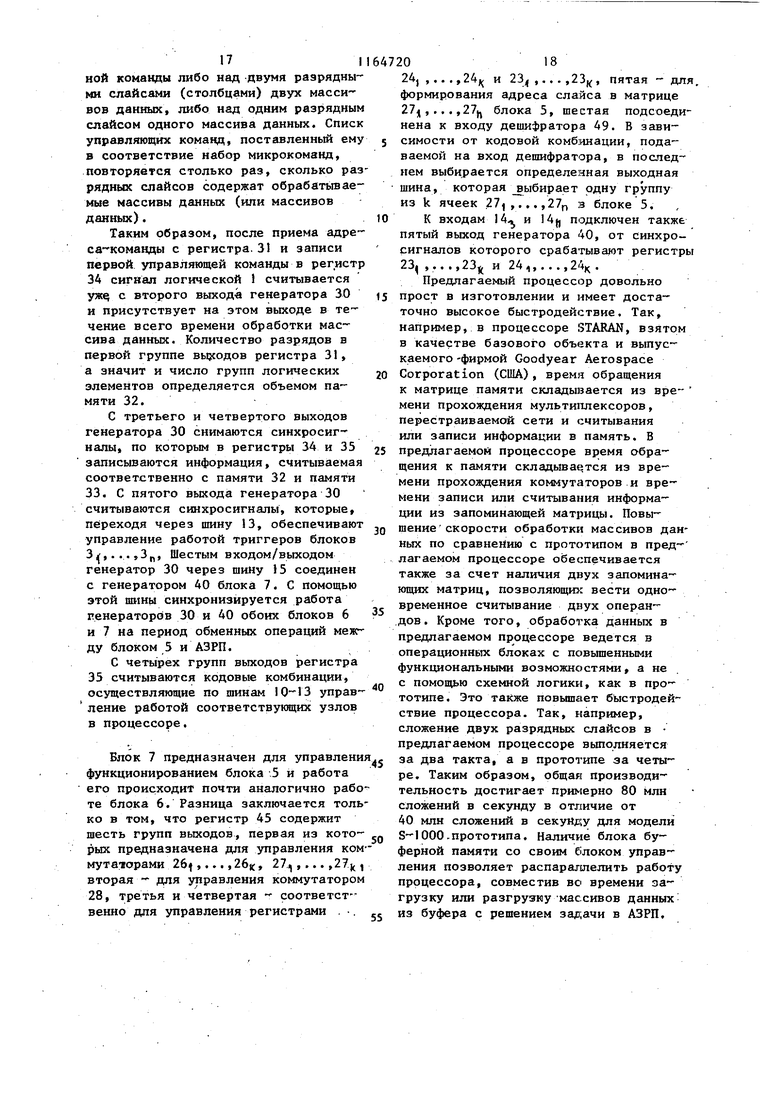

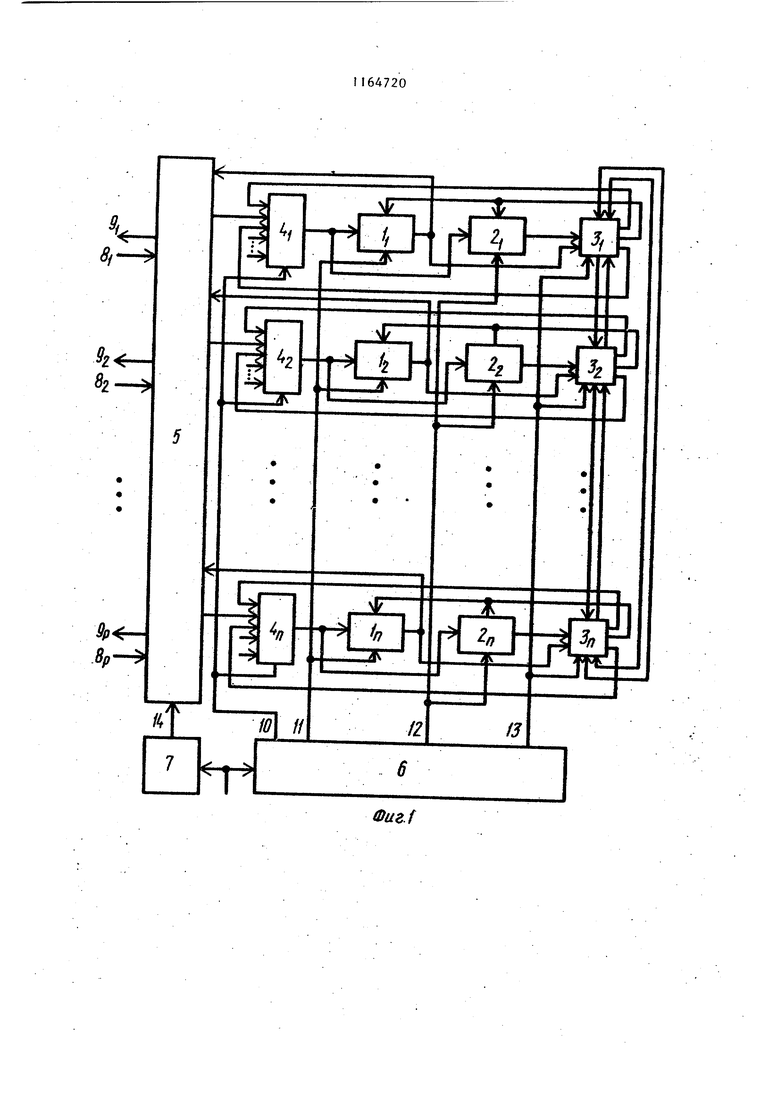

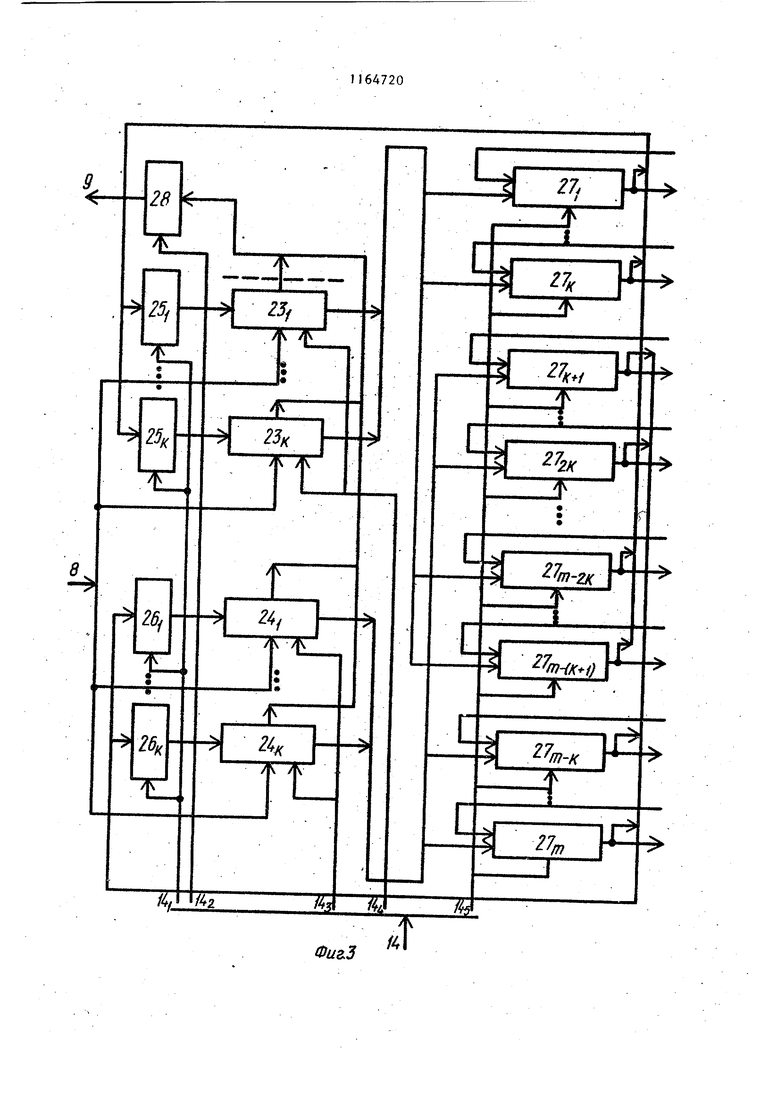

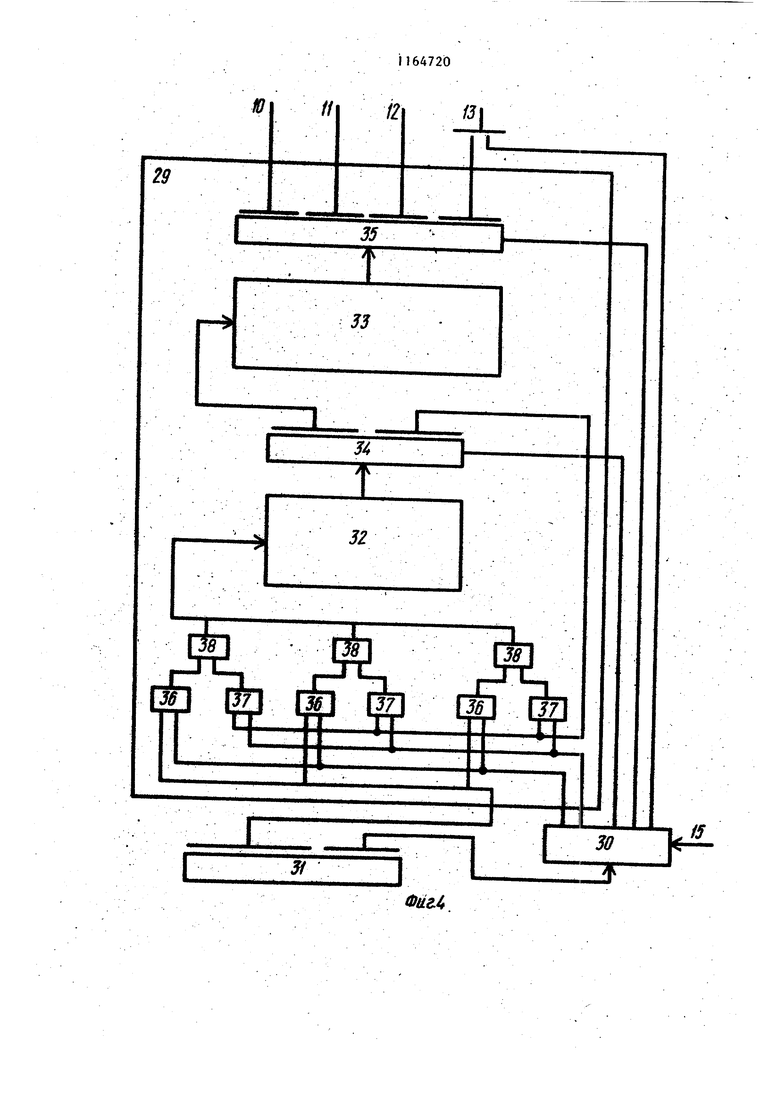

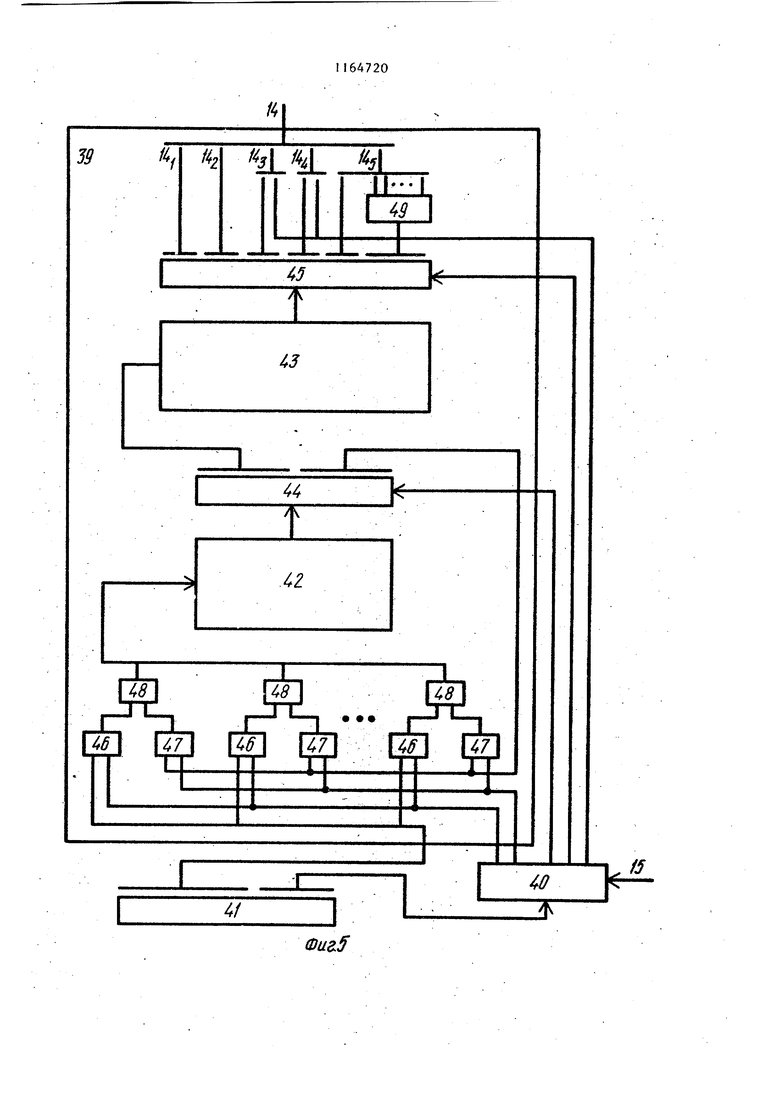

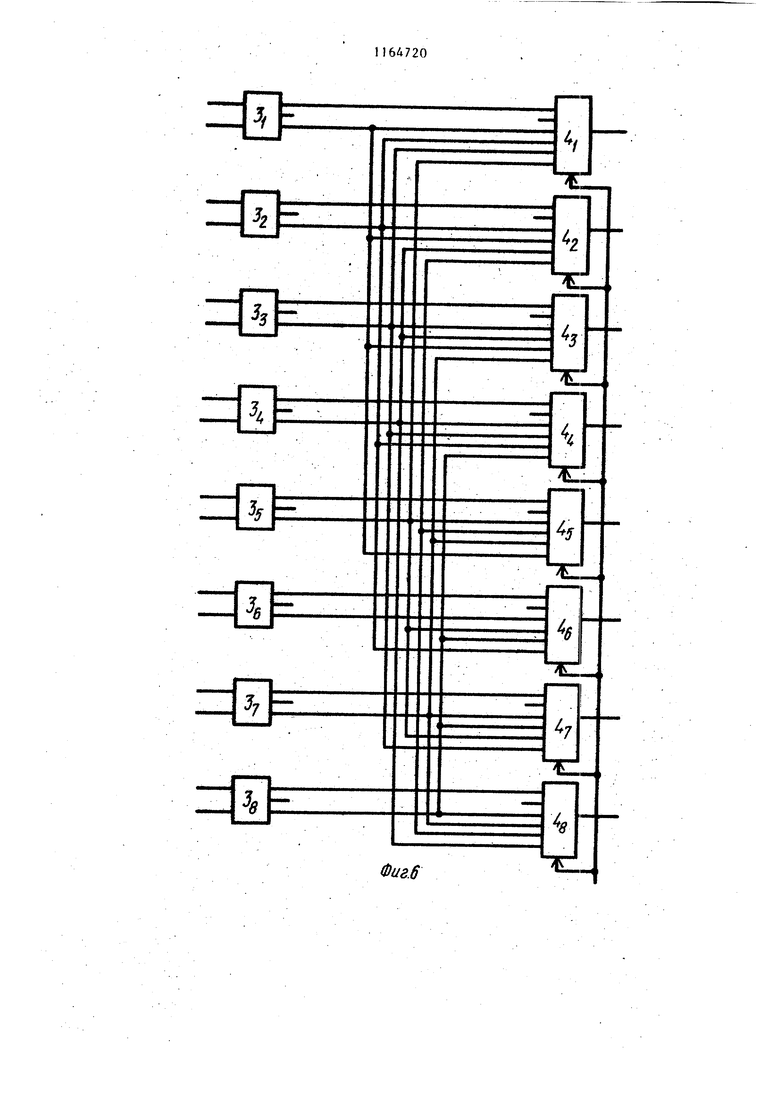

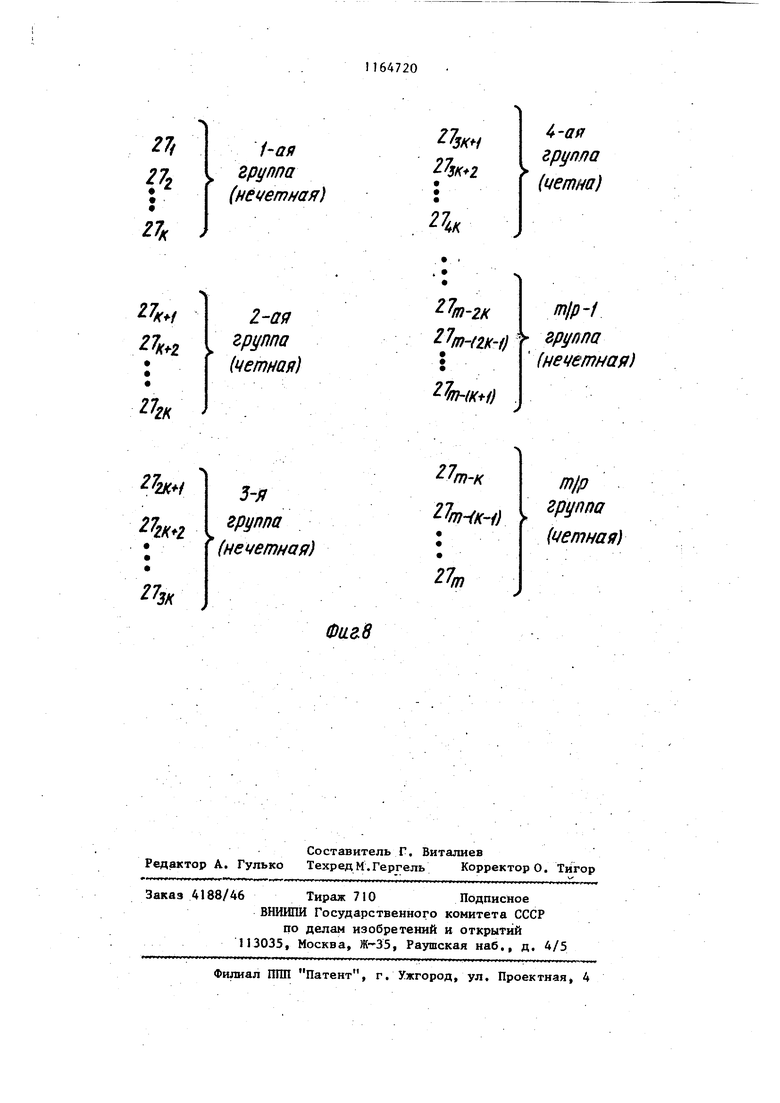

Иэобретение относится -к вычислительной технике и может : быть исj цольэовано для параллельной обработки информации. Известен ассоциативный параллельный процессор, содержащий три матрицы ассоциативной памяти, построенные на специальных элементах АЗУ, местное устройство управления, внеш. нее устройство управления и входные устройства с регистрами опроса, запи си и считывания ij. Однако подобные процессоры пока не нашли практического применения из-за громоздкости алгоритмов обра ботки данных, дороговизны специальных элементов, большой лотребляемой мощности.- Наиболее близким к изобретению является ассоциативный матричный процессор, содержащий устройство управления, блок параллельного ввода-вывода, ассоциативный матринный модуль, содержапдай матрицу памяти, обрабатывающие элементы на каждую строку памяти, перестановочную сеть, мультиплексор (блок коммутации). Матрица памяти связана с обрабатывающими элементами: через перестановочную сеть и мультиплексор. Обработка информации происходит в обрабатывающих элементах путем последовательного вьшесения разрядного среза из матрицы памяти. Выборка раз рядного среза осуществляется с помощью сложной перестановочной сети, составляющей 80% стоимости матрицы памяти 2 и З . Недостатком данного процессора яв ляется необходимость прохождения HH формации как в режиме записи ее в матрицу памяти, так и-в режиме выбор ки через сложную перестановочную сеть, что приводит к значительному снижению быстродействия процессора, а также надежности процессора в цело так как перестановочная сеть состоит из большого количества элементов. Кроме того, в процессоре отсутствует параллелизм в подготовке и обработке массивов данных, так как блок параллельного ввода-вывода подготавливает только восемь тридцатидвухразрядных слов. После передачи этих слов в мат рицу памяти-можно подготовить следующие восемь слов, т.к. обменные операции в процессоре STARAN протекают сравнительно медленно. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем что в ассоциативный матричный процессор, содержащий первую группу из п 3апоминаюпцте элементов, п операционных блоков, п коммутаторов и пер вый блок управления, первый, второй и третий выходы и вход которого соединены соответственно с управлякяциьш входами коммутаторов, входами записи запоминающих элементов первой группы, управляющими входами операционны блоков и управляющим входом процесср ра, причем первый вход-выход сдвига каадого операционного блока подключен к вторым входам-выходам сдвига предшествующего операционного блокаj первый информационный вход, первый, второй и третий выходы каждого опера ционного блока соединены соответственно с выходом соответствующего за- поминающего элемента первой группы, первым и вторым информационными входами соответствующего коммутатора и входом разрещения обращения соответ- ствуницего запоминающего элемента первой группы, информационньй вход которого подключен к выходу соответству ющего коммутатора, введены блок буферной памяти, второй блок управления и вторую группу запоминающих элемен1204 тов, управляющие входы, информационные входы, входы разрешения обращения и выходы которых соединены соответственно с четвертым выходом первого блока управления, выходами соответствующих коммутаторов, третьими выходами и вторыми информационными входами соответствующих операционных блоков, вкод и выход второго блока управления подключены соответственно к управляющему входу процессора и управляющему входу блока буферной памяти, первые входы-выхода которого соединены с информационным входом выходом процессора, а вторые входывыходы подключены к третьим информационным входам соответствующих KOMMV тятооов и выходам ссответствзгющих запоминающих элем ентов первой группы. . При этом первый управления содержит генератор синхросигналов, регистр интерфейса, память управляющих комавд, регистр управляющих команд, память микрокоманд, регистр микрокоманд, две группы элементов И и группу элементов ИЛИ, первые и вторые входы и выходы которых со.единены с выходами соответствующих элементов И первой и второй трупп и входом памяти управляющих команд, первый и второй выходы регистра интерфейса подключены соответственно к входу блока, первым входам элементов И первой группы и первому входу генератора синхросигналов, второй вход, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с входом блока, вторыми входами элементов И первой группы, первыми входами элементов И второй группы, управляющим входом регистра равляющих команд, управляющим входом регистра микрокоманд и выходом блока, информационный вход, первый и второй выходы регистра управляющих команд подключены соответственно к выходу йамяти управляющих команд, входу памяти микрокоманд и вторым входам элементов И второй группы, информационный вход и выходы регистра микрокоманд соединены соотетственно с выходом памяти т крокоанд и выходом блока. Второй блок управления содержит ешифратор, вход которого подключен вьпсоду регистра микрокоманд, а выходы дешифратора соединены с выходом блока. Операционный блок содержит сумматор, три триггера, коммутатор, эле мент И и элемент ИЛИ, первый и второй вход и выход которого соединены с вы ходом второго триггера, управляющим входом и третьим выходом блока вход переноса,первый и второй информационный вход, управляющий вход, выход результата и переноса сумматора подключены соответственно к выходу первого триггера, первому и второму инфорьйционным входам блока, управляющему входу блока,первому вхо ду элемента И и информационному вход первого триггера, синхровход и выход первого триггера соединены соответст венно с управляющим входом и первым .выходом блока, второй блок и выход элемента И подключены соответственно к выходу элемента ИЛИ и информационному входу второго триггера, управляющий вход которого соединен с управляющим входом блока, управляющий вход, первый, второй и третий входы и выход коммутатора подключены соответственно к управляющему входу блока, первому входу-выходу сдвига блока,выходу элемента И второму входу-вы ходу сдвига блока,и информационному входу третьего триггера,управляющий вход которого соединен с управляющим входом блока,а выход этого триггера по ключен к второму выходу и второму входу выходу сдвига блока. На фиг. 1 приведена структурная схема ассоциативного матричного процессора; на фиг. 2 -г принципиальная схема операционного блока; на. фиг. 3 - структурная схема одного узла блока буферной памяти; на фиг. 4 - схема первого блока управления; на фиг. 5 - то же, второго блока управления; на фиг. 6 - схема связей восьми операционных блоков с . соответствующими коммутаторами; на фиг. 7 - -таблица функций, выполняемы сумматором операционного блока; на фиг. 8 - разбиение ячеек блока буфер ной памяти на нечетные и четные груп пы с целью подключения их к регистра сдвига. Процессор содержит (фиг. I) две идентичные запоминакядие матрицы, состоящие из п запоминакицих элементов с .произвольной выборкой 1| , Ig 1 ft и 2 , 2,...2, операционные блок . ,3.,, коммутаторы 4, , г блок буферной памяти 5 и два бло6 и.7 управления. Входы 8, 8,..., р и выходы 9f, 9,...,9р процессора подключены к перььм входам и выходам блока 5, вторые выходы которого соединены с вторыми входами соответствующих коммутаторов 4, 42,-.-,4. Информационные входы одноименных элементов If, 2j, 1 и 2у,... , 1, и 2 двух матри1 объединены и подключены к выходам соответствующих коммутаторов 4( , 4,,..,4j. Выходы элементов 2t,2j,,.,,2n соединены с первыми входами соответствующих блоков 31, 3 ,.. . ,3f,, вторые входы которых объединены с вторыми входами блока 5 и подключены к входам соответствующих элементов 1 ,22 ,. . ., I. Входы разрешения обращения одноименных элементов 1 и 2, 1- и 22,... 1) и 2 объединены и подсоединены к вторым выходам соответствующих блоков 3 ,3, .. .3,, первые выходы которых подключены к первым входам соответствующих коммутаторов 4,, 4,,,...,4. Ч . +2 Третий выход блока 3 подключен третьему входу коммутатора 4, к четвертому входу коммутатора 4г, пятому входу коммутатора 4 и т.д.. Третий вход блока 32 подключен к третьему входу коммутатора 42, к четвертому входу коммутатора 4, пятому входу коммутатора 4 и т.д.. Каждый ,. блок 3,3-,...3 через первые вход и выход сдвига подключен соответственно к вторым выходу и входу сдвига предыдущего, блока 3, а первые вход и выход сдвига блока 3/ соединены соответственно с вторыми выходом и входом сдвига.блока 3,,. Управляющие входы коммутаторов 4. ,4,.. . ,4 элементов 1-( , Ц 2, ,2,.. .,2„ и блоков 3,|, 3,,...,3;, соответственно объединены и соединены управляющими шинами 10-13 с выходами блока 6. Управляющий вход блока 5 соединен с вькодом блока 7 управля- ницей шиной 14. Входы блоков 6 и 7 подключены к управляющему входу 15 процессора.. Операционный блок (фиг. 2) содержит одноразрядный сумматор 16, логические элементы И 17 и: ИЛИ 18, триггеры 19, 20 и 21 и коммутатор 22, два информационных входа, выход переноса, информационный и управляющий выходы, первые и вторые входы и выходы сдвига и управляющий вход. Первые два входа сумматора 16 соединены синформационными входами блоками, первьй- вьшод сумматора 16 подключен к входу триггера 19, выход которого соединен с выходом переноса блока 3 и третьим входом сумматора J6. Второй выход суммато ра 16 соединен с вторым входом элемента 17. Вход триггера 20 и второй вход коммутатора 22 объединены и подключены к выходу .элемента 17. Выход триггера 20 соединен с первым входом элемента 18, выход которого яв ляется управляющим выходом блока 3 и подключен к первому входу элемента 17 Первый и третий входы коммутатора 22 являются соответственно, первым и вто- рым входами сдвига блока 3. Выход ком мутатора 22 соединен с входом триггег ра 21, выход которого является инфор: мационным вьосодом блока 3, а .также . первым и вторым выходами сдвига блока 3. Управляющие входы сумматора 16, триггеров 19, 20 и 21 коммутатора 22 и второй вход элемента 18 подключены соответственно к выходам 13, 13, 13, 13, 13, 135 управляющей шины 13 блока 3. Блок 5 разбит на п/м иден тичных узлов, каждый из которых (фиг. 3.) содержит два блока регистр ров 23, 232....,23 и 24,, ,.. 24)f сдвига, коммутаторы 25,,25-,..., 25 к и 26,26,,...,26,ячейки 27 ,,27,...,27 памяти, сгруппированные определенным образом в четные и нечетные группы (фиг. 7), н выходной коммутатор 28. Параллельные регистров 23 ,232 ,... ,23((, А, ,24, ,.. 24,( объединены и подключены к .одному из входов 8 процессора, а параллельные .выходы этих регистров соединены с коммутатором 29. Выход коммутатора 28 является одним из выходов 9 процессора. Последовательные выхода регнстров 23f ,23,... ,23(с подсоединены к вторым 27,,27,,...,27 входам k чп-ЗЦ: 27 27,(,j нечетных групп, а 27. последовательные выходы регистров 24 ,24,.. . ,24. подсоединены к втО рым входам ячеек 271(., ,21,27, 27.ц, 27,(,j.. .,27 четных групп Первые входы ячеек 21 f ,21 t ,27 -121 являются вторыми входами блока 5, а их выходы являются вторыми выходами блока 5 и подключены к входам соответствующих коммутаторов 25, 254,...,25к и 26,26г,...,26зс. Выхо1208 ды коммутаторов 25 ,25,25| н 26(,26j , . ,. ,26;j( соединены с последовательными входами соответствующих,, регистров 23 ,23 ,... ,23|( и 24, 24 ,. .. ,24)t. Управляющие входы коммутаторов 26f ,26 .... ,26|, 25.(, 252,...,25 к и 28, регистров 23, 23, .. ;.,23, 24,24,.,.,24|j и ячеек 27,27-2 ,... ,27|„ соответствующими шинами соединены с управляющей шиной 14 блока 5. . Блок 6 управления (фнг. 4) срстоит из узла 29 микропрограммного управления, генератора 30. синхросигналов и регистра 31 интерфейса, прнчем узел 29 содержит память 32 управляющих команд, память 33 микрокоманд, регистр 34 управляющих команд, регтнстр 35 микрокоманд, группы логических элементов, каждая из которых со- стоит из двух элементов И 36 и 37, и одного элемента ШШ 38. При этом входы элементов lUW 38 подюпочены к входам элешнтов И 36 и 37, а вьосоды - к адресньм входам памяти 32« выход которой подключем к информационным входам регистра 34, Первая группа выходов этого регистра подсоэдннена к адресным, входам пам1гги 33, а вторая - к первым входам элементов 37 всех групп логических элементов. Первые входы всех элементов 36 подключены к первой группе выходов регистра 31, вторая группа выходов которого подключена к входу генератора 30. Пять выходов генера- тора 30 подключены соответственно К объединенным вторьм входам элемеитов 36, к объединеишш вторым входам элементов 37, к управляющим входам регистра 34 и регистра 35, а также к выходной управляющей шше 13. Шестой выход генератора 30 подключен к управлякщему входу 15 процессора. Блок 7 (фиг. 5) состоит нз узла 39 микропрограммного управления, генератора 40 синхросигналов и регистра 41 интерфейса, причем узел 30 содержит память 42 управляющих команд, память 43 микрокоманд, регистр 44 управляющих команд, регистр 45 микрокоманд, группы логических элемен. тов, каждая из которых состоит из вух элементов И 46 и 47 и одного элемента ИЛИ 48, а также дешифратор 49. При этом входы элементов ИЛИ 48 подключены к выходам элементов И 46 47, а вьпсоды - к адресным входам памяти 42, выход которой подключен I к информационным входам регистра 44, Первая группа выходов этого регистра подсоединена к адресным входам памяти 43, а вторая к первым входам элементов 47 всех групп логичес ких элементов. Первые входы ;всех эле ментов 46 подключены к первой группе выходов регистра 41, вторая группа выходов которого подключена к входу генератора 40. Пять выходов генеоатора 40 подключены соответственно к объединенным вторым входам элементов 46, к рбъеданенным вторым входам эле ментов 47, к управляющим входам регистра 44 и регистра 45 и к входам 14,, 144 управляющей шины 14. Шестой выход генератора 40 подключен к управляющему входу 15 процессора. Выходы регистра 45 с первой по пятую группы подключены соответствен но к входам 14 -14f управляющей шины 14, а шестая группа выходов соединена с входом дешифратора 49, выходы которого подключены к входу 14 г управляющей шины 14 блока 7. Функционирование ассоциативного .матричного процессора (фиг. 1) проис ходит следующим образом. На первом этапе осуществляется загрузка последовательно по словам поканалам 8,8,,..,8р массивов данных сначала в блок 5, а затем ввод этих же массивов данных уже последовательно по разрядам и параллельно по словам через вторые входы коммутато- ров 4 ,4-2.. .. ,4 , в элементы ... 1) и 2 ,,2 ,.. . ,2 , причем в обе запоминающие матрицы записывается идентичная информация. Необходимость хранения идентичной информации в обеих группах элементов 1 ,..., 1|, и 2,,..,2f, объясняется тем, что при, выполнении ряда арифметических илогических операций необходимо одновремен но обращаться к разниц разрядным сла сам одного и того же массива данных, что существенно сказывается на скорости вьшолнения данных операций. Коммутаторы 4(. ,4, .. ,4 настраиваются на пропускание информации из блока 5 или с другого направления с помощью управляющих сигналов, поступающих из блока 6 -по шине 10. Основным решающим ресурсом в предлагаемом процессоре является ассоциативное запоминающее решающее поле (АЗРП), содержащее 11 010 входные коммутаторы 4 ,4j,,.. . ,4, две запоминающие матрицы ЗЛементйв 1 tJz -л 2 ,22,.. . ,2„ и блоки 3 ,3 ,... ,3 п- При этом каждая запоминающая матрица представляет собой массив запоминающих элементов оперативной памяти с произвольной выборкой с организацией N х 1 бит, где N число бит в одном элементе 1 или 2. Очевидно, что в одном элементе можно разместить N/k k-разрядных слов, а в одной запоминающей матрице N/k It-разрядных массивов данных, т.е. каждый массив в запоминающей матрице размещается в своей коикретно адресуемой зоне. Таким образом, каждая запоминающая матрица разбивается на конкретно адресуемые зоны, в которых хранятся как масивы-операнды, так и массивырезультаты. При этом адресация к зоне и определенному разрядному слайсу в этой-зоне осуществляется в .соответствии с кодовыми комбинациями, приходящими по управляющим шинам Пи J 2 с блока 6. Обработка массивов данных осуществляется в блоках 3,3,:.,. ,3 fl путем последовательного считывания в них разрядных слайсов этих массивов. I Так, например, для.выполнения сложения Двух массивов необходимо повторить столько элементарных сложений, сколько значащш: разрядных слайсов содержится в массивах-операндах. При этом каждое элементарное сложение состоит из двух тактов. В первом такте одноименные слайсы счи- тьюаются с двух матриц lf,lg,...,l, и 2,,2, 2,..2 и посьшаются по двум информационным каналам в блоки 3{ ,32,...,3, где происходит их сложение, запоминание результата сложения и результата переноса, если таковой имеется. Настройка всех блоков 3,...,3, на выполнение конкретной операции осуществляется в соответствии с управляющими сигналами, приходящими по шине 13 из блока 6. Во вторым такте результат сложения с информационных выходов блоков 3,...,3fl пропускается через третьи -входы коммутаторов 4, ...,4„ и записывается в оба запоминающие элементы матриц 1,...,Т„ и 2|....,2jj, Переносы, воз никающие при сложении старших разрядных слайсов, считываются с выходов переноса блоков 3,...,3 и через первые входы коммутаторов 4,.., n записываются в зону массива-резуль тата матриц 1 (,...,„ и 2,..,,2. Наличие управляющих выходов в бло как 3(,...3 позволяет выборочно работать с определенными строками мат риц 1,|,.,.,1п и 2,,.,. 2р. Так, если на управляющих выходах каких-то блоков 3 присутствует уровень логического О, поступающий на управляющи входы соответствуклцих- одноименных элементов I и 2, то-эти строки исключаются из работы. Исключение заключается в том, что в данные элемен ты нельзя записывать или считывать на них информацию. Такая организация предлагаемого процессора позволяет .проводить операции как со всеми чис лами в .массиве данных, так и с выделенным подмассивом. Группа входов в коммутаторах 4jj...,4, начиная с четвертого, предназначена для осуществления пере становочных операций в предлагаемом процессоре. Связи восьми блоков 3 с соответствующими коммутаторами (фиг. б) позволяет осуществлять стандартные перестановки 1 х 1,2 х 2 и 4 X 4. Третьи входы коммутаторов 4,...,4 предназначены для коммутирования информационных бит с соответ ствующих блоков 3,..,.3. Когда же . необходимо осуще.ствить попарную перестановку информационных бит, коммутаторы 4,...,4 настраиваются на пропу екание информации с четвертого входа, При этом информация с блока 3 i будет считана с выхода коммутатора 4-, а информация с блока 3 g с выхода коммутатора 4,f. Аналогично для всех ос тадьных пар блоков 3 и коммутаторов, Для осуществления перестановок 2 х.2 или 4x4 коммутаторы необходимо настроить на пропускание информации соответственно с 5 и 6.входов. Полут ченный на выходах коммутаторов инфор мационный слайс записывается в матри це памяти. Очевидно, что .для перестановки слов в массиве операцию конкретной перестановки надо повто рить для каждого слайса данного маесива. В том случае, если надо провести нестандартные перестановки, ин- формационньш слайс несколько раз пропускается через коммутаторы 4|,... 4(j. Так, например, для перестановки содержимого блока 3 с номером 1, 2, 3, 4 и 5, 6, 7, 8 в блок 3 соответственно с номерами 4, 3,2, 1 и 8, 7, 20 6, 5 необходимо исходный информационный слайс дваязды пропустить через коммутаторы 4,.,.. ,4, в первый раз настроить их на перестановку 2 Хо2, а во второй раз на перестановку 1x1. Наличие первых и вторых входов и выходов сдвига блоков 3,...,3 позволяет в предлагаемом процессоре в сочетайии с заложенньми перестановками осуществлять сложные обменнь1е рации между блоками 3. Полученные в процессоре обработки массивы-резульТаты переписываются в блок 5 последо вательно по разрядам и параллельно по словам, а затем последовательно по словам с выходов 9,...,9р считываются во внешнее ОЗУ. Таким образом, наличие блока 5 в предлагаемом процессоре позволяет параллельно вести обработку массивов данных в АЗРП и осуществлять загрузку новых массивов или выгрузку полу- ченных массивов-результатов. Обработка информации, хранящейся , I f и ,. .. ,2)| в элементах 1 ,...,In и 2 осуществляется в блохах 3,,.... ,(фиг. 2). Набор логических и арифметических операций, выполняемых каждьм блоком 3, определяется сумматором 6 Р помощи которого можно осущест-. влять любую из 16 логических операций и операцию сложения над двумя ;операндами (согласно таблице, приведенной на фиг. 7). Ввиду отсутствия микросхемы одноразрядного АЛУ можно применить серийно выпускаемую микросхему К155МПЗ| предназначенную для логической и арифметической.обработки двух четерехразрядных операндов. При этом для работы используются два младших входа и вход переноса. Выбор одной из 16 логических операций и арифметической операции сложения осуществляется путем подачи соответствующего кодовой комбинации с выхода 13 управляющей шины 13. Триггер I9 служит для запоминания переноса при арифметической обработке данных. Триггер 20 предназначен для определения тех строк в матрицах If «Ц и 24,..,2, которые .подлежат обработке. Триггер 21 служит для запоминания результата логической .и арифметической обработки. Коммутатор 22 предназначен для коммутации информации с трех входов с целью записи ее в триггер 21 либо с предыдущего блока 3.j , либо с сумматора

131

16 данного блока 3;, либо с последукяцего блока 3}, . Первый и третий входы коммутатора 22 предназначены для осуществления операций обмена данными между соседними блоками 3. Настройка коммутатора 22 на коммутацию одного информационного входа происходит в соответствии с кодовой комбинацией, поступающей с выхода I3(j шины 13. Элемент ИЛИ 18 позволяет выдавать на управляющий выход блока 3 информацию либо с триггера 20, либо с выхода I3j шины. 13. Эле7 мент I7 служит для разрешения или запрета прохождения информации из сумматора 16 в триггер 20 и в триггер 21. Запись информации в триггеры 19, 20 и 21 происходит по синхрооигналам, поступающим соответственно с выходов 32, 13,, 13J шины 13. При обработке информации один бит первого операнда и один бит второго операнда считываются из элементов Ij и 2, и поступают на вход сумматора 16, Результат обработки поступает на второй вход элемента 17. На первом входе элемента 17 присутствует уровень логической 1, поступаю11р1Й либо с триггера 20 через элемент 18, либо с выхода 13/ через элемент 18, что является признаком разрешения работы с данной i-й строкой матриц ,,..., У, и 2,...,2. Далее результат обработки поступает .на вход коммутатора 23, с выхода которого записывается в триггер 2I. Одновременно при арифметической обработке пары битов операндов образовавшийся перенос с первого выхода 16 записывается в триггер 19.Результат, записанньйв триггере 19, учитьгоается при сложении последующих пар битов. Полученный результат в триггере 21 может быть записан либо в элементе 1 и 2, либо в соседний блок 3, и 3. . Если требуется игнорировать содержимое триггера 20, то по управляющей шине 13 на вход элемента 18 всех блоков 34,..Ф,3, подается уровень логической 1, что означает разрешение работы со всеми строками. Результат обработки может быть записан также и в триггер 20, что является условием выбора данной строки в матрицах I f,..., Ц и 2,...,2 для последующей обработки.

Таким образом, операция обработки двух бит операндов осуществляется в

47201/4

два этапа. В начале из запоминающих матриц считываются дЕа бита операндов, подается на вход сумматора 16 и результат записывается в триггере 5 21. На втором этапе результат может быть записан в матрицы 1 , .. ., Ij и 2|,...,2. В связи с тем, что блок 3j связан с последним, блоком 3 в процессоре можно осуществлять циклические сдвиги информации, содержащиеся а блоке 3f,...,3. Исходя из практической реализации процессора, триггеры 21 на уровне всех блоков 3,...,3(, можно заменить регистрами

5 сдвига. Ввод и вывод k-разрядной информации в предлагаемом процессоре осуществляется соответственно через входы 8(,...,8 р и выходы 9,...,9 р Каждый из входов и выходов представляет собой канал шириной в k-разря- дов. Блок 5 разбит на n/m р-идентичных .узлов (секций) и каждый из них через свои первые входы и выходы подключен к соответствукщ1;ему входу и

5 выходу 8 ,.. .,8 р и 9у,..,,9 р процессора. Все секции работают параллель. но от управляющих сигналов, поступающих по шине 14 с блока 7. Функционирование одной из секций блока 5

0 (фиг. 3) происходит следующим образом.

Ввод k-разрядной информации в ячейки 27 ,...,27 осуществляется через два блока регистров 23,..., 23 JJ и 24|(-,. . . ,24|(. Причем входная информация по шине 8 поступает на параллельные входы всех регистров 23 ,..., 23(, 24| ,... ,2А K, которые поочередно настраиваются на режим

Q параллельного приема иьгформации.

Установление режима рабюты регистров 23(,.. . ,23j. и 24,... ,24|f осуществляется соответственно с выходов 14 и 14 шины 14. За первые k-тактов

5 осуществляется последовательное зане сение k-разрядной информации в регистры 23,...,23 . В это время регистры 24,...,24 находятся в состоянии покоя. По истечении k-тактов ре-

0 гистры 23| ,... ,23)с переводятся в режим последовательного сдвига, а регистры 24,...,24 - в режим параллельного занесения информации. После заполнения регистров 24, ,...,24| они

5 переводятся в режим последовательного сдвига, и начинается заполнение регистров 23, ... ,24 ,Та.к происходит чередование заполнения считывание двух блоков регистров сдвига. Информация, считываемая с регистров 23,,. . . ,23|(, подводится одновременно к k-ячейкам памяти всех нечетных групп 27 , ... ,27.,.. . ,27. гк 27т-(К4 О регистров 24 ,,..., ц подводится к четным группам ,...,27.(.,..., . г ,,. ,27 (фиг. 8). В соответствии с кодовой комбинацией, поступающей с выхода 145 ины 14, осуществляется выбор режима работы ячеек 27,|,. , . ,27гц. Кроме того, с этого выхода 14 посту пают управляющие сигналы, которые вы бирают для режимов записи или чтения одну четную или нечетную группу, состоящую из k ячеек памяти. Таким образом, каждое k-разрядное слово, записанное в регистре сдвига, записыва ется...в ячейку памяти за k последовательных тактов, но так как загрузка происходит параллельно в k ячеек памяти, то за k тактов в ячейках памят записано k слов. После окончания загрузки п слов в памяти блока 5 находится массив, который затем может быть переписан .в АХРП параллельно по словам и последовательно по разрядам с вторых выходов блока 5. Точно также массивы-результаты из АЗРП поступают последовательно по разрядам и параллельно по словам на вторые входы блока 5 и непосредственно за-писываются в ячейки .. Вывод информации из буфера последовательно по словам с соответствующего выхода 9 происходит следующим образом. Выходы ячеек 27,.,.,27 соединены с коммутаторами 25,...,25)j и 26|,...,26у, причем -выходы нечётных групп ячеек 21 ,. . ., 21, 21t , .. ., 27, ...,27.(„,соединены соо ветственно с входами коммутаторов .25,..,,25, а выходы четных групп ilc-fi 272 ,TfnK.27),yj 27 соединены соответственно с входами . коммутаторов 26,...,26ц. Информация поступающая из первой нечетной группы ячеек 27 ,...,27 через группу коммутаторов 25 ,. . . ,25 j, последовательно заносится за k тактов в групп регистров 23i(,... ,23|; . Затем начинается аналогичное заполнение второй группы регистров 24 ,... ,24|j. через входные коммутаторы 26 первой четной группы ячеек 27,, ,... 27 к . При этом из первой группы регистров 23(,...,23 информация чере.з выходной коммутатор 28 начинает выдаваться с выходов 9 процессора и т.д. Таким образом, происходит поочередное заполнение регистров 23.,...,23 и 24|,...,24к из нечетных и четных групп ячеек 27 ,. . .27|у, при помощи коммутаторов 25., . , (, и 26..., 261 с последующей вьодачей информации через коммутатор 28 с выхода 9 процессора. Функционирование исполнительных ресурсов в процессоре происходит в соответствии с. управляющими сигналами, приходящими по шинам 10-13 с блока 6 и по щине 14 с блока 7. , Рассмотрим работу блока . 4), Управляющее слово, содержащее код команды, которую надо выполнить в АЗРП, и сигналы управления генератором 30, поступает на регистр 31, с второй группы выходов которого сигналы управления подаются в генератор 30 и разрешают появление на его выходах синхросигналов, Сигнал логической 1, снимаемый с первого или с второго выходов генератора 30, поступает соответственно на вторые входы элементов 36 или-37 всех групп соответственно логических элементов уз- ла1 29 и разрешает прохождение информации с двух направлений: либо с первой группы выходов регистра 31, либо с второй группы выходов регистра 34, Присутствие сигналов логической 1 одновременно на двух первых выходах генератора 30 исключается. В на- -чальный момент времени сигнал логической 1 подается с первого выхода генератора 30 и разрешает прохождение кода команды, которую необходимо выполнить в АЗРП предлагаемого процессора, на адресные входы памяти. Управляющие команды, хранящиеся в памяти 32, состоят из двух частей: в первой указан адрес соответствующей микрокоманды.в памяти 33, а во второй - адрес следующей управляющей команды. Для выполнения той или иной команды (сложить, отнять, найти, переставить попарно и т.д.) в памяти 32 соответствии с адресом командой, оступающей с регистра 31, выбираетя определенный список управляющих оманд. Этому списку управляющих ког.нд Поставлен в соответствие опрееленный набор микрокоманд в памяти .3 необходимый для выполнения заданной команды либо над двумя разрядными слайсами (столбцами) двух масси ВОВ данных, либо над одним разрядным слайсом одного массива данных. Списк управляющих команд, поставленный ему в соответствие набор микрокоманд, повторяется столько раз, сколько разрядных слайсов содержат обрабатьшаеные массивы данных (или массивов данных).

Таким образом, после приема адреса команды с регистра.31 и записи первой управляющей команды в регистр ЗА сигнал логической 1 считывается уж с второго выхода генератора 30 и присутствует на этом выходе в течение всего времени обработки мас сива данных. Количество разрядов в первой группе выгсодов регистра 31, а значит и число групп логических элементов определяется объемом па мяти 32.

С третьего и четвертого выходов генератора 30 снимаются синхросиг налы, по которым в регистры 34 и 35 записьюаются информация, считываемая соответственно с памяти 32 и памяти 33. С пятого выхода генератора 30 считываются синхросигналы, которые, переходя через шину 13, обеспечивают управление работой триггеров блоков 3/,...,3, Шестым входом/выходом генератор 30 через шину 15 соединен с генератором 40 блока 7. С помощью этой шины синхронизируется работа генераторов 30 и 40 обоих блоков 6 и 7 на период обменных операций меж ду блоком 5 и АЗРП.

С четырех групп выходов регистра 35 считываются кодовые комбинации, осуществляющие по шинам управ ление работой соответствующих узлов в процессоре.

Блок 7 предназначен для управлени функционированием блока 5 и работа его происходит почти аналогично работе блока 6. Разница заключается только в том, что регистр 45 содержит шесть групп выходов, первая из которык предназначена для згправления коммутаторами 26f,. ., 26)(, 27.Ц ,... ,27( f вторая для управления коммутатором 28, третья и четвертая - соответст венно для управления регистрами . -.

24, .... ,24j- и 23 ,.. . ,23, пятая - дл формирования адреса слайса в матрице 27j(,...,27 блока 5, шестая подсоединена к входу дешифратора 49. В зависимости от кодовой кoмб: шaции, подаваемой на вход дешифратора, в последнем выбирается определенная выходная шина, которая выбирает одну группу из k ячеек .27,...,27р )з блоке 5.

К входам 14 и 14j) подключен также пятый выход генератора 40, от синхросигналов которого срабатывают регистр 23, ,...,23 и 24,,...,24,.

Предлагаемый процессор довольно прост в изготовлении и имеет достаточно высокое быстродействие. Так, например, в процессоре STARAN, взятом в качестве базового объекта и выпускаемого -фирмой Goodyear Aerospace Corporation (США), время обращения к матрице памяти складывается из времени прохождения мультиплексоров, перестраиваемой сети и считывания или записи информации в память. В предлагаемой процессоре время обращения к памяти складывается из времени прохождения коммутаторов и времени записи или считывания информации из запоминающей матрицы. Повышение скорости обработки массивов данных по сравнению с прототипом в пред- лагаемом процессоре обеспечивается также за счет наличия диух запоминающих матриц, позволяющи : вести одновременное считывание днух операндов. Кроме того, обработка данных в предлагаемом процессоре ведется в операционных блоках с повьппенными функциональными возможностями, а не . с помощью схемной логики, как в прототипе. Это также повышает быстродействие процессора. Так, например, сложение двух разрядных слайсов в предлагаемом процессоре выполняется за два такта, а в прототипе за четыре. Таким образом, общая производительность достигает примерно 80 млн сложений в секунду в от 40 млн сложений в секуНд1;у для модели S-1000.прототипа. Наличие блока буферной памяти со своим блоком управления позволяет распарахиелить работу процессора, совместив во времени загрузку или разгрузку массивов данныхиз буфера с решением зар;ачи в АЗРП.

5±

C4J

csi

. «V4

s

«и

Фиг.3

Ж

ю

dt

30

Фиг.5

ж::

Фиг.6

Фиг.7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запор для дверей крытых товарных вагонов | 1923 |

|

SU479A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| STARAN | |||

| - Зарубежная радиоэлектроника, 1977, № 1 (прототипVi | |||

Авторы

Даты

1985-06-30—Публикация

1982-04-22—Подача