ный вход пятого D -триггера соединен с выходом второго элемента И, второй вход которого соединен с выходом вто рого элемента НЕ, вход которого соединен с вторым входом первого элемента И, выход которого соединен с информационным входом четвертого D-триггера блока управления, прямой выхоя третьего D -триггера которого coefimf с входом сложения сумматато15% вычитателя, вход вьЛйтания котороге соединен с входом вычитания вычитающего счетчика и с прямым выходом пятого D -триггера блока управления, выход четвертого элемента ИЛИ которого соединен с входом записи регистра частного, вход сброса которого соединен с прямым выходом восьмого О - триггера блока управления, вход первого элемента НЕ которого соединен с выходом счетчика, вход сброса кото рого соединен с прямым выходом первого П -триггера блока управления, выход третьего элемента ИЛИ которого соединен с информационным входом счетчика, выход знакового разряда регистра остатка соединен с входом второго элемента НЕ блока управления выход первого элемента ИЛИ которого соединен с входом сдвига регистра частного, вход записи вычитающего 1 08 счетчика соединен с прямым выходом второго Л -триггера блока управления, выходы И/2-старщих разрядов регистра остатка ( п - разрядность операндов) соединены соответственно с входами первой группы блока памяти, входы второй группы которого соединены соответственно с выходами П/4старших разрядов регистра делителя, выходы П разрядов которого соединены с соответствующими информационными входами блока умножителей, управляющий вход которого соединен с выходом вычитающего счетчика, выходы блока умножителей - с соответствукщими входами сумматора, выходы которого соединены соответственно с информационными входами первой группы сумматора-вычитателя, информационные входы второй группы которого соединены соответственно с выходами регистра остатка, информационные входы которого соединены соответственно с выходами сумматора-вычитателя, информационные входы Первой группы которого соединены соответственно с выходами И разрядов регистра делителя, вход записи регистра остатка соединен с выходом второго элемента ИЛИ блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1986 |

|

SU1325467A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для деления с самоконтролем | 1987 |

|

SU1559346A2 |

| Устройство для деления | 1984 |

|

SU1203515A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок управления, регистр частного, счетчик, сумматор, регистр остатка, регистр делителя, отличающееся тем, что, с целью повьшения быстродействия, в него введены блок памяти, сумматор-вьгчитатель, вычитающий счетчик, блок умножителей, а блок управления содержит восемь D -триггеров, два элемента ИИЛИ, четыре элемента ШТИ, три элемента И, два элемента НЕ, три элемента задержки, примем вход начальной установки устройства соединен с установочным входом первого О -триг гера, с входами сброса с второго по восьмой D -триггеров блока управления, вход пуска устройства соединен с первым входом первого элемента ИИЛИ блока управления, тактовый вход устройства - с тактовыми входами всех D -триггеров блока управления, прямой выход первого D -триггера блока управления - с вторым входом первого элемента И-ИЛИ, выход которого соединен с информационным входом второго D -триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ и через первый элемент задержки - с информационным входом третьего D триггера, прямой выход которого соединен с первыми входами первого и второго элементов И, с первыми входами второго и третьего элементов ИЛИ, прямой выход четвертого D-триггера соединен с первым входом четвертого элемента ИЛИ, с третьим входом первого элемента И-И.ПИ, с первым входом второго элемента И-ШТИ, выход которого соединен с информационным входом первого D -триггера, прямой выход пятого D -триггера соединен через второй элемент задержки с информационным входом шестого ffl D-триггера, прямой выход которого соединен с вторым входом второго :элемента ИЛИ, с вторым входом четверС того элемента ИЛИ, с вторым входом с второго элемента И-ИШ-, вторым входом первого элемента ИЛИ, первым входом третьего элемента И, выход которого соединен с информационным входом седьмого О -триггера, прямой выел ход которого соединен с вторым входом .третьего элемента ШЖ, третьим вхоО 00 дом первого элемента ИЛИ и через третий элемент задержки - с информационным входом восьмого D -триггера, прямой выход которого соединен с четвертым входом первого элемента И-ИЛИ, третьим входом второго элемента И-ИЛИ,. четвертый, пятый и шестой входы второго элемента И-ИЛИ соединены с входом первого элемента НЕ, выход которого соединен с пятым, шестым входами первого элемента И-ИЛИ, вторым входом третьего элемента И, информацио

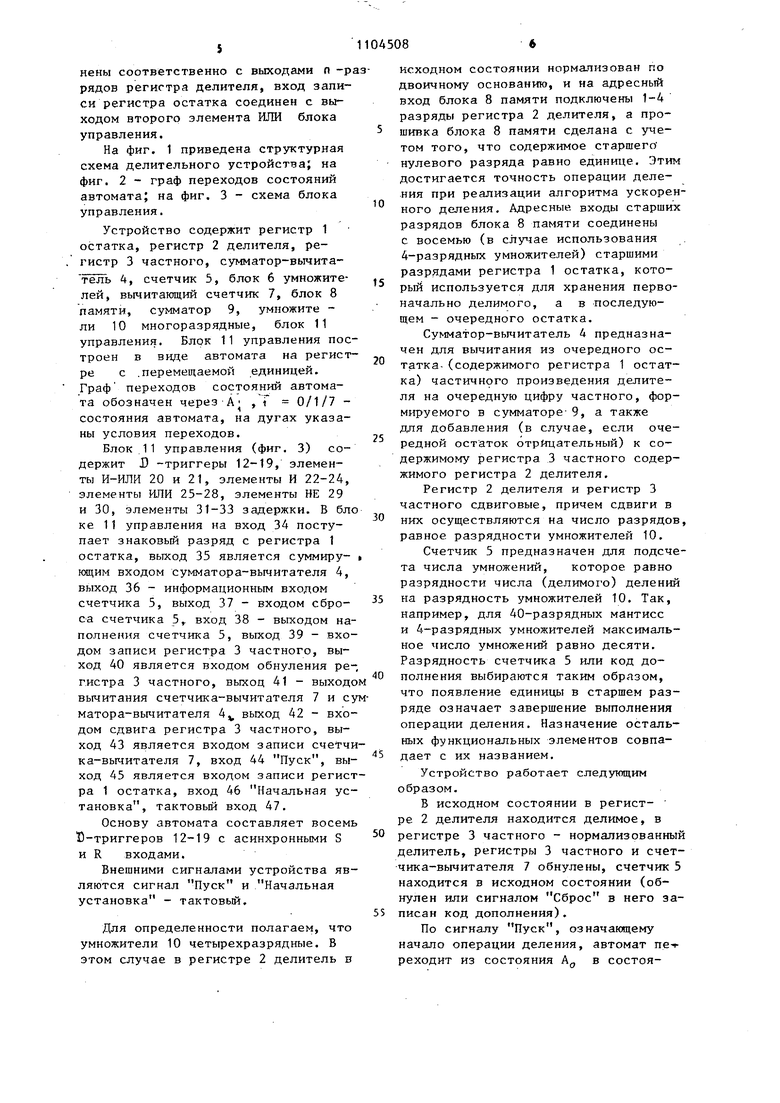

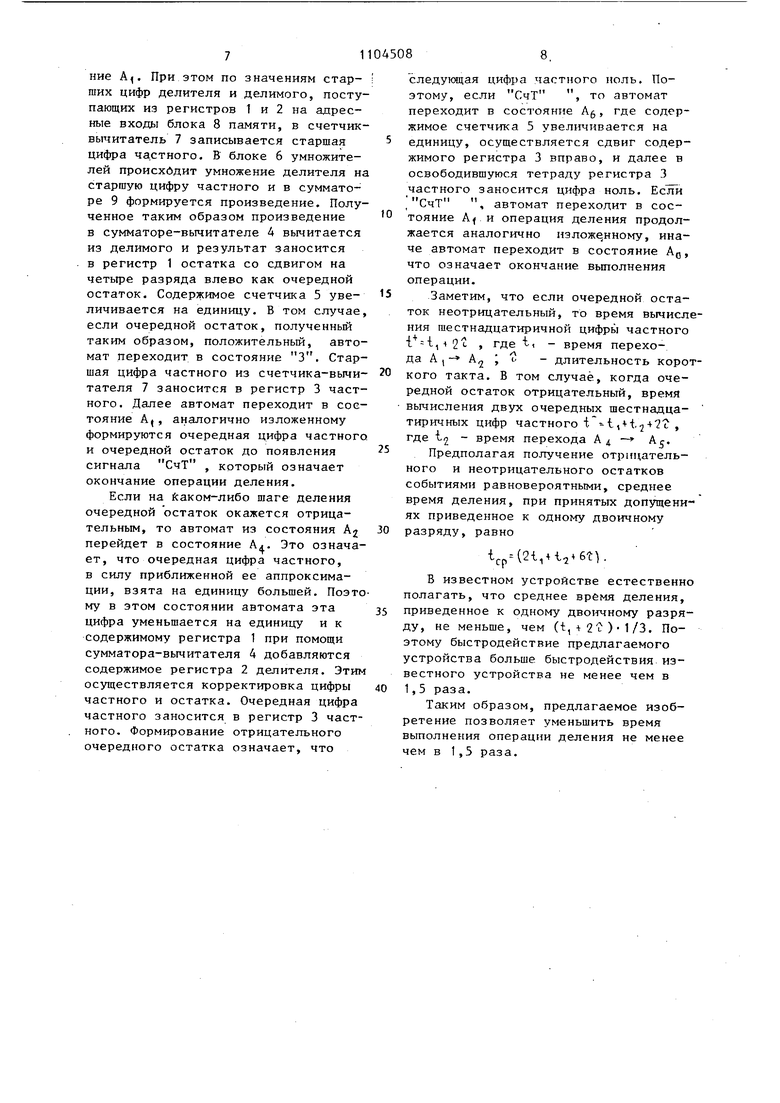

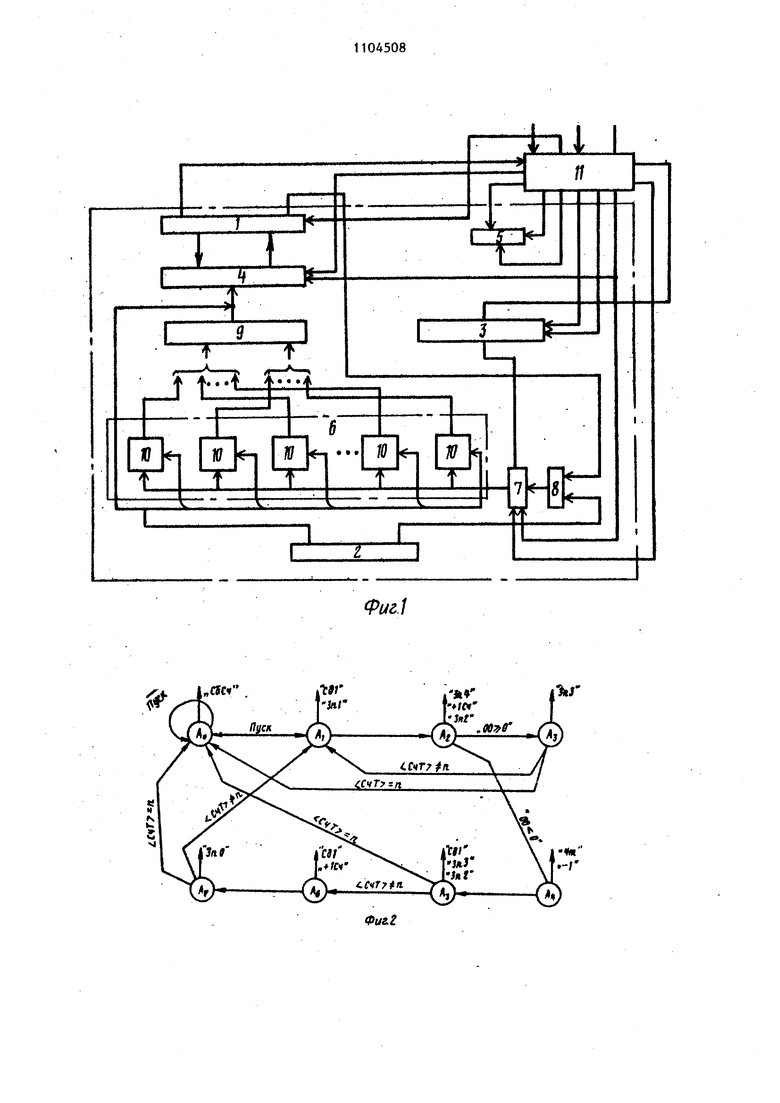

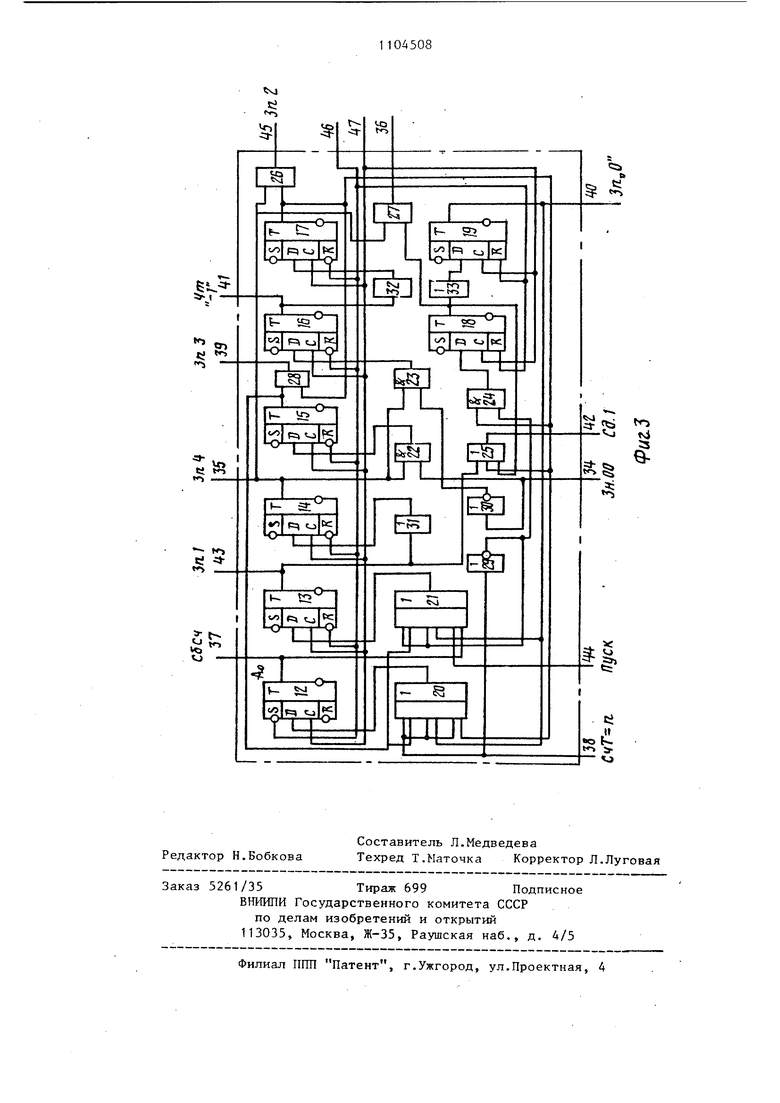

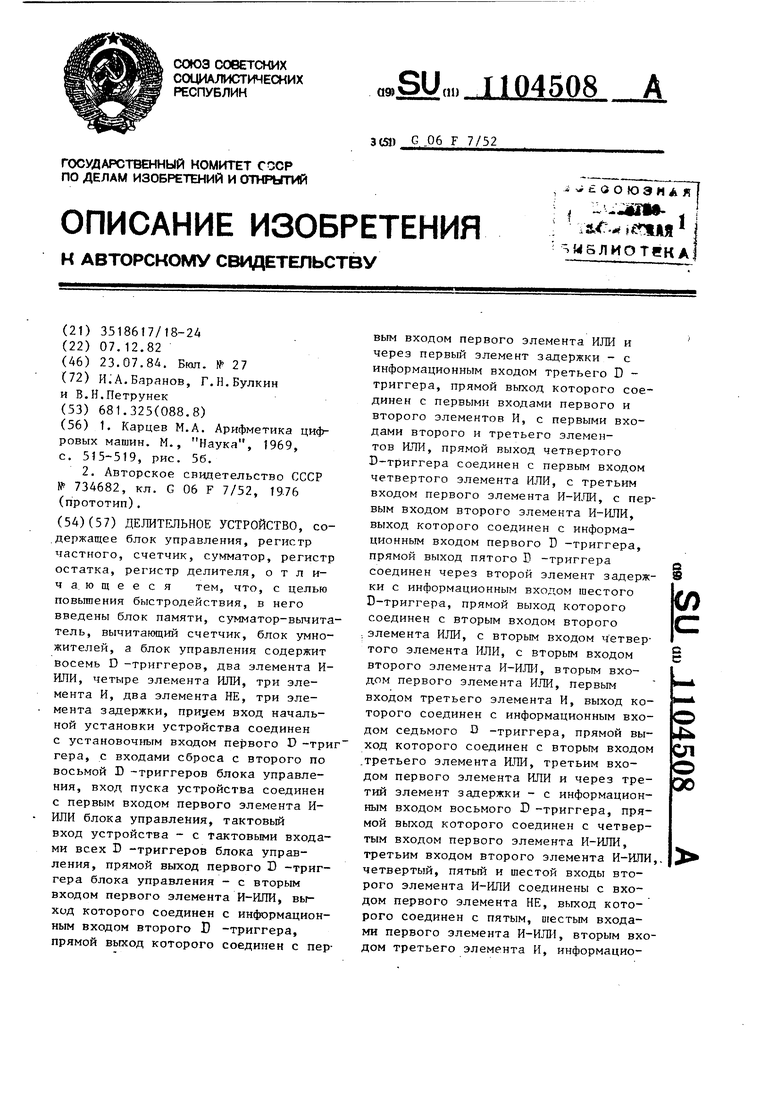

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифмети ческих устройств быстродействующих ЦВМ с жесткими ограничениями на маесогабаритные характеристики и энерг потребление. Известно устройство для деления, реализующее аппаратный метод второго порядка деления двоичных ЧИСЕЛ, содержащее регистр делимого, регистр делителя и горизонтальные ряды одноразрядных сумматоров с элементами на входах 2И-ИЛИ l . Недостатком этого устройства является большая сложность. Наиболее близким к изобретению по технической сущности является устройство для деления, содержащее блок управления, регистр частного, счетчик, сумматор, регистр остатка, регистр делителя 2j. Недостатком известного устройства основанного на реализации логического и аппаратурного первого порядка методов ускорения деления, является большое время выполнения операции деления. Цель изобретения - повьш1ение его быстродействия. Поставленная цель достигается тем, что в устройство для деления, содержащее блок управления, регистр частного, счетчик, сумматор, регистр остатка, регистр делителя, введены блок памяти, сумматор-вычитатель. 3 вычитающий счетчик, блок умножителей а блок упра вления содержит восемь D-триггеров, два элемента И-ИЛИ, четыре элементов ИЛИ, три элемента И, два элемента НЕ, три элемента задерж ки,(причем вход начальной установки устройства соединен с установочным входом первого D -триггера, с входа ми сброса с второго по восьмой D триггеров блока управления, вход пус ка устройства соединен с первым входом первого элемента И-ИЛИ блока управления, тактовый вход устройства с тактовыми входами всех D -триггеро блока управления, прямой выход первого D -триггера блока управления с вторым входом первого элемента ИИЛИ, выход которого соединен с информационным входом второго D -триг гера, прямой выход которого соединен с первым входом первого элемента ИЛИ и через первый элемент задержки - с информационным входом третьего D триггера, прямой выход которого соед нен с первыми входами первого и втор го элементов И, с первыми входами вт рого и третьего элементов ИЛИ, прямо выход четвертого D -триггера соедине с первым входом четвертого элемента ИЛИ, с третьим первого эле мента И-ИЛИ с первым входом второго элемента И-ИЛИ, выход которого соеди нен с информационным входом первого D-триггера, прямой выход пятого Ртриггера соединен через второй элемент задержки с информационным входо шестого D -триггера, прямой выход ко торого соединен с вторым входом второго элемента ИЛИ, с вторым входом четвертого элемента ИЛИ, с вторым входом второго элемента И-ИЛИ, вторым входом первого элемента ИЛИ, пер вым входом третьего элемента И, выход которого соединен с информационным входом седьмого О -триггера, пря мой выход которого соединен с вторым входом третьего элемента ИЛИ, третьим входом первого элемента ИЛИ и через третий элемент задержки - с информационным входом восьмого Р триггера, прямой выход которого соед нен с четвертым входом первого элемента И-ИЛИ, третьим входом второго элемента И-ИЛИ, четвертый, пятый и шестой входы второго элемента И-ИЛИ соединены с входом первого элемента НЕ, выход которого соединен с пятым, шестым входами первого элемен08та И-ИЛИ, вторым входом третьего элемента И, информационный вход пятого D -триггера соединен с выходом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с вторым входом первого элемента И, выход которого соединен с информационным входом четвертого D -триггера блока управления, прямой выход третьего D -триггера которого соединен с входом сложения сумматора-вычитателя, вход вычитания которого соединен с входом вычитания вычитающего счетчика и прямым выходом пятого D -триггера блока управления, выход четверто-. го элемента ИЛИ которого соединен с входом записи регистра частного, вход сброса которого соединен с прямым выходом восьмого D -триггера блока управления, вход первого элемента НЕ которого соединен с выходом счетчика, вход сброса которого соединен с прямым выходом первого D -триггера блока управления, выход третьего элемента ИЛИ которого соединен с информационным входом счетчика, выход знакового разряда регистра остатка соединен с входом второго элемента НЕ блока управления, выход первого элемента ИЛИ которого соединен с входом сдвига регистра частного, вход записи вычитающего счетчика соединен с прямь1м выходом второго D -триггера блока управления, выход П/2-старших разрядов регистра остатка ( П -разрядность операндов) соединены соответственно с входами первой группы блока памяти, входы второй группы которого соединены соответственно с выходами п/4-старших разрядов регистра делителя, выходы п разрядов которого соединены с соответствующими информационными входами блока умножителей, управляющий вход которого соединен с выходом вычитающего счетчика, выходы блока умножителей с соответствующими входами суммато- . ра, выходы которого соединены соответственно с информационными входами первой группы сумматора-вычитате, информационные входы второй групкоторого соединены соответственс выходами регистра остатка, информационные входы которого соединены соответственно с выходами сумматора-вычитателя, информационные входы первой группы которого соедийены соответственно с выходами п -р рядов регистра делителя, вход записи регистра остатка соединен с выходом второго элемента ИЛИ блока управления. На фиг. 1 приведена структурная схема делительного устройства; на фиг. 2 - граф переходов состояний автомата; на фиг. 3 - схема блока управления. Устройство содержит регистр 1 остатка, регистр 2 делителя, регистр 3 частного, сумматор-вычитатёль f, счетчик 5, блок 6 умножителей, вычитающий счетчик 7, блок 8 памяти, сумматор 9, умножите ли 10 многоразрядные, блок 11 управления. Блок 11 управления пос троен в виде автомата на регист ре с .перемещаемой единицей. Граф переходов состояний автомата обозначен через А , i 0/1/7 состояния автомата, на дугах указаны условия переходов. Блок 11 управления (фиг. 3) содержит D -триггеры 12-19, элементы И-ИЛИ 20 и 21, элементы И 22-24, элементы ИЛИ 25-28, элементы НЕ 29 и 30, элементы 31-33 задержки. В бл ке 11 управления на вход 34 поступает знаковьй разряд с регистра 1 остатка, выход 35 является суммиругацим входом сумматора-вычитателя 4, выход 36 - информационным входом счетчика 5, выход 37 - входом сброса счетчика 5,. вход 38 - выходом на полнения счетчика 5, выход 39 - вхо дом записи регистра 3 частного, выход 40 является входом обнуления ре гистра 3 частного, выход 41 - выход вычитания счетчика-вычитателя 7 и с матора-вычитателя 4 выход 42 - вхо дом сдвига регистра 3 частного, выход 43 является входом записи счеТч ка-вычитателя 7, вход 44 Пуск, вы ход 45 является входом записи регис ра 1 остатка, вход 46 Начальная ус тановка, тактовый вход 47. Основу автомата составляет восем -триггеров 12-19 с асинхронными S и R входами. Внешними сигналами устройства яв ляются сигнал Пуск и Начальная установка - тактовый. Для определенности полагаем, что умножители 10 четырехразрядные. В этом случае в регистре 2 делитель в исходном состоянии нормализован по двоичному основанию, и на адресный вход блока 8 памяти подключены 1-4 разряды регистра 2 делителя, а прошивка блока 8 памяти сделана с учетом того, что содержимое старшего нулевого разряда равно единице. Этим достигается точность операции деления при реализации алгоритма ускоренного деления. Адресные входы старших разрядов блока 8 памяти соединены с восемью (в случае использования 4-разрядных умножителей) старшими разрядами регистра 1 остатка, который используется для хранения первоначально делимого, а в последующем - очередного остатка. Сумматор-вычитатель 4 предназначен для вычитания из очередного остатка- (содержимого регистра 1 остатка) частичного произведения делителя на очередную цифру частного, формируемого в сумматоре- 9, а также для добавления (в случае, если очередной остаток отрицательный) к содержимому регистра 3 частного содержимого регистра 2 делителя. Регистр 2 делителя и регистр 3 частного сдвиговые, причем сдвиги в них осуществляются на число разрядов, равное разрядности умножителей 10. Счетчик 3 предназначен для подсчета числа умножений, которое равно разрядности числа (делимого) делений на разрядность умножителей 10. Так, например, для 40-разрядных мантисс и 4-разрядных умножителей максимальное число умножений равно десяти. Разрядность счетчика 5 или код дополнения выбираются таким образом, что появление единицы в старшем разряде означает завершение выполнения операции деления. Назначение остальных функциональных элементов совпадает с их названием. Устройство работает следующим образом. Б исходном состоянии в регисте 2 делителя находится делимое, в регистре 3 частного - нормализованный елитель, регистры 3 частного и счетчика-вычитателя 7 обнулены, счетчик 5 находится в исходном состоянии (обнулен или сигналом Сброс в него записан код дополнения). По сигналу Пуск, означающему начало операции деления, автомат пе еходит из состояния А„ в состояние А. При этом по значениям старших цифр делителя и делимого, поступающих из регистров 1 и 2 на адресные входы блока 8 памяти, в счетчиквычитатель 7 записывается старшая цифра ча.стного. В блоке 6 умножителей происходит умножение делителя на старшую цифру частного и в сумматоре 9 формируется произведение. Полученное таким образом произведение в сумматоре-вычитателе 4 вычитается из делимого и результат заносится в регистр 1 остатка со сдвигом на четыре разряда влево как очередной остаток. Содержимое счетчика 5 увеличивается на единицу. В том случае если очередной остаток, полученньй таким образом, положительный, автомат переходит в состояние 3. Старшая цифра частного из счетчика-вычитателя 7 заносится в регистр 3 частного. Далее автомат переходит в состояние AJ, аналогично изложенному формируются очередная цифра частного и очередной остаток до появления сигнала СчТ , который означает окончание операции деления.

Если на йаком-либо шаге деления очередной остаток окажется отрицательным, то автомат из состояния А перейдет в состояние Ах- Это означает, что очередная цифра частного, в силу приближенной ее аппроксимации, взята на единицу большей. Поэтому в этом состоянии автомата эта цифра уменьшается на единицу и к содержимому регистра 1 при помощи сумматора-вычитателя 4 добавляются содержимое регистра 2 делителя. Этим осуществляется корректировка цифры частного и остатка. Очередная цифра частного заносится в регистр 3 частного. Формирование отрицательного очередного остатка означает, что

следующая цифра частного ноль. Поэтому, если СчТ , то автомат переходит в состояние Ag, где содержимое счетчика 5 увеличивается на единицу, осуществляется сдвиг содержимого регистра 3 вправо, и далее в освободившуюся тетраду регистра 3 частного заносится цифра ноль. Если /СчТ , автомат переходит в состояние А и операция деления продолжается аналогично излoжeннo fy, иначе автомат переходит в состояние Ад, что означает окончание выполнения операции.

Заметим, что если очередной остаток неотрицательный, то время вычислния шестнадцатиричной цифры частного i i,i 2 где t, - время перехода А,- А, i - длительность корокого такта. В том случае, когда очередной остаток отрицательный, время вычисления двух очередных шестнадцатиричных цифр частного. , , где ij время перехода А - А.

Предполагая получение отрицательного и неотрицательного остатков событиями равновероятными, среднее время деления, при принятых допущениях приведенное к одному двоичному разряду, равно

(2i,.

в известном устройстве естественн полагать, что среднее время деления, приведенное к одному дво1тчному разряду, не меньше, чем (t,-v 2L ) 1/3. Поэтому быстродействие предлагаемого устройства больше быстродействия известного устройства не менее чем в 1,5 раза.

Таким образом, предлагаемое изобретение позволяет уменьшить время выполнения операции деления не менее чем в 1,5 раза.

Фиг.1

r

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Открытка или конверт | 1925 |

|

SU515A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для деления | 1976 |

|

SU734682A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1982-12-07—Подача