1

(61) 1483455

(21)4363703/24-24

(22)24.10.87

(46) 23.04.90. Бюл. № 15

(72) А.И.Бобровский, А.В.Воеводин,

Д.В.Мелаев и А.М.Трубицын

(53)681.3(088.8)

(56)Авторское свидетельство СССР ff 1483455, кл. G 06 F 11/00, 1987.

(54)УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ С САМОКОНТРОЛЕМ

(57)Изобретение относится к автоматике и вычислительной технике, может быть использовано при построении операционных блоков цифровых устройств и является усовершенствованием устройства по авт.св.СССР № 1483455, Цель изобретения - повышение достоверности контроля устройства. Устройство содержит регистр 1 остатка, регистр 2 делителя, умножитель 3, блок 4 памяти, ком гутатор 5, вычитающий счетчик 6, триггер 7, элементы И 8, 16, сумматор-вычитатель 9, регистр 10 частного, регистр 11 эталона, элемент ИЛИ-НЕ 12, блок 13 управления, счетчик 14 циклов, блок 15 поразрядного сравнения, элементы ИЛИ 17, 18. Контроль устройства осуществляется проверкой правильности работы блока 4 памяти, на выходе которого не должен появляться нулевой код в р разрядах, и сравнением на блоке 15 равенства состояний регистра 10 частного и регистра 11 эталона. 3 ил.

а S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1986 |

|

SU1325467A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1985 |

|

SU1317431A1 |

| Устройство для деления | 1984 |

|

SU1203515A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано при построении операционных блоков цифровых устройств и является усовершенствованием устройства по а.с.cccpN1483455. Цель изобретения - повышение достоверности контроля устройства. Устройство содержит регистр 1 остатка, регистр 2 делителя, умножитель 3, блок 4 памяти, коммутатор 5, вычитающий счетчик 6, триггер 7, элементы И 8,16, сумматор - вычитатель 9, регистр 10 частного, регистр 11 эталона, элемент ИЛИ-НЕ 12, блок 13 управления, счетчик 14 циклов, блок 15 поразрядного сравнения, элементы ИЛИ 17,18. Контроль устройства осуществляется проверкой правильности работы блока 4 памяти, на выходе которого не должен появляться нулевой код в P разрядах, и сравнением на блоке 15 равенства состояний регистра 10 частного и регистра 11 эталона. 3 ил.

Изобретение относится к автоматике и вычислительной технике, может быть использовано при построении операционных блоков цифровых устройств и является усовершенствованием изобретения по авт.св. № 1483455.

Целью изобретения является повышение достоверности контроля устройства.

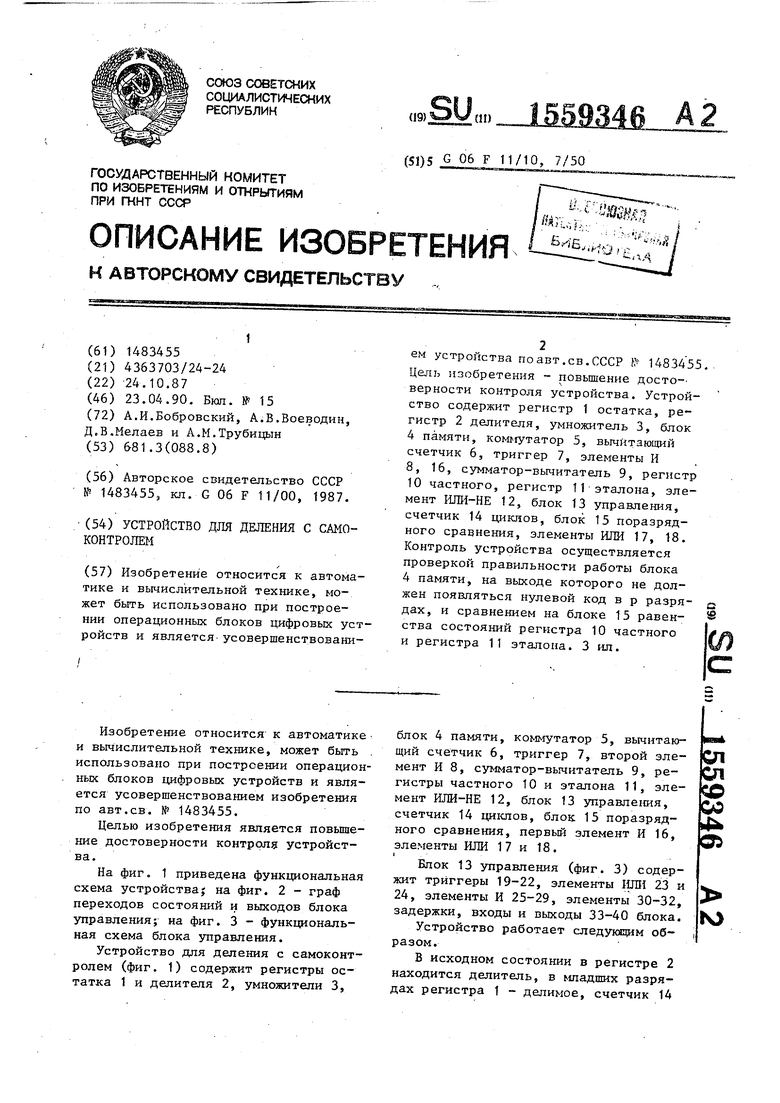

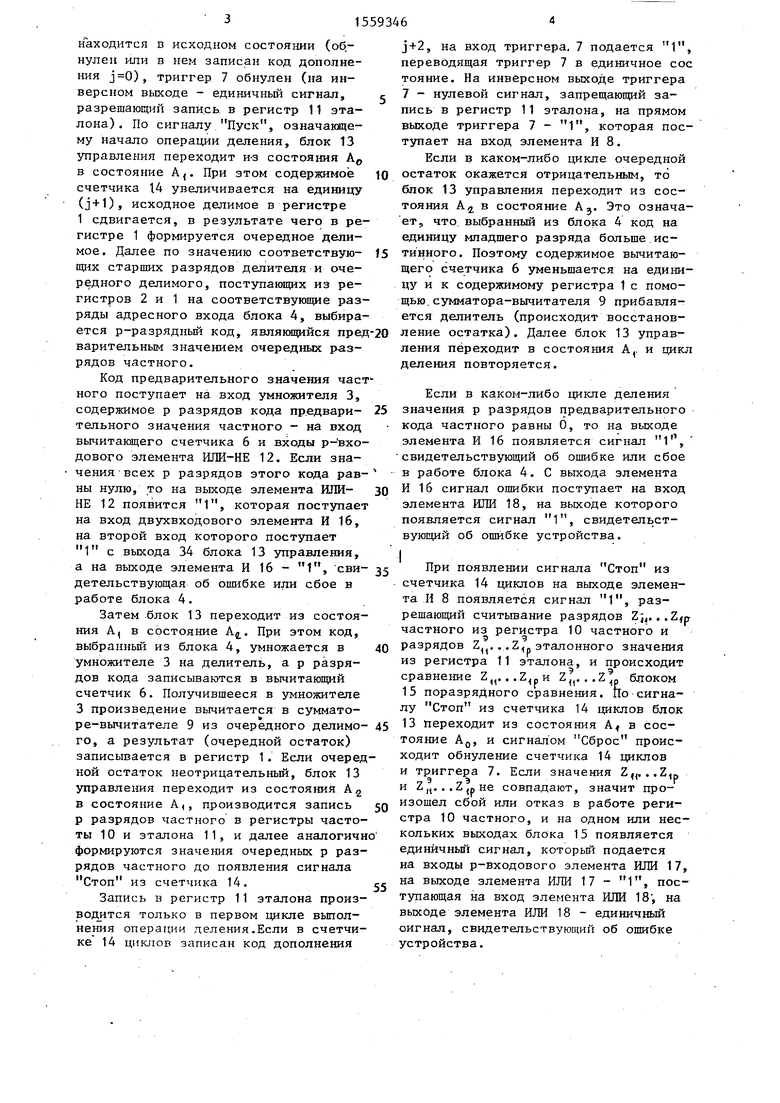

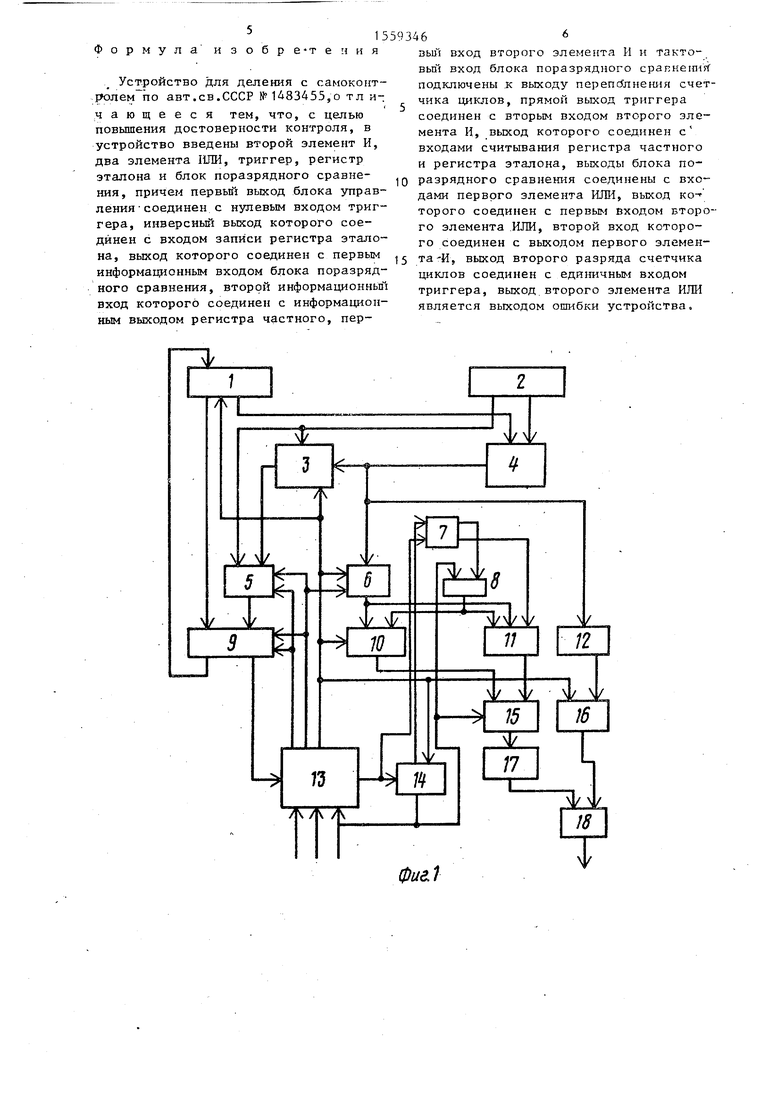

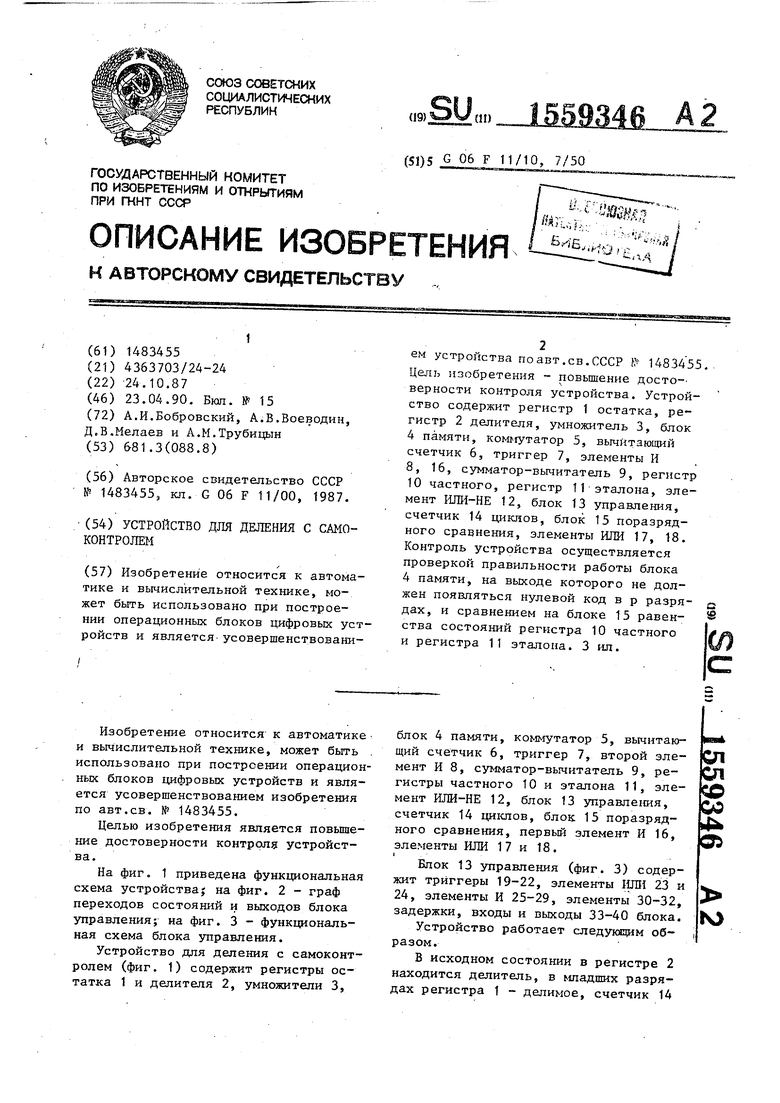

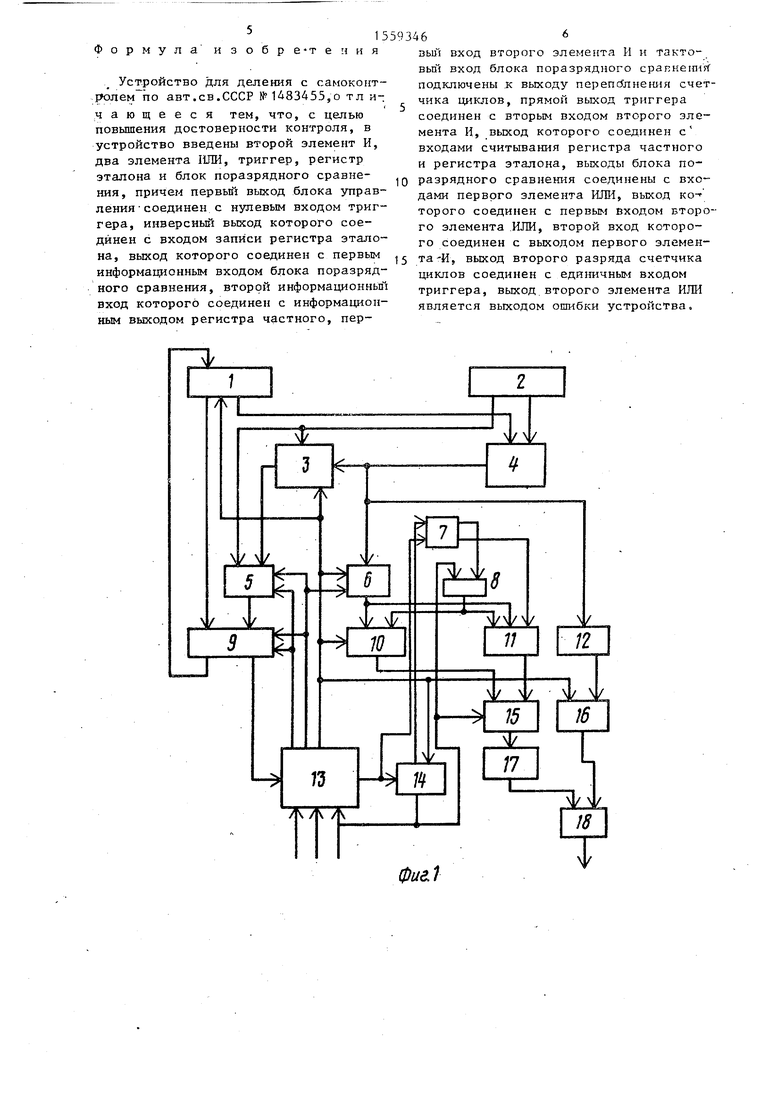

На фиг, 1 приведена функциональная схема устройстваj на фиг. 2 - граф переходов состояний и выходов блока управления; на фиг. 3 - функциональная схема блока управления.

Устройство для деления с самоконтролем (фиг. 1) содержит регистры остатка 1 и делителя 2, умножители 3,

блок 4 памяти, коммутатор 5, вычитающий счетчик 6, триггер 7, второй элемент И 8, сумматор-вычитатель 9, регистры частного 10 и эталона 11, элемент ИЛИ-НЕ 12, блок 13 управления, счетчик 14 циклов, блок 15 поразрядного сравнения, первый элемент И 16, элементы ИЛИ 17 и 18.

i

Блок 13 управления (фиг. 3) содержит триггеры 19-22, элементы ИЛИ 23 и 24, элементы И 25-29, элементы 30-32, задержки, входы и выходы 33-40 блока.

Устройство работает следующим образом.

В исходном состоянии в регистре 2 находится делитель, в младших разрядах регистра 1 - делимое, счетчик 14

сл

СП

Ј 00 4Ь О

Ю

находится в исходном состоянии (обнулен или в нем записан код дополнения ), триггер 7 обнулен (на инверсном выходе - единичный сигнал, разрешающий запись в регистр 11 эталона) . По сигналу Пуск, означающему начало операции деления, блок 13 управления переходит и-з состояния А0 в состояние A. При этом содержимое счетчика 14 увеличивается на единицу (j+1), исходное делимое в регистре 1 сдвигается, в результате чего в регистре 1 формируется очередное делимое. Далее по значению соответствую- щих старших разрядов делителя и очередного делимого, поступающих из регистров 2 и 1 на соответствующие разряды адресного входа блока 4, выбирается р-разрядный код, являющийся пред варительным значением очередных разрядов частного.

Код предварительного значения част ного поступает на вход умножителя 3, содержимое р разрядов кода предвари- тельного значения частного - на вход вычитающего счетчика 6 и входы р- вхо- дового элемента ИЛИ-НЕ 12. Если значения всех р разрядов этого кода равны нулю, то на выходе элемента ИЛИ- НЕ 12 появится 1, которая поступает на вход двухвходового элемента И 16, на второй вход которого поступает 1 с выхода 34 блока 13 управления, а на выходе элемента И 16 - 1, сви- детельствующая об ошибке или сбое в работе блока 4.

Затем блок 13 переходит из состояния А, в состояние At. При этом код, выбранный из блока 4, умножается в умножителе 3 на делитель, а р разрядов кода записываются в вычитающий счетчик 6. Получившееся в умножителе 3 произведение вычитается в суммато- ре-вычитателе 9 из очередного делимо- го, а результат (очередной остаток) записывается в регистр 1. Если очередной остаток неотрицательный, блок 13 управления переходит из состояния А2 в состояние А4, производится запись р разрядов частного в регистры частоты 10 и эталона 11, и далее аналогичн формируются значения очередных р разрядов частного до появления сигнала Стоп из счетчика 14.

Запись ы регистр 11 эталона производится только в первом цикле выполнения операции целения.Если в счетчике 14 циклов записан код дополнения

j+2, на вход триггера. 7 подается 1 переводящая триггер 7 в единичное сое тояние. На инверсном выходе триггера 7 - нулевой сигнал, запрещающий запись в регистр 11 эталона, на прямом выходе триггера 7 - 1, которая поступает на вход элемента И 8.

Если в каком-либо цикле очередной остаток окажется отрицательным, то блок 13 управления переходит из состояния А2 в состояние А. Это означает, что выбранный из блока 4 код на единицу младшего разряда больше истинного. Поэтому содержимое вычитающего счетчика 6 уменьшается на единицу и к содержимому регистра 1 с помощью сумматора-вычитателя 9 прибавляется делитель (происходит восстановление остатка). Далее блок 13 управления переходит в состояния А, и цикл деления повторяется.

Если в каком-либо цикле деления значения р разрядов предварительного кода частного равны 0, то на выходе элемента И 16 появляется сигнал 111, свидетельствующий об ошибке или сбое в работе блока 4. С выхода элемента И 16 сигнал ошибки поступает на вход элемента ИЛИ 18, на выходе которого появляется сигнал 1, свидетельствующий об ошибке устройства.

При появлении сигнала Стоп из счетчика 14 циклов на выходе элемента И 8 появляется сигнал 1, разрешающий считывание разрядов Zj4. ..Zj частного из регистра 10 частного и разрядов ZM ..Z1pэталонного значения из регистра 11 эталона, и происходит сравнение Z,,...Z4pH z r ..z p блоком 15 поразрядного сравнения. По сигналу Стоп из счетчика 14 циклов блок 13 переходит из состояния А в состояние А0, и сигналом Сброс происходит обнуление счетчика 14 циклов и триггера 7. Если значения Z,{. . ,Z,p и ZH. ..Z{pHe совпадают, значит произошел сбой или отказ в работе регистра 10 частного, и на одном или нескольких выходах блока 15 появляется единичный сигнал, который подается на входы р-входового элемента ИЛИ 17 на выходе элемента ИЛИ 17 - 1, поступающая на вход элемента ИЛИ 18; на выходе элемента ИЛИ 18 - единичный сигнал, свидетельствующий об ошибке устройства.

Формула изобре-течия

Устройство для деления с самоконтролем по авт.св.СССР №1483455,о тл ичающееся тем, что, с целью повышения достоверности контроля, в устройство введены второй элемент И, два элемента 1ШИ, триггер, регистр эталона и блок поразрядного сравнения, причем первый выход блока управления соединен с нулевым входом триггера, инверсный выход которого соединен с входом записи регистра эталона, выход которого соединен с первым информационным входом блока поразрядного сравнения, второй информационный вход которого соединен с информационным выходом регистра частного, пер15

1550346

5

вый вход второго элемента И и тактовый вход блока поразрядного сравнения подключены к выходу переполнения счетчика циклов, прямой выход триггера соединен с вторым входом второго элемента И, выход которого соединен с входами считывания регистра частного и регистра эталона, выходы блока поразрядного сравнения соединены с входами первого элемента ИЛИ, выход ко- торого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента -И, выход второго разряда счетчика циклов соединен с единичным входом триггера, выход второго элемента ИЛИ является выходом ошибки устройства.

фие.1

/7#гл

}( At }(A

, W ост С

e V- JSTTa/T

Стоп

iff

,А

.Сяож

-f

It I

fft/. OCfTJ. 4. Q

фиг.2

Авторы

Даты

1990-04-23—Публикация

1987-10-24—Подача