1

Изобретение относится к электросвязи и может быть использовано для передачи сигналов посредством многопозиционных методов модуляции.

Цель изобретения - повышение быстродействия.

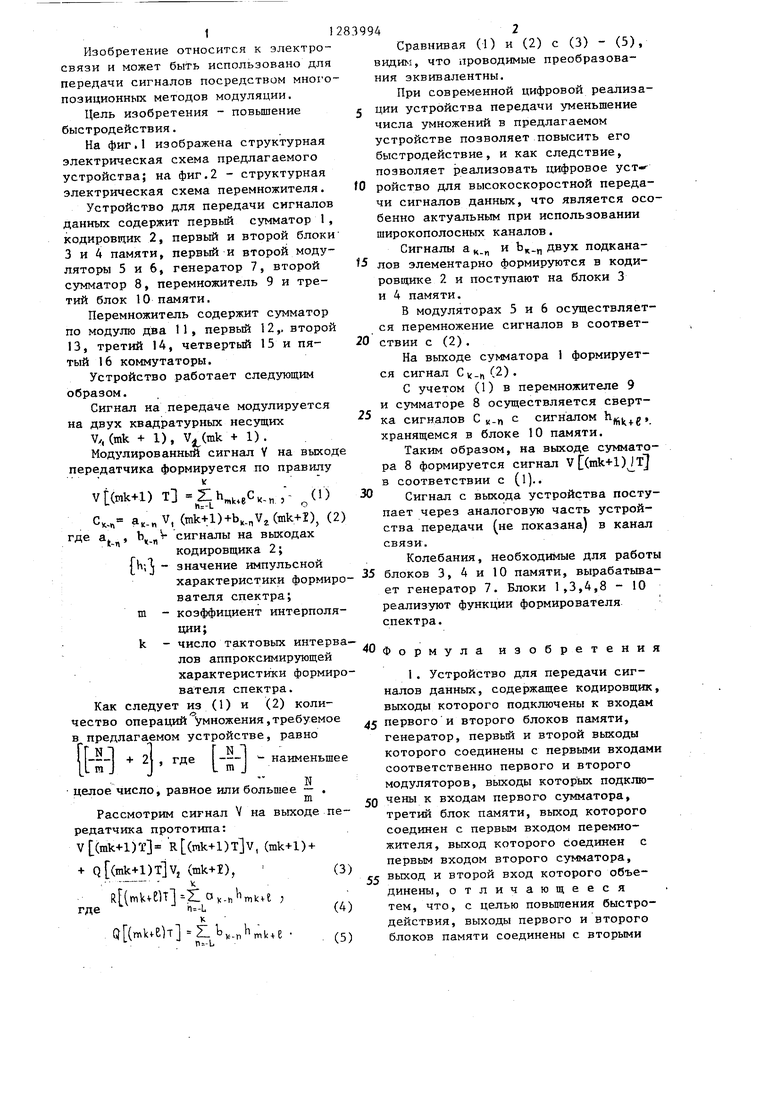

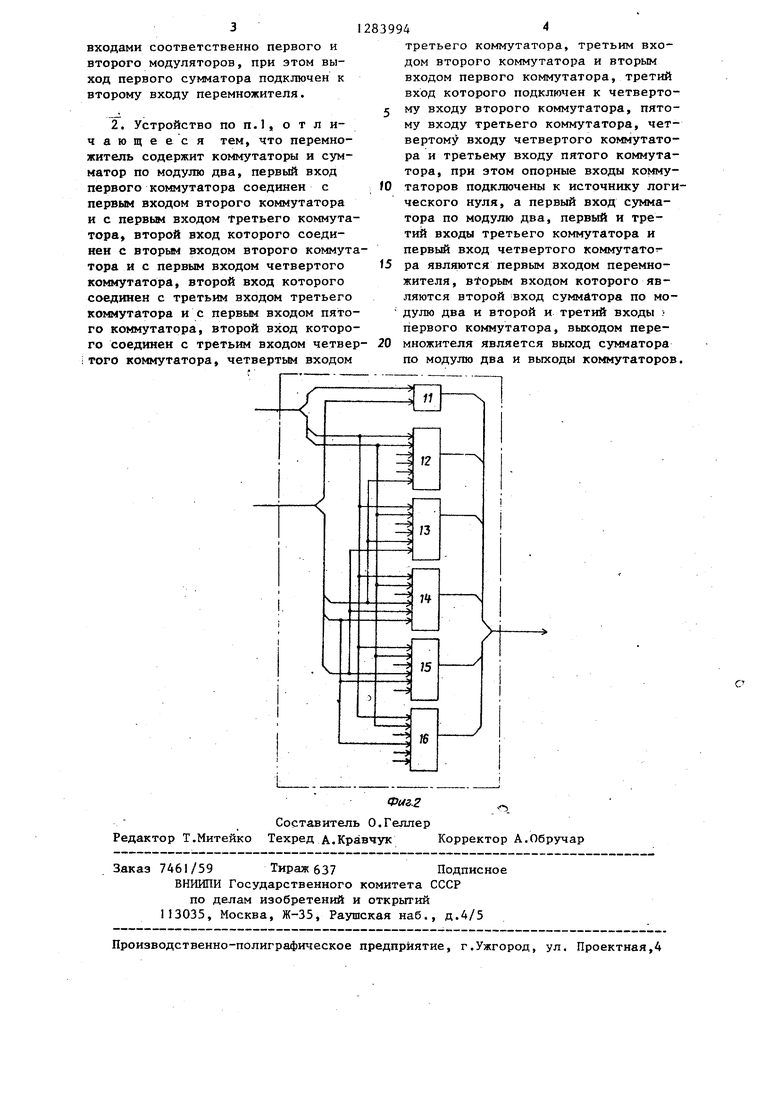

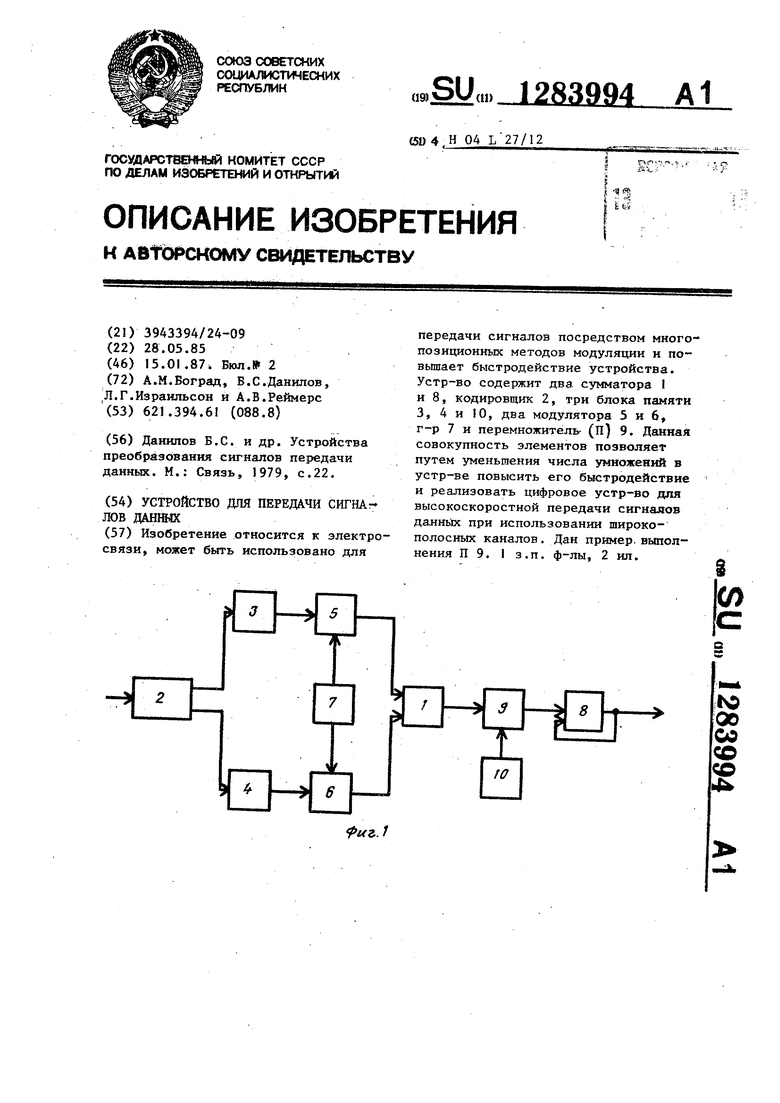

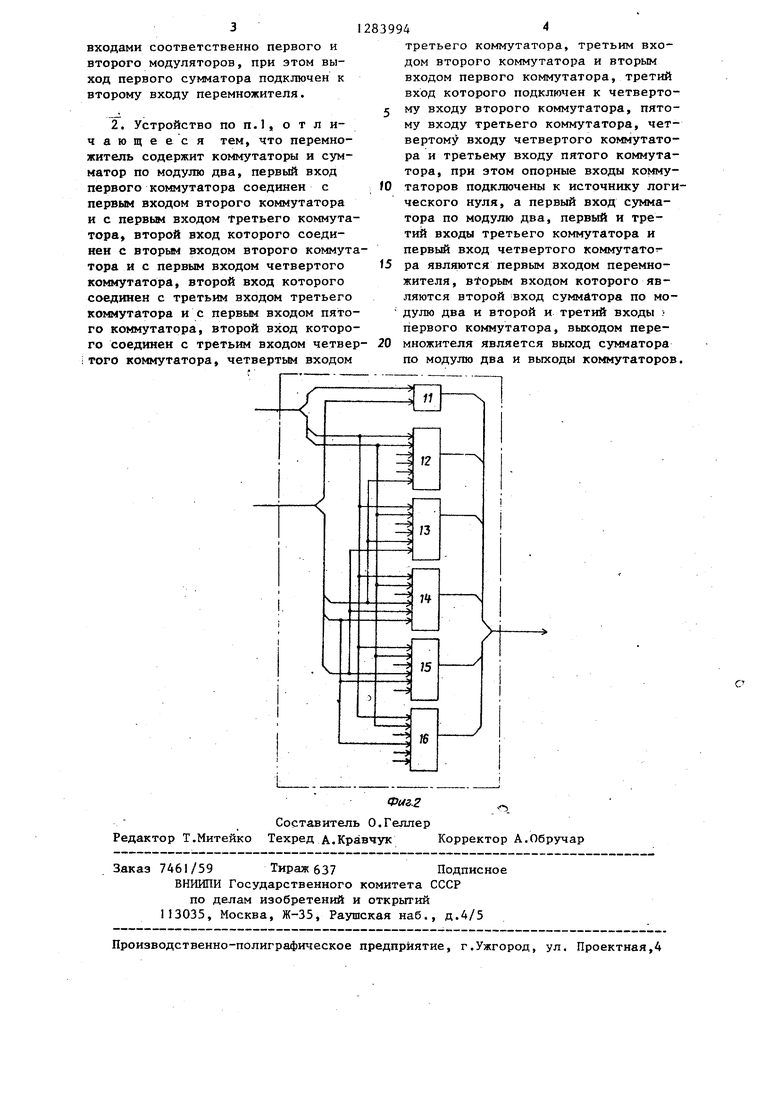

На фиг.1 изображена структурная электрическая схема предлагаемого устройства; на фиг.2 - структурная электрическая схема перемножителя.

Устройство для передачи сигналов данных содержит первый сумматор 1, кодировщик 2, первый и второй блоки 3 и 4 памяти, первый и второй модуляторы 5 и 6, генератор 7, второй сумматор 8, перемножитель 9 и третий блок 10 памяти.

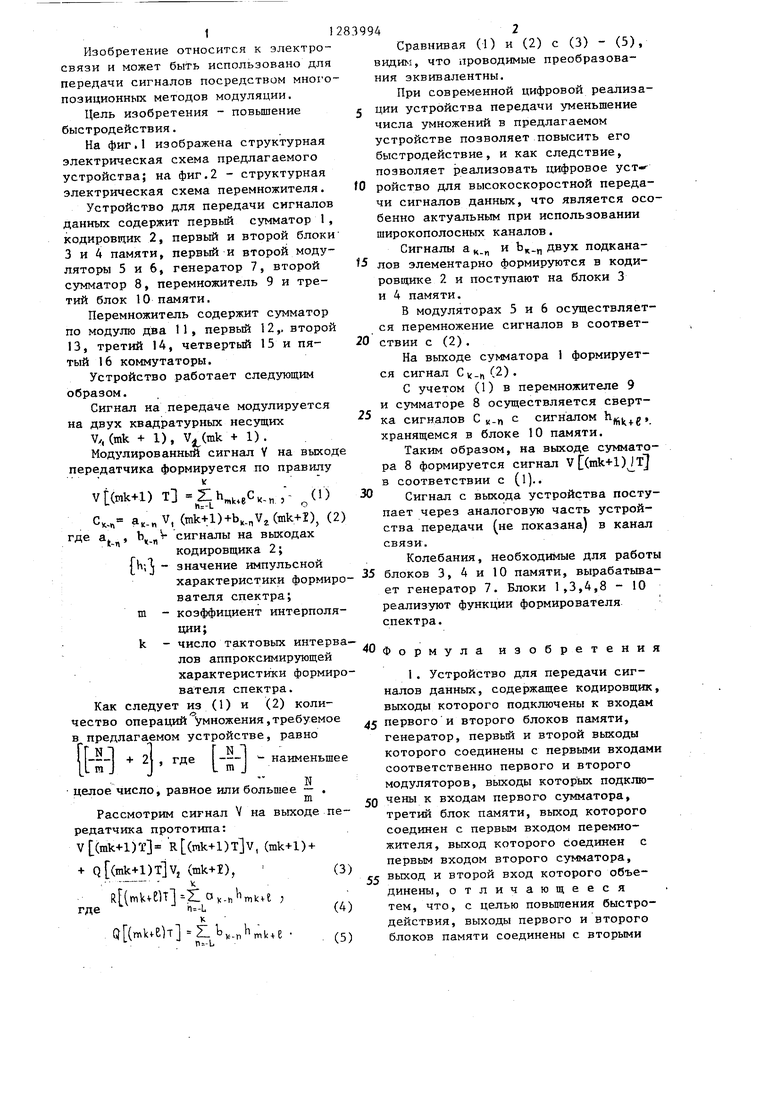

Перемножитель содержит сумматор по модулю два 1 1 , первый 12,. второй 13, третий 14, четвертый 15 и пятый 16 коммутаторы.

Устройство работает следующим образом.

Сигнал на передаче модулируется на двух квадратурных несущих

V/, (mk + 1), + 1) .

Модулированный сигнал Y на выходе

передатчика формируется по правилу с

vi(ink+l) т

С

где а, ,

Гь

, 3

(1)

к.-п а

t-na,,V, ()+b,.„VJmk+2), (2) Ч-Л

сигналы на выходах кодировщика 2; {Ь;Т - значение импульсной

характеристики формирователя спектра; m - коэффициент интерполяции;

k - число тактовых интервалов аппроксимирующей характеристики формирователя спектра, следует из (1) и (2) количество операций Умножения,требуемое в предлагаемом устройстве, равно

12839942

Сравнивая (1) и (2) с (3) - (5), видиь, что проводимые преобразования эквивалентны.

При современной цифровой реализа- 5 ции устройства передачи уменьшение числа умножений в предлагаемом устройстве позволяет повысить его быстродействие, и как следствие, позволяет реализовать цифровое уст- to ройство для высокоскоростной передачи сигналов данных, что является особенно актуальным при использовании широкополосных каналов.

Сигналы а и Ь. двух подкана- 5 лов элементарно формируются в кодировщике 2 и поступают на блоки 3 и 4 памяти.

В модуляторах 5 и 6 осуществляется перемножение сигналов в соответствии с (2) .

На выходе сумматора 1 формируется сигнал Cv-h(2).

С учетом (1) в перемножителе 9 и сумматоре 8 осуществляется свертка сигналов С . с сигналом Ь.п, хранящемся в блоке 10 памяти.

Таким образом, на выходе сумматора 8 формируется сигнал V (mk+l) )Т в соответствии с (l)..

Сигнал с выхода устройства поступает через аналоговую часть устройства передачи (не показана) в канал связи.

Колебания, необходимые для работы 35 блоков 3, 4 и 10 памяти, вырабатывает генератор 7. Блоки 1,3,4,8 - 10 реализуют функции формирователя спектра.

20

25

30

40 ф

ормула изобретения

Как

N 1 о1 Г N 1 ib-J - 2j , где ---J

наименьшее

N целое число, равное или большее - .

m

Рассмотрим сигнал V на выходе передатчика прототипа: V(mk+l)T R(mk+l), (mk+l) +

+ Q(mk-fl)TiVj (mk-t-I), (3)

R( Ox-hbmk.e ; где - n--L(4)

к

, (j(mk.6h z:t.i,,E.

Цг-Ь -J

1. Устройство для передачи сигналов данных, содержащее кодировщик, выходы которого подключены к входам

45 первого и второго блоков памяти, генератор, первый и второй выходы которого соединены с первыми входами соответственно первого и второго модуляторов, выходы которых подклю5Q чены к входам первого сумматора, третий блок памяти, выход которого соединен с первым входом перемножителя, выход которого соединен с первым входом второго сумматора,

выход и второй вход которого объединены, отличающееся тем, что, с целью повышения быстродействия, выходы первого и второго блоков памяти соединены с вторыми

40 ф

ормула изобретения

1. Устройство для передачи сигналов данных, содержащее кодировщик выходы которого подключены к входам

45 первого и второго блоков памяти, генератор, первый и второй выходы которого соединены с первыми входам соответственно первого и второго модуляторов, выходы которых подклю5Q чены к входам первого сумматора, третий блок памяти, выход которого соединен с первым входом перемножителя, выход которого соединен с первым входом второго сумматора,

выход и второй вход которого объединены, отличающееся тем, что, с целью повышения быстродействия, выходы первого и второго блоков памяти соединены с вторыми

входами соответственно первого и второго модуляторов, при этом выход первого сумматора подключен к второму входу перемножителя.

2. Устройство по п.1, о т л и- чающееся тем, что перемножитель содержит коммутаторы и сумматор по модулю два, первый вход первого коммутатора соединен с первым входом второго коммутатора и с первьм входом третьего коммутатора, второй вход которого соединен с вторым входом второго коммута тора и с первым входом четвертого коммутатора, второй вход которого соединен с третьим входом третьего коммутатора и с первым входом пятого коммутатора, второй вход которого соединен с третьим входом четвер I того коммутатора, четвертым входом

2839944

третьего коммутатора, третьим входом второго коммутатора и вторым входом первого коммутатора, третий вход которого подключен к четверто- 5 му входу второго коммутатора, пятому входу третьего коммутатора, четвертому входу четвертого коммутатора и третьему входу пятого коммутатора, при этом опорные входы комму- fO таторов подключены к источнику логического нуля, а первый вход сумматора по модулю два, первый и третий входы третьего коммутатора и первый вход четвертого коммутато f5 pa являются первым входом перемножителя, BtopbiM входом которого являются второй вход суммйтора по мо- дулю два и второй и третий входы : первого коммутатора, выходом пере- 20 множителя является выход сумматора по модулю два и выходы коммутаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Адаптивный корректор сигнала | 1978 |

|

SU794735A1 |

| Устройство адаптивной коррекции межсимвольных искажений | 1986 |

|

SU1332544A1 |

| МНОГОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2534938C1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах передачи данных | 1978 |

|

SU780209A1 |

| Устройство для приема дискретных сигналов | 1982 |

|

SU1030994A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

Изобретение относится к электросвязи, может быть использовано для передачи сигналов посредством много- позиционных методов модуляции и по- вьшает быстродействие устройства. Устр-во содержит два сумматора I и 8, кодировщик 2, три блока памяти 3, 4 и 10, два модулятора 5 и 6, г-р 7 и перемножитёль- (П) 9. Данная совокупность элементов позволяет путем уменьшения числа умножений в устр-ве повысить его быстродействие и реализовать цифровое устр-во для высокоскоростной передачи сигналов данньгх при использовании широкополосных каналов. Дан пример, выполнения П 9. 1 з.п. ф-лы, 2 кп. W с: го 00 со со tfZ.f

Фаг.2 Составитель О.Геллер Редактор Т.Митейко Техред А.Кравчук Корректор А.Обручар

Заказ 7461/59 Тираж 637Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

| Данилов B.C | |||

| и др | |||

| Устройства преобразования сигналов передачи данных | |||

| М.: Связь, 1979, с.22. |

Авторы

Даты

1987-01-15—Публикация

1985-05-28—Подача