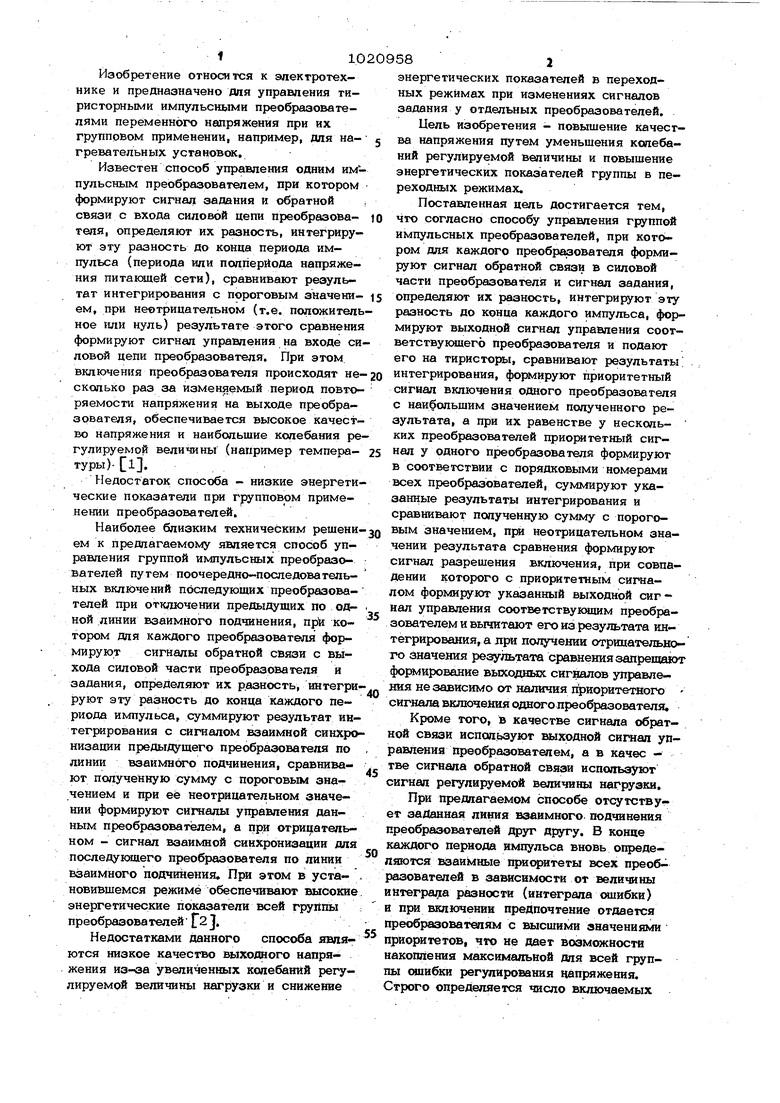

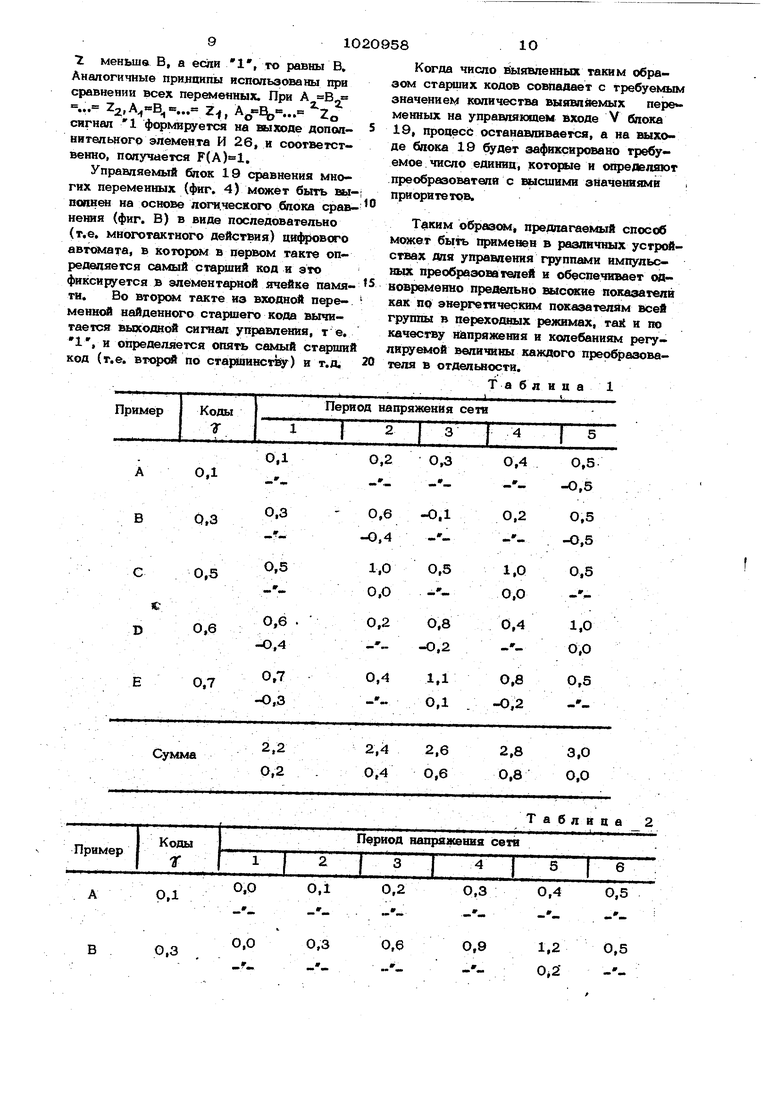

Изобретение относится к электротехнике и предназначено для управления ти ристорными импульсными преобразователями переменного напряжения при их групповом применении, например, для нагревательных установок. Известен способ управления одним импульсным преобразователем, при котором формируют сигнал задания и обратной связи с входа силовой цепи преобразователя, определяют их разность, интегрируют эту разность до конца периода импульса (периода или полперйода напряжения питакацей сети), сравнивают результат интегрирования с пороговым значением, при неотрицательном (т.е. положитель ное Щ1И нуль) результате этого сравнения формируют сигнал управления на входе си ловой цепи преобразователя. При этом включения преобразователя происходят не сколько раз за изменяемый период повторяемости напряжения на выходе преобразователя, обеспечивается высокое качество напряжения и наибольшие колебания ре гулируемой величины (например температуры)- 1.. Недостаток способа - низкие энергети ческие показатели при групповом применении преобразователей. Наиболее близким техническим решени ем к предлагаемок являете способ управления группой импульсных преобразователей путем поочередно-последовательных включений последующих преобразователей при отключении предыдущих по одной линии взаимного подчинения, пр котором для каждого преобразователя формируют сигналы обратной связи с выхода силовой части преобразователя и задания, определяют их разность, интегри руют эту разность до конца Каждого периода импульса, суммируют результат интегрирования с сигналом взаимной синхро низации предыдущего преобразователя по линии взаимнся о подчинения, сравнивают полученную сумму с пороговым значением и при её неотрицательном значении формируют сигналы управления данным преобразователем, а при отриц ательном - сигнал взаимной синхронизации для последукядего преобразователя по линии взаимного подчинения. При этом в установившемся режиме обеспечивают высокие энергетические показатели всей группы преобразователейL2 J. Недостатками данного способа являются низкое качество выходного напряжения из-за увеличенных колебаний регулируемой величинь нагрузки и снижение энергетических показателей в переходных режимах при изменениях сигналов задания у отдельных преобразователей. Цель изобретения - повышение качества напряжения путем уменьшения колебаний регулируемой величины и повышение энергетических показателей группы в переходных режимах. Поставленная цель достигается тем, что согласно способу управления группой импульсных преобразователей, при котором для каждого преобразователя формируют сигнал обратной связи в силовой части преобразователя и сигнал задания, определяют их разность, интегрируют эту разность до конца каждого импульса, формируют выходной сигнал управления соответствукниего преобразователя и подают его на тиристоры, сравнивают результаты . интегрирования, формируют приоритетный сигнал включения одного преобразователя с наибольшим значением полученного результата, а при их равенстве у нескольких преобразователей приоритетный сигнал у одного преобразователя формируют в соответствии с порядковыми номерами всех преобразователей, суммируют указанные результаты интегрирования и сравнивают полученную сумму с пороговым значением, при неотрицательном значении результата сравнения формируют сигнал разрешения включения, при совпадении которого с приоритетным сигналом форми1:уют указанный выходной сиг нал управления соответствукмцим преобразователем и вычитают его из результата интегрирования, а лри получении отрицательного значения результата сравнения запрещеаот формирование выходных сигналов управления не зависимо от наличия фиоритетного сигнала включения одного преобразователя. Кроме того, в качестве сигнала обратной связи используют выходной сигнал управления преобразователем, а в качес - тве сигнала обратной связи используют сигнал регулируемой величины нагрузки. При предлагаемом способе отсутствует заданная линия взаимного подчинения преобразователей друг другу. В конце каждого периода импульса вновь опредеnsQOTCH взаимные прио{ итеты всех преобразователей в зависимости от величины интеграла разности (интеграла ошибки) в при включении предпочтение отдается преобразоватшям с высшими значениями приоритетов, что не дает возможности накопления максимальной для всей группы синибки регулирования напряжения. Строго определяется число включаемых 6 следующий период преобразователей с высшими значениями приоритетов. Число это зависит от суммы сигналов задания для всей группы, которая определяет обшее среднее потребление энергии всеми преоб разователями и, поэтому чтределяе т чис, ло включаемых преобразователей с суммой мгновенных мощностей на уровне общего среднего потребления. На фиг. 1 1юказана схема устройства дяя осуществления одного из вариантов способа формулы; на фиг. 2 и 3 - диаграмма сигналов работы устройства по фиг. Ij на фиг. 4 - ojoeMa устройства Дня осуществления другого из вариантов способа} на-фиг. 5 - диаграммы сигналов работы устройства по фиг. 1| на фиг. 6 - схема логического устройства формирования приоритетного сигнала включения только одного преобразователя Устройство Для осуществления способа (фиг. 1,4) состоит из произвольного числа преобразователей j условно пронумерованных буквами латинского алфавита от А до Z Соответствующие буквы использованы для индексации одинаковых перемен ных в разшых преобразователях. Силовая часть каждого преобразоватояя состоит из встречно включенных вентилей 1 в цепи нагрузки 2, которые питаются от одной .и той же сети. Спеши управления (фиг. 1, 4) преобразователями различны но реал 1зуют один и тот же способ. Схема управления (фиг. 1) содержит в каждом преобразователе задающий блок 3; сивхрюнйзирсжанный сетью генератор тактовых импульсов, накапливакшщй сумматор 5 (выполняет функцию интегрирования в.ДЙ4ФОВОЙ форме) со статическими входамисуммирования и и 1читшия и соответствующими динамическими тактовыкда входами, формирователь 6 им ; пульсов с управлявшим в динамическим тактовыми входами и внутренней памятью с ее динамическим выходом, при этом вы ход задающего блока 3 щудключен к статичеокок у, в выход г гёратора 4 - к дв намическши1у тактовому входу сумматора входы вычитания сумматора объединены мехсду собой и динамическим вы ходом формирователя 6, статические выходы I которого подключены к управляющим печреходам вентилей. На всю группу преобразователей (фиг. 1) введены общий сумматор 7,сии :фонизироваш{ый сетью управляемый гене ратор 8 тактовых импульсов, логический блок 9 сравнения многих переменных с одинаковым количеством входов и выхо- дов, при этом каждый выход соответствующего (например, номер В латинского обозначения) накапливающего сумматора соответствующего преобразователя (т.е. В) объединен с соответствующим (т.е.В) входом общего румкштрра и с соответствующим (т.е. В) входом блока 9 сравнения, каждый соответствующий (обозначен F(B) на фиг. 1, 6) выход блока 9 соединен с соответствукшшм (т.е. В) входом формирователя 6, выходы старщих разрядов общего сумматора подключены к управляющим входам генератора 8, вы ход которого объединен с динамическими тактовыми входами всех формирователей 6. Схема управления (фиг. 4) содержит в каждом преобразователе функционально последовательно вкшоченные в прямом канале задающий бп(ж l6, первый суммируюший элемент 11, фильтр 12 низших частот, представляюптй собой интегратор, но в общем случае динамическое звено с передаточной функциейV/(P), второй суммирукяций элемент 13, релейный элемент 14 с формирователем, импульсов и управляемые вентили в цепи нагрузки;а в канале обратной связи (датчик 15 регулируемой величины, выход которого подключен к входу вычитания первого суммирующего элемента в Ьне каналов) тактируемый аналого-цифровой преобразователь.16, ифнормашюнный вход которого подключен к выходу фильтра низщих частот. На всю группу преобразователей (фиг.4) введены общий сумматор 17, синхронизированный сетью генератор 18 тактовых импульсов и управляемый блок 19 сравнеш1я многих переменных с одинаковым количеством информационных (обозначены буквой D на. фиг. 4) входов и, выходов, а также с управлякхцикш (обозначены буквой V на фиг 4) и тактовым входами, гфи этом каждый выход соответствующего (например, преобразователя В) аналогоцифрового преобразователя 16 объединен с соответствуюпшм (т.е. В) входом 19, соответствующий (т.е. В) выход которого соединен с входом соответствуквцего (т.е. В) второго суммирующего элемента преобразователя (т.е. В), выходы старщих разрядов общего сумматора , подключены к управляющим входам блока 19, тактовый вход блока 19 подключен ;к выходу генератора 18, другой выход которого объединен с тактовыми входами всех аналого-цифровых преобразователей 16. Схема логического Спока 9 сравнения Ы переменных, предстайленных М-разрядным двоичным кодом (фиг, 6, и код для переменной В имеет вид В-, В , BQ), состоит из фиксатора 20 равенства старших разрядов с М-1 выходами, выполненного на M-i элементах 21 сравнения с N входами и элементах И 22: К-1-ВХОДОВЫХ элементов ИЛИ-НЕ 23 не более чем трехвходбвых элементов И 24 и М-1-ВХОДОВЫХ вь1ходных элементов ИЛИ 25, из которых первый с выходом Р имеет дополнительный вход с дополнитель ным элементом И 26 в его цепи, а также элементов ИЛИ-НЕ с числом входов от 1 (инвертор) до Ы-1. Входы блока 9 соединены с входами элементов ИЛИ-НЕ и верхними входами трехвходовых элементов И (только для дополнительного элемента И вход включен через инвертор 28), выходы которых соединены с входами выходных элементов ИЛИ. К нилшим входам, трехвходовых элементов И подключены выходь элементов ИЛИ-НЕ, а к средним - выходы фик сатора 20. При реализации способа управления по пп. 1 и 2 формулы задакмдего блока 3 (фиг, 1) подаются сигналы задания в виде кодов , которые определяют тре буемое значение скважности импульсов тока нагрузки каждого преобразователя, Например, для группы из пяти преобрааоватейей (А, В ,,,, Е) в табл, 1 приведены произвольно взятые значения. Коды блока поступают на статические вхоры суммирования накапливакяшх сумк аторов 5, где складьгоаются по каждому импуль су генератора 4, это соответствует операций с ранее накопленной суммой, что соответствует операции интегрирования для аналоговых сигналов, Тактоиый им пульс поступает раз в период напряжения сети, номера этих периодов сети и значения накопленных сумм приведены в табл. 1. Процесс увеличения накопленной суммы можно графически интерпретировать прямой я1шией под углом 4 , . (фиг, 2 и а). В схеме (фиг. 1) применен -специальный блок 9, который формирует сигнал только на одном своем выходе, который соответствует вакото{я 1й подан код с наибольшим аначением накопленной суммы. Например, в конце первого периода работы согласно табо. 1 njMiоритетный сигнал первоначально формируется на выходе F блока 9, так как ве личина накопленной суммы 0,7 максимальна для всей группы. При равенстве накопленных сумм приоритет определяют в со ответствии с заранее субъективно принятой нумерацией преобразователей, в примере А, В, ..,, Е. В табл, 1 после суммирования в пятом периоде преобразователи располагаются в порядке старшинства так: Д, А, В, С, Е, а приоритетный сигнал первоначально формируется на выходе Рд блока 9, Меньше приоритет будет у преобразователя А, хотя накопленные суммы у оставшихся преобразователей равны. Сигнал на выходе обшего сумматора 7 (фиг, 1) определяет обшую сумму всех накопленных сумм (приведена внизу в табл, 1) и по ее значению определяют последовательно количество преобразователей, которые должны быть включены в следуюашй период. В примере (фиг. 1) используются только выходы старших целошсленных разрядов, наличие; KOTOpibJX говорят о том, что обшая сумма больше или равна единице или, что тоже самое, результат сравнения обшей суммы с единицей (пороговое значение для примера) положительный или нулевой, т.е. неотрицательный. При наливши на выходе обшего сумма тора 7 сигнала о неотрицательном результате сравнения генератор 8 формирует на своем выходе тактовые импульсы с частого&, гораздо большей сетевой. Эти импульсы поступают сразу на все шнамическне тактовые входы фо1я 1ирователя 6, но только в одном из них, на который с 9 поступает приоритетный сигнал , происходит переключение внутренней памяти. Одновременно с переключением на динамическом выходе этЫ1 внутренней памяти в атом формирователе 6 формируется импульс обратной связи, который поступает на входы вычитания своего накапливающего суьлматора 5 и уменьшает этим его сумму на , Это сразу же приводит к изменению обшей сумгла на заходе сумматора 7 а на выходе блока 9 сразу же появляется на крутом , который определяет новый старший код. Если сигнал неотрицательноста с выхода сумматора 7 созфаняется, то второй импульс с генфатора 8 повторяет опнсашше процессы до поаного исчезновения сигнала. В начале случайного периода фсфмироватевли 6, у которых переключена внутренняя память, фс жшруют выходные управляющие сигналы и вклочают управляемые вентили 1. Описанный поопехювательный процесс эквивалентен непссреД ственному определению числа включаемых в следующем периоде преобразователей как целого превышения первоначальной обшей с:уммы под нулем. Это число опреде|1яется кодсм старших пелочисленных раа рядов общего сумматора 7. В расолатриваемом примере после, первого периода по значению обшей суммы 2,2 должно быть включено два преобразователя, а после пятого - три (см. табл. 1), На фиг. 2 в .соответствии с табл. 1 построены даа«граммы Нумераций периодов напряжения сети (а), само напряжение (б), токи соотззетствуюших преобразователей (в, ...,ж) 1 4ическалс интерпретация накопленной суммы одного из них (з), общего тока группы (и). Величина выбранного псчрогового значения и начальные значё(Шя накопленных сумм не влняют на установйиии ся процесс работы группы: а переходный процесс 1быстро заканчивается, Так. в та€п.2 и на соответствующей 0й фиг 3 за пороговое значение принято 3, а начальные условия выбраны также . Как виА но пе реходный проиеёсгэаковчилсн за один перийд. При реализации способа управления по пп. 1 и 3 формулы в схеме (фиг. 4) с задающего блока Ю аналоговые сигналы, которые в относительных единицах также определяют скважность , На суммирукядем элементе 11 определяется разность с сигналом выхода датчика 15 регулируемой величины в результат (ш1ибка) поступает на ВХОД фильтра 12 низших частот (интегратора). аыход (интеграл) преклаает порог срабатывания релейного элемента 14 j поспе Еший включает управляемые вентили, когда стен жжится меньше нижнего пррся а - с1шмает управлякшве импульсы. С выяоДа фильтров 12 сигнал поступа:ет иа ййф фмапиойные вхолы преобразо BaTeita 16, которые концом каждо го периода ншфяженйя сети по такто -rt-вому импульсу с генератора 18 преобрй-iayipT в дафрсивой кой и фв1ксируют ава:чения интегралов ца выходах интеграте ов 12. В дальнейшем схема (фиг. S) работает схеме (фиг. 1) сошасно способу, С выходов преобразователя 16 сигналы поступают на входы сумматора 17, старшие разряды выходы которого определяют целое превышение суммы над кулем или число включаемых в следующий период преобразователей.. 1О2

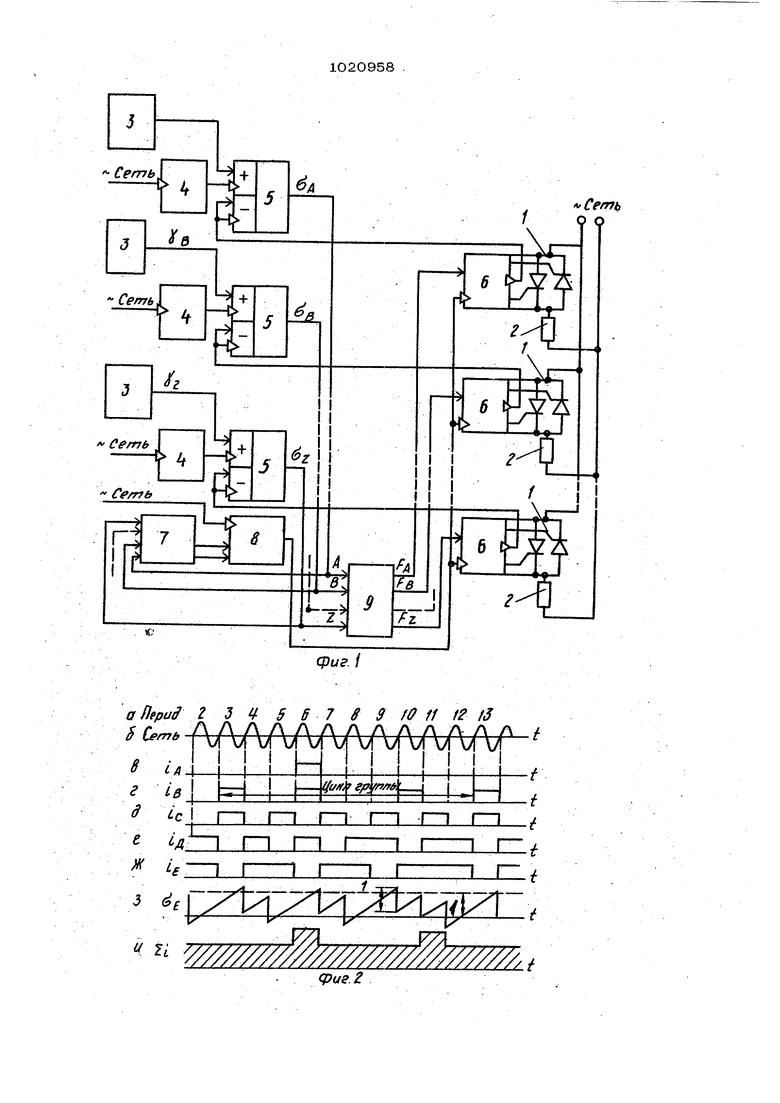

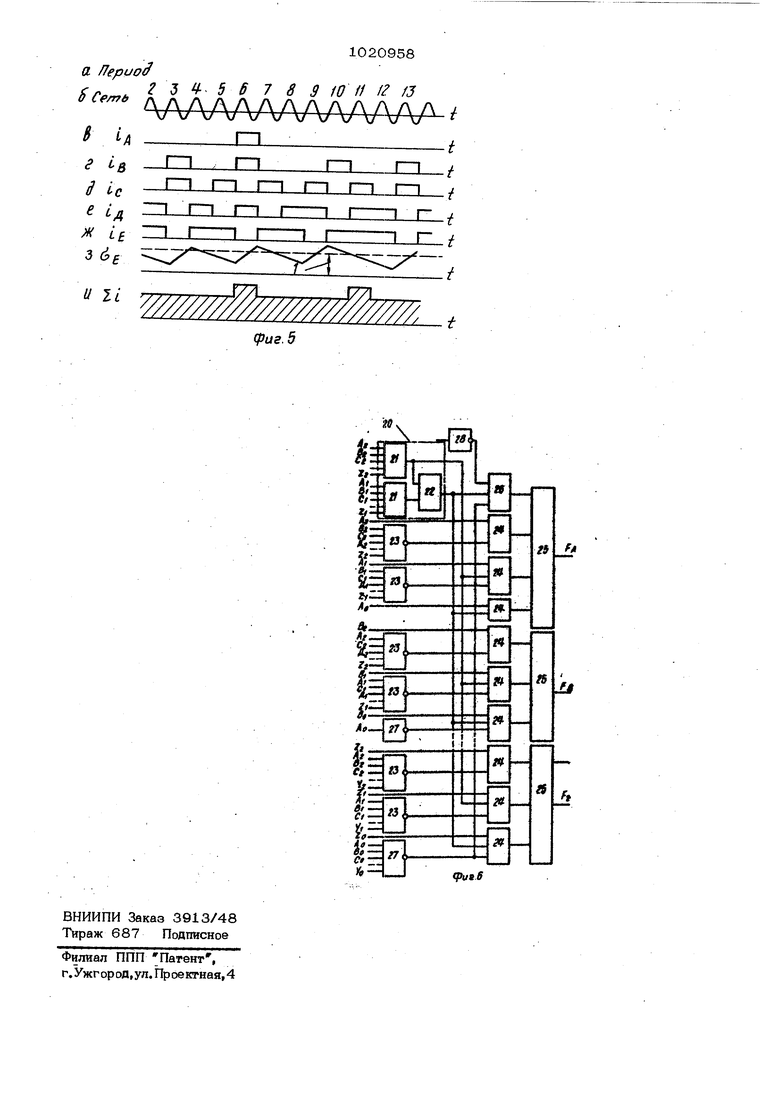

чих переменных, т.е. CJJ,I) Т. имеют значения, так как если они (или один из них) равны О, то коды. С, D ... 88/ )При мтеты преобразователей определяются также по значениям интегралов на выходах 4 1льтров 12, т.е. на выходах преобразователя 16. В табл.3 приведены значения соответствующих интегралов и суммы по периодамсети, а буквой В показана фиксация команды на включение в спе10гюший период. На фиг. 5 показаны соответствующие табл. 3 диагргммы. В схеме (фиг. 4) введен у1фа1В1шемыЙ &IOK 19 сравнения, который фо ширует сигналы на выходах по чвсду, отфедёляемому управлякицим кодом (ва входе V ), Е распределяет их в ссфтветспжи с приоритетом в соответствии с на.информационных входах (входах t)). Нахфимер, соглеюно табл. 3 в ковпё первого периода формируются сигналы на выходах 1} и Е. Дакиые сигналы переключают соответствующие релейные элементы 14, благодаря гистерезису остауотся . переключенными и в начале спедукяпего тюриода включают управляемые вентяли 1. Из фавненяя диаграмм (фиг. 1 и 5) ввАно, что характер работы группы хфв резных системах, но одном способе копуча ется подо&ым, хотя диаграммы нак И1ленных сумм (интегралов, фиг. 1е и фиг. 4) различны.. Логический блок сравне Егая многих переменных (. 6) формирует на своем выходе, например F(B)i сигнай 1, если либо код В (В2, В, BQ) бопыйой из А, В, С, ..., Z , либо больше А (с б ёктишю пронятый приоритет порядковой цумераЕЕии которого старше) и бопыие или равен С, Тй , ..., 2 (приоритет хоторвых младше). Код В может быть самым большим, когда i, А С Л,, ,.. 2j, тсмпда фцрмирогются сигналы 1 на выходе верхнего апемента 2 в канале сраввеЬвя кода В, на вызсоде верхнего алеМента И 24, н выходе Р (В) соответствевно ЕЛИ к«мгда . , , .«.2,, О, тогда аналсягвчао форкгаруieipa сигнал I на средних элементах, причем Rd вход среднего элемента И 24 . подается также сигнал с фиксатора 2О о равенстве ста|иаих разрядов. Наконец, сравнение только младших ко дов, когда прочие равны, ва выходе ниж-с него элемента И 24 формируется сигнал 1, яогда равны прбчие коды, сигнал с фиксатора 20 , , значения про1 меньше В, а если , то равны В. Аналогичные принципы использованы при сравнении всех переменных. При А В ... Z2,... Z, ... 2о сигнал 1 форми цгется на выходе дополнительного элемента И 26, и соответственно, получается F(A)1.

Управляемый блок 19 сравнения мно гих переменных (фнг. 4) может быть выпопнен на основе логи.ческого блока сравнения (фиг. В) в виде последовательно (т.е. многотактного действия) авт Яъ4ата, в котором в первом такте определяется самый старший код и это фиксируется в элементарной ячейке памяти. Во Тагором такте из входной пере менн найденного старшего кода вычитается выходной сигнал управления, те. 1, и определяется опять самый код (т.е. по CTajHimHcr) и т.д,

Когда число Е ыявленных таким образом ставших кодов совпадает с требуемым значением количества выявляемых пере менных на управляющем входе V блока 19, процесс останавливается, а на выходе блока 19 будет звфихсир ано требуемое число единиц, которые и шределяют преобразователи с высшими значениями приоритетов.

Таким образсш, предлагаемый способ может быть применен в различных устройствах для управления группами импульсHbiX преобразователей и обеспечивает одновременно предельно высокие покада1телй как по энергетическим показателям Всей группы в переходных режимах, Tait и по качеству напряжения и колебаниям регули1: емой величины каждого преобразователя в отдельности.

Т а б л и и а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ ПРЕОБРАЗОВАТЕЛЕЙ | 1983 |

|

SU1284443A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Цифровой фильтр | 1984 |

|

SU1205152A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Устройство для сортировки деталей на группы | 1987 |

|

SU1469507A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

1. СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ ПРЕОБРАЗОВАТЕЛЕЙ, заключающийся в том, что дпя каждого преобразователя форми гют сигнал обратной связи -в силовой части . преобразователя и сигнал задания, опре- дел яют их разность, интегрируют эту разность до конод каждого импульса, формирукА выходной сжгнал управления соогветсгоукяцего пр бразователя и подают его на тиристоры, отличающийся тем, что, с целью цовышения качест-. ва шдходного напряжения путем уменьшен; НИН Колебаний регулируемой величины и повышения энергетических показателей группы в переходных режимах, сравнивают результаты интe pиppвaния, формируют приоритетный сигнал включения одно- . го преобразователя с наибольшим значением полученного результата, а цри их равенстве у нескольких преобразователей приоритетный сигнал у одного преобразователя формируют в соответствии с порядковыми номерами всех преобразователей, суммируют указанные результаты интегри;рювания и сравнивают полученную сумк с пороговым значением, при неотрицательном значении результата сравнения формиЙют сигналразрешения включения, при совпадении которого с приоритетным сигналом формируют указанный выходной сигнал управления соответствующим преобразователем и вычитают его из результата внтегр ров яния, а при получении отрицательного значения результата сравнения W запрюшают формирование выходных сигналов управления всех преобр азователей независимо от наличия приоритетного сигнала ввэиочения одного преобразователя. 2,Способ по п. 1, о т л и ч а ю Ш и и с я тем, что в качестве сигнала обратной связи используют выходной сиг нал управлитя преобразователем. 3,Способ по п. 1, о т л и ч а ю - щ и и с я тем, что в качестве сигнйиа 1C о6ратн й связи используют сигнал регуо лируемой величины нагрузки. СП 00

0,3

0,0

0,3

f

Таблица

0,5

1,2

0,9 0,211

0,5

0,0

0,5

т -.0,6

0.0

0,6

0,0О,7

0,7

2,2

О,О

Сумма

2,4 V

O.i0,20,3О.4

Oil

0,3

0,3 0,5

0,5

0,6

0.6 В

0.7

0.7 В 2,22,42,62,83,О

. Сумма

12

1020958

Гфодолженае табл. 2

1,0

|Г . 0,5, 0.5

1,0

0,8

1,2

1|4 0,4 0,0 .2

О,8

1,1

1,4 - 0,5 0,1 ,4

5,0

4,8

4,6 2.0 2,8

Таблица, 3

0,5 В

0,5

-0,10.2 В

0,5

0,5 В

0.2

0,4

О.8 В

В 0.4

0.8

1,1

О,5 В В

фиг. I

г I $ ff 7 ff /ffff f/ 13

I I

(Uffif «

j mm r-i r-n r-i - r- n r

-

I tL

L

y////////////////////////Mm.,

cpus.Z

Д-/

-t

« I

т i i:

I -i i

ilRT .

r kk If. f. r. J. °

iA г IB

.

f-c

e LA ie

3 4 и li

mm///////////.

.1D2O958

ЛУ V/ V, ХУ, vj V/

I Mig 1

H I H

ri

1 r1 rn I -f

I I

41с/

-t

y.

(.3

4

и Период

с 2 Ъ 5 6 7 8 9 10 fi // /J

/ХЛЛЛЛЛЛЛЛЛЛЛ/

LAгп

I-II-II- -I

///// 7////////////.

(риг. 5

1020958

У.

/К:

ft

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ УПРАВЛЕНИЯ ШИРОТНО-ИМПУЛЬСПЬШ РЕГУЛЯТОРОМ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1969 |

|

SU425173A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-05-30—Публикация

1981-07-29—Подача