СЛ

Фи.1

Изобретение относится к вычислительной технике и может использоваться для построения многомашинных вычислительных систем.

Цель изобретения - повьппание производительности устройства за счет создания на передающей стороне очереди пакетов с возможностью передачи пакета по межмашинной магистрали с одновременным приемом в блок буферно памяти следующего пакета,

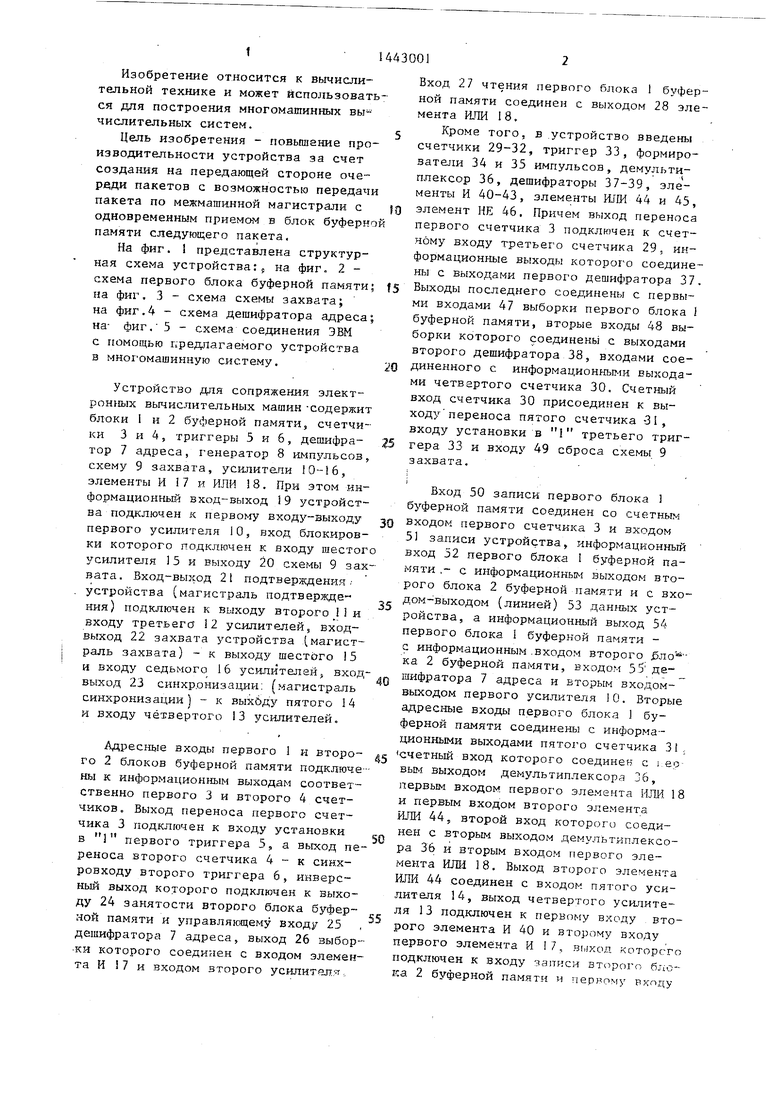

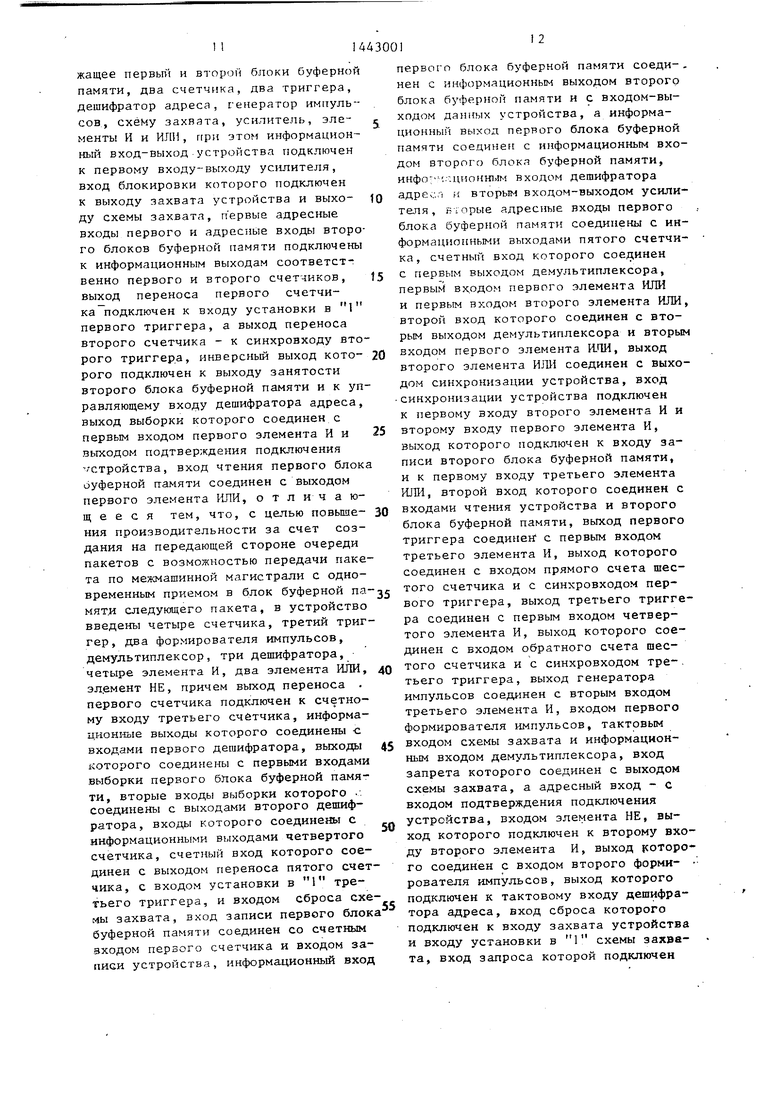

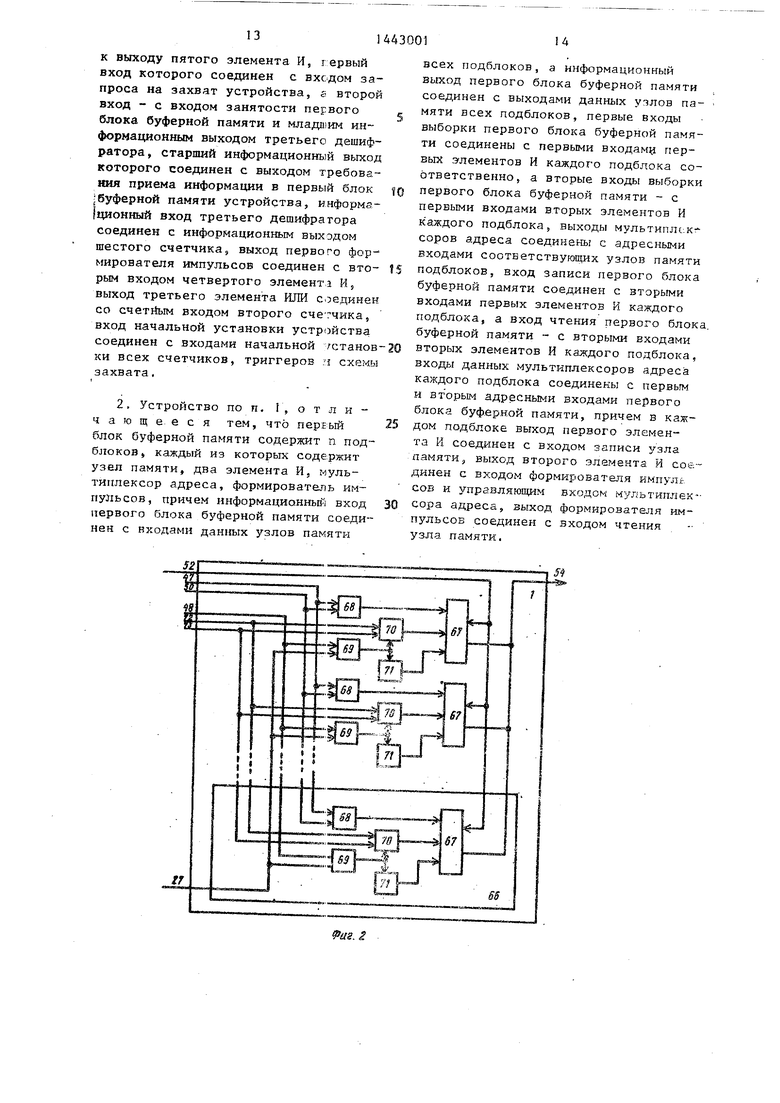

На фиг. 1 представлена структурная схема устройства:, на фиг. 2 - схема первого блока буферной памяти; на фиг. 3 - схема схемы захвата; на фиг.4 - схема дешифратора адреса; на- фиг, 5 - схема соединения ЭВМ с помощью предлагаемого устройства в многомашинную систему.

Устройство для сопряжения электронных вычислительных машин -содержит блоки I и 2 буферной памяти, счетчики 3 и 4, триггеры 5 и 6, дешифра- тор 7 адреса, генератор 8 импульсов, схему 9 захвата, усилитепи 10-16, элементы И 7 и ИЛИ 18. При этом ин- формационньш вход-выход 9 устройства подключен к первому входу-выходу первого усилителя 10, вход блокировки которого подключен к входу шестог усилителя 15 и выходу 20 схемы 9 захвата. Вход-выход 21 подтверждения; устройства (магистраль подтвержде- ния) подключен к выходу второго 1 1 и входу третьегсг 12 усилителей, вход- выход 22 захвата устройства (магистраль захвата) - к выходу шестого 15 и входу седьмого 16 усилителей, вход выход 23 синхронизации: (магистраль синхронизации - к выхбду пятого 14 и входу четвертого 13 усилителей.

Адресные входы первого 1 и второ- го 2 блоков буферной памяти подключены к информационным выходам соответственно первого 3 и второго 4 счетчиков. Выход переноса первого счетчика 3 подключен к входу установки

в 1 первого триггера 5, а выход переноса второго счетчика 4 - к синх- ровходу второго триггера 6, инверс- ный выход которого подключен к выходу 24 занятости второго блока буферной памяти и управляющему входу 25 дешифратора 7 адреса, выход 26 выбор- ки которого соединен с входом элемента И I 7 и входом второго усилителя,,

0

0

с

0

5

Вход 27 чтения первого блока 1 буферной памяти соединен с выходом 28 элемента ИЛИ 18.

Кроме того, в .устройство введены счетчики 29-32, триггер 33, формирователи 34 и 35 импульсов, демульти- плексор 36, дешифраторы 37-39, элементы И 40-43, элементы ИЛИ 44 и 45, элемент НЕ 46, Причем выход переноса первого счетчика 3 подключен к счетному входу третьего счетчика 29, информационные выходы которог о соединены с выходами первого дешифратора 37. Выходы последнего соединены с первыми входами 47 выборки первого блока буферной памяти, вторые входы 48 выборки которого соединены с выходами второго дешифратора 38, входами соединенного с информационными выходами четвертого счетчика 30, Счетный вход счетчика 30 присоединен к выходу переноса пятого счетчика -31, входу установки в 1 третьего триггера 33 и входу 49 сброса схемы 9 захвата.

f

Вход 50 записи первого блока

буферной памяти соединен со счетным входом первого счетчика 3 и входом 51 записи устройства, информационный вход 52 первого блока I буферной памяти ,- с информационньп выходом второго блока 2 буферной памяти и с входом-выходом (линией) 53 данных устройства, а информационный выход 54 первого блока 1 буферной памяти - с информационным .входом второго ло ка 2 буферной памяти, входо.м 55 дешифратора 7 адреса и вторым входом- выходом первого усилителя 1 О, Вторые адресные входы первого блока 1 буферной памяти соединены с информационными выходами пято1 о счетчика 31, счетный вход которого соединев с i ео вым выходом демультиплексора 36, первым входом первого элемента ИЛИ 18 и первым входом второго элемента ИЛИ 44, второй вход которого соединен с вторым выходом демультиплексора 36 и вторым входом первого элемента ШШ. 18. Выход второго элемента Ш1И 44 соединен с входом пятого усилителя 14, выход четвертого усилителя 13 подключен к первому входу второго элемента И 40 и второму входу первого элемента И 17, выход .которсго подключен к входу за)тиси второго блока 2 буферной памяти и первому вх-пду

третьего элемента ЯПИ 45, второй вхо которого подсоединен к входу 56 чтения устройства и входу чтения второг блока 2 буферной памяти.

Выход первого триггера 5 соединен с входом третьего элемента Н 41, выход которого соединен с входом прямого счета шестого счетчика 32 и синх- ровходом первого триггера 5. Выход третьего триггера 33 соединен с первым входом четвертого элемента И 42, выход которого со единен с входом обратного счета шестого счетчика 32 к с синхрозходом третьего триггера 33. Выход генератора 8 импульсов соединен с вторым входом третьего элемента И 4, входом первого формировател 34 импульсов, тактовым входом 57 схемы 9 захвата и информационным входом демультиплексора 36, вход запрета которого соединен с выходом 20 схемы 9 захвата, а адресный вход - с выходом третьего усилителя 12 и входом элемента НЕ 46, выход которого под- ключей к второму входу второго элемента И 40. Выход последнего присоединен к входу формирователя 35 им- nyjIbCOB, подключенного выходом к тактовому входу 58 дешифратора 7 адреса вход 59 сброса которого подключен к выходу седьмого усилителя 16 и входу 60 установки схемы 9 захвата, вход 61 запроса которой подключен к вьпсоду пятого элемента И 43. Первый вход элемента И 43 соединен с входом 62 запроса устройства на захват, а . второй вход - с выходом 63 занятости первого блока 1 буферной памяти и младшим информационным выходом тре- тьего дешифратора 39, старший информационный выход которого соединен с выходом 64 требования приема информации в. первый блок 1 буферной памяти устройства. Информационные входы третьего дешифратора 39 соединены с информационными выходами шестого счетчика 32, выход первого формирователя 34 импульсов - с вторым входом четвертого элемента И 42, выход третьего элемента ИЛИ 45 - со счет ным входом второго счетчика 4, вход 65 начальной установки устройства - с входами нача 1ьной установки всех счетчиков, триггеров и схемы 9 захвата.

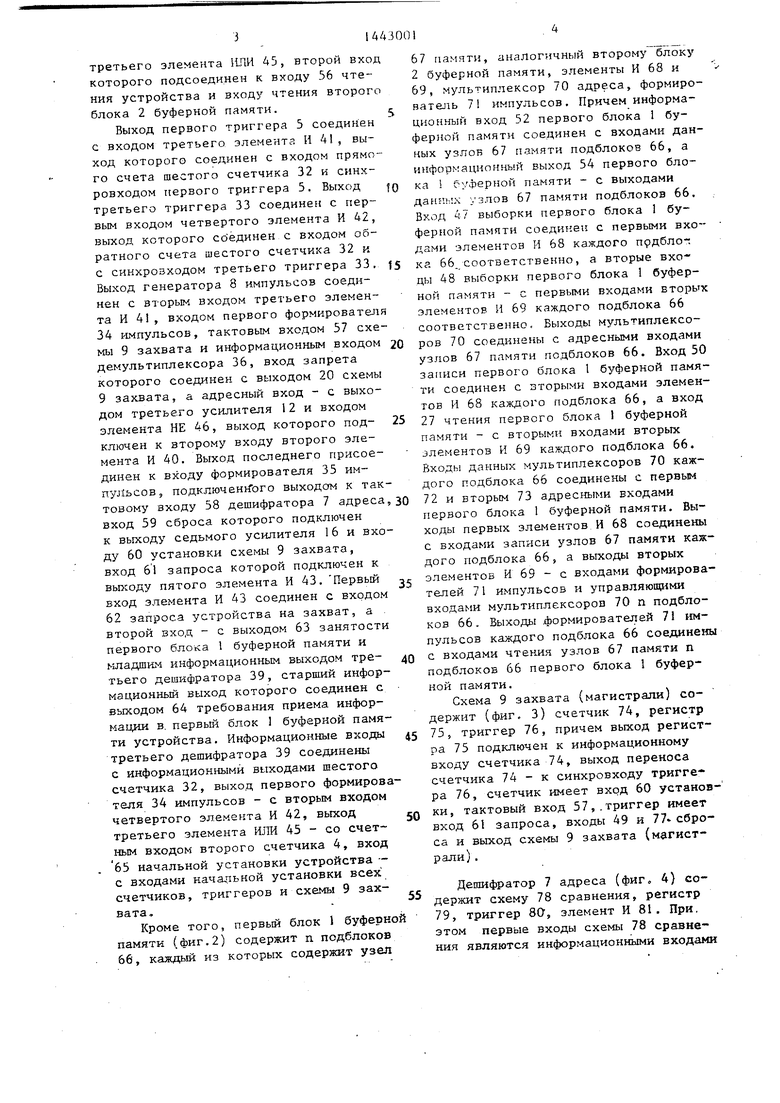

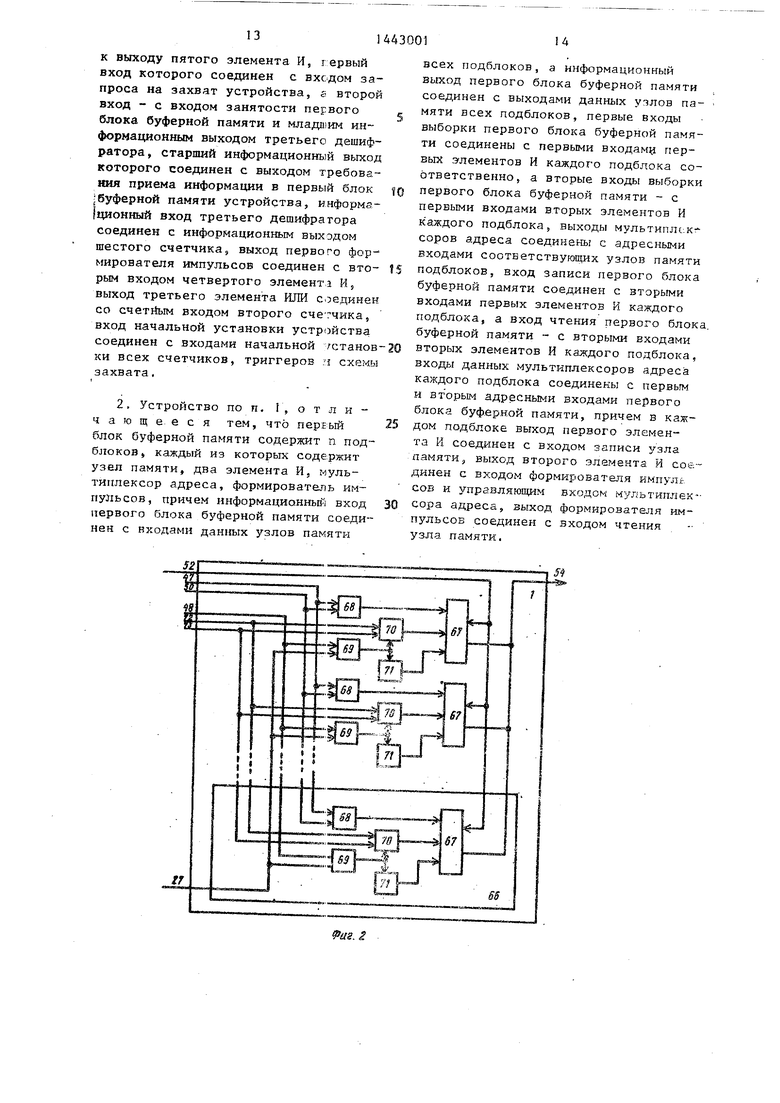

Кроме того, первый блок 1 буферно памяти (фиг.2) содержит п. подблоков 66, каждый из которых содержит узел

.

Q 5 0 5 О г Q 5 п

5

67 памяти, аналогичный второму блоку 2 буферной памяти, элементы И 68 и 69, мультиплексор 70 адре-са, формирователь 71 импульсов. Причем информационный вход 52 первого блока 1 буферной памяти соединен с входами данных узлов 67 памяти подблоков 66, а И11формационнь й выход 54 первого блока i буферной памяти - с выходами даняь. х узлов 67 памяти подблоков 66. Вход 47 выборки первого блока 1 буферной памяти соединен с первыми входами элементов И 68 каждого прдбло-. ка 66. соответственно, а вторые входы 48 выборки первого блока 1 буферной памяти - с первыми входами вторых элементов И 69 каждого подблока 66 соответственно. Выходы мультиплексоров 70 соединены с адресными входами узлов 67 памяти подблоков 66. Вход 50 записи первого блока 1 буферной памяти соединен с вторыми входами элементов И 68 каждого подблока 66, а вход 27 чтения первого блока 1 буферной памяти - с вторыми входами вторых элементов И 69 каждого подблока 66. Входы данных мультиплексоров 70 каждого подблока 66 соединены с первым 72 и вторьЕм 73 адресными входами первого блока 1 буферной памяти. Выходы первых элементов И 68 соединены с входами : 1апнси узлов 67 памяти каждого подблока 66, а выходы вторых элементов И 69 - с входами формирователей 71 импульсов и управляющими входами мультиплексоров 70 п подблоков 66. Выходы формирователей 7 i импульсов каждого подблока 66 соединены с входами чтения узлов 67 памяти п подблоков 66 первого блока I буферной памяти.

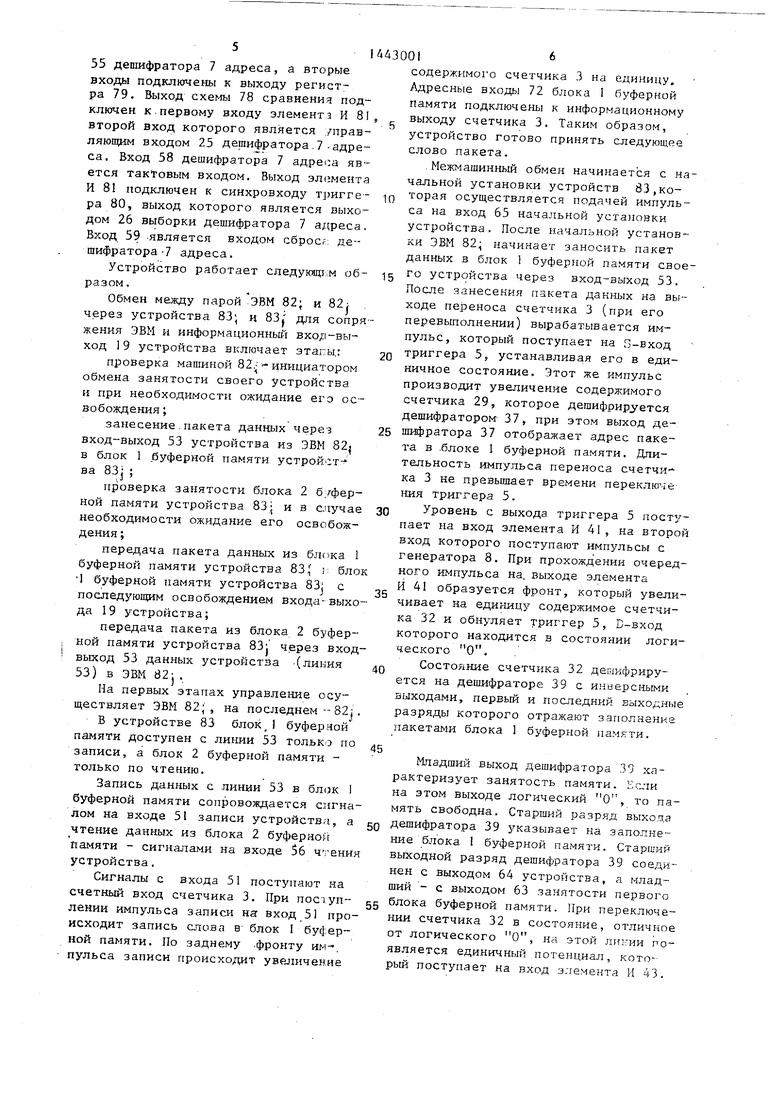

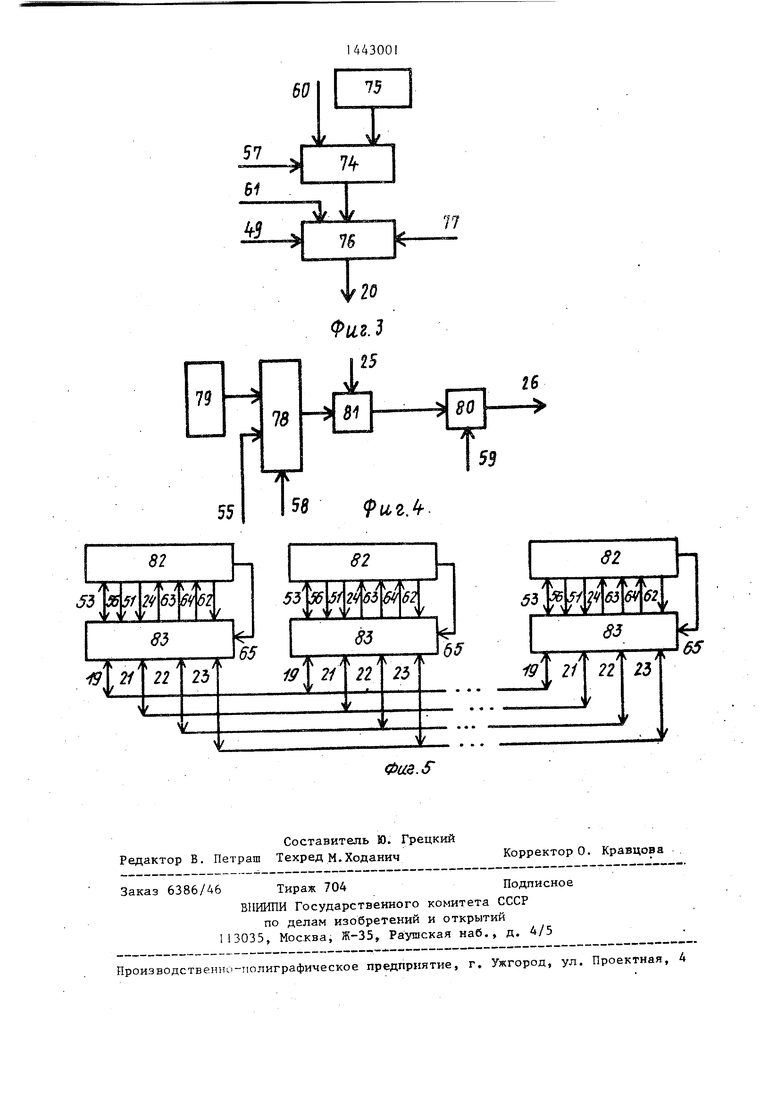

Схема 9 захвата (магистрали) содержит (фиг, 3) счетчик 74, регистр 75, триггер 76, причем выход регистра 75 подключен к информационному входу счетчика 74, выход перекоса счетчика 74 - к синхровходу триггв ра 76, счетчик имеет вход 60 установ- ки, тактовый вход 57,.триггер имеет вход 61 запроса, входы 49 и 77 сброса и выход схемы 9 захвата (магистрали) .

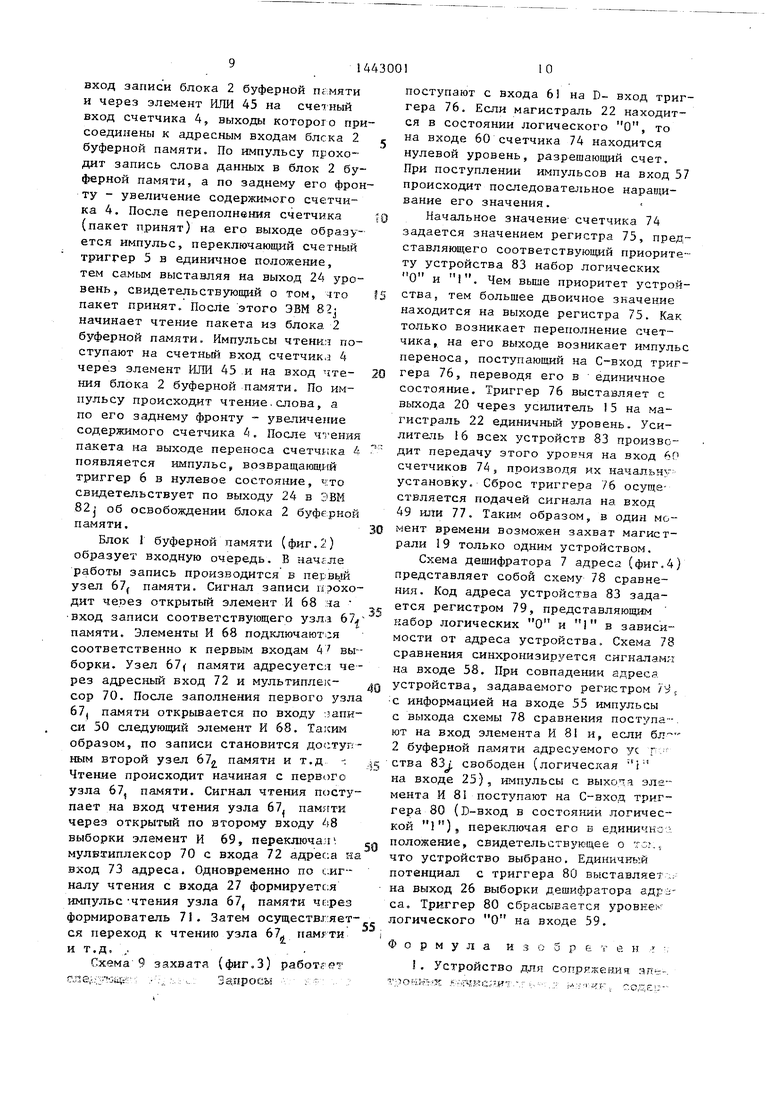

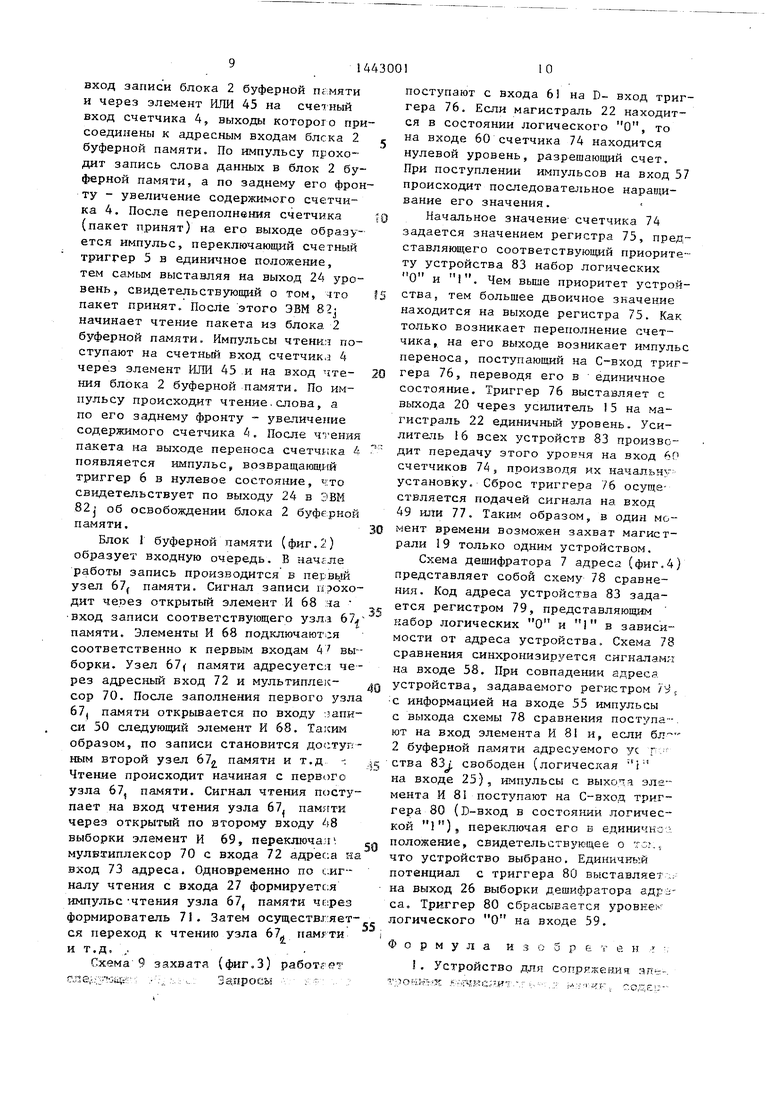

Дешифратор 7 адреса (фиг. 4) содержит схему 78 сравнения, регистр 79, триггер 80, элемент И 81. При. этом первые входы схемы 78 сравнения являются информационными входами

55 дешифратора 7 адреса, а вторые входы подключены к выходу регистра 79. Выход схемы 78 сравнения подключен к.первому входу элементз И 81 второй вход которого является управляющим входом 25 дешифратора.7-адреса. Вход 58 дешифратора 7 адреса яв- ется тактовым входом. Выход эл(мента И 81 подключен к синхровходу триггера 80, выход которого является выходом 26 выборки дешифратора 7 адреса. Вход 59 -является входом сбросг-; дешифратора 7 адреса,

Устройство работает следумцз:;м образом .

Обмен между парой ЭВМ 82; и 82; . через устройства 83; и для сопряжения ЭВМ и информационный BXO;I-выход 19 устройства включает этапы,:

проверка машиной SZ/ инициатором обмена занятости своего устройства и при необходимости ожидание его освобождения;

занесение.пакета данных через вход-выход 53 устройства из ЭВМ 82 в блок 1 .буферной памяти устройст- ва 83; ;

проверка занятости блока 2 буферной памяти устройства 83; ив случае

освобож

необходимости ожидание его дения;

передача пакета данных из блока 1 буферной памяти устройства 83, j: бло 1 буферной памяти устройства 83j с последующим освобождением входа-выхода 19 устройства;

передача пакета из блока 2 буферной памяти устройства 83; через вход выход 53 данных устройства -(линия 53) в ЭВМ 82j.

На первых этапах управление осуществляет ЭВМ 82;, на последнем--82;

В устройстве 83 блок, буферной памяти доступен с линии 53 только по записи, а блок 2 буферной памяти - только по чтению.

Запись данных с -пинии 53 в блак I буферной памяти сопровождается сигналом на входе 51 записи устройства, а чтение данных из блока 2 буферноГг памяти - сигналами на входе 56 Ч ; ени устройства.

Сигналы с входа 51 поступают на счетный вход счетчика 3. При nociyn- Ленин импульса записи на вход 51 происходит запись слова в- блок I буферной памяти. По заднему .фронту им-, пульса записи происходит увеличение

5

10

15

,

ЗО

20

к -

.

43001

содержимого счетчика 3 на единицу. Адресные входы 72 блока I буферной памяти подключены к информационному выходу счетчика 3. Таким образом, устройство готово принять следующее слово пакета.

.Межмашинный обмен начинается с начальной установки устройств 83,которая осуществляется подачей импульса на вход 65 начальной уста)ювки устройства. После начальной установки ЭВМ 82; начинает заносить пакет данных в блок 1 буферной памяти своего устрсзйства через вход-выход 53. После занесения пакета данных на выходе nejDenoca счетчика 3 (при его перевыполнении) вырабатывается импульс, который поступает на G-вход триггера 5, устанавливая его в единичное состояние. Этот же импульс производит увеличение содержимого счетчика 29, которое дешифрируется дешифратором- 37, при этом выход дешифратора 37 отображает адрес пакета в -блоке 1 буферной памяти. Длительность импульса переноса счетчи-- ка 3 не превышает времени переключе ния триггера 5.

Уровень с выхода триггера 5 постз - пает на вход элемента И 41, на второй вход которого поступают импульсы с генератора 8. При прохождении очередного импульса на. выходе элемента И 4 образуется фронт, который увеличивает на единицу содержимое счетчика 32 и обнуляет триггер 5, Б-вход которого находится в состоянии логического О.

Состояние счетчика 32 деиифриру- ется на дешифраторе 39 с инверсными выходами, первый и последний выходные разряды которого отражают заполнение пакетами блока 1 буферной памяти.

25

35

40

Младший выход дешифратора 39 характеризует занятость памяти. Если на этом выходе логический О, то память свободна. Старший разряд выхода

дешифратора 39 указывает на заполнение блока буферной памяти. Старший выходной разряд дешифратора 39 соединен с выходом 64 устройства, а младший - с выходом 63 занятости первого

блока буферной памяти. При переключении счетчика 32 в состояние, отличное от логического О, на этой лгпгии появляется единичный потенциал, который поступает на вход элемента И 43,

Таким образом, прием пакетов в блок 1 буферной памяти возможен до появления уровня логического О на выходе 64.При наличии уровня разрешения захвата на входе 62 на входе 61 схемы захвата образуется сигнал, разрешающий устройству 83jпроизвести захват.

После разрешения всевозможных конфликтов по захвату входа-выхода (ма- гистраль) 19 устройства от различньь. устройств 83 и предоставления входа- выхода 19 устройству 83; на выходе 20 схемы 9 захвата вырабатывается уровень, который переключает усили- тель 10 на передачу и через усили- тель 15 выставляется на вход-выход 22 захвата, сигнал с выхода 20 схемы 9 захвата поступает на вход запрета де- мультиплексора 36, разрешая прохождение синхроимпульсов с генератора 8 на входы элементов ИЛИ 18 и 4. Синхроимпульсы с выхода 28 элемента ИЛИ 18 поступают на вход 27 чтения блока I буферной памяти, а с выхода элемента ИЛИ 44 через усилитель 14 - на вход-выход (магистраль) 23 синхронизации устройства.

Синхроимпульсы, поступая на вход 27 чтения блока 1 буферной памяти, инициируют чтение первого слова пакета, определяемого содержимым счетчика 30, на магистраль 19. В первом слове пакета должна содержаться информация об адресуемом устройстве 83-.. Адресное слово через усилитель 10 устройства 83 поступает на входы 55 дешифраторов 7 адреса остальных устройств 83. Работа дешифраторо синхронизируется импульсами тактовой частоты, которые поступают через усилитель 13 с магистрали 23 на элемент И 40, с выхода которого через формирователь импульсов 35 они проходят на вход 58 дешифратора 7 адреса. Если адрес устройства и информация в адресном слове совпадают, происходит появление единичного уровня на выходе 26 дешифратора 7 адреса, который через усилитель 11 выставляется на магистраль 21 подтверждения. Дешифратор 7 адреса выполняет функции схемы подтверждения обращения к устройству. Если блок 2 буферной памяти устройства 83j занят, то дешифратор 7 адреса через усили- тель 11 держит на магистрали 21 уро- вень логического О.

З ровень с магистрали 21 через усилитель 12 поступает на адресный вход

5 Q 5

5 0 5 Q .

0

демультиплексора 36 устройства 83; , переключая направление прохождения синхроимпульс на счетный вход счетчика 31 и на второй вход элемента ИЛИ 18. Выходы счетчика 31 подключены к вторым адресньм входам 73 блока 1 буферной памяти. По синхроим- .. пульсу происходит чтение слова пакета, определяемого содержимым счетчика 30 по адресу, хранящемуся в счетчике 31, на магистраль 19. По заднему фронту синхроимпульса происходит наращивание содержимого счетчика 31. После того, как пакет считан (переполнение счетчика 31), на выходе счетчика 31 образуется импульс, который поступает на З-вход триггера 33, устанавливая его в состояние логической 1. Этим же импульсом увеличивается содержимое счетчика 30, тем самым осуществляется переход по чтению к следующему пакету в очереди, сбрасывается схема 9 захвата, освобождается магистраль 19. Длительность импульса переноса счетчика 31 не превышает времени переключения триггера 33 .

Синхросигналы с генератора 8 поступают на вход формирователя 34 импульсов, работающего по заднему фрон ту импульса, исключение этого элемента позволяет получить на входах элементов И 41 и 42 последовательность сдвинутых по фазе синхроимпульсов. На выходе элемента И 42 образуется фронт, которьй уменьшает на единицу содержимое счетчика 32 и сбрасывает триггер 33, D-вход которого подклю-. чен к логическому О. Такой способ включения счетчика 32 позволяет в любой момент времени контролировать содержимое блока 1 буферной памяти и производить одновременно запись.пакета данных в блок 1 буферной памяти и чтение пакета на магистраль 19.

Если блок 1 буферной памяти жит еще пакеты, что характеризуется состоянием счетчика 32, и магистраль 19 свободна (отсутствует уровень на магистрали 22), устройство 83j может захватить магистраль 19. Рассмотрим передачу пакета данных, передаваемого по магистрали 19 в блок 2 буферной памяти устройства 83 j, Синхроимпульс с устройства 83; по магистрали 23 через усилитель 13, элемент; И 17, открытый уровень на выходе 26 дешифратора 7 адреса поступает на

вход записи блока 2 буферной пгмяти и через элемент ИЛИ 45 на счетный вход счетчика 4, выходы которого присоединены к адресным входам блска 2 буферной памяти. По импульсу проходит запись слова данных в блок 2 буферной памяти, а по заднему его фронту - увеличение содержимого счетчика 4. После переполнения счетчика (пакет принят) на его выходе образуется импульс, переключающий счетный триггер 5 в единичное положение, тем самым выставляя на выход 24 уровень, свидетельствующий о том, что пакет принят. После этого ЭВМ 82j начинает чтение пакета из блока 2 буферной памяти. Импульсы чтени: поступают на счетньЕй вход счетчика 4 через элемент ИЛИ 45 .и на вход чтения блока 2 буферной памяти. По импульсу происходит чтение.слова, а по его заднему фронту - увеличение содержимого счетчика U, После пакета на выходе переноса счетчика 4 появляется импульс, возвращающий триггер 6 в нулевое состоя1-ше, ;то свидетельствует по выходу 24 в ЭВМ 82j об освобождении блока 2 буферной памяти.

Блок 1 буферной памяти (фиг.2} образует входную очередь. В начсле работы запись производится в первый узел 67, памяти. Сигнал записи i. дит через открытый элемент И 68 на вход записи соответствующего узла 67 памяти. Элементы И 68 подключаются соответственно к первьм входам 4 выборки. Узел 67с памяти адресуется через адресный вход 72 и мультипле: - сор 70, После заполнения первого узла 67, памяти открьшается по входу :5апи- cii 50 следующий элемент И 68. Таким образом, по записи становится достугг ным второй узел 672 памяти и т,д -. Чтение происходит начиная с первого узла 67, памяти. Сигнал чтения поступает на вход чтения узла 67 памяти через открытый по второму входу 48 выборки элемент И 69, переключая , мулва-иплексор 70 с входа 72 адрес:а н вход 73 адреса. Одновременно по сигналу чтения с входа 27 формируетс.я импульс -чтения узла 67 памяти ЧЕ1рез формирователь 71. Затем осуществляется переход к чтению узла 67 памяти

и т,д. ..

Схема 9 захвата (фнг.З) рабоТсйт

сле,о;; 014:::-Запросы

поступают с входа 61 на D- вход триггера 76. Если магистраль 22 находится в состоянии логического О, то на входе 60 счетчика 74 находится нулевой уровень, разрешающий счет, При поступлении импульсов на вход 57 происходит последовательное наращивание его значения,

Начальное значение счетчика 74 задается значением регистра 75, представляющего соответствующий приоритету устройства 83 набор логических

О и

Чем выше приоритет устрой0

0

5

0

0

5

ства, тем больщее двоичное значение находится на выходе регистра 75, Как только возникает переполнение счетчика, на его выходе возникает импульс переноса, поступающий на С-вкод триггера 76, переводя его в единичное состояние. Триггер 76 выставляет с выхода 20 через усилитель 15 на магистраль 22 единичньй уровень. Уси- литепь 16 всех устройств 83 производит передачу этого уровня на вход 60 счетчиков 74, производя их начальну установку. Сброс триггера 76 осуществляется подачей сигнала на вход 49 Ш1И 77. Таким образом, в один момент времени возможен захват магистрали 19 только одним устройством.

Схема дешифратора 7 адреса (фиг.4) представляет собой схему 78 сравнения. Код адреса устройства 83 задается регистром 79, преде та ВЛЯЮЕДИМ набор логических О и в зависимости от адреса устройства. Схема 78 сравнения синхронизируется сигналамя на входе 58, При совпадении адреса устройства, задаваемого регистром 79, с информацией на входе 55 импульсы с выхода схемы 78 сравнения поступа-. ют на вход элемента И 81 и, если бл 2 буферной памяти адресуемого ус т . ства 83; свободен (логическая Т на входе 25), импульсы с выхопя элемента И 81 поступают на С-вход триггера 80 (D-ВХОД в состоянии логической 1), переключая его в единично:; . положение, свидетельствующее о т:;..- что устройство выбрано. Единичный потенциал с триггера 80 выставляет ;.; на выход 26 выборки дешифратора адреса. Триггер 80 сбрасывается уровне.к логического

О на входе 59,

о р м у л а изо 5 р е т е н

. Устройство для сопряжения ап

томК К , ;-Чд-;с; К 8 .-.г : -- .;;

жащее nepsbri t и BTopoii блоки буферной памяти, два счетчика, два триггера, дешифратор адреса, генератор импульсов., схему захвата, усилитель, эле- менты И и ИЛИ, ггри этом информационный вход-выход устройства подключен к первому входу-выходу усилителя, вход блокировки которого подключен к выходу захвата устройства и выхо- ду схемы захвата, первые адресные входы первого и адресные входы второго блоков буферной памяти подключены к информационным выходам соответственно первого и второго счетчиков, выход переноса первого счетчика подключен к входу установки в 1 первого триггера, а выход переноса второго счетчика - к синхровходу второго триггера, инверсный выход кото- рого подключен к выходу занятости второго блока буферной памяти и к управляющему вхо;; у дешифратора адреса, выход выборки которого соединен с первым входом первого элемента И и выходом подтверждения подключения стройства, вход чтения первого блока буферной п-амяти соединен с выходом первого элемента ИЛИ, отличающееся тем, что, с целью повыше- ния производительности за счет создания на передающей стороне очереди пакетов с возможностью передачи пакета по межмашинной магистрали с однопервого блока буферной памяти соеди- , нен с информационным выходом второго блока буферной памяти и с входом-выходом данных устройства, а информационный выход первого блока буферной памяти соединен с информационным входом второго блока буферной памяти, инфот ч.-.ционн1)Гм входом дешифратора адрес: н вторым входом-выходом усилителя, Еюрые лдчресные входы первого блока буферной памяти соединены с информационными выходами пятого счетчика, счетный вход которого соединен с первым выходом демультиплексора, первым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, второй вход которого соединен с вторым выходом демультиплексора и вторым входом первого элемента ПТИ, выход второго элемента ИЛИ соединен с выходом синхронизации устройства, вход синхронизации устройства подключен к первому входу второго элемента И и второму входу первого элемента И, выход которого подключен к входу записи второго блока буферной памяти, и к первому входу третьего элемента ИЛИ, второй вход которого соединен с входами чтения устройства и второго блока буферной памяти, выход первого триггера соединен с первым входом третьего элемента И, выход которого соединен с входом прямого счета шес

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1460724A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с магистралью | 1984 |

|

SU1246107A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

Изобретение относится к вычислительной технике и используется для построения многомашинных вычислительных систем. Цель изобретения - пов ышение производительности -устройства за счет создания на передающей стороне очереди пакетов с возможностью передачи пакета по межмашинной магистрали с одновременным приемом в блок буферной памяти следующего пакета. С этой целью устройство содержит два блока 1,2 буферной памяти, причем блок 1 содержит п подблоков, аналогичных блоку 2. 1 з.п. фтлы, 5 ил.

временным приемом в блок буферной па-э того счетчика и с синхровходом пермятк следующего пакета, в устройство введены четыре счетчика, третий триггер, два формирователя импульсов, демультиплексор, три дешифратора, четыре элемента И, два элемента ИЛИ, эл.емент НЕ, причем выход переноса . первого счетчика подключен к счетному входу третьего счётчика, информационные выходы которого соединены -с входами первого дешифратора, выходы которого соединены с первьми входами выборки первого блока буферной памяти, вторые входы выборки которого .. соединены с выходами второго дешифратора, входы которого соединены с информационными выходами четвертого счетчика, счетный вход которого соединен с выходом переноса пятого счетчика, с входом установки в 1 третьего триггера, и входом сброса схе- слы захвата, вход записи первого блока буферной памяти соединен со счетным входом первого счетчика и входом записи устройства, информационный вход

40

45

50

55

вого триггера, выход третьего тригге ра соединен с первым входом четвертого элемента И, выход которого соединен с входом обратного счета шестого счетчика и с синхровходом тре-. тьего триггера, выход генератора импульсов соединен с вторым входом третьего элемента И, входом первого формирователя импульсов, тактовым входом схемы захвата и информационным входом демультиплексора, вход запрета которого соединен с выходом схемы захвата, а адресный вход - с входом подтверждения подключения устройства, входом элемента НЕ, выход которого подключен к второму вхо ду второго элемента И, выход роторо го соединен с входом второго форми- рователя импульсов, выход которого подключен к тактовому входу дешифратора адреса, вход сброса которого подключен к входу захвата устройства и входу установки в 1 схемы захвата, вход запроса которой подключен

0

5

0

5

вого триггера, выход третьего триггера соединен с первым входом четвертого элемента И, выход которого соединен с входом обратного счета шестого счетчика и с синхровходом тре-. тьего триггера, выход генератора импульсов соединен с вторым входом третьего элемента И, входом первого формирователя импульсов, тактовым входом схемы захвата и информационным входом демультиплексора, вход запрета которого соединен с выходом схемы захвата, а адресный вход - с входом подтверждения подключения устройства, входом элемента НЕ, выход которого подключен к второму входу второго элемента И, выход роторо- го соединен с входом второго форми- рователя импульсов, выход которого подключен к тактовому входу дешифратора адреса, вход сброса которого подключен к входу захвата устройства и входу установки в 1 схемы захвата, вход запроса которой подключен

к выходу пятого элемента И, iервый вход которого соединен с входом запроса на захват устройства, а второй вход - с входом занятости первого блока буферной памяти и младшим информационным выходом третьего дешифратора , старший информационньгй выход которого соединен с выходом требования приема информации в первый блок ;буферной памяти устройства, информа- (ционный вход третьего дешифратора соединен с информационным выходом шестого счетчика, выход первого формирователя импульсов соединен с вто- рым входом четвертого элемента И; выход третьего элемента ИЛИ соединен со счетйым входом второго счетчика, вход начальной установки устр йства соединен с входами начальной станов ки всех счетчиков, триггеров .ч схемы захвата.

2, Устройство по п. 1, о т л и - чающе. еся тем, что перьый блок буферной памяти содержит п подблоков каждый из которых содержит узел памяти, два элемента И, мультиплексор адреса, формирователь импульсов, причем информационньш вход первого блока буферной памяти соединен с входами данных узлов памяти

всех подблоков, а информационный выход первого блока буферной памяти соединен с выходами данных узлов па- мяти всех подблоков, первые входы выборки первого блока буферной памяти соединены с первыми входаму первых элементов И каждого подблока соответственно, а вторые входы выборки первого блока буферной памяти - с первыми входами вторых элементов И ка:ждого подблока, выходы мультиплс к соров адреса соединены с адресньп-1и входами соответствующих узлов памяти подблоков, вход записи первого блока буферной памяти соединен с вторыми входами первых элементов И каждого подблока, а вход чтения первого блок буферной памяти - с вторыми входами вторых элементов И каждого подблока, входы данных мультиплексоров адреса каждого подблока соединены с первым и вт орым адресными входами первого блока буферной памяти, причем в каждом подблоке выход первого элемента И соединен с входом записи узла памяти, выход второго элемента И соединен с входом формирователя импульсов и управляющим входом мультиплексора адреса, выход формирователя импульсов соединен с входом чтения узла памяти.

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| С, 06 F 13/12, 1981 , Авторское свидетельство СССР , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-07—Публикация

1987-01-26—Подача