обмена соединен с четвертым входом блака управления.и является пятым входом устройства, четвертый вход первого блока усиления, второй вход блока управления и третий вход второго блока усиления соединены с четвертым входом блока регистров,вто рой вход второго блока усиления соединен с первым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для согласования интер-фЕйСОВ | 1979 |

|

SU822166A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для управления вводом- ВыВОдОМ | 1979 |

|

SU794631A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Устройство для обмена данными | 1974 |

|

SU506847A1 |

УСТРОЙСТВО ДЛЯ ВВОДАЫЯВОДА ИНФОРМАЦИИ, содержащее перэый и второй блоки усиления, коммутатор, регистр, блок регистров, первый и второй блоки прерьшаний, дешифратор, блок управления, селектор и- блок обмена, входы-вЬкоды группы первого и второго блоков усиления являются соответственно входами-выходами первой и второй групп устройства, первые вход и выход первого блока усиления соединены соответственно с первыми выходом и входом первого блока пре(шваний, вторые вход и выход первого блока усиления соединены с первым выходом и первым входом блока обмена, .второй выход которого соединен с первым входом коммутатора, второй вход которого соединен с первым вьЬсодом второго блока усиления второй выход которого соединен с вторым входом второго блока прерываний-и первым входом блока регистров, первый выход которого соединен с перт вым входом второго блока прерываний, первый выход которого соединен с четвертым входом коммутатора, третий вход которого соединен с вторым выходом блока регистров, второй вход которого соединен с выходом дешифратора и первым входом второго блока усиления, первый выход селектора соединен с вторым входом блока обмена, отл.и чающееся тем, что, с целью повьш1ения быстродействия устройства, в него введен блок постоянной памяти, выход которого является первым выходом устройства, третьи входы блока постоянной памяти и первого блока прерываний являются первым входом устройства, второй выход второго блока прерываний соединен с вторым входом блока постоянной памяти, первый вход которого соединен с вторым выходом первого блока прерываний, второй вход которого сое(Л динен с шестым входом коммутатора, первым входом блока управления и является вторым входом устройства, третий выход первого блока усиления соединен с пятым входом коммутатора, выход которого соединен с входом регистра, выход которого является вторым выходом устройства, седьмой вход коммутатора соединен с вторым 00 выходом блока управления, третий 4 выход которого соединен с третьим входом блока регистров, четвертый вход которого является третьим входом устройства, пятый вход блока регистров соединен с вторым входом дешифратора, входом селектора, третьими входами блока управления и первого блока усиления и является четвертым входом устройства, второй выход селектора соединен с пятым входом блока управления, четвертый выход которого соединен с первым входом селектора, третий вход блока

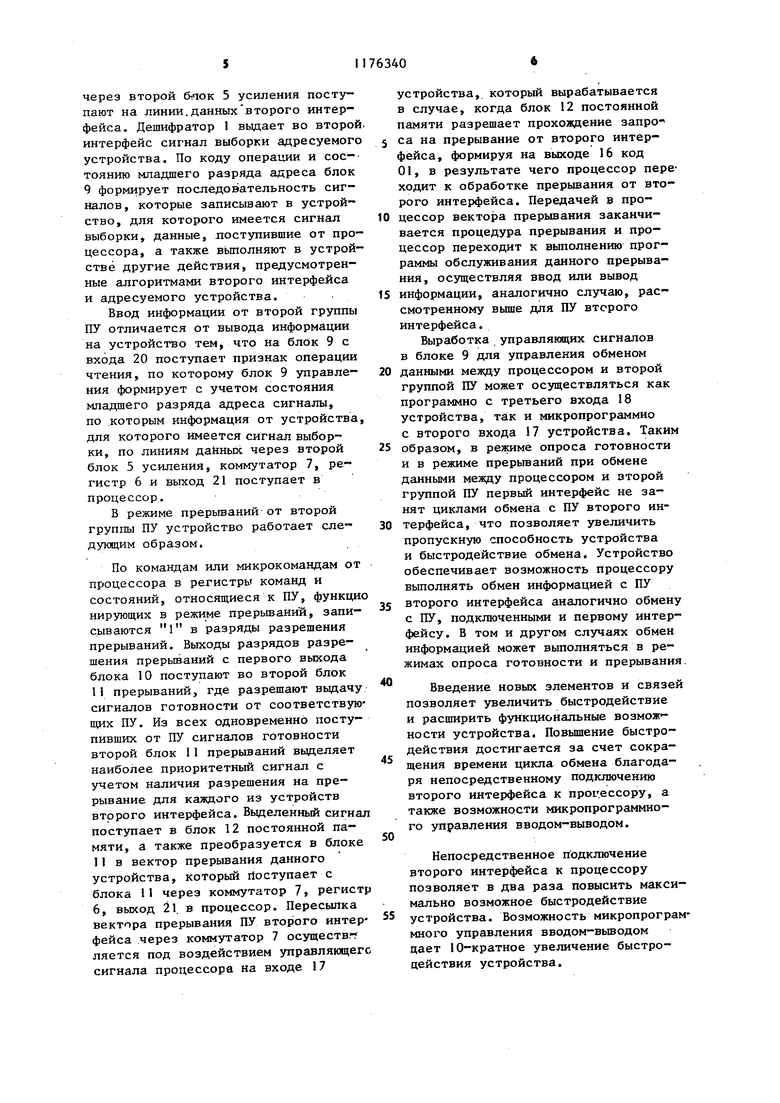

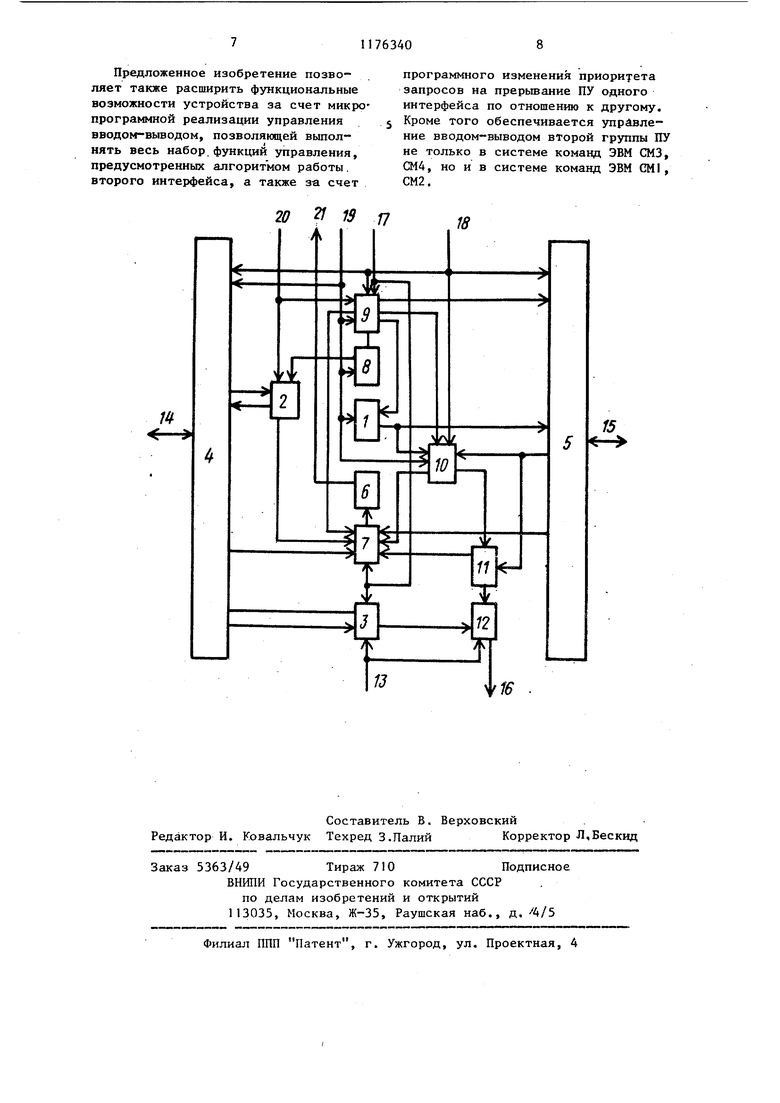

Изобретение относится к вычислительной технике и может быть использовано для построения систем ввода-вывода периферийных процессо ров, ЭВМ и управляющих вычислитель ных комплексов на их базе,,использующих интерфейс.Общая шина и со держащих периферийные устройства (ПУ) интерфейса с радиальными свя зями для сигналов выборки и призна ков готовности. Цель изобретения - повышение быстродействия устройства. На чертеже представлено устройс для ввода информации. Устройство содержит дешифратор 1, блок 2 обмена, первый блок 3 прерываний, первый и второй блоки4 и 5 усиления, регистр 6, коммута тор 7, селектор 8, блок 9 управления, блок 10 регистров, второй бло 1 1 прерываний, блок 12 постоянной памяти, первый вход 13, первую и в рую группы 14 и I5 входов-выходов первый выход 16, второй, третий, четвертый и пятый входы 17-20, вто рой выход 2. Устройство для управления вводом-выводом работает следующим образом. Устройство осуществляет обмен данными между процессором и ПУ, подключенными к первому или второму интерфейсу в режиме опроса готовности и в режиме .грерьшаний. Первый интерфейс представляет собой унифицированную систему магистральных -связей между процессором, оперативной памятью и ПУ. Второй интерфейс представляет собой унифицированную систему магистральных шин данных и управляющих сигналов,. - также радиальных шин сигналов и готовности, Kгiждoмy ПУ подключенному ко второму интер{«йсу, соответствуют два адреса на зходной адресной шине 19: адрес регистра команд и состояний и адрес регистра данных. В зависимо сти от адреса, поступающего по адресной шине на четвертый вход устройства 19 и на селектор 8, последний разрешает работу блока 2 обмена, управляющего обменом информацией по первому интерфейсу, либо блока 9 выдачи управляющих сигналов, управляющего обменом информацией со второй группой ПУ. В режиме опроса готовности первой группы ПУ устройство работает следующим образом. Перед обменом информацией с ПУ осуществляется опрос готовности этого устройства путем чтения и анализа содержимого его регистров состояния. С этой целью процессор выдает адрес регистра состояния ввода или вывода устройства на вход 19 и признак операции Чтение на вход 20. Селектор 8 определяет принадлежность адреса к диапазону адресов первого интерфейса и запускает в работу блок 2 обмена, который управляет обменом информатдией по первому интерфейсу, обеспечивая в данном . случае чтение выбранного регистра состояния со входов-выходов 14 через первый блок 4 усиления, коммутатор 7, регистр 6, выход 21 на вход процессода. Если разряд готовности будет в 1, процессор переходит к выполнению операции обмена информа1щей с соответствующим устройством первого интерфейса, если же разряд готовности будет в О, процессор периодически повторяет операцию чтения регистра состояний этого ПУ до получения 1 в разряде готовнос-. ти.

3

При вводе информации процессор выдает адрес регистра данных ввода . устройства на вход 19 и признак операции Чтение на вход 20. Селектор. 8 запускает блок 2 обмена, который обеспечивает чтение регистра данных ПУ со входов-выходов 14 через первый блок 4 .усиления, коммутатор 7, ре-:гистр 6, выход 21 на вход процессора.

При вьщаче информации процессор устанавливает адрес регистра данных вывода на вход 19 и признак операции Запись или Запись байта на вход 20. Селектор 8 запускает блок 2 обмена, который обеспечивает выдачу адреса с входа 19, данных с входа 18 и кода операции через первый блок 4 усиления, вход-выход 14 на вход ПУ и запись информации в адресуемый регистр данных.

В режиме прерьшаний от первой группы ПУ устройство функционирует следующим образом.

В режиме прерываний от первой группы ПУ устройство функционирует следующим образом.

В регистры состояний первой группы ПУ, которым разрешается работать в режиме прерываний, записываются 1 в разряды разрешения прерываний через первый блок 4 усиления с определенного разряда входа 18. Запросы на прерывание от ПУ первого интерфейса поступают через первый блок 4 усиления на первый вход первого блока 3 прерываний, который выделяет самый приоритетный запрос на прерывание, сравнивает его с приоритетом выполняющейся программы, поступающим на вход блока 3 с входа 13, и, если приоритет поступившего запроса вьше, при появлении разрешающего сигнала на своем втором входе выдает сигнал на прерывание в блок 12 постоянной памяти. При нулевом значении сигнала на втором или третьем входах блока 12 последний разрешает прохождение запроса на прерывание от первой группы ПУ, формируя на выходе 16 код 10. Получив этот код, процессор переходит к обработке прерывания от первого интерфейса, в процессе которого принимает вектор прерывания ПУ, поступаюций с входавыхода 14 через первый блок 4 усиления, коммутатор 7, регистр 6, выходную информационную шину 21. Передачей в

763404

процессор вектора прерывания заканчивается процедура прерывания.,Затем процессор переходит к выполнению программы обслуживания прерывания, 5 в процессе которого осуществляет обмен очередным символом с ПУ, как описано выше.

В режиме обмена по опросу готовности второй группы ПУ устройство раfO ботает следующим образом.

Перед обменом информацией с ПУ второго интерфейса осуществляется опрос готовности этого устройства с помощью команд чтения соответствую 5 щего регистра в блоке 10 регистров. С этой целью процессор устанавливает адрес регистра команд и состояний требуемого устройства на вход 19 и признак операции Чтение на вход

20 20. Младшие разряды адреса с входа 19 поступают на пятый вход блока 10, определяя выбор адресуемого регистра команд и состояний. Одновременно селектор 8 определяет принадлежность

25 адреса диапазону адресов ПУ второго интерфейса и через свой второй выход запускает в работу блок 9 управления, который обеспечивает чтение выбранного регистра команд и состояний

3Q блока 10 в процессор через коммутатор 7, регистр 6 и выход 21, причем состояние разряда, соответствующего готовности устройства, считывается непосредственно с радиальной шины готовности, адресуемого устройства. Если разряд готовности будет в 1, процессор переходит к выполнению операции обмена информацией с соответствующим устройством второго интер-.

фейса, если же разряд готовности будет в О, то процессор периодически повторяет операцию чтения этого регистра команд и состояний до получения 1 в разряде готовности. При чтении регистров команд и состояний никакие управляющие сигналы во второй интерфейс не выдаются.

При выводе информации адрес устройства, подключенного к второму

интерфейсу, поступает на селектор 8 и дешифратор свхода 19,данные- свхода 18, и признак операции записи - на четвертый вход блока 9 с входа 20, На третий вход блока 9 с входа 19

поступает младший разряд адреса в качестве признака работы с регистром данных или регистром команд и состояний ПУ. Данные с входа 18

через второй блок 5 усиления поступают на линии.данныхвторого интерфейса. Дешифратор 1 выдает во второй интерфейс сигнал выборки адресуемого устройства. По коду операции и сое- тоянию младшего разряда адреса блок 9 формирует последовательность сигналов, которые записывают в устройство, для которого имеется сигнал выборки, данные, лоступившие от процессора, а также вьтолняют в устройстве другие действия, предусмотренные алгоритмами второго интер|фейса и адресуемого устройства.

Ввод информации от второй группы ПУ отличается от вывода информации на устройство тем, что на блок 9 с входа 20 поступает признак операции чтения, по которому блок 9 управления формирует с учетом состояния младшего разряда адреса сигналы, по .которым информация от устройства для которого имеется сигнал выборки, по линиям дайных через второй блок 5 усиления, коммутатор 7, ре гистр 6 и выход 21 поступает в процессор.

В режиме прерьгоаний от второй группы ПУ устройство работает следующим образом.

По командам или микрокомандам от процессора в регистры команд и состояний, относящиеся к ПУ, функцио нирующих в режиме прерываний, записываются 1 в разряды разрешения прерываний. Выходы разрядов разрешения прерываний с первого выхода блока 10 поступают во второй блок 11 прерываний, где разрешают выдачу сигналов готовности от соответствую щих ПУ. Из всех одновременно поступивших от ПУ сигналов готовности второй блок 11 прерываний выделяет наиболее приоритетный сигнал с учетом наличия разрешения на прерывание для каждого из устройств второго интерфейса. Выделенный сигнал поступает в блок 12 постоянной памяти, а также преобразуется в блоке 11 в вектор прерывания данного устройства, который rtoступает с блока 1 через коммутатор 7 регистр 6, выход 21. в процессор. Пересылка вектора прерывания ПУ второго интерфейса через коммутатор 7 осуществг ляется под воздействием управляющего сигнала процессора на входе 17

устройства,, который вырабатывается в случае, когда блок 12 постоянной памяти разрешает прохождение запро- 5 са на прерывание от второго интерфейса, формируя на выходе 16 код 01, в результате чего процессор пере ходит к обработке прерывания от второго интерфейса. Передачей в процессор вектора прерывания заканчивается процедура прерывания и процессор переходит к выполнению программы обслуживания данного прерывания, осуществляя ввод или вывод

5 информации, аналогично случаю, рассмотренному выше для ПУ второго интерфейса.

Выработка управляющих сигналов в блоке 9 для управления обменом

0 данными между процессором и второй группой ПУ может осуществляться как программно с третьего входа 18 устройства, так и микропрограммно с второго входа 17 устройства. Таким

5 образом, в режиме опроса готовности и в режиме прерьгеаний при обмене данными между процессором и второй группой ПУ первый интерфейс не занят циклами обмена с ПУ второго интерфейса, что позволяет увеличить пропускную способность устройства и быстродействие обмена. Устройство обеспечивает возможность процессору выполнять обмен информацией с ПУ

5 второго интерфейса аналогично обмену с ПУ, подключенными и первому интерфейсу. В том и другом случаях обмен информацией может выполняться в режимах опроса готовности и прерывания.

Введение новьк элементов и связей

позволяет увеличить быстродействие и расширить функциональные возможности устройства. Повышение быстродействия достигается за счет сокращения времени цикла обмена благодаря непосредственному подключению второго интерфейса к прог.ессору, а также возможности микропрограммного управления вводом-выводом.

Непосредственное подключение второго интерфейса к процессору позволяет в два раза повысить максимально возможное быстродействие 5 устройства. Возможность микропрограммного управления вводом-вьшодом дает 10-кратное увеличение быстродействия устройства.

Предложенное изобретение позволяет также расширить функциональные возможности устройства за счет микропрограммной реализации управления вводом-выводом, позволяющей выполнять весь набор, функций управления, предусмотренных алгоритмом работы. второго интерфейса, а также за счет 2f

программного изменения приоритета запросов на прерывание ПУ одного интерфейса по отношению к другому. Кроме того обеспечивается управление вводом-выводом второй группы ПУ не только в системе команд ЭВМ СМЗ, СМ4, но и в системе команд ЭВМ CMI, СМ2. 19

Авторы

Даты

1985-08-30—Публикация

1983-12-30—Подача