Изобретение относится к микропроцессорной технике и предназначено для организации дисциплины приоритетных прерываний в микропроцессорных системах управляющих и вычислительных комплексов.

Цель изобретения - повышение быстродействия обработки прерываний.

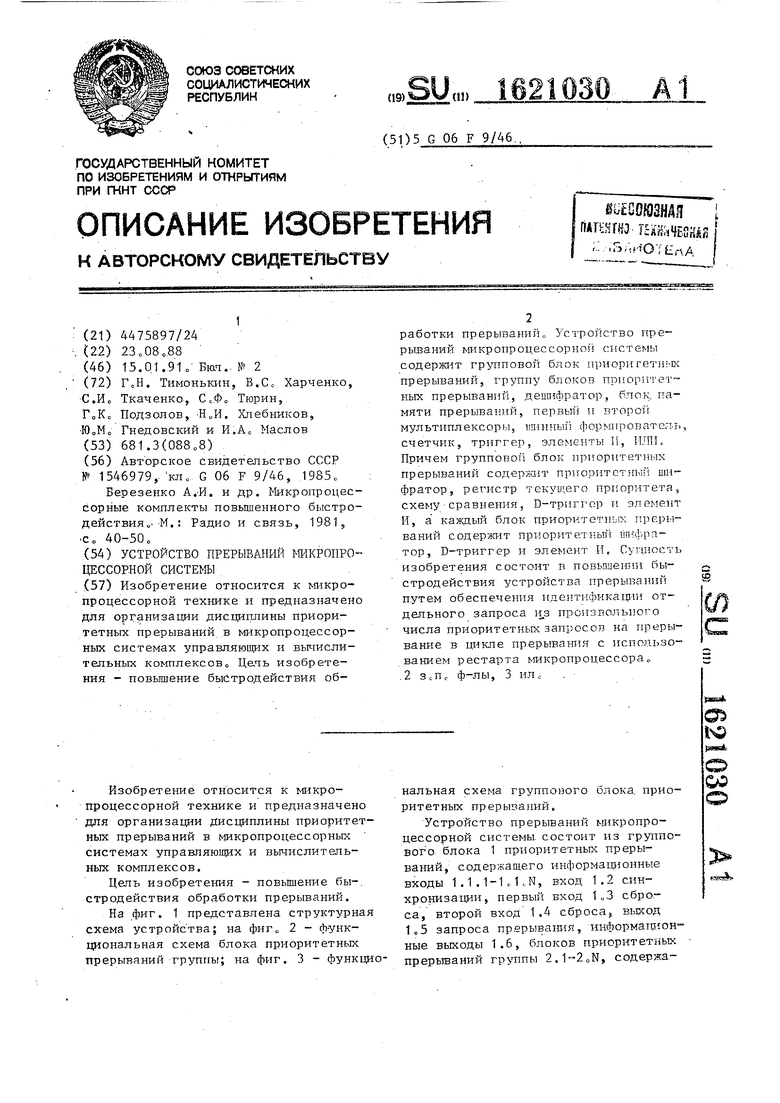

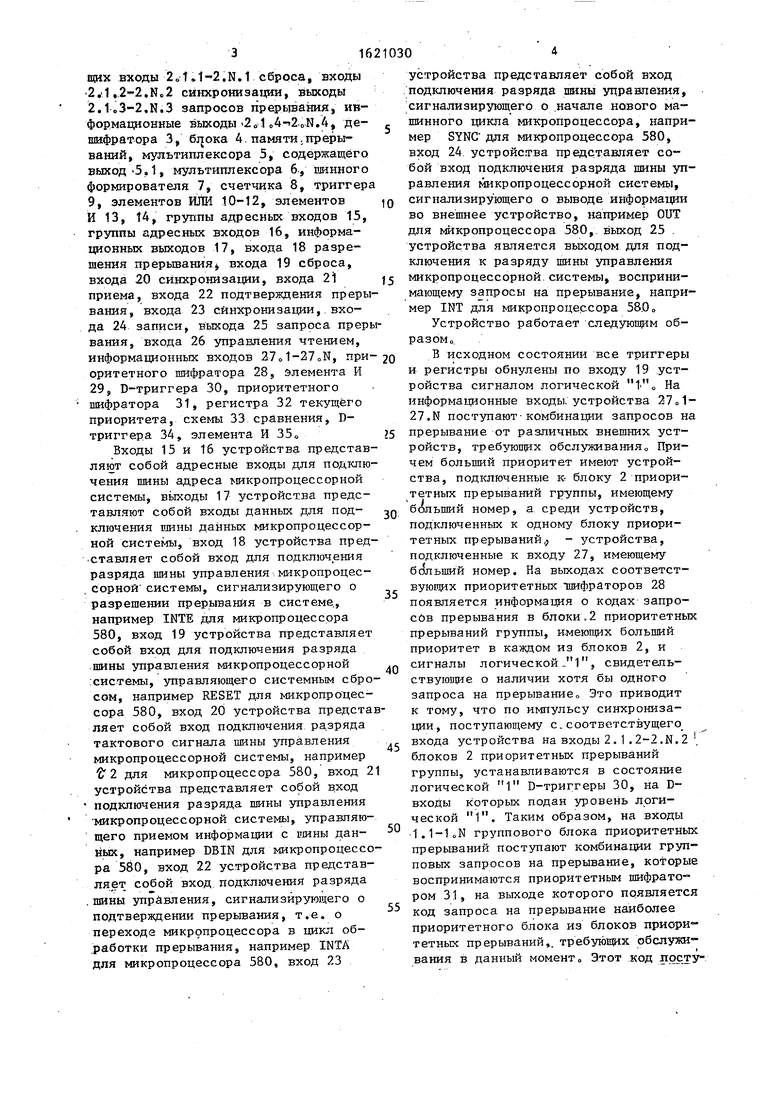

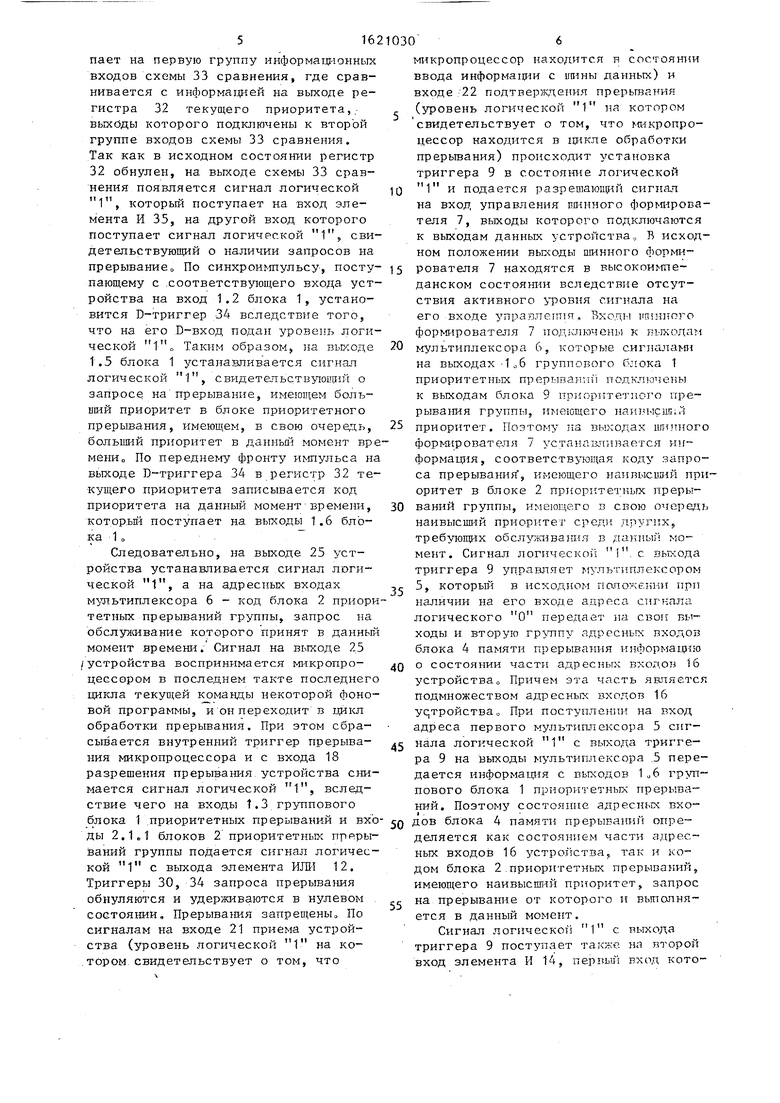

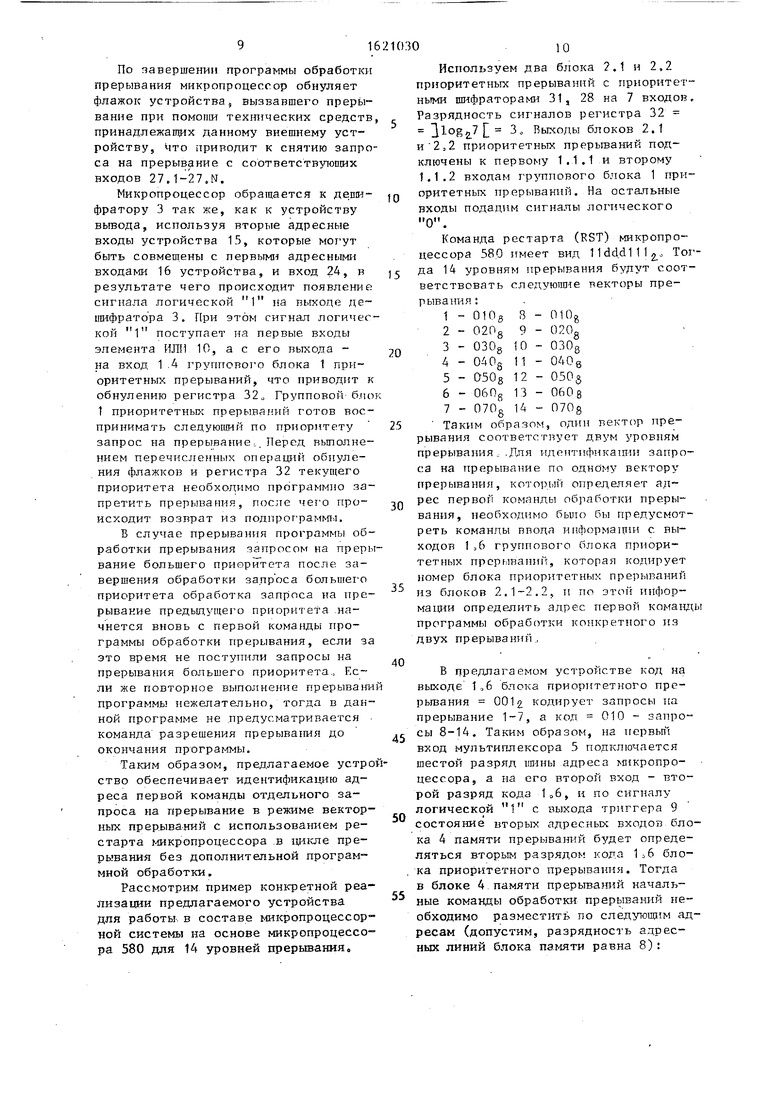

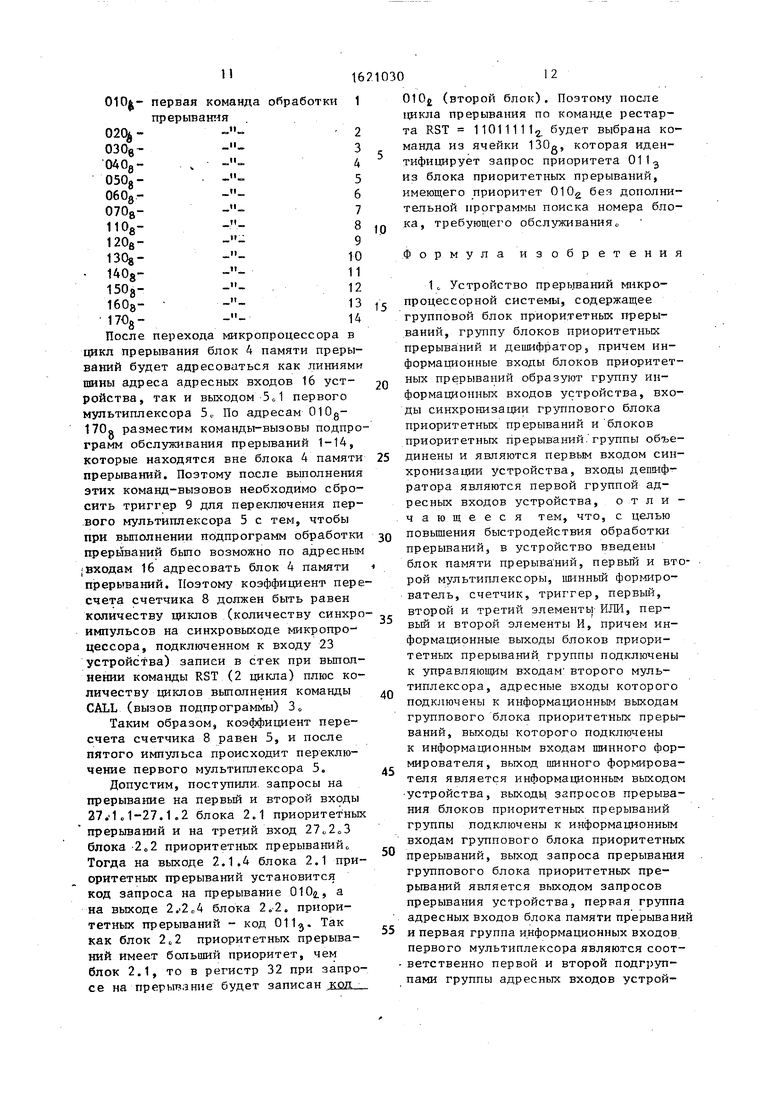

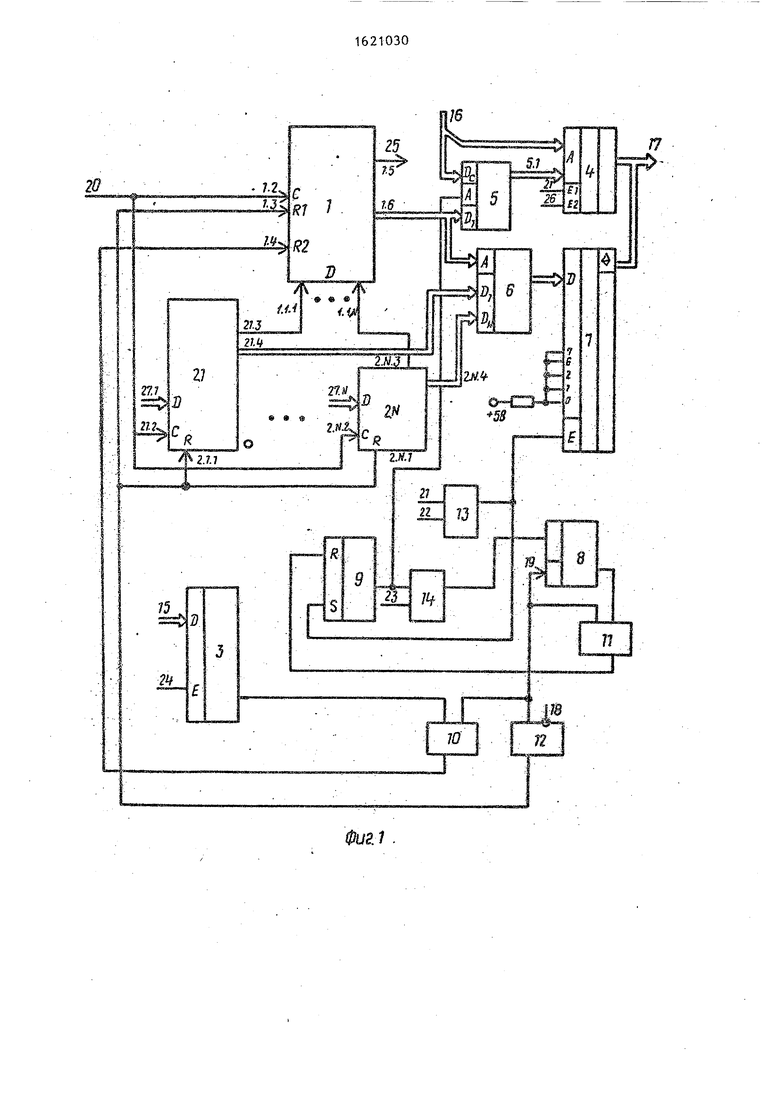

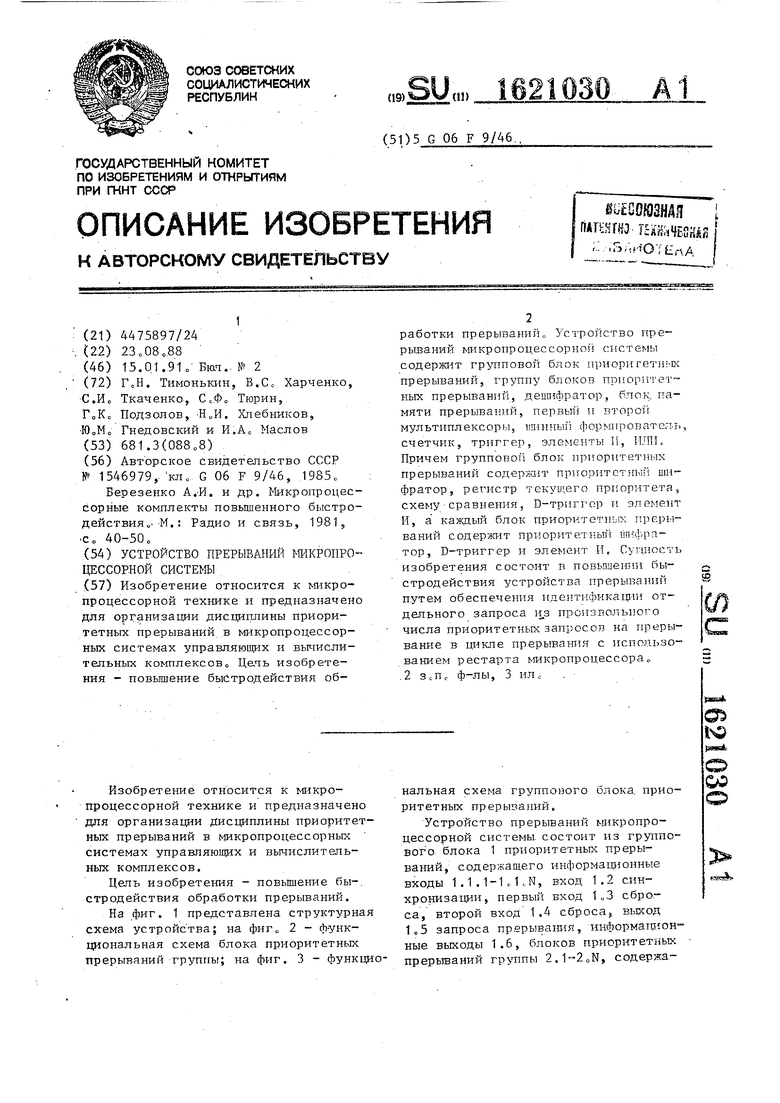

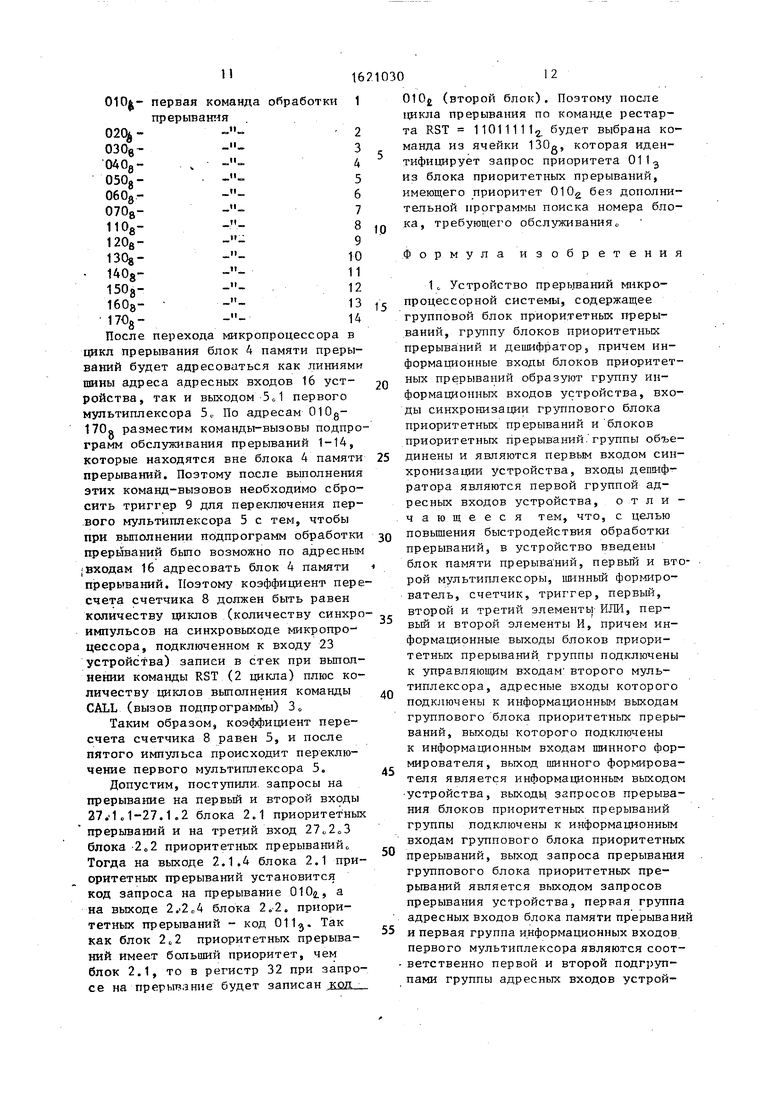

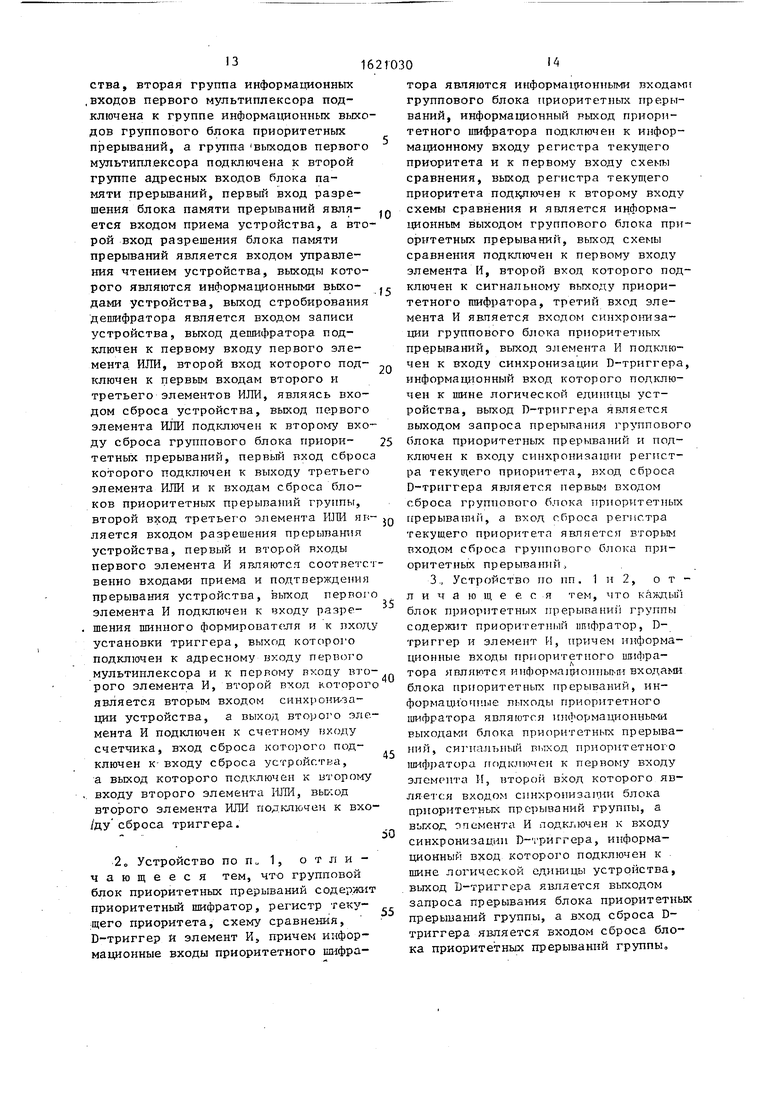

На фиг. 1 представлена структурная схема устройства; на фиг„ 2 - функциональная схема блока приоритетных прерываний группы; на фиг. 3 - функциональная схема группового блока приоритетных прерываний.

Устройство прерываний микропроцессорной системы состоит из группового блока 1 приоритетных прерываний, содержащего информационные входы 1.1.1-b1cN, вход 1.2 синхронизации, первый вход 1„3 сброса, второй вход 1.4 сброса, выход 1„5 запроса прерывания, информационные выходы 1.6, блоков приоритетных прерываний группы 2.1-2..N, содержаю

Ив

о

СЈ

К5ЧЯ

щих входы .N.1 сброса, входы 2. 1.,NC2 синхронизации, выходы 2.1o3-2,N.3 запросов прерывания, информационные выходы 201,.4, де- шифратора 3, 4 памяти,прерываний, мультиплексора 5, содержащего выход 5.1, мультиплексора 6, шинного формирователя 7, счетчика 8, триггер 9, элементов ИЛИ 10-12, элементов И 13, t4, группы адресных входов 15, группы адресных входов 16, информационных выходов 17, входа 18 разрешения прерывания входа 19 сброса, входа 20 синхронизации, входа 21 приема, входа 22 подтверждения прерывания, входа 23 синхронизации, входа 24 записи, выхода 25 запроса прервания, входа 26 управления чтением, информационных входов 2701-270N, при оритетного шифратора 28, элемента И 29, D-триггера 30, приоритетного шифратора 31, регистра 32 текущего приоритета, схемы 33 сравнения, I)- триггера 34, элемента И 350

Входы 15 и 16 устройства представляют собой адресные входы для подключения шины адреса микропроцессорной системы, выходы 17 устройства представляют собой входы данных для под- клгачения шины данных микропроцессорной системы, вход 18 устройства представляет собой вход для подключения разряда шины управления микропроцессорной системы, сигнализирующего о разрешении прерывания в системе, например INTE для микропроцессора 580, вход 19 устройства представляет собой вход для подключения разряда шины управления микропроцессорной системы, управляющего системным сбросом, например RESET для микропроцессора 580, вход 20 устройства предсталяет собой вход подключения разряда тактового сигнала шины управления микропроцессорной системы, например t2 для микропроцессора 580, вход 2 устройства представляет собой вход подключения разряда шины управления микропроцессорной системы, управляющего приемом информации с шины дан ных, например DBIN для микропроцессора 580, вход 22 устройства представляет собой вход подключения разряда шины управления, сигнализирующего о подтверждении прерывания, т.е. о переходе микропроцессора в цикл обработки прерывания, например INTA для микропроцессора 580, вход 23

,

gд 20 5

о35

40

45

50

55

устройства представляет собой вход подключения разряда шины управления, сигнализирующего о начале нового машинного цикла микропроцессора, например SYNC для микропроцессора 580, вход 24 устройства представляет собой вход подключения разряда шины управления микропроцессорной системы, сигнализирующего о выводе информации во внешнее устройство, например OUT для микропроцессора 580, выход 25 устройства является выходом для ттод- ключения к разряду шины управления микропроцессорной системы, воспринимающему запросы на прерывание, например INT для микропроцессора 580

Устройство работает следующим об- разом0

В исходном состоянии все триггеры и регистры обнулены по входу 19 устройства сигналом логической На информационные входы устройства 27„1- 27.N поступают комбинации запросов на прерывание от различных внешних устройств, требующих обслуживания Причем больший приоритет имеют устройства, подключенные к блоку 2 приоритетных прерываний группы, имеющему больший номер, а среди устройств, подключенных к одному блоку приоритетных прерываний,; - устройства, подключенные к входу 27, имеющему больший номер. На выходах соответствующих приоритетных -шифраторов 28 появляется информация о кодах запросов прерывания в блоки.2 приоритетных прерываний группы, имеющих больший приоритет в каждом из блоков 2, и сигналы логической 1, свидетельствующие о наличии хотя бы одного запроса на прерывание Это приводит к тому, что по импульсу синхронизации, поступающему с. соответствущего входа устройства на входы 2, 1 .2-2.N.2 блоков 2 приоритетных прерываний группы, устанавливаются в состояние логической 1 D-триггеры 30, на D- входы которых подан уровень логической 1. Таким образом, на входы 1.1-KN группового блока приоритетных прерываний поступают комбинации групповых запросов на прерывание, которые воспринимаются приоритетным шифратором 31, на выходе которого появляется код запроса на прерывание наиболее приоритетного блока из блоков приори тетных прерываний,, требующих обслуживания в данный момент Этот код лосту5162

пает на первую группу информационных входов схемы 33 сравнения, где сравнивается с информацией на выходе регистра 32 текущего приоритета, выходы которого подключены к второй группе входов схемы 33 сравнения. Так как в исходном состоянии регистр 32 обнулен, на выходе схемы 33 сравнения появляется сигнал логической 1, который поступает на вход элемента И 35, на другой вход которого поступает сигнал логической 1, свидетельствующий о наличии запросов на прерывание По синхроимпульсу, поступающему с соответствующего входа устройства на вход 1.2 блока 1, установится D-триггер 34 вследствие того, что на его D-вход подан уровень логической Таким образом, на выходе 1.5 блока 1 устанавливается сигнал логической 1, свидетельствующий о запросе на прерывание, имеющем больший приоритет в блоке приоритетного прерывания, имеющем, в свою очередь, больший приоритет в данный момент вре менИо По переднему фронту импульса на выходе D-триггера 34 в регистр 32 текущего приоритета записывается код приоритета на данный момент времени, который поступает на выходы 1.6 блока 1 о

Следовательно, на выходе 25 устройства устанавливается сигнал логической 1, а на адресных входах мультиплексора 6 - код блока 2 приоритетных прерываний группы, запрос на обслулмвание которого принят в данный момент времени. Сигнал на выходе 25 /устройства воспринимается микропроцессором в последнем такте последнего цикла текущей команды некоторой фоновой программы, и он перехолит в цикл обработки прерывания. При этом сбрасывается внутренний триггер прерывания микропроцессора и с входа 18 разрешения прерывания устройства снимается сигнал логической 1, вследствие чего на входы t.3 группового блока 1 приоритетных прерываний и входы 2.1.1 блоков 2 приоритетных прерываний группы подается сигнал логической 1 с выхода элемента ИЛИ 12. Триггеры 30, 34 запроса прерывания обнуляются и удерживаются в нулевом состоянии. Прерывания запрещены По сигналам на входе 21 приема устройства (уровень логической 1 на котором свидетельствует о том, что

0306

микропроцессор находится в состоянии ввода информации с шины данных) и входе 22 подтверждения прерывания (уровень логической 1 на котором свидетельствует о том, что микропроцессор находится в цикле обработки прерывания) происходит установка триггера 9 в состояние логической

0 1 и подается разрешающий сигнал

на вход, управления шинного формирователя 7, выходы которого подключаются к выходам данных устройства , В исходном положении выходы шинного форми5 рователя 7 находятся в высокоимпе- данском состоянии вследствие отсутствия активного уровня сигнала на его входе управления. Вхочл ттннгто формирователя 7 подключены к Р1гходам

0 мультиплексора 6, которые сигналами на выходах 1 „6 группового блока 1 приоритетных прерппаппп подключены к выходам блока 9 приоритетного прерывания группы, имеющего наивысшей

5 приоритет. Поэтому па выходах шинного формирователя 7 устанавливается информация, соответствующая коду запроса прерывания, имеющего наивысший приоритет в блоке 2 приоритетных преры0 ваний группы, имеюцсго в свою очередь наивысший приоритет среди ппугях, требующих обслуживания в данный момент. Сигнал логической 1 с выхода триггера 9 управляет мультиплексором

С 5, который в исходном положении при наличии на его входе адреса сигнала логического О передает на своп выходы и вторую группу адресных входов блока 4 памяти прерывания информацию

0 о состоянии части адресных входов 16 устройства Причем эта часть является подмножеством адресных входов 16 устройства о При поступлении на вход адреса первого мультиплексора 5 сиг-

5 нала логической 1 с выхода триггера 9 на выходы мультиплексора 5 передается информация с выходов 106 группового блока 1 приоритетных прерываний. Поэтому состояние адресных вхо0 Д°в блока 4 памяти прерываний определяется как состоянием части адресных входов 16 устройства, так и кодом блока 2 приоритетных прерываний, имеющего наивысший приоритет, запрос

е на прерывание от которого и выполняется в данный момент.

Сигнал логической 1 с выхода триггера 9 поступает также на нторой вход элемента И 14, первый вход которого подключен к второму входу 23 синхронизации устройства, на который подается синхросигнал, сопровождающий каждый цикл работы микропроцессора. Поэтому счетчик 8 по своему счетному входу начинает подсчет этих импульсов синхронизации.

Микропроцессор воспринимает вектор прерывания, поступающий с выхода шинного формирователя (разряды шинного формирователя 7, соответствующие разрядам 7, 6, 0, 1, 2 команды RST1Idddl11, подключены через ограничительный резистор к шине +5В источника питания), и адресует первую команду обработки прерывания, адрес которой зависит не только от вектора прерывания, но и от кода блока приоритетного прерывания, выста- вившего этот вектор прерывания. Поэтому из блока 4 памяти прерываний будет считана команда обработки прерывания „ соответствующая данному наиболее приоритетному запросу на пре- рывание, без дополнительной программной обработки. Эта команда считывается из блока 4 памяти прерываний после подачи активного уровня сигнал на вход 26 управления блока 4 памяти прерывания устройства, на который может быть подан, например, сигнал выборки кристалла с дешифратора микропроцессорной системы, и после подачи на вход 21 приема устройства сигнала логической 1, свидетельствующего о приеме информации по шине данных микропроцессора. При считывании команды выходы шинного формирователя 7 переводятся в высоко- импедансное состояние, так как с входа 22 подтвеждения прерывания сня активный уровень сигнала вследствие того, что микропроцессор выполняет цикл выборки команды из памяти по- еле цикла прерывания по значению команды рестарта.

Первая команда обработки прерывания представляет собой, например, команду безусловного перехода в об- ласть памяти, где записана программа обработки конкретного прерывания. После осуществления такого перехода счетчик 8 обнуляется и импульс с его выхода переполнения, поступающий на вход элемента ИЛИ 11, обнуляет триггер 9. Мультиплексор 5 отключается от выходов 1„6 группового блока 1 приоритетных прерываний и вновь подключается к части адресных линий адресных входов 16 устройства, что представляет возможность его адресации по адресным линиям 16 при выполнении, например, программы прерывания.

Выполняя программу обработки конкретного прерывания, микропроцессор обязательно осуществляет операции записи в стек содержимого регистров общего назначения и состояния, а затем разрешает прерывания специальной командой, что обеспечивает возможность многоуровневых прерываний,, Если после выполнения этих операций поступил запрос на обслуживание с блока 2 приоритетных прерываний, имеющего больший приоритет, чем тот, чей запрос обслуживается, вновь по импульсу синхронизации, поступающему с входа 20 устройства на вход 1.2 группового блока 1 приоритетных прерываний, установится D-триггер 34 Это произойдет потому, что после программного разрешения прерываний на входе 18 устройства вновь будет присутствовать сигнал логической 1, что снимет активный уровень сигнала с входов обнуления 1„ЗВ- триггера 34 и 2„1„1-20N ID-триггеров 30„ Установится D-триггер 30 в блоке приоритетных прерываний, имеющем больший приоритет, что вызовет изменение кода на выходе приоритетного шифратора 31, и, так как этот код будет больше кода, записанного в регистре 32, то вновь появится сигнал логической 1 на выходе схемы 33 сравнения.

I

Таким образом, произойдет очеред1- ное прерывание программы независимо от степени завершения предыдущей.

Предлагаемое устройство предусматривает хранение запросов на прерывание в триггерах-флажках устройств, вызывающих прерывание по входам 27.1- 27.N. Эти флажки остаются установленными до завершения программы обработки прерывания от данного устройства и обнуляются микропроцессором при помощи технических средств данного внешнего устройства, например портов вывода с адресами, соответствующими внешним устройствам. Выходные сигналы дешифраторов этих портов вывода активизируют входы обнуления триг- г ер ов-фл ажк о в„

По завершении программы обработки прерывания микропроцессор обнуляет флажок устройства, вызвавшего прерывание при помощи технических средств принадлежащих данному внешнему уст- ройству5 что приводит к снятию запроса на прерывание с соответствующих входов 27.1-27.N.

Микропроцессор обращается к дешифратору 3 так же, как к устройству вывода, используя вторые адресные входы устройства 15, которые могут быть совмещены с первыми адресными входами 16 устройства, и вход 24, в результате чего происходит появление сигнала логической 1 на выходе дешифратора 3. При этом сигнал логической 1 поступает на первые входы элемента ИЛИ 10, ас его выхода - на вход 1 4 группового блока 1 приоритетных прерываний, что приводит к обнулению регистра 32„ Групповой бпо 1 приоритетных прерывании готов воспринимать следующий по приоритету запрос на прерывание . Перед выполнением перечисленных операций обнуления флажков и регистра 32 текущего приоритета необходимо программно запретить прерывания, после чего происходит возврат из подпрограммы,

В случае прерывания программы обработки прерывания запросом на прерывание большего приоритета после завершения обработки запроса большего приоритета обработка запроса на прерывание предыдущего приоритета начнется вновь с первой команды программы обработки прерывания, если за это время не поступили запросы на прерывания большего приоритета, Если же повторное выполнение прерывани программы нежелательно, тогда в данной программе не предусматривается команда разрешения прерывания до окончания программы.

Таким образом, предлагаемое устроство обеспечивает идентификацию адреса первой команды отдельного запроса на прерывание в режиме, векторных прерываний с использованием рестарта микропроцессора в цикле прерывания без дополнительной программной обработки.

Рассмотрим пример конкретной реализации предлагаемого устройства для работы в составе микропроцессорной системы на основе микропроцессора 580 для 14 уровней прерывания.

10

15

21030ю

Используем два блока 2.1 и 2,2 приоритетных прерываний с приоритетными шифраторами 31, 28 на 7 входов. Разрядность сигналов регистра 32 logj. Ј 30 Выходы блоков 2.1 и 252 приоритетных прерываний подключены к первому 1.1.1 и второму 1.1.2 входам группового блока 1 приоритетных прерываний. На остальные входы подадим сигналы логического О.

Команда рестарта (RST) микропроцессора 580 имеет вид 11ddd111Ј„ Тогда 14 уровням прерывания будут соответствовать следующие векторы прерывания :

OlOg

О 2 Од

0308

04 Ое

050g

06 0 g

0708

Таким образом, один вектор прерывания соответствует двум уровням прерывания Для идентификации запроса на прерывание по одному вектору прерывания, который определяет адрес первой команды обработки прерывания, необходимо было бы предусмотреть команды ввода информации с выходов 1,6 группового блока приоритетных прерываний, которая кодирует номер блока приоритетных прерываний из блоков 2.1-2.2, и по этой информации определить адрес первой команды программы обработки конкретного из двух прерывании ,

20

25

30

35

В предлагаемом устройстве код на выходе 1,6 блока приоритетного прерывания 001 Ј кодирует запросы на прерывание 1-7, а код 010 - запросы 8-14. Таким образом, на первый вход мультиплексора 5 подключается шестой разряд шлны адреса микропроцессора, а на его второй вход - второй разряд кода Кб, и по сигналу логической 1 с выхода триггера 9 состояние вторых адресных входов блока 4 памяти прерываний будет определяться вторым разрядом кода 1i6 блока приоритетного прерывания. Тогда в блоке 4 памяти прерываний начальные команды обработки прерываний необходимо разместить по следующим адресам (допустим, разрядность адресных линий блока памяти равна 8):

010|- первая команда обработки

прерывания

и„

и п

1

П. || 1

.. II

7 8 9

10 11 12 13 14

020$-- -2

0308-- -3

0408-ч

0508-- -5 06 08- 07081108120в130в-- 140815081608-

1708После перехода микропроцессора в цикл прерывания блок 4 памяти прерываний будет адресоваться как линиями шины адреса адресных входов 16 устройства, так и выходом 501 первого мультиплексора 5с По адресам 010g- 170g разместим команды-вызовы подпрограмм обслуживания прерываний 1-14, которые находятся вне блока 4 памяти прерываний. Поэтому после выполнения этих команд-вызовов необходимо сбросить триггер 9 для переключения первого мультиплексора 5 с тем, чтобы при выполнении подпрограмм обработки прерываний было возможно по адресным входам 16 адресовать блок 4 памяти прерываний. Поэтому коэффициент пересчета счетчика 8 должен быть равен количеству циклов (количеству синхроимпульсов на синхровыходе микропроцессора, подключенном к входу 23 устройства) записи в стек при выполнении команды RST (2 цикла) плюс количеству циклов выполнения команды CALL (вызов подпрограммы) 3„

Таким образом, коэффициент пересчета счетчика 8 равен 5, и после пятого импульса происходит переключение первого мультиплексора 5.

Допустим, поступили запросы на прерывание на первый и второй входы 27. 1 о 1-27.1.2 блока 2.1 приоритетных прерываний и на третий вход 27о203 блока 202 приоритетных прерываний Тогда на выходе 2.1.4 блока 2.1 приоритетных прерываний установится код запроса на прерывание 010is a на выходе 2.-2Р4 блока 2.2. приоритетных прерываний - код 011. Так как блок 2 ,.2 приоритетных прерываний имеет больший приоритет, чем блок 2.1, то в регистр 32 при запросе на прерывание будет записан кол

i 010 (второй блок). Поэтому после цикла прерывания по команде рестарта RST 110111112. будет выбрана команда из ячейки 130о, которая идентифицирует запрос приоритета 0113 из блока приоритетных прерываний, имеющего приоритет 0102 без дополнительной программы поиска номера бло- JQ ка, требующего обслуживания,,

Формула изобретения

10 Устройство прерываний микро.с процессорной системы, содержащее групповой блок приоритетных прерываний, группу блоков приоритетных прерываний и дешифратор, причем информационные входы блоков приоритет.,„ ных прерываний образуют группу информационных входов устройства, входы синхронизации группового блока приоритетных прерываний и блоков приоритетных прерываний группы объе25 динены и являются первым входом синхронизации устройства, входы дешифратора являются первой группой адресных входов устройства, отличающееся тем, что, с целью

OQ повышения быстродействия обработки прерываний, в устройство введены блок памяти прерываний, первый и второй мультиплексоры, шинный формирователь, счетчик, триггер, первый, второй и третий элементы ИЛИ, пер вый и второй элементы И, причем информационные выходы блоков приоритетных прерываний группы подключены к управляющим входам второго мультиплексора, адресные входы которого подключены к информационным выходам группового блока приоритетных прерываний, выходы которого подключены к информационным входам шинного формирователя, выход шинного формирователя является информационным выходом устройства, выходы запросов прерывания блоков приоритетных прерываний группы подключены к информационным входам группового блока приоритетных

50 прерываний, выход запроса прерывания группового блока приоритетных прерываний является выходом запросов прерывания устройства, первая группа адресных входов блока памяти прерываний

55 и первая группа информационных входов

первого мультиплексора являются соот- ветственно первой и второй подгруппами группы адресных входов устрой40

45

13

ства, вторая группа информационных .входов первого мультиплексора подключена к группе информационных выходов группового блока приоритетных прерываний, а группа выходов первого мультиплексора подключена к второй группе адресных входов блока памяти прерываний, первый вход разрешения блока памяти прерываний является входом приема устройства, а второй вход разрешения блока памяти прерываний является входом управления чтением устройства, выходы которого являются информационными выходами устройства, выход стробирования дешифратора является входом записи устройства, выход дешифратора подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к первым входам второго и третьего элементов ИЛИ, являясь входом сброса устройства, выход первого элемента ИЛИ подключен к второму вхо ду сброса группового блока приоритетных прерываний, первый БХОД сброса которого подключен к выходу третьего элемента ИЛИ и к входам сброса блоков приоритетных прерываний группы, второй вход третьего элемента ИЛИ яв- ляется входом разрешения прорывания устройства, первый и второй входы первого элемента И являются соответственно входами приема и подтверждения прерывания устройства, выход первого элемента И подключен к входу разрешения шинного формирователя и к входу установки триггера, выход которого подключен к адресному входу первого мультиплексора и к перлону входу второго элемента И, второй вход которого является вторым входом синхрони/за- ции устройства, а выход второго элемента И подключен к счетному входу счетчика, вход сброса которого подключен к-входу сброса устройства, а выход которого подключен к второму входу второго элемента ИЛИ, выход второго элемента ИЛИ подключен к вхо/ду сброса триггера.

2„ Устройство по п„ 1, отличающееся тем, что групповой блок приоритетных прерываний содержит приоритетный шифратор, регистр теку- щего приоритета, схему сравнения, D-триггер и элемент И, причем информационные входы приоритетного шифра-

1621030

14

0

5

0

5

0

0

5

тора являются информационными входами группового блока приоритетных прерываний, информационный РЫХОД приоритетного шифратора подключен к информационному входу регистра текущего приоритета и к первому входу схемы сравнения, выход регистра текущего приоритета подк-лючен к второму входу схемы сравнения и является информационным выходом группового блока приоритетных прерываний, выход схемы сравнения подключен к первому входу элемента И, второй вход которого подключен к сигнальному выходу приоритетного шифратора, третий вход элемента И является входом синхронизации группового блока приоритетных прерываний, выход элемента И подключен к входу синхронизации D-триггера, информационный вход которого подключен к шине логической единицы устройства, выход D-триггера является выходом запроса прерывания группового блока приоритетных прерываний и подключен к входу синхронизации регистра текущего приоритета, вход сброса D-триггера является первым входом сброса группового блока приоритетных прерываний, а вход сброса регистра текущего приоритета является вторым входом сброса группового блока приоритетных прерываний,

3, Устройство по пп. 1 и 2, отличающееся тем, что каждый блок приоритетных прерываний группы содержит приоритетный шифратор, D- триггер и элемент И, причем информационные входы приоритетного шифратора являются информационными входами блока приоритетных прерываний, информационные выходы приоритетного шифратора являются информационными выходами блока приоритетных прерываний, сигнальный выход приоритетного шифратора подключен к первому входу элемента И, второй вход которого является входом синхронизации блока приоритетных прерываний группы, а выход отемента И подключен к входу синхронизации D-триггера, информационный вход которого подключен к шине логической единицы устройства, выход Ь-триггсра является выходом запроса прерывания блока приоритетных прерываний группы, а вход сброса D- трнггера является входом сброса блока приоритетных прерываний группы,,

Фиг. 1.

х 27/7

282

27.12

« в

mi 2.1.2

28

28.1

21.1

2.Щ 0

2.7.3

29

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

Изобретение относится к микропроцессорной технике и предназначено для организации дисциплины приоритетных прерываний в микропроцессорных системах управляющих и вычислительных комплексов о Цель изобретения - повышение быстродействия обработки прерываний,, Устройство прерываний микропроцессорной системы содержит групповой блок щшоригетнчх прерываний, группу блоков приоритетных прерываний, дешифратор, блок памяти прерывании, первый ч второй мультиплексоры, шинный формирователь, счетчик, триггер, элементы П, ИТИ. Причем групповой блок приоритетных прерываний содержит приоритетным шифратор, регистр текущего приоритета, схему сравнения, D-триггср и элемент II, а каждый блок приоритетно прерываний содержит приоритетный ипчЬрч- тор, D-триггер и элемент И, Сочность изобретения состоит в повышении быстродействия устройства прерываний путем обеспечения идентификации отдельного запроса из произвольного числа приоритетных запросов на прерывание в цикле прерывания с использованием рестарта микропроцессора,, 2 ЗсП,. ф-лы, 3 ил о «

Фиг. 2

| Авторское свидетельство СССР W 1546979, кл„ G 06 F 9/46, 19850 Березенко А.И | |||

| и др | |||

| Микропроцессорные комплекты повышенного быстродействия,,- М.: Радио и связь, 1981, с 40-50„ |

Авторы

Даты

1991-01-15—Публикация

1988-08-23—Подача