Изобретение относится к автоматике и вычислительной технике и может найти применение в системах регистрации и обработки случайных сигналов, в частности может быть использовано для обработки данных, получаемых от координатометра.

Цель изобретения - повышение достоверности выводимой информации за счет запрета вьшода сбойных значений

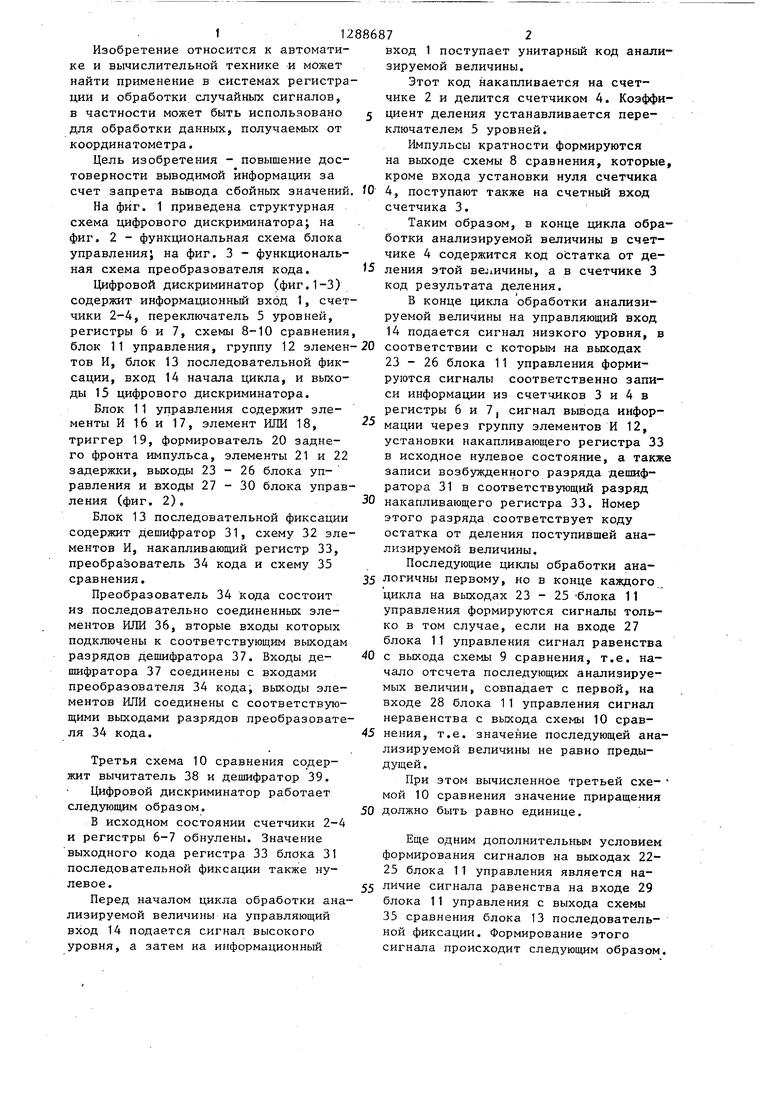

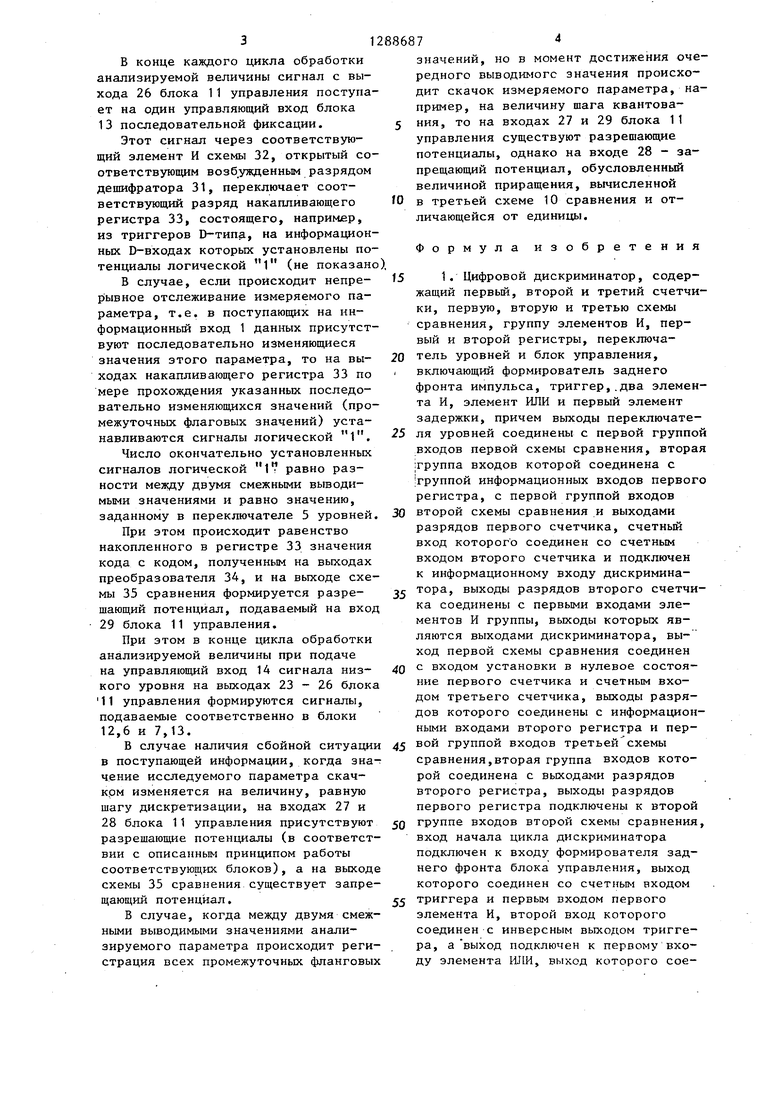

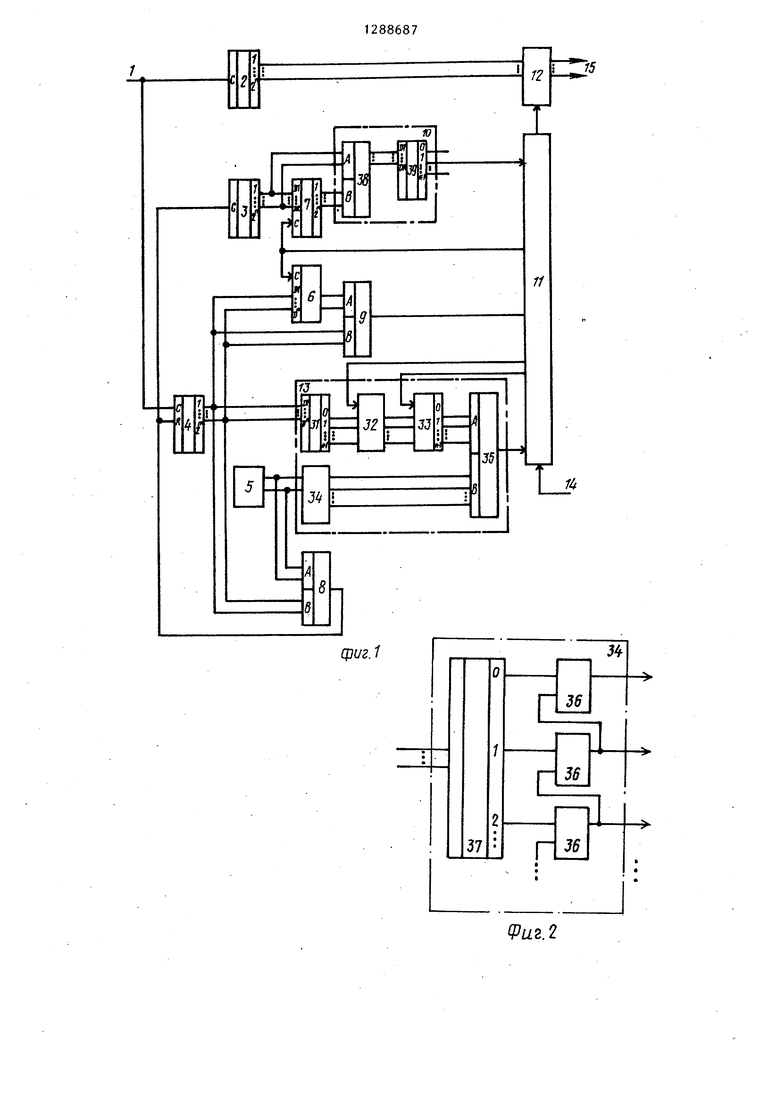

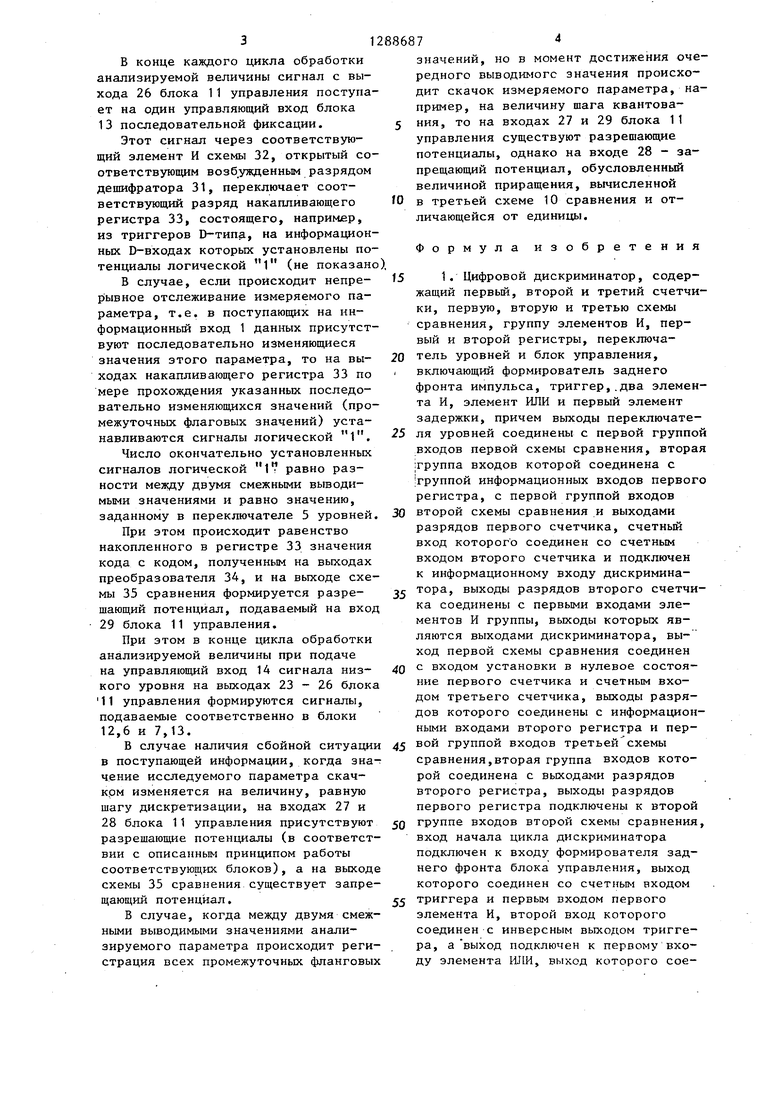

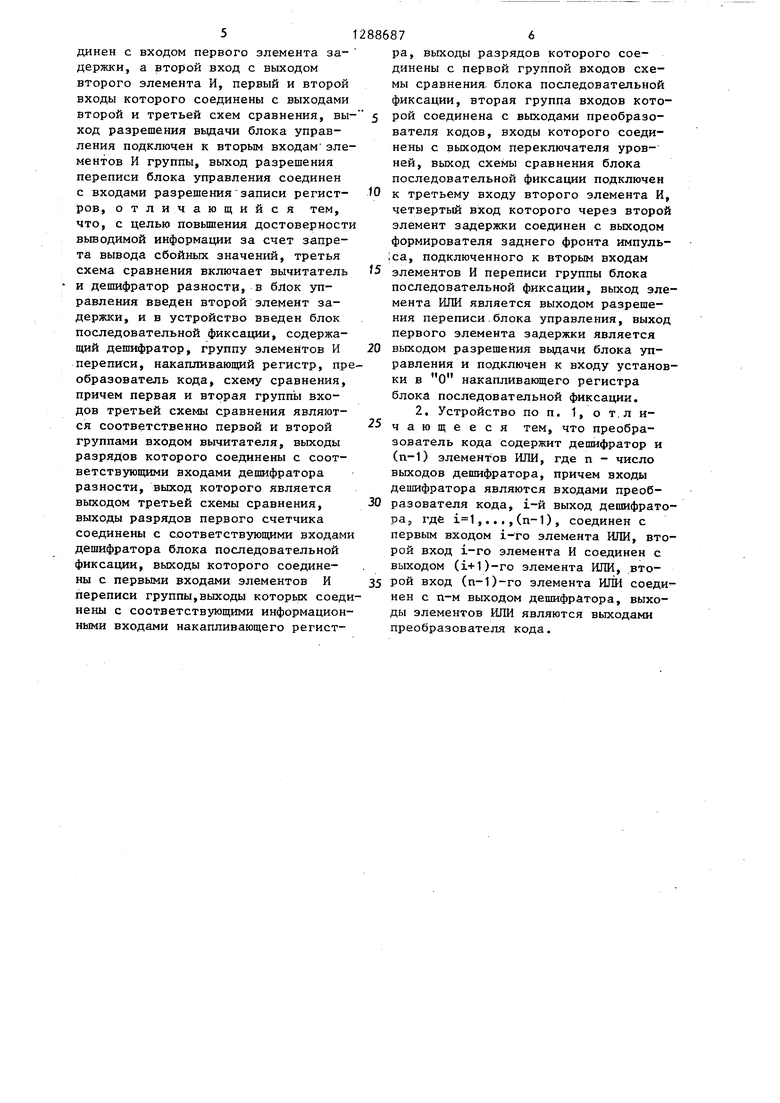

На фиг. 1 приведена структурная схема цифрового дискриминатора; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема преобразователя кода.

Цифровой дискриминатор (фиг.1-3) содержит информационный вход 1, счетчики 2-4, переключатель 5 уровней, регистры 6 и 7, схемы 8-10 сравнения блок 11 управления, группу 12 злемен тов И, блок 13 последовательной фиксации, вход 14 начала цикла, и выходы 15 цифрового дискриминатора.

Блок 11 управления содержит элементы И 16 и 17, элемент ИЛИ 18, триггер 19, формирователь 20 заднего фронта импульса, элементы 21 и 22 задержки, выходы 23 - 26 блока уп- равления и входы 27 - 30 блока управления (фиг. 2).

Блок 13 последовательной фиксации содержит дешифратор 31, схему 32 элементов И, накапливающий регистр 33, преобразователь 34 кода и схему 35 сравнения.

Преобразователь 34 кода состоит из последовательно соединенных зле- ментов ИЛИ 36, вторые входы которых подключены к соответствующим выходам разрядов дешифратора 37. Входы де- шифратора 37 соединены с входами преобразователя 34 кода, выходы элементов ИЛИ соединены с соответствующими выходами разрядов преобразователя 34 кода.

Третья схема 10 сравнения содержит вычитатель 38 и дешифратор 39.

Цифровой дискриминатор работает следующим образом.

В исходном состоянии счетчики 2-4 и регистры 6-7 обнулены. Значение выходного кода регистра 33 блока 31 последовательной фиксации также нулевое.

Перед началом цикла обработки анализируемой величины на управляющий вход 14 подается сигнал высокого уровня, а затем на информационный

соответствии

вход 1 поступает унитарнвй код анализируемой величины.

Этот код накапливается на счетчике 2 и делится счетчиком 4. Коэффициент деления устанавливается переключателем 5 уровней.

Импульсы кратности формируются на выходе схемы 8 сравнения, которые, кроме входа установки нуля счетчика 4, поступают также на счетный вход счетчика 3.

Таким образом, в конце цикла обработки анализируемой величины в счетчике 4 содержится код остатка от деления этой ве 1ичины, а в счетчике 3 код результата деления.

В конце цикла обработки анализируемой величины на управляющий вход 14 подается сигнал низкого уровня, в

с которым на выходах 23 - 26 блока 11 управления формируются сигналы соответственно записи информации из счетчиков 3 и 4 в регистры 6 и 7, сигнал вьшода информации через группу элементов И 12, установки накапливающего регистра 33 в исходное нулевое состояние, а также записи возбутвденного разряда дешифратора 31 в соответствующий разряд накапливающего регистра 33. Номер этого разряда соответствует коду остатка от деления поступившей анализируемой величины.

Последующие циклы обработки ана- логичны первому, но в конце каждого цикла на выходах 23 - 25 блока 11 управления формируются сигналы толь

0 5

0

5

ко в том случае, если на входе 27 блока 11 управления сигнал равенства с выхода схемы 9 сравнения, т.е. начало отсчета последующих анализируемых величин, совпадает с первой, на входе 28 блока 11 управления сигнал неравенства с вькода схемы 10 сравнения, т.е. значение последующей анализируемой величины не равно предыдущей.

При этом вычисленное третьей схе- мой 10 сравнения значение приращения должно быть равно единице.

Еще одним дополнительным условием формирования сигналов на выходах 22- 25 блока 11 управления является наличие сигнала равенства на входе 29 блока 11 управления с выхода схемы 35 сравнения блока 13 последовательной фиксации. Формирование этого сигнала происходит следующим образом.

Б конце каждого цикла обработки анализируемой величины сигнал с выхода 26 блока 11 управления поступает на один управляющий вход блока 13 последовательной фиксации.

Этот сигнал через соответствующий элемент И схемы 32, открытый соответствующим возб ужденным разрядом дешифратора 31, переключает соответствующий разряд накапливающего регистра 33, состоящего, например, из триггеров D-типа., на информационных D-входах которых установлены потенциалы логической 1 (не показано),

В случае, если происходит непрерывное отслеживание измеряемого параметра, т.е. в поступающих на информационный вход 1 данных присутствуют последовательно изменяющиеся значения зтого параметра, то на выходах накапливающего регистра 33 по мере прохождения указанных последовательно изменяющихся значений (промежуточных флаговых значений) устанавливаются сигналы логической 1.

Число окончательно установленных сигналов логической l7 равно разности между двумя смежными выводимыми значениями и равно значению, заданному в переключателе 5 уровней.

При этом происходит равенство накопленного в регистре 33 значения кода с кодом, полученным на выходах преобразователя 34, и на выходе схемы 35 сравнения формируется разрешающий потенциал, подаваемый на вход 29 блока 11 управления.

При этом в конце цикла обработки анализируемой величины при подаче на управляющий вход 14 сигнала низкого уровня на выходах 23 - 26 блока 11 управления формируются сигналы, подаваемые соответственно в блоки 12,6 и 7,13.

значений, но в момент достижения редного выводш огс значения прои дит скачок измеряемого параметра пример, на величину шага квантов

5 ния, то на входах 27 и 29 блока управления существуют разрешающи потенциалы, однако на входе 28 - прещающий потенциал, обусловленны величиной приращения, вычисленно

/О в третьей схеме 10 сравнения и о личающейся от единицы.

Формула изобретен

f5

20

1. Цифровой дискриминатор, сод жащий первый, второй и третий сче ки, первую, вторую и третью схемы сравнения, группу элементов И, пе вый и второй регистры, переключатель уровней и блок управления,

, включающий формирователь заднего

фронта импульса, триггер,.два эле та И, элемент ИЛИ и первый элемен задержки, причем выходы переключ

25 ля уровней соединены с первой гру входов первой схемы сравнения, вт |группа входов которой соединена с |группой информационных входов пер регистра, с первой группой входов второй схемы сравнения и выходами разрядов первого счетчика, счетны вход которого соединен со счетным входом второго счетчика и подключ к информационному входу дискримин тора, выходы разрядов второго сче ка соединены с первыми входами эл ментов И группы, выходы которых я ляются выходами дискриминатора, в ход первой схемы сравнения соедин с входом установки в нулевое сост ние первого счетчика и счетным вх дом третьего счетчика, выходы раз дов которого соединены с информац ными входами второго регистра и п

30

35

40

В случае наличия сбойной ситуации 45 ° группой входов третьей схемы

в поступающей информации, когда значение исследуемого параметра скач- крм изменяется на величину, равную шагу дискретизации, на входах 27 и 28 блока 11 управления присутствуют разрешающие потенциалы (в соответствии с описанным принципом работы соответствующих блоков), а на выходе схемы 35 сравнения существует запрещающий потенциал.

В случае, когда между двумя смежными выводимыми значениями анализируемого параметра происходит регистрация всех промежуточных фланговых

значений, но в момент достижения очередного выводш огс значения происходит скачок измеряемого параметра, например, на величину шага квантования, то на входах 27 и 29 блока 11 управления существуют разрешающие потенциалы, однако на входе 28 - запрещающий потенциал, обусловленный величиной приращения, вычисленной

в третьей схеме 10 сравнения и отличающейся от единицы.

Формула изобретения

1. Цифровой дискриминатор, содержащий первый, второй и третий счетчики, первую, вторую и третью схемы сравнения, группу элементов И, первый и второй регистры, переключатель уровней и блок управления,

включающий формирователь заднего

фронта импульса, триггер,.два элемента И, элемент ИЛИ и первый элемент задержки, причем выходы переключателя уровней соединены с первой группой входов первой схемы сравнения, вторая |группа входов которой соединена с |группой информационных входов первого регистра, с первой группой входов второй схемы сравнения и выходами разрядов первого счетчика, счетный вход которого соединен со счетным входом второго счетчика и подключен к информационному входу дискриминатора, выходы разрядов второго счетчика соединены с первыми входами элементов И группы, выходы которых являются выходами дискриминатора, выход первой схемы сравнения соединен с входом установки в нулевое состояние первого счетчика и счетным входом третьего счетчика, выходы разрядов которого соединены с информационными входами второго регистра и пер

сравнения,вторая группа входов которой соединена с выходами разрядов второго регистра, выходы разрядов первого регистра подключены к второй

РУПпе входов второй схемы сравнения, вход начала цикла дискриминатора подключен к входу формирователя заднего фронта блока управления, выход которого соединен со счетным входом

триггера и первым входом первого элемента И, второй вход которого соединен с инверсным выходом триггера, а выход подключен к первому входу элемента ИЛИ, выход которого соединен с входом первого элемента задержки, а второй вход с выходом второго элемента И, первый и второй входы которого соединены с выходами второй и третьей схем сравнения, выход разрешения вьщачи блока управления подключен к вторым входам элементов И группы, выход разрешения переписи блока управления соединен с входами разрешения записи регистров, отличающийся тем, что, с целью повьшгения достоверности вьюодимой информации за счет запрета вывода сбойных значений, третья схема сравнения включает вычитатель и дешифратор разности, в блок управления введен второй элемент задержки, и в устройство введен блок последовательной фиксации, содержащий дешифратор, группу элементов И переписи, накапливаюш;ий регистр, преобразователь кода, схему сравнения, причем первая и вторая группы входов третьей схемы сравнения являются соответственно первой и второй группами входом вычитателя, выходы разрядов которого соединены с соответствующими входами дешифратора разности, выход которого является выходом третьей схемы сравнения, выходы разрядов первого счетчика соединены с соответствующими входами дешифратора блока последовательной фиксации, выходы которого соединены с первыми входами элементов И переписи группы,выходы которьк соединены с соответствующими информационными входами накапливающего регист

ра, выходы разрядов которого соединены с первой группой входов схемы сравнения, блока последовательной фиксации, вторая группа входов которой соединена с выходами преобразователя кодов, входы которого соединены с выходом переключателя уровней, выход схемы сравнения блока последовательной фиксации подключен к третьему входу второго элемента И, четвертый вход которого через второй элемент задержки соединен с выходом формирователя заднего фронта импуль- ica, подключенного к вторым входам элементов И переписи группы блока последовательной фиксации, выход элемента ИЛИ является выходом разрешения переписи.блока управления, выход первого элемента задержки является выходом разрешения выдачи блока управления и подключен к входу установки в о накапливающего регистра блока последовательной фиксации.

2, Устройство по п. 1, о т.л и- чающееся тем, что преобразователь кода содержит дешифратор и (п-1) элементов ИЛИ, где п - число выходов дешифратора, причем входы дешифратора являются входами преобразователя кода, i-й выход дешифратора , ГДЕ ,..,,(п-1), соединен с первым входом i-ro элемента ИЛИ, второй вход i-ro элемента И соединен с выходом (i+D-ro элемента ИЛИ, второй вход (n-l)-ro элемента ИЛИ соединен с п-м выходом дешифратора, выходы элементов ИЛИ являются выходами преобразователя кода.

фиг.

3

37

36

Фиг. 2

Составитель E. Иванова Редактор О. Головач Техред В.Кадар

Заказ 7809/47 Тираж 694Подписное

. ВНИИПИ Государствен ного комитета СССР

по делам изобретений и открытий 113035, 5:1осква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Vu.2.3

Корректор В. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для формирования информативных признаков при распознавании изображений | 1986 |

|

SU1361591A1 |

| Устройство для обработки и ввода информации | 1980 |

|

SU951286A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Амплитудный анализатор | 1988 |

|

SU1737273A1 |

Устройство относится к области автоматики и вычислительной техники и может найти применение в системах регистрации и обработки случайных сигналов, в частности может быть использовано для обработки данных, получаемых от координатометра. Цель изобретения - повышение достоверности выводимой информации за счет запрета вывода сбойных значений.Устройство содержит переключатель уровней, счетчики, регистры, схемы сравнения, блок управления, блок последовательной фиксации, включающий преобразователь кода, дешифратор, накапливакщий регистр, группу зле- ментов И, схему сравнения. Достоверность вьшодимой информации повышается за счет определения величины .приращения путем идентификации в поступающей информации сбойной ситуации и запрещения вьшода сбойного измеренного значения, соответствующего заданному уровню дискриминации. 1 з.п. ф-лы, 3 ил. W ю ас СХ) а 00

| Многоканальный цифровой дискриминатор | 1975 |

|

SU591854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1985-05-30—Подача