Устройство относится к автоматике и вычислительной технике и может найти применение в системах регистрации и обработки случайных сигналов, в частности, может быть использовано для обработки, данных, получаемых от координатографа. Известен многоканальный цифровой дискриминатор, содержащий блок счет чиков исследуемой величины, переклю чатели уровней и блоки .вращения)/ по числу уровней дискриминации,триггер ,и,блок совпадения ll. Иавестным дискриминатором можно дискриминировать анализируемую вели чину по ряду уровней дискриминации, но сам дискриминатор построен путем составления из одноканальных дискриминаторов. Такое решение требует большого объема оборудования, Наиболее близким к предложенному изобретению является цифровой дискр минатор, содержащий счетчик, переключатель уровней, первый и втйрой блоки сравнения, блок выдачи, блок памяти и блок управления, Информационный вход дискриминатора соединен со счетным входом счетчика, выходы разрядов которого соединены с информ ционными входами блока памяти и блока выдачи, с входами первой группы второго блока сравнения и с входами второй группы первого блока сравнения. Входы первой группы первого бло ка сравнения соединены с выходами переключателя уровней. Выходы блока памяти соединены с входами -второй Группы второго блока сравнения, Первый, второй и третий входы блока управления соединены соответственно с выходами первого и второго блоков сравнения и с управляющим входом , дискриминатора, а первый и второй вы ходы блока управления соединены софт ветственно с управляющими входами . блока памяти и блока выдачи. Выходы блока выдачи и первого блока сравнения являются выходами дискриминатора Блок управления цифрового дискриминатора содержит элемент И и элемент задержки, выход которого соединен с первым выходом блока, первый, второй и третий входы которого соединены со входами элемента И, выход которого соединен со вторым выходом блока 2 , Недостаток известного цифрового дискриминатора заключается в его низких функциональных возможностях, т.е, им можно Дискриминировать анализируемую величину только по уровням дискриминации с шагом 2, где п - целое число. Цель изобретения - расширение функциональных возможностей цифрового дискриминатора за счет обеспвп чения анализа данных с шагом п,где п - целое число, Поставленная цель достигается тем, что в цифровой дискриминатор, содержащий первый счетчик, переключателей уровней, первую и вторую схемы сравнения, группу элементов И, блок управления и первый регистр, причем входы первой группы первой схемы сравнения соединены с выходами переключателя уровней,информационные входы первого регистра соединены с входами первой группы второй схемы сравнения и с входами второй 1руппы первой схемы сравнения, выходы первого регистра подключены к входам второй группы второй схемы сравнения, выходы первого счетчика соединены с информационными входами элементов И группы, пёрвьтй и второй выходы блока управления подключены к управляющим входам первого регистра и элементов И группы соответственно, первый и второй входы блока управления соединены с выходом второй схемы сравнения и с управляющим входом дискриминатора соответственно, информационный вход дискриминатора подключен к информационному входу первого счетчика, выходы элементов И группы соединены с выходами дискриминатора, введены второй и третий счетчики,вто рой регистр и третья схема сравнения, причем выходы второго счетчика соединены с информационными входами второго регистра и с входами первой группы третьей схемы сравнения, выходы второго регистра подключены к входам второй группы третьей схемы сравнения, выход которой соединен со вторым входом блока управления, первый выход которого подк.гпочен к управляющему входу второго регистра,, выход первой схемы ссавнения соединен с информационным входом второго счетчика и с входом установки в нулевое состояние третьего счетчика, выходы которого подключены к информационным входам первого регистра,информационный вход дискриминатора подключен к счетному входу третьего счетчика, кроме того, блок управления содержит элементы И, ИЛИ, триггер, формироватчэль, элемент задержки, причем первый и второй входы блока управления соединены .с первым и вторым входами соответственно первого элемента И, выход которого подключен к первому xoду элемента ИЛИ, выход котюрого через элемент .задержки соединен с первым выходом блока управления, третий вход блока управления через формирователь соединен с третьим входом первого элемента И, с счетным входом триггера и с первым входом второго элемента И, выход которого подключен к второму входу элемента ИЛИ, выход которого соединен с в сорым выходом блока управления, инверсный выход триггера подключен к вто:рому входу второго элемвнтэ И.

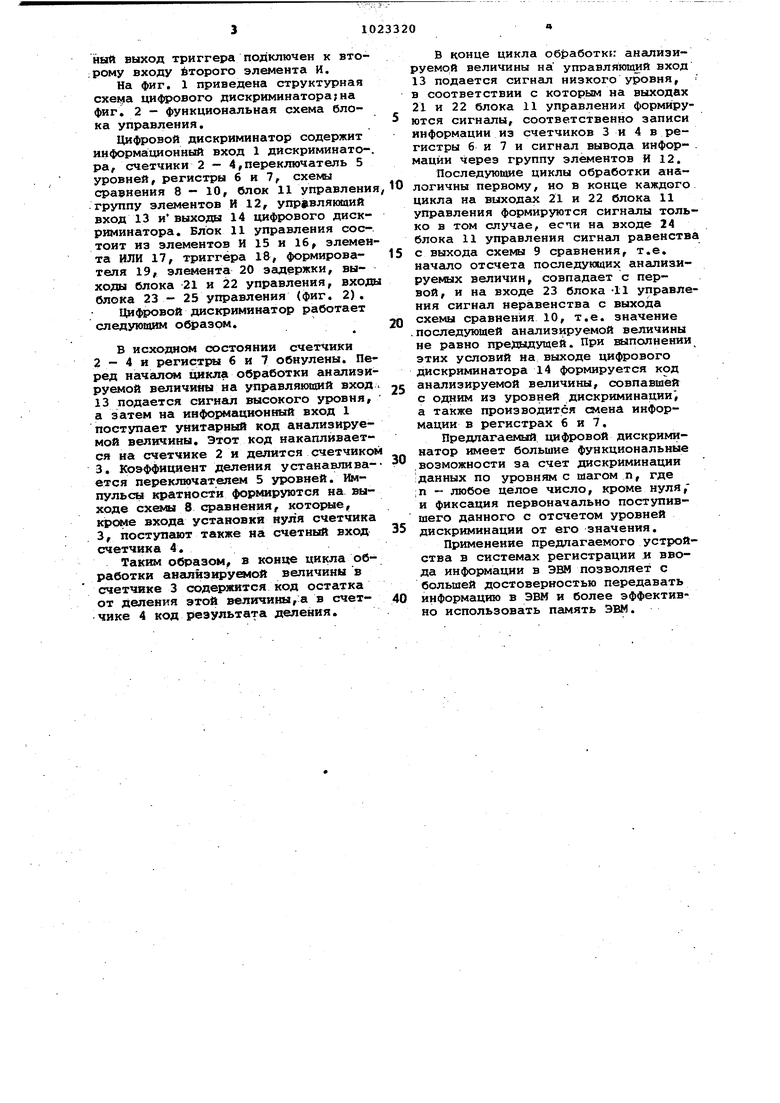

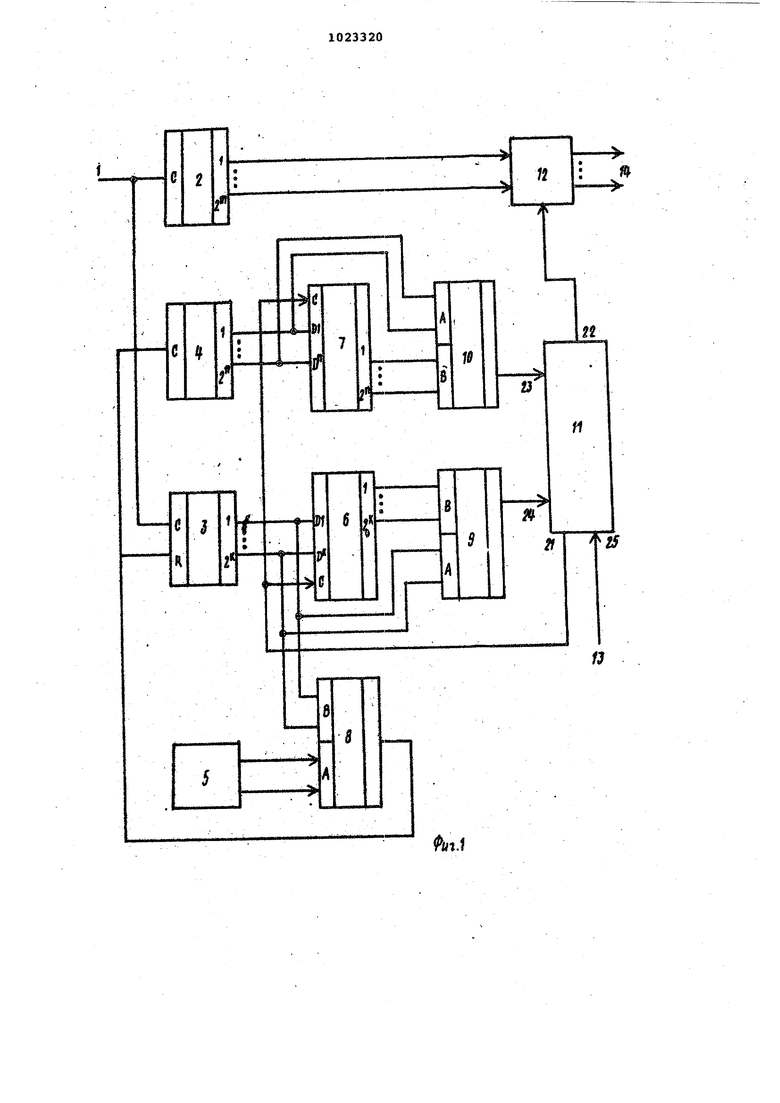

На фиг. 1 приведена структурная цифрового дискриминатора;на фиг, 2 - функциональная схема блока управления.

Цифровой дискриминатор содержит информационный вход 1 дискриминатора, счетчики 2 - 4,переключатель 5 уровней, регистры 6 и 7, схемы сравнения 8 - 10, блок 11 управлени группу элементов И 12, управляющий вход 13 ивыходы 14 цифрового дискриминатора. Блок 11 управления состоит из элементов И 15 и 16 элемента ИЛИ 17, триггера 18, формирователя 19, элемента 20 эадержки, выходы блока 21 и 22 управления, вход блока 23 - 25 управления (фиг. 2).

Цифровой дискриминатор работает следующим образе.

В исходном состоянии счетчики 2 - 4 и регистры 6 и 7 обнулены. Перед начешсял цикла обработки анализируемой величипы на управляющий вход 13 подается сигнгш высокого уровня, а затем на информационный вход 1 поступает унитарный код анализируемой величины. Этот код накапливается на счетчике 2 и делится счетчико 3, Коэффициент деления устанавливается переключателем 5 уровней. №«пульсы кратности формируются на выходе схемы 8 сравнения, , крсяле входа установки нуля счетчика 3, поступают также на счетный вход счетчика 4.

Таким образом, в конце цикла обработки анализируемой величины в счетчике 3 содержится код остатка от деления этой величины,а в счетчике 4 код результата деления.

В конце цикла обработки анализируемой величины на управляющий вход 13 подается сигнал низкого уровня, в соответствии с которым на выходах 21 и 22 блока 11 управления формируются сигналы, соответственно записи информации из счетчиков 3 и 4 в регистры 6 и 7 и сигнал вывода информацйи через группу элементов И 12.

Последующие циклы обработки аналогичны первому, но в конце каждого цикла на выходах 21 и 22 блока 11 управления формируются сНгналы только в том случае, еепи на входе 24 блока 11 управления сигнал равенств с выхода схемы 9 сравнения, т.е. начало отсчета последующих анализируемых величин, совпадает с первой, н на входе 23 блока -11 управления сигнал неравенства с выхода схемы сравнения 10, т.е. значение .последующей анализируемой величины не равно предыдущей. При наполнении этих условий на, выходе цифрового дискриминатора 14 формируется код ансшизируемой величины, совпавщей с одним из уровней дискриминации , а также производится смена информации в регистрах 6 и 7.

Предлагаемый цифровой дискриминатор имеет большие функциональные .возможности за счет дискриминации Сданных по уровням с шагом п, где ; п - любое целое число, кроме нуля, и фиксация первоначально поступившего данного с отсчетом уровней дискриминации от его значения.

Применение предлагаемого устройства в системах регистрации .и ввода информации в ЭВМ позволяет с большей достоверностью передавать информацию в ЭВМ и более эффективно использовать память ЭВМ.

IS

18

ts

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| Цифровой дискриминатор | 1984 |

|

SU1259244A1 |

| Цифровой дискриминатор | 1983 |

|

SU1170447A1 |

| Цифровой дискриминатор | 1985 |

|

SU1288687A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128248A1 |

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| Цифровой дискриминатор | 1981 |

|

SU1003069A1 |

| Цифровой дискриминатор | 1983 |

|

SU1151951A1 |

| Цифровой дискриминатор | 1979 |

|

SU881732A1 |

| Цифровой дискриминатор | 1981 |

|

SU951292A1 |

1. ЦИФ рОВОЙ ДИСКРИМИНАТОР, содержащий первый:счетчик, переключател уровней, первую и вторую схе,мы сравнения, группу элементов И, блок упр вления и первый регистр, причем входая первой гфуппы первой схемы сравнения соединены с выходами переключателя уровней, информационные входы первого регистра соединены с входами первой группы второй схемы сравнения и-е- входами второй группы первой сЬсеМй сравнения, выходы первого регистра подключены к входам второй группы второй схемы, сравнения, выхода первого счетчика соединены с информационными входами элементов И группы, первый и второй выходы блока упргцвления подключены к управлякщим входам первого регистра и элет ентов И группы соответственно, первый и второй входы блока управления соединены с выходом второй схемы сравнения и с управляющим входом дискриминатора соответственно, информационный вход дискриминатора подключен к информационному входу первого «зчетчйка, выходы элементов И группы соединены с выходами дискриминатора, о т л ичающий с я тем, с целью расширения функциональных возможностей дискриминатора за счет обес-печения анализа дацных с шагом п, где п - целое число,в него введены второй и третий счётчики, второй регистр и третья схема сравнения,причем выходы второго счетчика соединены с инфо 1ационнымйвходами второго регистра и с входами первой группы третьей схемы сравнения, выходы второго регистра подключены к входам второй Группы третьей схемы сравнения, выход которой соединен с вторым входом блока управления, первый выход которого подключен к управляющему входу второго регистра, выход первой схемы сравнения соединен с информационным входом второго счетчика и с входом установки в нулевое состояние третьего счетчика, выходы которо го подключены к информационным вхо, первого регистра, информационный в дискриминатора подключен к счетнсялу входу третьего счетчика. 2. даскриминатор по п. 1, о т л ич а ю щ и и с я тем, что. в нем блок управления.содержит элементы И,ИЛИ, триггер, формирователь, элемент задержки, причем первый и второй входая блока управления соединены с первьаши вторьм входами соорветственНо пе во го элемен.та И, выход которого под кпючен к первсму входу элемента ИЛИ, выход которого через элемент задержки соединен с первым выходом блока управления, третий вход блока управления через формирователь соединен стретьим входом первого элемента И, оо счетным входом триггера и с первым входом второго элемента И, выход которого подключен к второму входу элемента ИЛИ, выход которого соединен с вторым выходом блока уп.равления, инверсный выход триггера подключен к второму входу второго .элемента И.

23

i$

17

20

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальный цифровой дискриминатор | 1975 |

|

SU591854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-06-15—Публикация

1981-07-21—Подача