и синхронизирующему входу второго триггера, вход установки в О которого соединен с выходом селектора импульсов по длительности и с первым входом входного элемента ИЛИ, выход которого подключен к счетным входам счетчиков, а второй Вход - к выходу входного элемента И, первьй вход которого соединен с прямым выходом «триггера, а второй вход - с выходом второго формирователя заднего фронта

импульса, в блок управления дополнительно введены третий формирователь заднего фронта импульса и элемент задержки, причем вход начала цикла обработки устройства через элемент задержки соединен с входом второго формирователя заднего фронта импульса и входом третьего формиров-ателя заднего фронта импульса, выход которого подключен к второму входу входного элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1984 |

|

SU1259244A1 |

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128248A1 |

| Цифровой дискриминатор | 1981 |

|

SU1003069A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Цифровой дискриминатор | 1983 |

|

SU1170447A1 |

| Цифровой дискриминатор | 1985 |

|

SU1288687A1 |

| Счетчик фотонов | 1986 |

|

SU1345065A1 |

| Цифровой дискриминатор | 1983 |

|

SU1151951A1 |

| Устройство для считывания графической информации | 1985 |

|

SU1372343A1 |

ЦИФРОВОЙ ДИСКРИМИНАТОР, содержащий первый и второй счетчики, первый и второй регистры, первый и второй элементы сравнения, переключатель уровней, блок вьщачи числа и блок управления, включающий формирователи переднего и заднего фронтов импульса, триггер, элементы ИЛИ-НЕ, И, ИЛИ, причем счетные входы счетчиков объединены, выходы разрядов первого счетчика соединены с установленными входами первого регистра, с пер-, вой группой входов первого элемента сравненияМ с информационными входами блока выдачи числа, выходы которого являются выходами устройства, выходы первого регистра соединены с второй группой входов первого элемента сравнения, инверсные выходы вто рого регистра соединены с установочными входами второго Летчика, выходы разрядов которого соединены с установочными входами второго регистра, с входами элемента ИЛИ-НЕ блока управления и с первой группой входов второго элемента сравнения, вторая группа входов которого подключена к выходам переключателя уровней,а выход - к входу установки в О второго счетчика, выход первого элемента сравнения соединен с первым входом первого элемента И блока управления, второй вход которого подклю.чен к выходу элемента ИЛИ-НЕ, а третий - к синхронизирующему входу триггера, к выходу второго формирователя заднего фронта импульса и кпервому входу второго элемента И, второй вход которого соединен с инверсным выходом триггера, а выход - с входом (Л записи второго регистра и с первым входом элемента ИЛИ, второй вход которого подключен к выходу первого .элемента.И и входу первого формирователя заднего фронта импульса, выход которого подключен к входу записи первого регистра, вход начала цикла обработки устройства соединен с входом формирователя переднего фронх та импульса, выход которого подклюК9 чен к входу управления записью втог рого счетчика, выход элемента ИЛИ соединен с управляющим входом блока выдачи числа, отлич ающе е с я тем, что, с целью повышения .помехоустойчивости цифрового дискриминатора путем запрета действия коротких импульсов помехи во время счета сигналов унитарного кода, в него введены селектор импульсов по длительности, второй триггер, входные элементы И, ИЛИ, причем информационный вход устройства подключен к входу . селектора импульсов по длительности

1

Изобретение относится к области информационно-измерительной и вычислительной техники и может найти применение в системах регистрации и обработки случайных сигналов, в частности может быть использовано дпя обработки данных, получаемых от координатографа.

Известен многоканальный цифровой дискриминатор, содержащий блок счетчиков исследуемой величины, переключатели уровней и блоки сравнения по числу уровней дискриминации, тригге- р|Ы и блок совпадения {. .

Это устройство может дискриминировать анализируемую величину по ряду уровней дискриминации, однако состоит из одноканальных дискриминаторов, что требует большого объема оборудования.

Наиболее близким к изобретению по технической сущности является известный цифровой дискриминатор, содержащий первьй и второй счетчики, первый и второй блоки памяти, первый и второй элементы сравнения, переключатель уровней, блок управления и блок выдачи, причем выходы разрядов 1. первого счетчика соединены с установочными входами первого блока памяти первой группой входов первого элемента сравнения и информационными входами блока вьщачи, выходо которого являются выходами устрриства, выходы первого блока памяти соединены с .второй группой входов первого элемента сравнения, выход которого соединен

с первым управляющим входом блока управления, второй управляющий вход которого является управляющим входом устройства, первый и второй выходы блока управления соединены соответственно с управляющими .входами первого блока памяти и блока выдачи, счетный вход первого счетчика соединен с информационным входом устройства и со счетным входом второго счетчика, выходы разрядов которого соединены с группой информационных входов блока управления, второй группой входов второго элемента сравнения и группой установочных входов второго регистра, инверсные вьпсоды разрядов которого соединены с установочными входами второго счетчика, третий и четвертый выходы блока управления соединены с управляющими входами второго блока памяти и второго счетчика соответственно, выходы переключателя уровней соединены с первой группой входов второго элемента сравнения, выход которого соединен с входом установки второго счетчика в нулевое состояние, блок управления цифрового дискриминатора содержит формирователь переднего фронта, первый и второй формирователи заднего фронта, триггер, первьй и второй элементы И, элемент ИЛИ, элемент ИЛИ-НЁ, причем группа информационных входов блока соединена с входами элемента ИЛИ-НЕ, выход которого соединен с входом первого элемента И, выход которого соединен с

3 1

входом элемента ИЛИ и с входом первого формирователя заднего фронта, выход которого является первым выходом блока, первый управляющий вход блока соединен с входом первого элемента И, второй управляющий вход блока соединен с.входами формирователя переднего фронта и второго формирователя заднего фронта, вьгход которого соединен с входом синхронизации триггера, входами первого и второго элементов И, нулевой выход триг гера соединен с входом второго элемента И, выход которого соединен с входом элемента ИЛИ, выход которого является вторым выходом блока, выход второго элемента И является третьим выходом блока, выход формирователя переднего фронта является четвертым выходом блока .

Недостатком известного цифрового дискриминатора является низкая функциональная надежность вследствие возможности нарушения заданных уровней дискриминации выводимых значений а также вывода квазиповторяющихся (отличающихся на единицу) значений в области уровня дискриминации, что наряду с нарушением функций дискриминатора приводит к избыточности выводимой информации.

Указанные сбои в работе дискриминатора возникают, когда первьй и вто рой счетчики дискриминаторов из-за . технологических разбросов параметров фиксируют различающиеся значе.ния анализируемой величины при наличии в поступающем унитарном коде уко роченного импульса, формируемого, например, при окончании тактирования временных интервалов.

При этом в области значений уровней дискриминации возникают ситуации когда второй счетчик, участвующий в формировании сигнала разрешения вывода дискриминируемых значений, дает такое разрешение, а первый счетчик, участвующий в формировании сигнала запрета вывода повторных значений, не вводит запрет и значение анализируемой величины, зафиксированное пер вым счетчиком, выводится.

Кроме того, низкая помехоустойчивость дискриминатора проявляется в том, что при воздействии коротких импульсов помехи на информационный вход устройства во время поступления унитарного кода происходит либо

28247

нарушение функций дискриминатора, а51алогичное рассмотренным сбоям, возникающим из-за технологических разбросов параметров счетчиков,

5 либо при засчитывании эти-х импульсов помехи обеими счетчиками возникает погрешность выводимых значений, при этом может быть запрещен вывод ряда значений анализируемой величи10 ны, лежащих в области заданных уровней дискриминации.

Целью изобретения является повышение помехоустойчивости цифрового дискриминатора путем запрета деист- :

15 ВИЯ коротких-импульсов помехи во

время счета сигналов унитарного кода, I

Поставленная цель достигается

тем, что в цифровой дискриминатор, содержй1щий первый и второй счетчики, первый и второй регистры, первый и второй элементы сравнения, переключатель уровней, блок выдачи числа и блок управления, включающий формирователи переднего и заднего фронтов

25 импульса, триггер, элементы ИЛИ-НЕ, И, ИЛИ, причем счетные входы счетчиков объединены, выходы разрядов первого счетчика соединены с установочными входами первого регистра, с пер вой группой входов первого элемента сравнения и с информационными входами блока вьщачи числа, выходы которого являются выходами устройства, выходы первого регистра соединены с второй

35 группой входов первого элемента сравнения, инверсные выходы второго регистра соединены с установочными входами второго счетчика, выходы разрядов которого соединены с уста40 новочными входами второго регистра, с входами элемента ИЛИ-НЕ блока управления и с первой группой входов второго элемента сравнения, вторая группа входов которого подключена к

5 выходам переключателя уровней, а

выход - к входу установки в О второго счетчика, выход первого элемента сравнения соединен с первым входом первого элемента И блока управления,

50 второй вход которого подключен к выходу элемента ИЛИ-НЕ, а третий - к синхронизирующему входу триггера, к выходу второго формирователя заднего фронта импульса и к первому входу .

55 второго элемента И, второй вход которого соединен с инверсным выходом триггера, а выход - с входом записи второго регистра и с первым входом 51 элемента ШШ, второй вход которого яодключен к выходу первого элемента И и входу первого формирователя задйего фронта импульса, выход которого подключен к входу записи первого регистра, вход начала цикла обработки устройства соединен с входом формирователя переднего фронта импульса, выход которого подключен к входу управления записью второго счетчика, выход элемента ИЛИ .соединен с управляющим входом блока выдачи числа, введены селектор импульсов по длительности, второй триггер, входные элементы И, ИЛИ, причем информационный вход устройства подключен к вход селектора импульсов по длительности и синхронизирующему входу второго триггера, вход установки в О которого соединен с выходом селектора импульсов по длительности и с первым входом входного элемента ИЛИ, выход которого подключец к счетным входам счетчиков, а второй вход - к выходу входного элемента И, первьй вход которого соединен с прямым выходом триггера, а второй вход - с выходом второго формирователя заднего фронта импульса, в блок управления дополнительно введены третий формирователь заднего фронта импульса и элемент задержки, причем вход начала цикла обработки устройства через элемент задержки соединен с входом второго формирователя заднего фронта импульса и входом третьего формирователя заднего импульса, выход которого подключен к второму входу входного элемента И.

Принцип действия предлагаемого устройства заключается в определении кратности анализируемой величины шагу уровней дискриминации путем деления этой величины на величину шага при условии запрета действия коротких импульсов помехи и фиксации укороченного последнего импульса унитарного кода.

Для отсчета уровней дискриминации от первоначально поступившей анализируемой величины остаток от деления ее запоминается, а затем вычитается из последующих значений анализируемых величин,

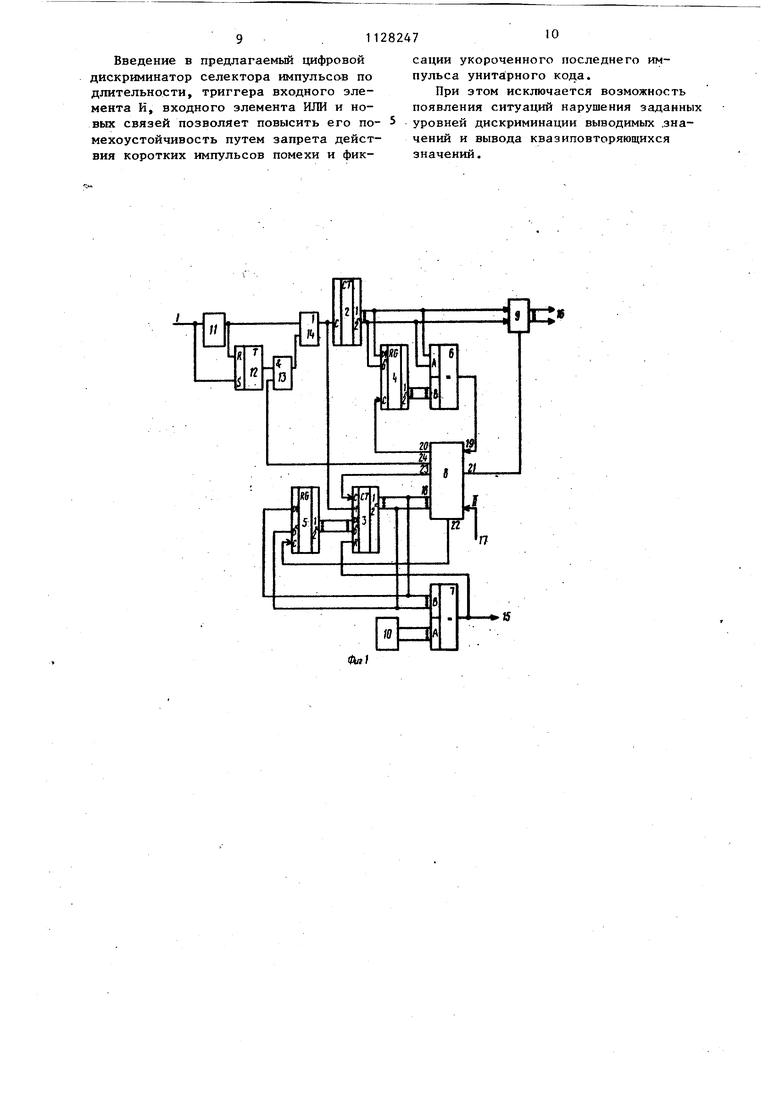

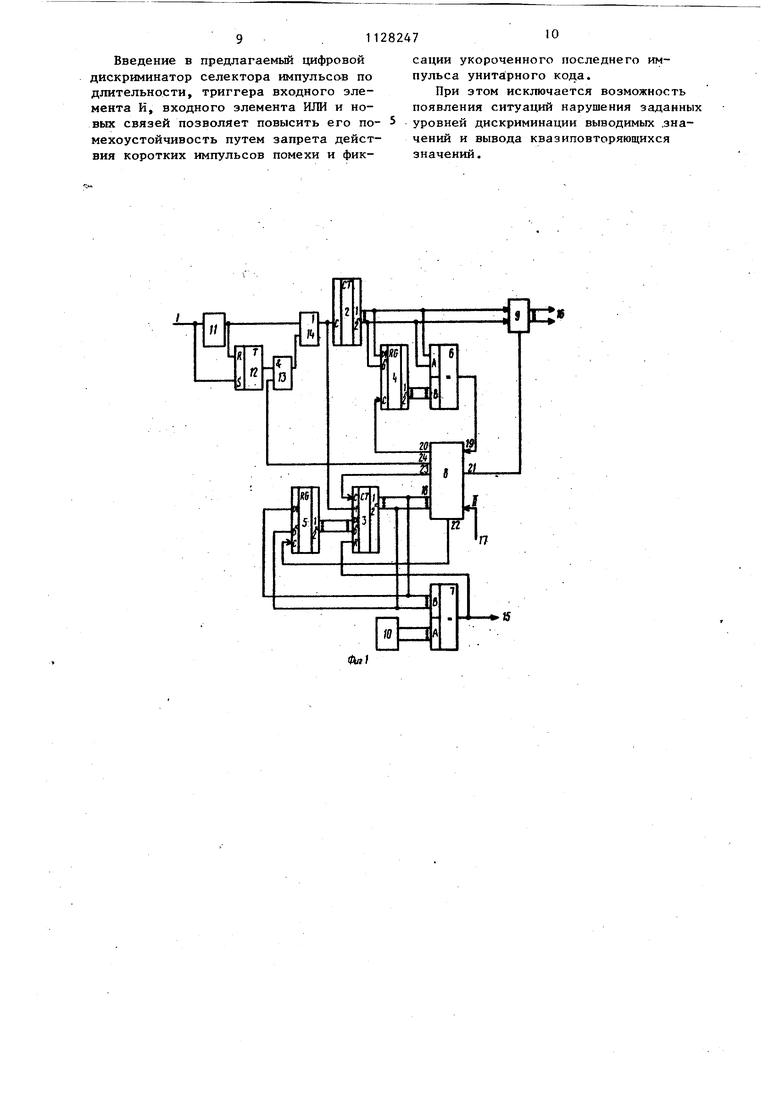

На фиг. 1 дана структурная схема цифрового дискриминатора; на фиг. 2 схема блока управления.

рователь 25 переднего фронта импульса, формирователи 26-28 заднего фронта импульса, триггер 29, элемент 30 задержки, элементы И 31 и 32, элемент ИЛИ 33, элемент ШШ-НЕ3

Цифровой дискриминатор работает следующим образом.

В исходном состоянии в триггер 12 счетчик 2 и регистры 4 и 5 .записаны нули.

Перед началом цикла обработки на управляющий вход 17 подается сигнал высокого уровня, в соответствии с которым на выходе 23 блока 8 управления формируется сигнал разрешения записи в счетчик 3 содержимого регистра 5, а затем на информационный вход 1 начинает поступать унитарный код анализируемой величины.

Этот код подается на вход селектора 11 импульсов по длительности.

Последний представляет собой устройство, которое пропускает на выход импульсы, длительность которых больше или равна заданной, и задерживает их на время заданной длительности, а импульсы меньшей длительности блокирует.

Заданная длительность селектора должна быть такой, чтобы не пропускать на выход импульсы помехи и короткие импульсы, но достаточной для.пропускания импульсов, обеспечивающих устойчивую работу счетчиков.

.Одна из возмож1 1Х реализаций такого селектора содержит ждущий мультивибратор нижнего порогового уровня, первый и второй ждущие мультивибраторы верхнего порогового уровня, первый и второй формирователи заднего фронта импульса, первый и второй элементы И, триггер. 7 Устройстбо содержит информационный вход 1, первый и второй счетчики 2 и 3, первый и второй регистры 4 и 5, первый и второй элементы 6 и 7 сравнения, блок 8 управления, блок 9 выдачи числа, переключатель 10 уровней, селектор 11 импульсов по длительности, триггер 12, входной элемент И 13, входной элемент ИЛИ 14, выходы 15 и 16. цифрового дискриминатора, управляющий вход 17 (начала цикла обработки) устройства, группа входов блока 18 управления, вход блока 19 управления, первый - пятый выходы 20-24 блока управления, формиИмпульсы с выхода селектора поступают на нулевой установочный вход триггера 12, на единичный установочный вход которого поступает входная последовательность импульсов унитарного кода. ,

Таким образом, триггер 12 любым входным импульсом устанавливается в единичное состояние, а сбрасывается в нулевое состояние лишь отселектированным импульсом унитарного кода.

Поэтому при поступлении на вход устройства импульса унитарного кода осуществляется установка в единичное состояние триггера 12 этим импульсом, а через время, определяемое задержкой этого импульса в селекторе 11, производится сброс триггера 12 в нулевое состояние. .

Если во входной последовательноети короткий импульс помехи располо.жен в паузе поступления смежных импульсов унитарного кода, то сброс триггера из единичного состояния, в которое он установлен указанным импульсом помехи, в нулевое состояние осуществляется последующим селектированным импульсом .унитарного кода, поскольку импульс помехи в селекторе блокируется.

11мпульсы с выхода селектора 11 поступают также через элемент ИЛИ 14 на счетные входы счетчиков 2 и 3. Код, содержащий в счетчике 3, сравнивается элементом 7 сравнения с кодом величины шага, уровня дискриминации, который задан переключателем 10 уровней.

При равенстве кодов на. выходе элемента 7 сравнения формируется сиг нал, устанавливающий счетчик 3 в нулевое состояние. Таким образом, счетчик 3 производит деление поступившего числа, по модулю заданного переключателем 10 уровней. .

После прекращения передачи кода анализируемой величины на управляющий вход 17 подается сигнал низкого уровня, в соответствии с которым на выходе 24 блока 8 управления фор iиpyeтcя сигнал, который, поступая на вход элемент И 13, производит опрос (анализ) состояния триггера 12

В зависимости от длительности последнего поступившего импульса унитарного кода триггер 12 может находиться в этот момент либо в нулевом, либо в единичном состоянии (в случае

когда этот импульс укорочен, например, вследствие окончания тактирования временного интервала).

Поскольку такой укороченный импульс блокирован селектором 11 и не засчитан счетчиками и 3 устройства, имеет место погрешность в значении анализируемой величины.

Для устранения этого в случае, если триггер 12 находится в единичном состоянии, на выходе элемента И 13 формируется дополнительный им.пульс, которкй, поступая через элемент ШШ 14 на счетные входы счетчиков 2 и 3, увеличивает содержимое последних на единицу.

Далее через время, определяемое - элементом 30 задержки блока 8 управления, на выходах 20-22 блока 8 управления формируются сигналы соответственно записи кода анализируемой величины в первый регистр 4 отпирания блока 9 выдачи числа и записи . остатка от деления в регистр 5.

Последующие циклы обработки производятся аналогично первому, однако теперь после подачи сигнала на управляюпщй вход 17 устройства на выходах 20 и 21 блока 8 управления формируются сигналы только в том случае, если на выходе элемента 6 сравнения - сигнал неравенства, т.е. новое значение анализируемой величины не равно предыдущему (условие необходимо для устранения избыточности выдаваемой информации), и если на выходе счетчика О, т;е. анализируемая величина достигает одного из уровней дискриминации.

При выполнении этих условий на выходе 16 устройства формируется код исследуемой величины, а во время поступления унитарного кода анализируемой величины на выходе 15 устройства формируются сигналы при достижении анализируемой величиной очередного уровня дискриминации.

Сигналы на выходе 22 блока 8 управления во втором и всех последующих циклах обработки не формируются, так как триггер 29 блока 8 управления установлен в единичное состояние. Поэтому в регистре 5 сохранится результат деления первого посту-. пившего на -информационный вход 1 числа по модулю числа, заданного переключателем 10 уровней. 9 . 11 Введение в предлагаемый цифровой дискриминатор селектора импульсо.в по длительности, триггера входного элемента И, входного элемента ИЛИ и новых связей позволяет повысить его помехоустойчивость путем запрета действия коротких импульсов помехи и фик7сации укороченного последнего импульса унита:рного кода. При этом исключается возможность появления ситуаций нарушения заданных уровней дискриминации выводимых .значений и вывода квазиповторяющихся значений.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальный цифровой дискриминатор | 1975 |

|

SU591854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой дискриминатор | 1981 |

|

SU1003069A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-06-10—Подача