Изобретение относится к приборостроению, в частности к средствам анализа амплитудных характеристик сигналов, и может быть использовано, например, в аппаратуре для гранулометрического анализа полидисперсных систем при контроле загрязнения воздушной или жидкой сред.

Целью изобретения является повышение функциональной надежности за счет сокращения аппаратурных затрат.

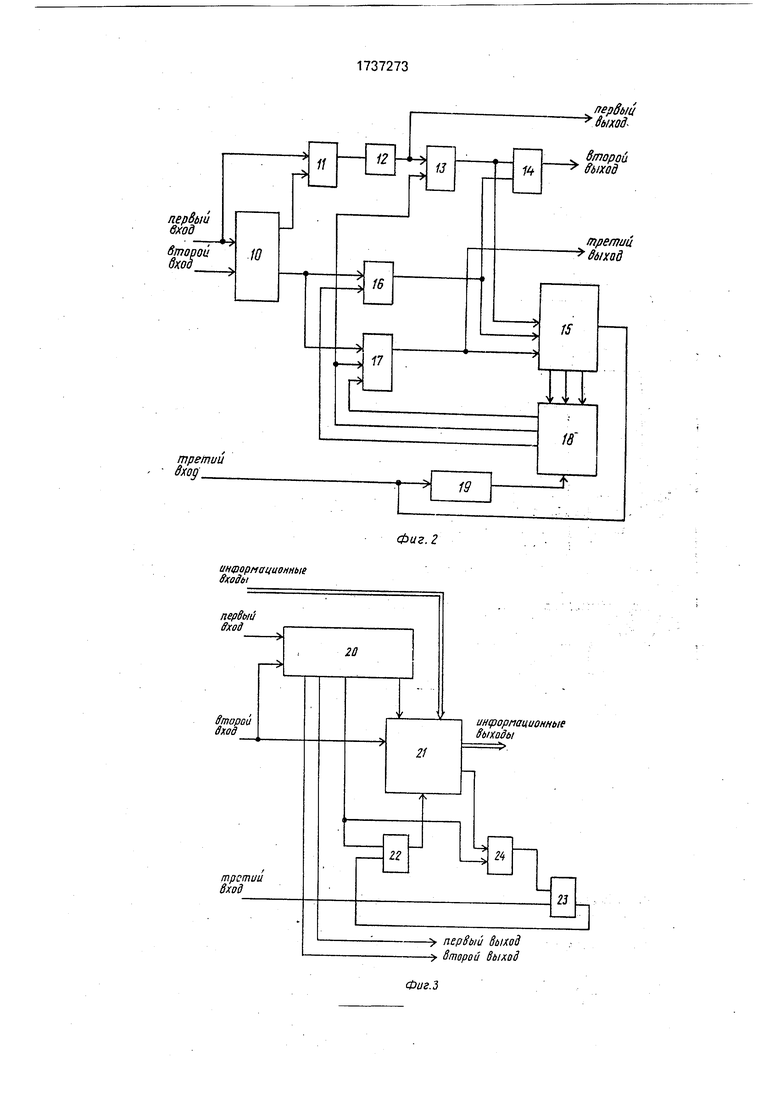

На фиг. 1 представлена блок-схема амплитудного анализатора; на фиг. 2 - схема блока временного анализа; на фиг. 3 - схема блока инкрементирования данных ОЗУ; на фиг. 4 - схема формирователя кода адреса ОЗУ, импульса конца преобразования и строба младшего разряда.

Амплитудный анализатор содержит многоканальный блок 1 сравнения, блок 2 временного анализа, элемент ИЛИ 3, регистр 4, блок 5 инкрементирования данных ОЗУ, приоритетный шифратор 6, формирователь 7 кода адреса ОЗУ, импульса конца преобразования и строба младшего разряда, ОЗУ 8, триггер 9. Многоканальный блок 1 сравнения входом подключен к входу устройства, первым выходом - к первому входу блока 2 временного анализа, первым входом управления - к линии измерение устройства, второму входу блока 2 временного анализа и первому входу элемента ИЛИ 3, вторыми выходами - к входам регистра 4, входом записи соединенного с вторым входом управления многоканального блока 1 сравнения и первым выходом блока 2 временного анализа, вторым выходом соединенного с вторым входом элемента ИЛИ 3 и первым входом блока 5 инкрементирования, а третьим выходом - с входом наивысшего приоритета шифратора 6, остальными входами соединенного с выходами регистра 4, а выходами -с информационными входами формирователя 7, входом соединенного с выходом блока 5 инкрементирования, перСП

С

vi со vi ю VI со

вым входом управления - с выходом элемента ИЛИ 3, первыми выходами - с адресными входами ОЗУ 8, вторым выходом - с третьим входом блока 2 временного анализа и входом сброса триггера 9, входом уста- новки подключенного к линии очистка ОЗУ устройства, а выходом - к второму входу управления формирователя 7 и второму входу блока 5 инкрементирования, третьим входом соединенного с третьим выходом формирователя 7, вторьш выходом - с входом записи ОЗУ 8, информационными выходами - с информационными входами ОЗУ 8, а информационными входами - с выходами ОЗУ 8, являющимися выхо- дами устройства.

Многоканальный блок 1 сравнения содержит амплитудные дискриминаторы на разные пороги срабатывания, входами подключенные к входу блока 1, выходами - к входам установки триггеров соответственно, выход амплитудного дискриминатора высшей чувствительности является первым выходом блока 1, вторыми выходами кото- рого являются выходы триггеров, первыми и вторыми входами сброса подключенные к первому и второму входам управления блока 1 соответственно.

Блок 2 временного анализа (фиг. 2) со- держит реле 10 времени, последовательно соединенные триггер 11, одновибратор 12, триггер 13, элемент ИЛ И 14, а также регистр 15, триггеры 16, 17, преобразователь 18 кодов, элемент 19 задержки. Реле 10 времени, первый и второй входы которого являются первым и вторым входами блока 2 соответственно, первым входом подключено также к входу сброса триггера 11, первым выходом - к синхровходу триггера 11, выход одно- вибратора 12, соединенный с входом установки триггера 13, является первым выходом блока 2, вторым выходом которого является выход элемента ИЛИ 14, первыми вторым входами соединенного с первым и вторым входами регистра 15 соответственно, вторым входом регистр 15 соединен также с выходом триггера 16, входом уста новки соединенного с вторым выходом реле 10 времени и входом установки триггера 17, выход которого является третьим выходом блока 2 и соединен с третьим входом регистра 15, выходами соединенного с входами преобразователя 18 кодов, первым выходом соединенного с вторым входом установки триггера 17, вторым выходом - с выходами сброса триггеров 13, 17, третьим выходом - с входом сброса триггера 16, входом стро- бирования - с выходом элемента 19 задер; жки, входом подключенного к входу записи

регистра 15, являющимся третьим входом блока 2 временного анализа.

Реле 10 времени содержит генератор импульсов, выходом подключенный к счетному входу счетчика импульсов, два входа сброса которого являются двумя входами реле 10 времени соответственно, а выходы подключены к дешифратору, первый выход которого является первым выходом реле speN.uHH, а второй выход -вторым выходом реле 10 времени и соединен с третьим входом сброса счетчика.

Блок 5 инкрементирования данных ОЗУ (фиг. 3)содержит многофазный генератор 20 импульсов, счетчик 21 импульсов, элемент И 22, элемент ИЛИ 23, триггер 24. Многофазный генератор 20 импульсов, первый и второй входы которого являются первым и вторым входами блока 5 соответственно, вторым входом соединен также с входом сброса счетчика 21 импульсов, первым выходом - с входом записи счетчика 21 импульсов, вторым выходом - с первым входом элемента И 22, вторым входом соединенного с выходом элемента ИЛИ 23, первым входом соединенного с выходом триггера 24, синхровходом сброса соединенного с первым входом элемента И 22, а входом установки - с выходом переполнения счетчика 21 импульсов, информационные входы которого являются информационными входами, а выходы - информационными выходами блока 5 инкрементирования. Третьим входом блока 5 является второй вход элемента ИЛИ 23, а первым и вторым выходами - четвертый и третий выходы многофазного генератора 20 импульсов соответственно.

Амплитудный анализатор работает следующим образом.

В режиме измерение освобождается от сигнала сброса по второму входу реле 10 времени и одновременно триггеры многоканального блока 1 сравнения, что дает им возможность устанавливаться при соответствующей амплитуде входного импульса. Срабатывание дискриминатора наивысшей чувствительности в многоканальном блоке 1 сравнения освобождает от сигнала сброса по первому входу реле 10, начинающего отсчет времени. При достижении первого порога срабатывания импульсом, поступающим на синхровход, устанавливается триггер 11, сброс которого по завершению входного импульса амплитудного анализатора вызывает запуск одновибрато- ра 12. Передним фронтом импульса одно- вибратора 12 информация с вторых выходов многоканального блока 1 сравнения переписывается в регистр 4, а триггеры блока 1

сбрасываются импульсом одновибратора 12, устанавливающим триггер 13. На втором выходе блока 2 временного анализа появляется сигнал, обуславливающий отработку при помощи блока 5 инкрементирования данных ОЗУ 8 по адресу размерной группы, код которого поступает от формирователя 7, принимающего информацию от приоритетного шифратора 6, анализирующего состоя- ние выходов регистра 4 при уровне логического нуля на входе наивысшего приоритета. Код адреса размерной группы входного импульса поступает на первые выходы формирователя 7 через коммутатор.

Для каждой размерной группы в ОЗУ 8 отводится несколько ячеек памяти по количеству разрядов, например десятичных разрядов, если входы-выходы ОЗУ 8 содержат четыре информационные линии. Отработка команды инкрементирования данных ОЗУ 8 осуществляется последовательно для каждого разряда, код адреса разряда формируется при помощи счетчика 25 импульсов в формирователе 7.

Для отработки команды инкрементирования сигналом по первому входу блока 5 обеспечивается работа многофазного генератора 20, импульсом с первого выхода которого производится запись данных ОЗУ в счетчик 21 импульсов, импульсом с второго выхода, поступающего через элемент И 22 на счетный вход - инкрементирование счетчика 21 импульсов, для младшего разряда - безусловное, что обеспечивается приходом сигнала логической единицы на второй вход элемента И 22 через элемент ИЛИ 23 от дешифратора 26, регистрирующего на выходе счетчика 25 импульсов код младшего разряда, для последующих разрядов - при условии переполнения счетчика 21 импульсов во времени инкрементирования предыдущего разряда, что регистрируется триггером 24. Импульсом с третьего выхода многофазного генератора 20 производится запись данных в ОЗУ 8 по коду адреса текущего разряда, обновляющегося при приходе на счетный вход счетчика 25 импульса с четвертого выхода многофазного генератора 20. После проведения операции инкрементирования по всем разрядам передним фронтом импульса переполнения счетчика 25, поступающего через элемент И 27 и элемент ИЛИ 28 на второй выход формирователя 7, производится запись в регистр 15 состояний триггеров 13, 16, 17 анализируемых преобразователем 18 кодов, формирующим управляющие импульсы для триггеров 13, 16, 17 с приходом импульса стробирования.

В случае установленного состояния триггера 13 и сброшенных состояний триггеров 16, 17 преобразователь 18 формирует импульс на первом выходе, устанавливая

триггер 17. Команда инкрементирования повторяется, но по адресу общего количества регистрируемых входных импульсов, так как на входе наивысшего приоритета шиф- ратооа б в этом случае присутствует сигнал

логической единицы. После завершения данной команды преобразователь 18 кодов формирует импульс на втором выходе, сбрасывая триггеры 13, 17.

При затягивании входного импульса

амплитудного анализатора относительно номинального значения достигается срабатывание реле 10 времени по второму порогу, устанавливаются триггеры 16, 17, реле 10 сбрасывается и продолжает свою работу. В

этом случае после отработки команды инкрементирования по адресу ОЗУ 8 общего количества входных импульсов преобразователь 18 кодов сформирует импульс на третьем выходе, сбрасывая триггер 16 и завершая строб команды инкрементирования. Триггер 17 остается установленным, поэтому при завершении входного импульса, сопровождающегося установкой триггера 13, будет отработана команда

инкрементирования и триггеры 13, 16 17 окажутся сброшенными.

Для корректного функционирования предлагаемого устройства необходимо, чтобы время отработки двух команд инкремен- тировачия не превышало времени достижения реле 10 первого порога срабатывания.

Режиму измерение должна предшествовать очистка ОЗУ. Для этого по линии очистка ОЗУ поступает импульс, устанавливающий триггер 9, что инициирует по вто- рому входу работу многофазного генератора 20 импульсов и, следовательно,

приводит к отработке команды инкрементирования. Одновременно сигнал с выхода триггера 9 обеспечивает нулевое состояние счетчика 21 импульсов, поддерживая соответствующий сигнал на входе сброса и блокируя в счетчике 21 вход записи, а также обеспечивает появление на втором выходе формирователя 7 импульса переполнения с выхода счетчика 29 импульсов, формирующего в данном режиме код размерной группы и общего количества.

Таким образом, производится запись нулевых данных в рабочие ячейки ОЗУ 8 Импульс переполнения возвращает триггер 9 в нулевое состояние, завершая отработку режима очистка ОЗУ,

Формула изобретения

Амплитудный анализатор, содержащий многоканальный блок сравнения, вход которого является входом устройства, блок временного анализа, входом соединенный с выходом многоканального блока сравнения, отличающийся тем, что, с целью повышения функциональной надежности за счет сокращения аппаратных затрат, в него введены ОЗУ, блок инкрементирования данных ОЗУ, формирователь кода адреса ОЗУ, импульса конца преобразования и строба младшего разряда, регистр, приоритетный шифратор, триггер, элемент ИЛИ, блок временного анализа вторым входом подключен к первому входу элемента ИЛИ и линии измерение устройства, первым выходом - к второму входу управления многоканального блока сравнения и входу записи регистра, входами соединенного с вторыми выходами многоканального блока сравнения, вторым выходом - к второму

входу элемента ИЛИ и первому входу блока инкрементирования, третьим выходом - к входу наивысшего приоритета шифратора, остальными входами соединенного с выходами регистра, а выходами - с информационными входами формирователя, входом соединенного с первым выходом блока инкрементирования, первым входом управления - с выходом элемента ИЛИ, первыми

выходами - с адресными входами ОЗУ, вторым выходом - с третьим входом блока временного анализа и входом сброса триггера, входом установки подключенного к линии очистка ОЗУ устройства, а выходом - к

второму входу управления формирователя и второму входу блока инкрементирования, третьим входом соединенного с третьим выходом формирователя, вторым выходом - с входом записи ОЗУ, информационными выходами - с информационными входами ОЗУ, а информационными входами - с выходами ОЗУ, являющимися выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| Программируемый многофазный тактовый генератор | 1990 |

|

SU1785069A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Система для контроля электронных устройств | 1988 |

|

SU1667074A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Устройство для многоканальной регистрации временных характеристик процессов | 1980 |

|

SU900252A1 |

Изобретение относится к средствам анализа амплитудных характеристик сигналов и может быть использовано для сортировки по размерам и подсчета количества частиц при контроле загрязнения воздушной или жидкой сред. Цель изобретения - повышение функциональной надежности обеспечивается ОЗУ, для которого счет входных импульсов по размерным группам обеспечивается блоком инкрементирова- ния данных ОЗУ. В формировании кода адреса ОЗУ, по которому отрабатывается команда инкрементирования, принимают участие многоканальный блок сравнения, блок временного анализа, регистр, приоритетный шифратор, формирователь. 4 ил.

Фиг.1

первый вход

второй вход

третий вход

информационные ffxodbi

первый ffxod

второй вход

третий вход

первый вы ходSfHOpOLt

ffbixad

третий выход

Фиг, 2

инфорпационные Выходы

Второй Выход

вход

27

28

первый вход управление

Второй Выход

26

третий выход

25

первые Выходы

я

29

30

Фиг А

| Анализатор амплитудных характеристик динамических процессов | 1977 |

|

SU669187A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Беляев С | |||

| П., Никифорова Н | |||

| К., Смирнов В | |||

| В | |||

| и др | |||

| Оптико-электронные методы изучения аэрозолей | |||

| М.: Энергоиздат, 1981, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

Авторы

Даты

1992-05-30—Публикация

1988-10-10—Подача