Изобретение относится к вычислительной технике, в частности к устройствам управления, и может быть использовано для управления многобуферным обменом с памятью в вычислительных 5 комплексах.

Цель изобретения - расширение функциональных возможностей за счет управления буферным обменом в вычислительном комплексе.

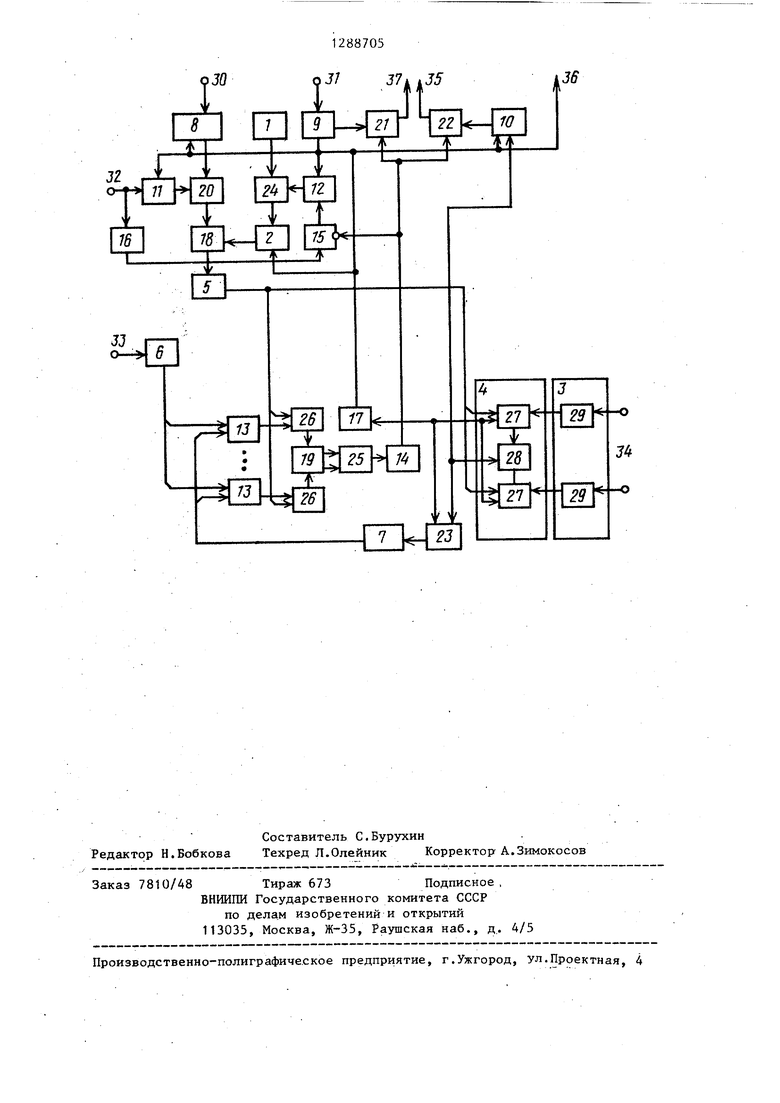

На чертеже представлена структурная схема устройства.

Устройство содержит генератор 1 импульсов, счетчик 2, блок 3 памяти, коммутатор 4, первый 5, второй 6, и третий 7 дешифраторы, первый 8, второй 9 и третий 10 регистры, пер- вьй 11 и второй 12 триггеры, группу счетчиков 13, формирователь 14 им15

состояние. При этом на выходе дешифратора 5 появляется сигнал, который разрешает подключение инверсных вьгходов j-ro счетчика 13 к второму входу j-ro блока 26 элементов И. Если j-й счетчик 13 находится в нулевом состоянии, то на выходе формирователя 14 появляется сигнал, который разрешает выдачу кода номера j блока из j-ro регистра 29 в регистр 10 (код младших разрядов дискрипто- ра), а затем вьщачу кода дискрипто- ра из регистров 9 и 10 на вход 35 ВК. При этом также регистры 8-10, триггеры 11 и 12 и счетчик 2 устанавливаются в нулевое состояние, сигнал с выхода элемента 17 задержки поступает на вход готовности ВК, содержимое j-ro счетчика 13 увеличивает25

пульсов, элемент 15 запрета, первый ся на единицу, т.е. j-й буфер за- и второй 17 элементы задержки, пер- хватывается для обмена, вый 18 и второй 19 блоки элементов Если содержимое j-ro счетчика 13 ИЛИ, первьш 20, второй 21, третий 22 и четвертый 23 блоки элементов И, первый 24 и второй 25 элементы И, первую 26 и вторую 27 группы блоков элементов И, блок 28 элементов ИЛИ, Ьлок 29 регистров, выход 30 задания номера блока вычислительного комплекса, выход 31 старших разрядов дискриптора вычислительного комплекса, выход 32 запуска вычислительного комплекса, выход 33 кода открепленного буфера вычислительного комплекса, выход 34 младших разрядов дискриптора -вычислительного комплекса, вход 35 младших разрядов дискриптора вычислительного комплекса, вход 36 готовности вычислительного комплек30

35

не равно нулю, то нулевой сигнал с выхода формирователя 14 разрешает прохождение задержанного элементом 16 импульса запуска через элемент 15 запрета и установку в единичное состояние триггера 12. При этом с помощью счетчика 2 и генератора 1 проводится последовательный анализ содержимого счетчиков 13 до тех пор, пока не найден i-й счетчик 13, содержимое которого равно нулю. Далее работа устройства аналогична процессу, описанному для случая j-ro счетчика 13.

рует в качестве результата дискрип- тор с соответствующим математическим

Формула изобретения

С выхода 33 ВК поступает им- пульсньш код i номера открепленного

са; вход з 7 старших разрядов ди скрип-40 буфера, в результате чего б-й счетчик тора вычислительного комплекса. У яется.

Таким образом, устройство формиУстройство работает следующим образом.

В исходном состоянии регистры 8-45 адресом, описывающим информационную 10, триггеры 11 и 12, счетчик 2 обну- часть выявленного для обмена буфера, лены, в регистрах 29 хранятся коды номеров блоков, i-й (,п) счетчик 13 обнулен, если i-й буфер не находится в обмене.50

С выхода 30 вычислительного комплекса (ВК) в регистр 8 записывается код j номера блока (параметра операции записи или чтения при многобуферном обмене), с выхода 31 ВК в регистр 9 записывается код старших разрядов дискриптора, с выхода 32 ВК поступает импульс запуска, который устанавливает триггер 11 в единичное

Устройство для распределения ресурсов памяти в вычислительном комплексе, содержад(ее счетчик, первый дешифратор, блок памяти, коммутатор, генератор импульсов, первый триггер, пер- 55 вый и второй блоки элементов И, группу счетчиков, первый регистр, первый блок элементов ИЛИ, первый элемент И, группу блоков элементов И, причем вход младших разрядов дискриптора

состояние. При этом на выходе дешифратора 5 появляется сигнал, который разрешает подключение инверсных вьгходов j-ro счетчика 13 к второму входу j-ro блока 26 элементов И. Если j-й счетчик 13 находится в нулевом состоянии, то на выходе формирователя 14 появляется сигнал, который разрешает выдачу кода номера j блока из j-ro регистра 29 в регистр 10 (код младших разрядов дискрипто- ра), а затем вьщачу кода дискрипто- ра из регистров 9 и 10 на вход 35 ВК. При этом также регистры 8-10, триггеры 11 и 12 и счетчик 2 устанавливаются в нулевое состояние, сигнал с выхода элемента 17 задержки поступает на вход готовности ВК, содержимое j-ro счетчика 13 увеличивается на единицу, т.е. j-й буфер за- хватывается для обмена, Если содержимое j-ro счетчика 13

ся на единицу, т.е. j-й буфер за- хватывается для обмена, Если содержимое j-ro счетчика 13

не равно нулю, то нулевой сигнал с выхода формирователя 14 разрешает прохождение задержанного элементом 16 импульса запуска через элемент 15 запрета и установку в единичное состояние триггера 12. При этом с помощью счетчика 2 и генератора 1 проводится последовательный анализ содержимого счетчиков 13 до тех пор, пока не найден i-й счетчик 13, содержимое которого равно нулю. Далее работа устройства аналогична процессу, описанному для случая j-ro счетчика 13.

рует в качестве результата дискрип- тор с соответствующим математическим

Формула изобретения

адресом, описывающим информационную часть выявленного для обмена буфера,

адресом, описывающим информационную часть выявленного для обмена буфера,

Устройство для распределения ресурсов памяти в вычислительном комплексе, содержад(ее счетчик, первый дешифратор, блок памяти, коммутатор, генератор импульсов, первый триггер, пер- вый и второй блоки элементов И, группу счетчиков, первый регистр, первый блок элементов ИЛИ, первый элемент И, группу блоков элементов И, причем вход младших разрядов дискриптора

памяти устройства соединен с информационным входом блока памяти, выход которого подключен к информационному входу коммутатора, первый, второй входы и выход первого элемента И со- единены соответственно с выходами первого триггера, генератора импульсов и со счетным входом счетчика, вход задания режима устройства подключен к информационному входу перво го регистра, отличающееся тем, что, с целью расширения функциональных возможностей за счет управления буферным обменом в вычислительном комплексе, в него введены второй и третий дешифраторы, второй и третий регистры, второй триггер, формирователь импульсов, элемент запрета, первый и второй элементы задержки, второй блок элементов РШИ, третий и четвертый блоки элементов И, второй элемент И, причем выход первого блок элементов И подключен к входу первого дешифратора, выход первого регистра соединен с первым входом первого

блока элементов И, выход которого

подключен к первому входу первого блока элементов ИЛИ, вход запуска устройства подключен к единичному входу второго триггера и к входу первого элемента задержки, выход которого подключен к информационному входу элемента запрета, вход старших разрядов дискриптора памяти устройства подключен к информационному входу второго регистра, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с выходом старших разрядов дискриптора памяти устройства,выход формиро- вателя импульсов подключен к входу второго элемента задержки, к первому входам третьего и четвертого блоков

5 О 5 0

0 5

5

элементов И, к второму входу второго блока элементов И, к управляющему входу коммутатора и к управляющему входу элемента запрета, выход которого соединен с единичным входом первого триггера, выход второго элемента задержки подключен к входам сброса счетчика, первого, второго и третьего регистров, первого и второго триггеров и к выходу готовности устройства, выход счетчика соединен с вторым входом первого блока.элементов ИЛИ , выход третьего регистра подключен к второму входу третьего блока элементов И, выход которого соединен с входом младших разрядов дискриптора памяти устройства, вход кода маски буфера устройств подключен к входу второго дешифратора, выходы которого подключены к входам сброса. соответствующих счетчиков группы, -Инверсные выходы которых подключены к первым входам соответствующих блоков элементов И группы, вторые входы которых подключены к выходам первого дешифратора, выходы блоков элементов и группы подключены к входам второго блока элементов ИЛИ, выход которого соединен с соответствующим входом второго элемента И, выход которого подключен к входу формирователя импульсов, выход коммутатора подключен к информационному входу третьего регистра и к второму входу четвертого блока элементов И, выход которого соединен с входом третьего дешифратора, выходы которого подключены к счетным входам соответствующих счетчиков группы, выход первого дешифратора подключен к второму информационному входу коммутатора, выход второго триггера подключен к второму входу первого блока элементов И.

JJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для идентификации паролей пользователей | 1990 |

|

SU1784961A1 |

| Программируемый логический контроллер | 1984 |

|

SU1497616A1 |

| Устройство для сортировки чисел | 1983 |

|

SU1151952A1 |

| Устройство для считывания информации из ассоциативной памяти большого объема | 1988 |

|

SU1631607A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1388886A1 |

| Многопроцессорная вычислительная система | 1990 |

|

SU1798799A1 |

| Устройство для выбора задач на обслуживание | 1984 |

|

SU1244671A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам управления, и может быть использовано для управления многобуферным обменом в вычислительных комплексах. Целью изобретения является расширение функциональных возможностей за счет управления многобуферным обменом в вычислительных комплексах. Устройство содержит генератор импульсов, счетчик, блок памяти, коммутатор, с первого по третий дешифраторы, с первого по третий регистры, первый и второй триггеры, группу счетчиков, формирователь импульсов, элемент запрета, первый и второй элементы задержки, первый и второй блоки элементов ИЛИ, с первого по четвертый блоки элементов И, первый и второй элементы И, группу блоков элементов И. Устройство осуществляет аппаратную переадресацию пймяти, образуя адрес из номера блока памяти и дескриптора адреса. 1 ил. (Л 00

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1985-03-22—Подача