Изобретение относится к вычислиельной технике и может быть испольовано для контроля и диагностики олупроводниковой оператиыной памяти икро-ЭВМ.

Известно устройство для контроля олупроводниковой оперативной памяи, содержащее блок управления, три счетчика, три триггера, программиуемый делитель частоты, дешифратор, ва блока вентилей, два сумматора о модулю два, компаратор ошибок и блок индикации.

Известное устройство характеризуется невозможностью проверки ОЗУ ЭВМ на уровне системы и недостаточной универсальностью, поскольку устройство не может обеспечить надежный контроль БИС ОЗУ различных типов.

Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство для контроля памяти, содержащее первый, второй, третий и четвертый счетчики, блоки постоянной и оперативной памяти, первый и второй регистры, арифметическо-логический блок, блок местного управления, блок управления, коммутатор, блок сравнения и блок индикации. Недостатками данного устройства . являются низкое быстродействие вследствие контроля ОЗУ до первого сбоя и невозможности сбора информации о неисправных микросхемах памяти группы одновременно проверяемых микросхем, число которых соответствует разрядности проверяемого ОЗУ; недостаточная достоверность, надежность и эффективность контроля ОЗУ ЭВМ как на-уровне микросхем, так и на уровне системы, вследствие ограниченного, набора генерируемых тестов; невозможность надежного и достоверного контроля ОЗУ ЭВМ разрядности, отличной от заданной, и контроля дополнительных разрядов для ОЗУ с контролем на четность или с исправлением ошибок.

Целью изобретения является повышение быстродействия и надежности устройства.

Поставленная цель достигается тем, что в устройство для контроля памяти, содержащее первый счетчик, выходы которого подключены к соответствующим входам блока постоянной памяти и одним входам блока оперативной памяти, выходы которых соединены

5

0

5

0

0

5

с информационными входами второт О, третьего, четвертого .счетчиков, первого и второго регистров, первый арифметическо-логический блок, первые и соответствующие вторые входы которого подключены к выходам второго и третьего счетчиков соответственно, блок местного управления, информационные выходы которого соединены с другими входами блока оперативной памяти, а соответствующие выходы - с первым -и вторым входами блока управления, входы первой группы которого и информационные входы первого счетчика подключены к соответствующим выходам блока постоянной памяти, а выходы первой группы блока управления - к входам выборки второго, третьего, четвертого счетчиков, первого и второго регистров, коммутатор, первый блок индикации и блок сравнения, введены пятый, шестой, седьмой и восьмой счетчики, третий, четвертый и пятый регистры, первый, второй и третий триггеры, второй арифметическо-логический блок, группа элементов И, второй блок индикации, первая, вторая и третья группы формирователей, причем третий и четвертый

выходы блока местного управления подключены соответственно к первому управляющему входу первого счетчика и одним управляющим входам блоков оперативной и постоянной памяти, ин5 формационные входы которых соединены с одними входами, а выходы - с другими входами второго блока индикации, информационные входы пятого, шестого, седьмого и восьмого счетчиков, а также третьего и четвертого регистров объединены и подключены к соответствующим выходам блока постоянной памяти, а их управляющие входы и одни входы первого, второго и третьего триггеров соединены с соответствующими выходами второй группы блока управления, выходы третьей группы которого подключены к соответствующим входам перQ вого и второго арифметическо-логичес- ких блоков, выходы четвертой группы - к одним входам третьей группы форми- . рователей, а выходы пятой группы - к одним входам первой группы формирова5 телей и блока сравнения, другие входы которого соединены с выходами первой группы формирователей, а выходы - с одними входами группы элементов И, выходы которой соединены

с входами пятого регистра, выходы которого соединены с входами первой группы первого блока индикации и другими входами второй группы блока управления, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы которого подключены соответственно к другому входу первой группы формирователей, другим входам группы элементов И, первому и второму входам пятого регистра, второму и третьему входам первого счетчика, другим входам первой, второй и третьей групп формирователей, к одному входу первого блока индикации и другим входам первого, второго и третьего триггеров, третий и четвертый входы блока управления подключены к одним выходам второго регистра, пятый, шестой и седьмой входы - к выходам первого, второго и третьего триггеров, восьмой вход - к выходу блока сравнения, входы третьей группы - к выходам третьего и четвертого регистров, а входы четвертой группы - к выходам переноса второго, третьего, четвертого, пятого, шестого, седьмого и восьмого счетчиков соответственно, третий выход регистра соединен с входами первого и второго арифметическо-логичес ких блоков, выходы которых подключены к одним входам коммутатора, выходы которого подключены к одним входам второй группы формирователей, входы первой и второй групп второго арифметическо-логического блока подключены к выходам пятого и шестого счетчиков, выходы четвертого и седьмого счетчиков соединены с другими входами коммутатора и входами второй группы первого блока индикации, выходы первого регистра подключены к входам третьей группы первого блока индикации, первый и пятый выходы блока местного управления соединены с четвертым входом первого счетчика и другим объединенным управляющим входом блока постоянной памяти, четвертого и седьмого счетчиков соответственно, выходы первой и второй группы формирователей и входы/выходы третье группы формирователей являются выходами устройства.

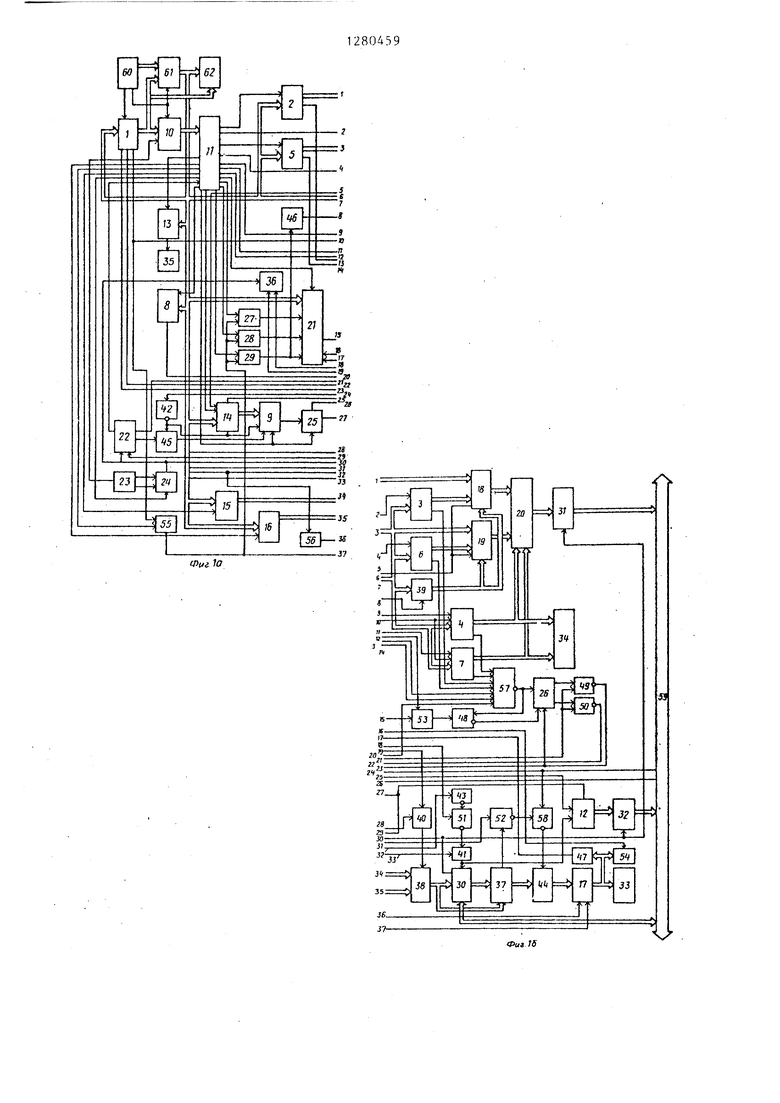

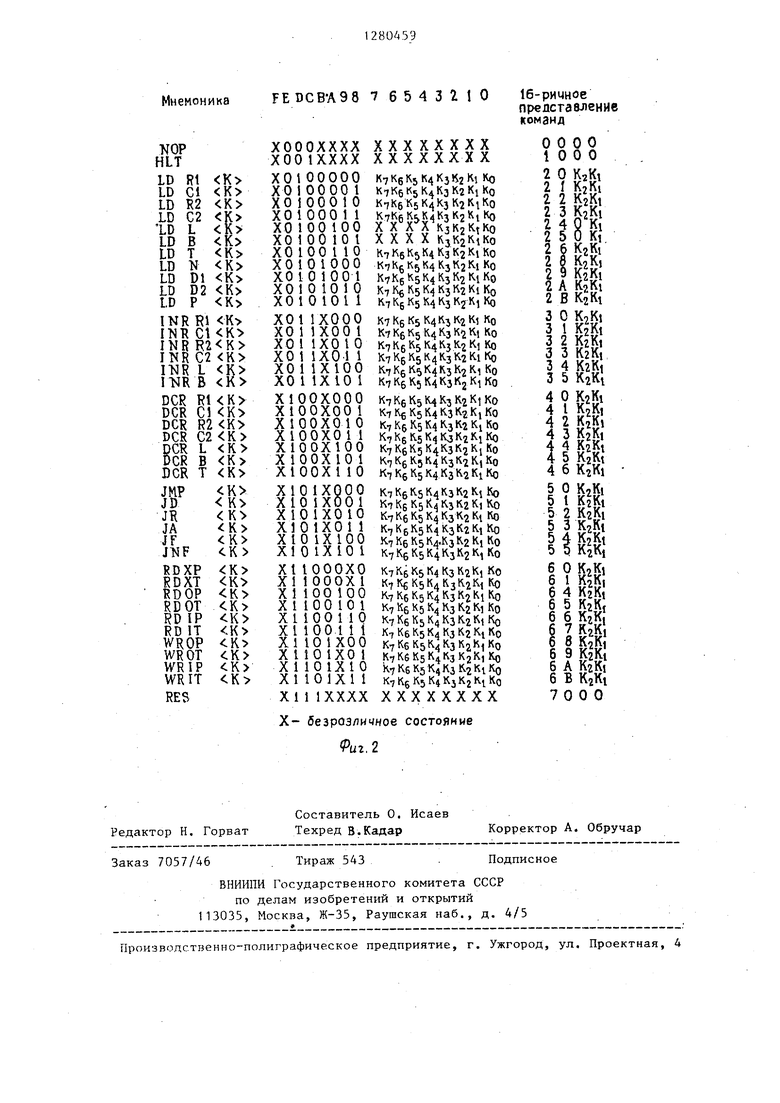

На фиг. 1 (q и & ) изображена схе ма устройства для контроля памяти; на фиг. 2 - коды команд устройства.

Устройство содержит счетчики 1-9, блок постоянной памяти (БПП) 10,

дешифраторы 11 и 12, регистры 13-17, арифметическо-лог ические блоки 18 и 19, коммутатор 20, мультиплексор 21, генератор тактовых импульсов 22, 5 пульт управления 23, триггеры 24-29, .формирователи 30-31, первый блок индикации, включающий группы элементов индикации 33-36, блок сравнения 37, блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 38 и

О 39, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 40 и 41, элементы НЕ 42 и 43, блок элементов И 44, элементы И 45-47, элементы И-НЕ 48-52, элементы ИЛИ 53-56, элементы ИЛИ-НЕ 57 и 58, системную щину

5 59, дополнительный пульт управления 60, блок оперативной памяти (БОП) 61, второй блок индикации 62.

Блоки 23 и 60 представляют собой блок местного управления, а блоки

0 9, 12, 21, 22, 24-26, 38-43, 45-58 - блок управления.

Основной пульт 23 управления содержит три клавиши управления: ПУСК- запуск устройства для выполнения

программы тестирования или для продолжения тестирования после останова по команде программы; СБРОС - останов выполнения программы тестирования и сброс счетчика адреса микро0 команд (счетчика 1), счетчиков адреса памяти (счетчиков 4 и 7), регистра ошибок (регистра 17), триггеров условий перехода (триггеров 27-29); ПЗУ 1/2 - выбор области па5 мяти микрокоманд (БПП 10).

Группы элементов 33-36 индикации индицируют: адрес ряда микросхем памяти (состояние счетчика 4), адрес платы памяти (состояние счетчика 7) ,

0 состояние регистра ошибок (регистра 17), условия теста (состояние триггеров 27-29), состояние останова (состояние триггера 24).

К устройству может быть подклю5 чен дополнительный пульт 60 управления и индикации (блок 62), предназначенный для записи программ в БОП 61 или чтения состояния БОП 61 или БПП 10.

0 Пульт 60 управления представляет ,собой 20-клавишную клавиатуру, со- , держащую цифровые и управляющие клавиши О, 1, 2, 3, 4, 5, 6, 7, 8, 9, А, В, С, D, Е, F - клавиши ввода

5 16-ричных цифр; ЗАПИСЬ - запись введенных четырех цифр в ОЗУ 61; ЧТЕНИЕ ВПЕРЕД - пошаговое чтение содержимого памяти микрокоманд в прямом направлении; ЧТЕНИЕ НАЗАД - пошаговое чтение

содержимого памяти микрокоманд в обратном направлении; ПЗУ/ОЗУ - выбор источника -программ.

Блок 62 индикации индицирует: 4-значный код вводимых данных; 2-энач ный код текущегооадреса памяти микрокоманд; выбранный источник тестовых программ.

Счетчики 2 и 5 предназначены для установки в соответствии с тестовой программой адреса тестируемой ячейки проверяемых БИС ОЗУ. Счетчики 3 и 6 предназначены для установки относительного адреса фоновых ячеек. Действительный адрес фоновых ячеек формируется при этом путем операции в АЛБ 18 и 19 над содержимым счетчиков 2 и 3, 5 и 6. Для обращения к тестируемой ячейке при таком использовании счетчиков содержимое счетчиков 2 и 5 передается на выходы АЛБ 18 и 19 без изменения путем установки на управляющих входах АЛБ 18 и 19 кода II1I. Таким образом АЛБ 18 и 19 используются для вычисления текущего адреса соответственно строк и столбцов тестируемых БИС ОЗУ.

Счетчики 4 и 7 предназначены для установки на программе соответственно адреса ряда памяти на плате и адреса платы памяти.

Коммутатор 20 предназначен для подключения адресных линий с выходов АЛБ 18 и 19 и счетчиков 4 и 7 с помощью перемычек на входы группы формирователей 31 в соответствии с емкостью тестируемых БИС ОЗУ, числом рядов микросхем памяти на плате и числом плат памяти, установленных на системной шине 59 и подлежащих тестированию. Так, например, для тестирования ОЗУ ЭВМ емкостью 64 К байт, реализованного на одной плате и на микросхемах емкостью 16 К бит, по семь линий адреса (для адресации к 16 К ячейкам микросхем) снимаются с АЛБ 18 и АЛБ 19, а две линии адреса (для адресации к четырем рядам микросхем) -со счетчика 47. Для тестирования ОЗУ ЭВМ емкостью 1 М байт, реализованного на четырех платах, каждая из которых имеет емкость 256 К байт и выполнена на микросхемах емкостью 64 К бит, по восемь адресных линий (для адресации к 64 К ячейкам микросхем) снимаются с АЛБ 18 и АЛБ 19, две линии адреса (для адресации к четырем рядам микросхем на плате) - со счетчика 4 и две ли

0

5

нии (для адресации к платам памяти - со счетчика 7.

Инвертирование кода адреса тестируемых ячеек осуществляется путем инвертирования блоком 39 кода на управляющих входах АЛБ 18 и 19 при пес тригге0

редаче злементом И 46 ра 29.

Регистр 13 предназначен для загрузки номера теста, который индици- руется элементами индикации 35. Счетчик 8 быть использован в каче стве таймера.

Регистры 15 и 16 цредназначены для установки соответственно младшего и старшего байта данных. Записываемые данные поступают на вход .Тестируемого ОЗУ через блок 38 элементов ИСКЛЮЧАЩЕЕ ИЛИ, осуществляющего инвертирование или неинвертнрование данных, через группу формирователей

30и системную шину 59. Инвертирование или неинвертирование данных определяется путем операции ИСКЛЮЧАЮЩЕЕ ИЛИ (элемент .40) над .состоянием соответствующего разряда кода команды и состоянием триггера 27.

Считываемая во время чтения тестируемого ОЗУ информация сравнивается блоком 37 с требуемой, снимав-. мой с выходов блока 38. Результат сравнения стробируется в блоке 44 элементов И в течение определенного числа тактов после прихода сигнала

5 подтверждения данных с системой шины 59. Результат сравнения накапливается в регистре 17.

Устройство взаимодействует с тестируемым ОЗУ через системную шину 59

0 и выдает через группу формирователей.

3120-разрядный код адреса, позволяющий адресоваться к 1 М байту памяти; выдает и принимает через двунаправленную группу формирователей 30 16-разрядный код данных; вьщает через группу формирователей 32 сигналы записи, чтения памяти и ввода- вывода. Устройство принимает с шины 59 сигналы подтверждения данных и запрета ОЗУ.

Направлением передачи данных через группу формирователей 30 управляет элемент 41, который в зависимости от состояния выхода элемента 5 51 инвертирует или неинвертирует состояние соответствующего разряда кода команды. Состояние 1 триггера 28 вызывает изменение операции обращения при обращении к фоновым

5

0

7

ячейкам тестируемого ОЗУ. С выхода элемента 41 снимается дополнительный код операции обращения к тестируемому ОЗУ. Дешифратор 12 формирует одну из четырех команд управления ЗАПИСЬ В ПАМЯТЬ, ЧТЕНИЕ ПАМЯТИ ЗАПИСЬ В ПОРТ ВЬГООДА, ЗАПИСЬ В ПОРТ ВВОДА.

Имеется возможность выполнения операции чтения тестируемого ОЗУ с контролем или без контроля считываемой информации. В последнем случае О в соответствующем разряде кода команды, поступающий на вход элемента И-НЕ 52, вызывает запрет строби- рования результата сравнения в блоке 44. Стробирование осуществляется в течение всего времени действия синала подтверждения данных на шине 59 Использование стробирования в течение всего времени чтения данных с выходов тестируемого ОЗУ позволяет обнаружить также кратковременные изменения состояния на любом выходе тестируемого ОЗУ.

Имеется возможность маскирования контроля старшего байта считываемых данных при тестировании 8-разрядных ОЗУ в отличие от 16-разрядных, при тестировании которых маскирование снимается. Маскирование осуществляется путем поддержки в состоянии сброса старших разрядов регистра 17 при 1 в шестом разряде регистра 1

При запуске устройства включаетс триггер 24, разрешая работу генератора 22 и захватывая системную шину 59 путем открывания формирователей 30-32. Генератор 22 формирует постоянные тактовые импульсы, поступающие на вход элемента И 45, и двух- фазные тактовые импульсы Ф 1 и Ф 2. По Ф 1 стробируется дешифратор 11, по Ф 2 изменяется состояние счетчика 1 , В исходном состоянии триггер 26 сброшен и тактовые импульсы Ф 2 через элемент И-НЕ 50 поступают на счетный вход счетчика 1, каждый раз увеличивая его состояние на единицу

При обнаружении дешифратором команды останова триггер 24 сбрасывается и выполнение тестовой программы может быть продолжено по команде ПУСК с пульта 23. Команду останова целесообразно использовать для останова выполнения тестовой программы при обнаружении хотя бы одной ошибки тестирования одного ряда микро

0

схем с целью записи промежуточных результатов диагности и, что значительно сокращает общее .время диагностики ОЗУ микро-ЭВМ.

Все команды, кроме команд обращения к тестируемому ОЗУ или к портам ввода-вывода, выполняются за один цикл (такт Ф 1 плюс Ф 2). При обнаружении дешифратором 11 кода команды обращения к тестируемому ОЗУ или к порту ввода-вывода включается триггер 25, который запрещает формирование генератором 22 сигналов Ф 1 и Ф 2 и стробирует дешифратор 12, обеспечи5 вая управляющие команды требуемой длительности. При появлении на шине 59 сигнала запрета ОЗУ триггер 25 не включается (поддерживается в состоянии сброса) и управляющие команды на шине 59 запрещаются.

Триггер 25 сбрасывается через определенное число тактов генератора 22 после прихода сигнала подтверждения с системной шины 59. Требуемое

5 число тактов загружается в регистр 14 и заносится в счетчик 9 каждый раз по команде обращения к тестируемому ОЗУ или порту ввода-вывода. С приходом сигнала подтверждения разрешается

0 прохождение тактовых импульсов через элемент И 45, под действием которых счетчик 9, работающий на вычитание, начинает изменять свое состояние. При переполнении счетчика 9 триггер 24

5 сбрасывается.

0

5

При выполнении команды перехода требуемое условие перехода в зависимости от кода выбирается мультиплексором 21. При выполнении условия перехода (обнаружение О) сигнал выхода мультиплексора 21 через элементы ИЛИ 53 и И-НЕ 48 поступает на вход установки в 1 триггера 26. Состояние триггера 26 меняется, разрешая прохождение через элемент 49 тактового импульса на вход загрузки счетчика 1 , в который заносится адрес перехода (разряды 7, 6, ..., 0). По концу

0 данного импульса триггер 26 возвращается в исходное состояние.

Элементы И 47 и ИЖ 54 определяют состояние регистра 17 - обнаружение 1 во всех разрядах регистра 17 и

5 обнаружение хотя бы одной ошибки.

При выполнении операции инкремен- тирования или декрементирования состояния счетчиков дешифратор 11 дешифрирует код данной операции и выдает сигнал, поступающий через элементы ИЛИ 53 и И-НЕ 48 на вход установки в 1 триггера 26. Триггер 26 включается и импульс Ф 2 с генератора 22 через элемент И-НЕ 49 поступает на вход загрузки счетчика 1, в который загружается адрес перехода. Пр переполнении соответствующего счетчика сигнал переноса данного счетчик через элемент ИЛИ-НЕ 57 поступает на вход установки в О триггера 26 и на вход элемента И-НЕ 48, запрещая прохождение сигнала с выхода элемента 53 на вход установки триггера 26. Состояние триггера 26 не изменяется и импульс Ф 2 с генератора 22 через элемент И-НЕ 50 поступает на счетный вход счетчика 1, изменяя его состояние на единицу. Использование совмещения операций инкремен- тирования и декрементирования с операцией перехода позволяет исключить отдельные операции перехода и повысить скорость выполнения тестовых программ.

При использовании в качестве источника программ БОП 61 с пульта 60, с которого осуществляется также запись тестовой программы, производится выбор БОП 61 и запрет БПП 10.

Управляя дополнительным входом БПП 10, который является старшим адресом БПП 10, с пульта 23 можно осуществлять выбор между двумя наборами тестовых программ, которые могут храниться с БПП 10.

Небольшой набор команд позволяет легко программировать различные алгоритмы генерирования тестов. Используется следующая.мнемоника команд.

-NOP- отсутствие операции.

HLT - устройство переходит в состояние останова и находится в этом состоянии до повторного запуска с пульта управления. Состояние счетчиков и регистров при не изменяется ,

LD г - (г), загрузить байт К в регистр г (г - один из регистров или счетчик ов R1, R2, С1 , С2, L, В, Т, Р, N, D1, D2).

INR г К - (г)-(г) 1 , увеличить, на единицу содержимое счетчика г с переходом по адресу К при отсутствии переполнения счетчика и с переходом к следующей микрокоманде - при переполнении счетчика (г - один, пз счетчиков R1, R2, С1, С2, L, В, Т).

иа

W

15

28045910

DCR (г)-(г) - 1 - уменьшить на единицу содержимое счетчика г с переходом по адресу К при отсутствии переполнения счетчика и с переходом к следующей микрокоманде при переполнении счетчика.

безусловный переход по адресу К.

JD К - переход по адресу К при состоянии О триггера Т1. При выполнении команды состояние триггера меняется на противоположное.

JR : К - переход по адресу при состоянии О триггера Т 2. При выполнении команды состояние триггера меняется на противоположное.

JA К - переход по адресу К при состоянии О триггера ТЗ. При выполнении команды состояние триггера меняется на противоположное.

JF СК - переход по адресу К при, по крайней мере, одном нуле в регистре ошибок.

JNF -ilO - переход по адресу К при нулевом состоянии регистра ошибок.

RD ХР - чтение состояния фоновой ячейки тестируемого ОЗУ (или чтение порта ввода-вывода) по адре.- су, формируемому путем операции К( над содержимым счетчиков R1 и R2 и операции Kj над содержимым .счетчи20

25

ков С1 и С2. K и Kj - соответственно младшая и старшая 4-битЬвые части байта К.

35 RD XT :К - чтение состояния тестируемой ячейки тестируемого ОЗУ (или чтение порта ввода-вывода) по адресу, формируемому путем операции К , над содержимьт счетчиков R1 и R2

40 и операции К над содержимым счетчиков С1 и С2.

RDOP К - чтение состояния фоновой ячейки тестируемого ОЗУ (или

45 чтение порта ввода-вывода) по адресу, формируемому путем операции К над содержимым счетчиков R1 и R2 и К над содержимым счетчиков С1 и С2, и сравнение считываемых данных с содержи50 мым регистров D1 и D2.

крот К - чтение состояния тестируемой ячейки тестируемого ОЗУ (или порта ввода-вывода) по адресу, фор- 55 мируемому путем операции К, над содержимым счетчиков R1 и R2 и операции Kj над содержимым счетчиков С1 и С2, и сравнение считываемых данных с содержимым регистров D1 и D2.

RD IP K - чтение состояния фоновой ячейки тестируемого ОЗУ (или порта ввода-вывода) по адресу, формируемому путем операции Kf над содержанием счетчиков R1 и R2 и операции К над содержимым счетчиков С1 и С2, и сравнение считываемых данных с инвертированным содержанием регистров D1 и D2.

RDIT dK -чтение состояния тестируемой ячейки тестируемого ОЗУ (или порта ввода-вывода) по адресу, формируемому путем операции К над содержимым счетчиков R1 и R2 и опера- ции К над содержимым счетчиков С1 и С2, и сравнение считываемых данных с инвертированным содержанием регистров D1 и D2,

WROP :К - запись содержимого регистров 1 1, 1 2 в фоновую ячейку тестируемого ОЗУ (или запись в порт ввода-вывода) по адресу, формируемому путем операции К над содержимым счетчиков R1 и R2 и операции К над содержимым счетчиков С1 и С2,

WROT СК - запись содержимого регистров -Dl и D2 в тестируемую ячейку тестируемого Т53У (или в порт ввода- вывода) по адресу, формируемому путем операции К, над содержимым счет- чиков R1 и R2 и операции К над содержимым счетчиков С1 и С2.

WRIP К - запись инвертированного содержимого регистров D1 и D2 в фоновую ячейку тестируемого ОЗУ (или в порт ввода-вывода) по адресу, формируемому путем операции К над содержимым счетчиков R1 и R2 и операции К над содержимым счетчиков С1 и С2.

WRIT :К - запись инвертированного содержимого регистров D1 и D2 в тестируемую ячейку тестируемого ОЗУ (или в порт ввода-вывода) по адресу, формируемому путем операции К, над содержимым счетчиков С1 иС2.

RES - сброс триггеров условий перехода и регистра ошибок.

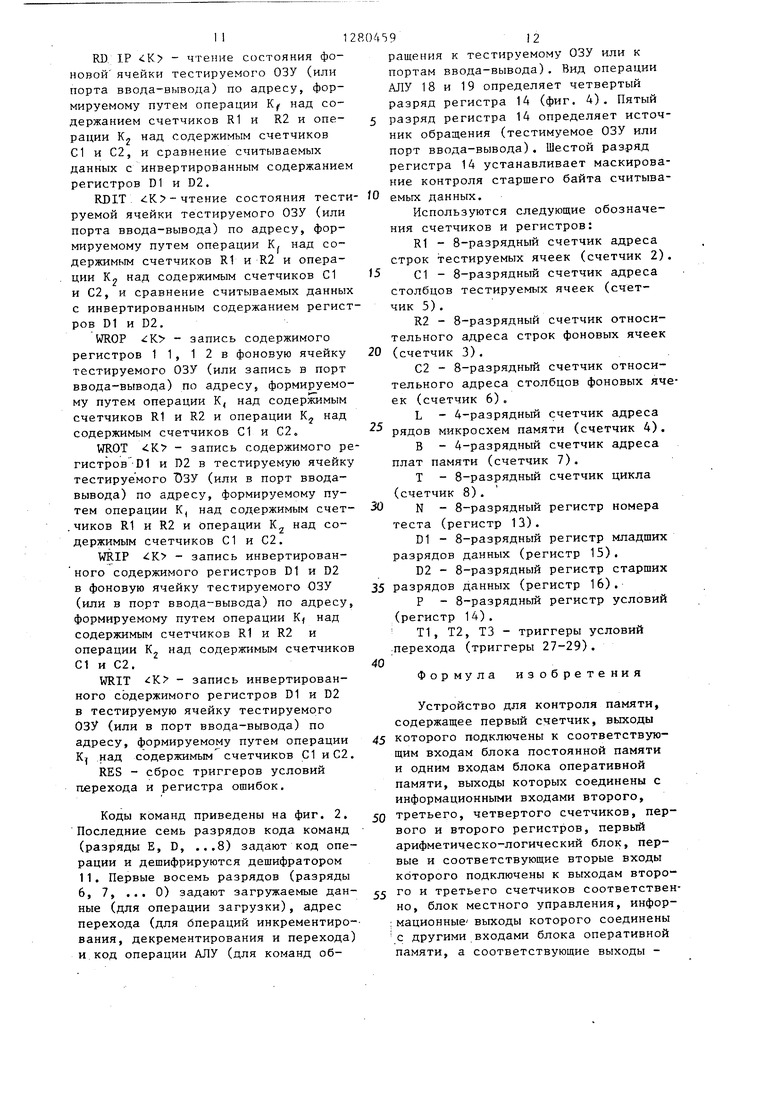

Коды команд приведены на фиг. 2, Последние семь разрядов кода команд

(разряды Е, D, ...8) задают код операции и дешифрируются дешифратором

11. Первые восемь разрядов (разряды 6, 7, ... 0) задают загружаемые данные (для операции загрузки), адрес перехода (для бпераций инкрементиро-- вания, декрементирования и перехода) и код операции АЛУ (для команд о60

5

0

ращения к тестируемому ОЗУ или к портам ввода-вывода). Вид операции АЛУ 18 и 19 определяет четвертый разряд регистра 14 (фиг. 4). Пятый разряд регистра 14 определяет источник обращения (тестимуемое ОЗУ или порт ввода-вывода). Шестой разряд регистра 14 устанавливает маскирование контроля старшего байта считываемых данных.

Используются следующие обозначения счетчиков и регистров:

R1 - 8-разрядный счетчик адреса строк тестируемых ячеек (счетчик 2).

С1 - 8-разрядный счетчик адреса столбцов тестируемых ячеек (счетчик 5) .

R2 - 8-разрядный счетчик относительного адреса строк фоновых ячеек (счетчик 3).

С2 - 8-разрядный счетчик относительного адреса столбцов фоновых ячеек (счетчик 6).

L - 4-разрядный счетчик адреса рядов микросхем памяти (счетчик 4).

В - 4-разрядный счетчик адреса плат памяти (счетчик 7).

Т - 8-разрядный счетчик цикла (счетчик В).

N - 8-разрядный регистр номера теста (регистр 13).

D1 - 8-разрядный регистр младших разрядов данных (регистр 15).

D2 - 8-разрядный регистр старших 5 разрядов данных (регистр 16).

Р - 8-разрядный регистр условий (регистр 14).

Т1, Т2, ТЗ - триггеры условий перехода (триггеры 27-29). 0

0

Формула изобретения

Устройство для контроля памяти, содержащее первый счетчик, выходы

5 которого подключены к соответствующим входам блока постоянной памяти и одним входам блока оперативной памяти, выходы которых соединены с информационными входами второго,

0 третьего, четвертого счетчиков, первого и второго регистров, первый арифметическо-логический блок, первые и соответствующие вторые входы которого подключены к выходам второ5 го и третьего счетчиков соответственно, блок местного управления, инфор- ;мационные выходы которого соединены с другими входами блока оперативной памяти, а соответствующие выходы с первым и вторым входами блока управления, входы первой группы которого и информационные входы первого . счетчика подключены к соответствующим выходам блока постоянной памяти, а выходы первой группы блока управления, к входам выборки второго, третьего, четвертого счетчиков, первого и второго регистров, коммутатор первый блок индикации и блок сравнения, отличающееся тем, .что, с целью повышения быстродействия и надежности устройства, в него введены пятый, шестой, седьмой и восьмой счетчики, третий, четвертый и пятый регистры, первый, второй и третий триггеры, второй арифметичес- ко-логический блок, группа элементов И, второй блок индикации, первая, вторая и третья группы формирователей, причем третий и четвертый выходы блока местного управления подключены соответственно к первому управляющему входу первого счетчика и одним управляющим входам блока оперативной и постоянной памяти, информационные входы которых соединены с одними входами, а выходы - с другими входами второго блока индикации, информационные входы пятого, шестого, седьмого и восьмого счетчиков, а также третьего и четвертого регистров объединены и подключены к соответствующим выходам блока постоянной памяти, а их управляющие входы и одни входы первого, второго и третьего триггеров соединены с соответствующими выходами второй группы блока управления, выходы третьей группы которого подключены к соответствующим входам первого и второго арифметическо-логических блоков, выходы четвертой группы - к одним входам третьей группы формирователей, а выходы пятой группы - к одним входам первой группы формирователей и блока сравнения, другие входы которого соединены с выходами первой группы формирователей, а выходы - с одними входами группы элементов И, выходы которой соединены с входами пятого регистра, выходы которого соединены с входами первой группы первого блока индикации и другими вхо

5

дами второй группы блока управления, первьш,второй,третий, четвертый, пятый, шестой, седьмой и восьмой выходы которого подключены соответственно к другому входу первой группы формирователей, другим входам группы элементов И, первому и второму входам пятого регистра, второму и третьему входам первого счетчика, другим входам первой, второй и третьей групп формирователей, к одному входу первого блока индикации и другим входам первого, второго и третьего триггеров, третий и четвертый входы блока

0

5

0

управления подключены к одним выходам второго регистра, пятый, шестой и седьмой входы - к выходам первого, второго и третьего триггеров, связанных с первым блоком индикатора, восьмой вход - к входу устройства, девятый выход - к управляющему входу блока сравнения, входы третьей группы - к выходам третьего и четвертого регистров, а входы четвертой группы - к выходам переноса второго, третьего, четвертого, пятого, шестого, седьмого и восьмого счетчиков соотв ётствен- но, третий выход второго регистра соединен с входами первого и второго арифметическо-логических блоков, выходы которых подключены к одним входам коммутатора, выходы которого подключены к одним входам второй группы формирователей, входы первой

5 и второй групп второго арифметичес- ко-логического блока подключены к выходам пятого и шестого счетчиков, выходы четвертого и седьмого счетчиков соединены с другими входами

0 коммутатора и входами второй группы первого блока индикации, выходы первого регистра подключены к входам третьей группы первого блока индикации, первый и пятый выходы блока

5 местного управления соединены о входами сброса первого, четвертого и седьмого счетчиков соответственно, управляющим входам блока постоянной памяти соответственно, четвертого и

0 седьмого счетчиков соответственно, выходы первой и второй группы формирователей и входы/выходы третьей группы формирователей являются выходами устройства.

Фиг JS

Ч

МнемоникаFEDCB-A98 7 6543210

Х- безрозличное состояние «Риг, 2

Редактор Н. Горват

Составитель 0. Исаев Техред В.Кадар

Заказ 7057/46

Тираж 543

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7 6543210

ХХХХХХХХ X X X ХХХХ X

KV Kg KS «4 Кз Кг KI KO

K7K6 5 4 3K2KiKo

HTKeKsK kaK i ii o

7 бК&54 3 2 1 XX X X K KoKtl

ХХХХ KjKjKlKo

К7КбК5К4КзК2К1Ко KT KC Kg Kj K2 KI KO К7КбК5К4КзК2К1Ко K7l%K5K4K3K2KiKo К7К5К5К4КзК2гК1 KQ

К7КбК5К4К5К2К1 KQ К7КбК5К4КзК К1 KO

К7КбК5К4КзКгК, KG

К7КбК5К4КзК2К1Ко К7КбК5К4КзК2К1 KO К7КбК5К4КзК2К1Ко

К7КбК5К4КзКгК,Ко К7К€К5К4КзКгК1Ко К7КбК5К4КзК2К1Ко К7 kg К.5 К Kj Kj KI KO К7КбК5К4КзК2К1 Ко

К7 Kg KU К4 3 г 0

KT Кб KS 4 Кз 2 KI KO

К7КбК.5К4КзК2К.1Ко К7КбК5К4 зК2К1Ко Кб Kj К4 Кз К7КбК5К4КзКгК, Ко К7КбК5К4.КзК2К1Ко 4 3 2 К7КбК5К4КзК2К1Ко 71% К5К4 1 К7 Kg Kj К4 Кз 2 1 К7 Kg KS К Кз KO К7 Kg KS К4 Кз К.2 KI KO К Кб KS К4 Кз К2 KI KO К7КбК5К4КзК2К,Ко К7 Кб 5 K2Ki KO К7 Кб К5 К Кз 2 KO К7 Kg Kj К Kj К2 KI Kg

ХХХХХХХХ

Корректор А. Обручар

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

Изобретение относится к области вычислительной техники и может быть использовано для контроля и диагностики полупроводниковой оперативной памяти микро-ЭВМ. Целью изобретения является повышение быстродействия и надежности устройства. Устройство содержит счетчики, блок постоянной памяти, дешифраторы, регистры, арифметическо-логические блоки, коммутатор, мультиплексор, генератор, пульт управления, триггеры, формирователи, индикаторы, блок сравнения, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы НЕ, элементы И, И-НЕ, ИЛИ, блок оперативной памяти. 2 ил.. (Л

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Данилин Н.Н., Попель Л.М | |||

| Установка функционального контроля БИС ОЗУ Элекон-Ф-ЗУ | |||

| - Электронная промышленность, 1977, вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-12-30—Публикация

1983-06-06—Подача