Изобретение относится к радиотехнике, а именно к следящим системам управления и фильтрации, в частности к следящим фильтрам для выделения сигналов на фоне помех,

Цель изобретения - повышение точности системы.

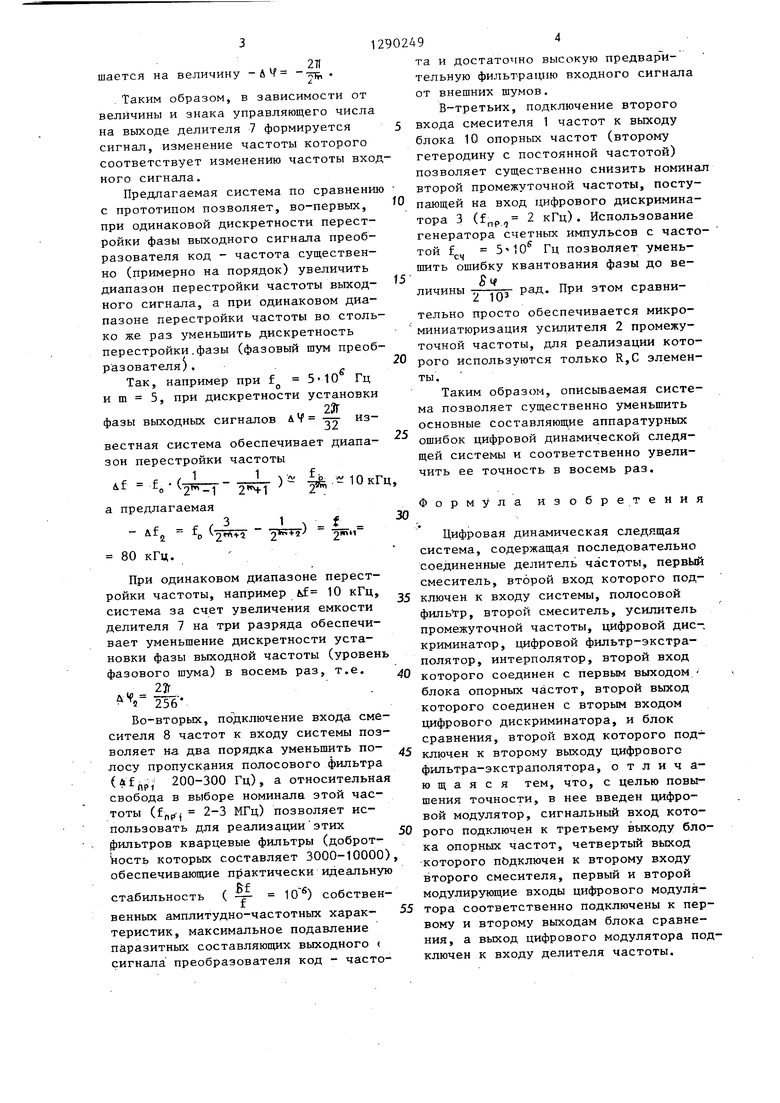

На фиг. 1 приведена блок-схема цифровой динамической следящей системы; на фиг. 2 - функциональная

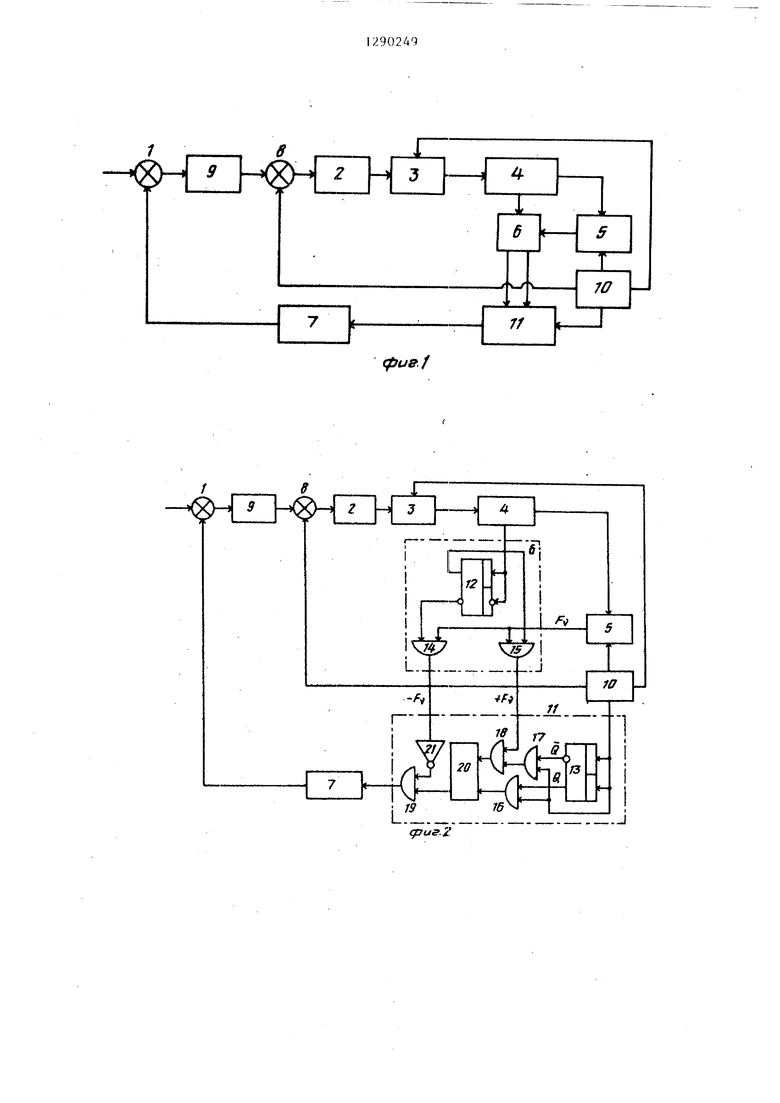

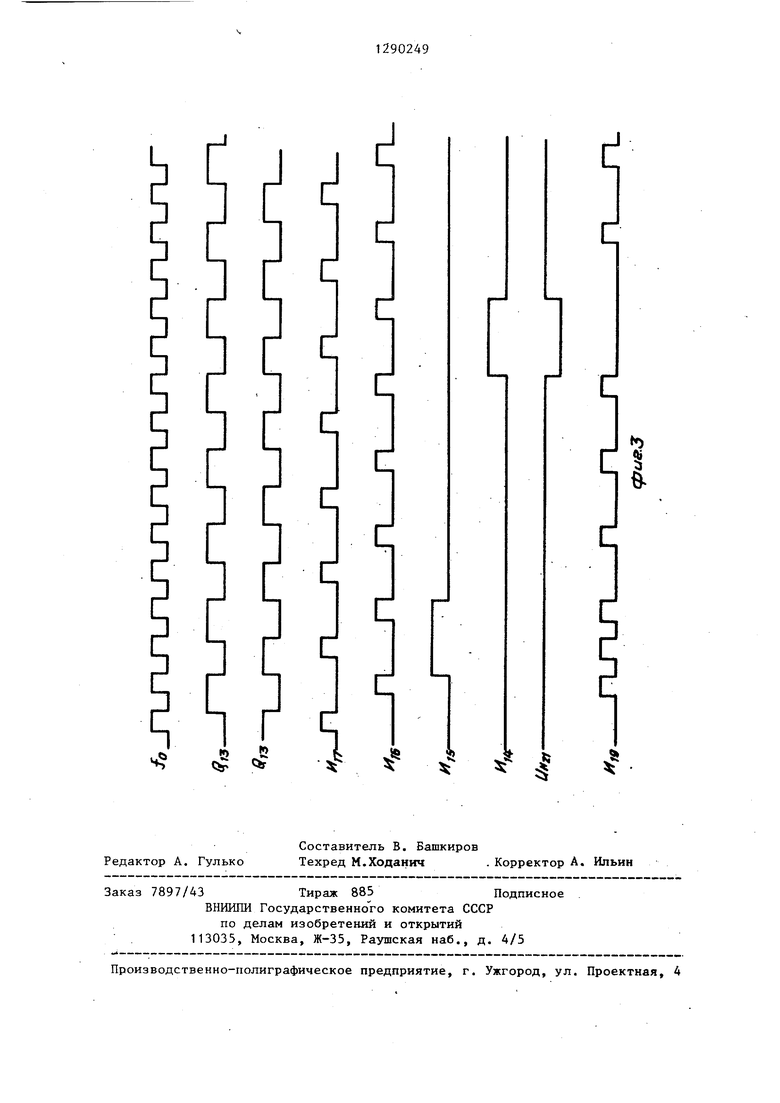

схема с примерной технической реализацией блока сравнения и цифрового модулятора; на фиг. 3 - временные диаграммы, поясняющие работу системы

Схема (фиг. 1 и 2) включает первый и второй смесители частот 1 и 8,усилитель промежуточной частоты 2, цифровой дискриминатор 3, цифровой фильтр-экстраполятор 4, интерполятор 5, блок сравнения 6, делитель 7, по- лосовой фильтр 9, блок опорных частот 10, цифровой модулятор 11, триггеры 12 и 13, элементы И 14-19, элемент ШШ 20 и инвертор 21.

Система работает следующим обра- зом.

Входной сигнал поступает на первый вход смесителя 1, на второй вход которого поступает сигнал обратной связи с выхода делителя 7 частоты, в результате чего на выходе полосового фильтра 9 выделяется сигнал второй промежуточной частоты , поступающий на первый вход смесителя 8, на второй вход которого с четвертого выхода блока 10 опорных частот поступает сигнал с постоянной частотой f fflMD- Рго результате перемножения этих сигналов на выходе усилителя 2 вьщеляется сигнал второй промежуточной частоты ,, , поступающий на вход цифрового фазового дискриминатора 3, на второй вход которого с второго выхода блока 10 опорных частот поступает сигнал эталон- ной промежуточной частоты fnpoo- На выходе дискриминатора 3 в цифровой форме выделяется величина рассогласования по фазе

Ч

1

сЛ13Г- 2l f

1

где fрц - частота счетных импульсов

После обработки величины + aNj в цифровом фильтре-экстраполяторе 4 модуль результирующего двоичного числа /4 выдается в интерполятор 5, на второй ВХОД; которого из блока 7 опорных частот поступает сигнал

с частотой

t

преобразующий это

число в поток управляющих импульсов

С„

с частотой F N. N. ха

рактеризует дискретность установки частоты интерполятора. Эти импульсы поступают в блок 6 сравнгння, куда одновременно с второго выхода цифрового фильтра-зкстраполятора 4 (знакового разряда) поступает сигнал о знаке рассогласования управляющего числа +N

Чпр

который в зависимости от

5 0

0 5 0 5

0

5

знака рассогласования с помощью триггера 12 открывает элемент И 14 (в случае отрицательного рассогласования) или элемент И 15 (в случае положительного рассогласования N) . При этом управляющие импульсы F поступают на соответствующие модулирующие входы цифрового фазового модулятора 11, на сигнальный вхо/з; которого (на вход триггера 13 и элементов И 16 и 17) с выхода блока 10 опорных частот поступает сигнал с частотой f . В результате на выходе элементов И 16 и 17 вьщеляются импульсы с частотой следования f /2, сдвинутые по фазе друг относительно друга на Л . И 1пульсы с выхода элемента, И 16 через элемент ИЛИ 20 проходят на вход элемента И 19 непрерывно, а импульсы с выхода элемента И 17 проходят -через элемент И 18 и элемент ИЛИ 20 только в тех случаях, когда на второй вход элемента И 18 поступает управляющий импульс +F jj с вькода элемента И 15 блока 6. Таким образом, при наличии на модулирующем входе модулятора 11 положительного управляющего импзшьса +F на его выход через элемент И 19 проходит дополнительный импульс, в результате чего фаза выходного сигнала делителя 7 увеличи- 27Г вается на величину + uif - , где

m - число разрядов делителя часто- ты 7.

При поступлении с выхода элемента И 14 блока 6 на модулирующий вход модулятора 11 управляющего импульса -Fji, соответствующего отрицательному рассогласованию, на выходе инвертора 21 создается нулевой потенциал, запирающий на это время элемент И 19, что приводит к исключению очередного импульса И 16, поступающего на вход делителя. 7. В этом случае фаза выходного сигнала делителя 7 уменьшается на величину

-.

. Таким образом, в зависимости от величины и знака управляющего числа на выходе делителя 7 формируется сигнал, изменение частоты которого соответствует изменению частоты входного сигнала.

Предлагаемая система по сравнению с прототипом позволяет, во-первых, при одинаковой дискретности перестройки фазы выходного сигнала преобразователя код - частота существенно (примерно на порядок) увеличить диапазон перестройки частоты выходного сигнала, а при одинаковом диапазоне перестройки частоты во столько же раз уменьшить дискретность перестройки.фазы (фазовый шум преоб- р&зователя), .

Так, например при f и m 5, при

5-10° Гц

дискретности установки

фазы выходных сигналов 4V - известная система обеспечивает диапазон перестройки частоты

.f - а предлагаемая

) -.

f, кГц.

ь

+ 2

При одинаковом диапазоне перестройки частоты, например &f 10 кГц, система за счет увеличения емкости делителя 7 на три разряда обеспечивает уменьшение дискретности установки фазы выходной частоты (уровень фазового шума) в восемь раз, т.е.

10 - 23Г 256 Во-вторых, подключение входа смесителя 8 частот к входу системы позволяет на два порядка уменьшить полосу пропускания полосового фильтра ( 200-300 Гц), а относительная свобода в выборе номинала этой частоты (fftp 2-3 МГц) позволяет использовать для реализации этих фильтров кварцевые фильтры (доброт- ость которых составляет 3000-10000) обеспечивающие практически идеальную

стабильность ( - 10 ) собствен- венных амплитудно-частотных харак- теристик, максимальное подавление паразитных составляющих выходного сигнала преобразователя код - часто

та и достатоггно высокую предварительную фильтрацию входного сигнала от внешних шумов.

В-третьих, подключение второго входа смесителя 1 частот к выходу блока 10 опорных частот (второму гетеродину с постоянной частотой) позволяет существенно снизить номинал второй промежуточной частоты, поступающей на вход цифрового дискриминатора

3 (f

ПР-Т

2 кГц). Использование

генератора счетных импульсов с частотой f З Ю Гц позволяет уменьшить ошибку квантования фазы до не- S

личины т;-rjrrj- рад. При этом сравнительно просто обеспечивается микроминиатюризация усилителя 2 промежуточной частоты, для реализации которого используются только R,C элементы.

Таким образом, описываемая система позволяет существенно уменьшить основные составляющие аппаратурных ошибок цифровой динамической следящей системы и соответственно увеличить ее точность в восемь раз.

30

Ф

о р м у л а

из обретения

5

0

5

0

5

Цифровая динамическая следящая система, содержащая последовательно соединенные делитель частоты, первый смеситель, второй вход которого подключен к входу системы, полосовой филь тр, второй смеситель, усилитель промежуточной частоты, цифровой дис-. криминатор, цифровой фильтр-экстра- полятор, интерполятор, второй вход которого соединен с первым выходом - блока опорных частот, второй выход которого соединен с вторым входом цифрового дискриминатора, и блок сравнения, второй вход которого подключен к второму выходу цифрового фильтра-экстраполятора, отличающаяся тем, что, с целью повышения точности, в нее введен цифровой модулятор, сигнальный вход которого подключен к третьему выходу блока опорных частот, четвертый выход которого пЬдключен к второму входу второго смесителя, первый и второй модулирующие входы цифрового модулятора соответственно подключены к первому и второму выходам блока сравнения, а выход цифрового модулятора подключен к входу делителя частоты.

(pue.f

(ffue.Z

14 Е С О

5

Редактор А. Гулько

Составитель В. Башкиров

Техред М.Ходанич . Корректор А. Ильин

Заказ 7897/43Тираж 885Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

d

h

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая динамическая следящая система | 1981 |

|

SU962846A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU890358A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368857A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368856A1 |

| Цифровая динамическая следящая система | 1985 |

|

SU1285428A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Следящий измеритель частоты | 1978 |

|

SU766024A1 |

| ИЗМЕРИТЕЛЬ СКОРОСТИ | 2011 |

|

RU2492505C1 |

| ПАССИВНЫЙ КВАНТОВЫЙ СТАНДАРТ ЧАСТОТЫ | 1984 |

|

SU1241959A1 |

| УСТРОЙСТВО ДЛЯ СОЗДАНИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛОКАЦИОННЫМ СТАНЦИЯМ | 2006 |

|

RU2329603C2 |

Изобретение относится к следящим системам управления и фильтрации. Целью изобретения является повышение точности системы управления. В цифровую динамическую следящую систему введен цифровой модулятор, сигнальный вход которого подключен к третьему выходу блока опорных частот, четвертый выход которого подключен к второму входу второго смесителя, первый и второй модулирующие входы модулятора подключены к соответствующим выходам блока сравнения-, выход модулятора - к входу делителя частоты, а второй вход смесителя является входом системы. 3 ил. (Л Ю 4ib СО

| ЦИФРОВАЯ ДИНАМИЧЕСКАЯ СЛЕДЯЩАЯ СИСТЕМА | 0 |

|

SU348979A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для выбора требуемого фильтра | 1972 |

|

SU444150A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU890358A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-02-15—Публикация

1985-05-15—Подача