1

Изобретение относится к автоматике, а именно к следящим системам управления и фильтрации, в частности к следящим, фильтрам для выделения сигналов на фоне помех.

Известна цифровая динамическая следящая система, содержащая в качестве преобразователя код-частота управляемый цифровой делитель частоты с переменным коэффициентом деления 1 .

Недостатком данного устройства является невысокая точность работы при увеличении диапазона перестройки частоты преобразователя код-частота, так как при этом возрастает ошибка дискретности установки частоты, уменьшение которой за счет увеличения коэффициента деления управляемого делителя уменьшает диапазон перестройки частоты преобразователя код-частота.

Наиболее близкой к предлагаемой является цифровая динамическая следящая система, содержащая последовательно соединенные смеситель частот, первый вход которого подключен к входу системы, усилитель промежуточной частоты, цифровой дискриминатор, цифровой фильтр-экстраполятор.

интерполятор и блок сравнения, второй вход которого подключен к второму выходу цифрового фильтра-экстраполятора, а выход - к первому входу первого делителя частоты, второй вход которого соединен с первым выходом блока опорных частот,-вторым выходом подключенного к второму входу интерполятора 2.

10

Известная цифровая динамическая следящая система характеризуется недостаточной точностью, обусловленной относительно высоким уровнем паразитной модуляции сигнала на вы15ходе полосового фильтра, выходом соединенного с вторым входом смесителя, за счет неидеальности работы аналогового смесителя и полосового фильтра.

20

Цель изобретения - повышение точ мости системы.

Поставленная цель достигается тем, что в нее введены первый цифровой фазовращатель и последовательно

25 соединенные второй цифровой фазовращатель, дешифратор, блок совпадений и второй делитель частоты, выход которого подключен- к второму входу смесителя частот, причем выход

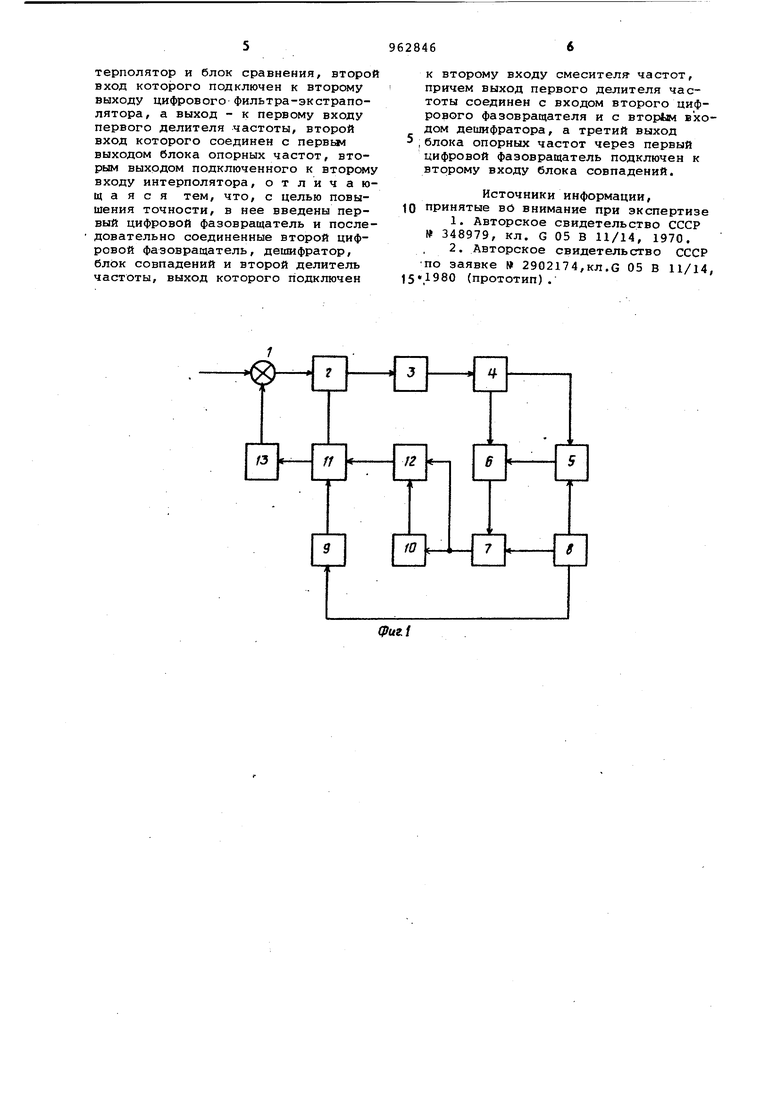

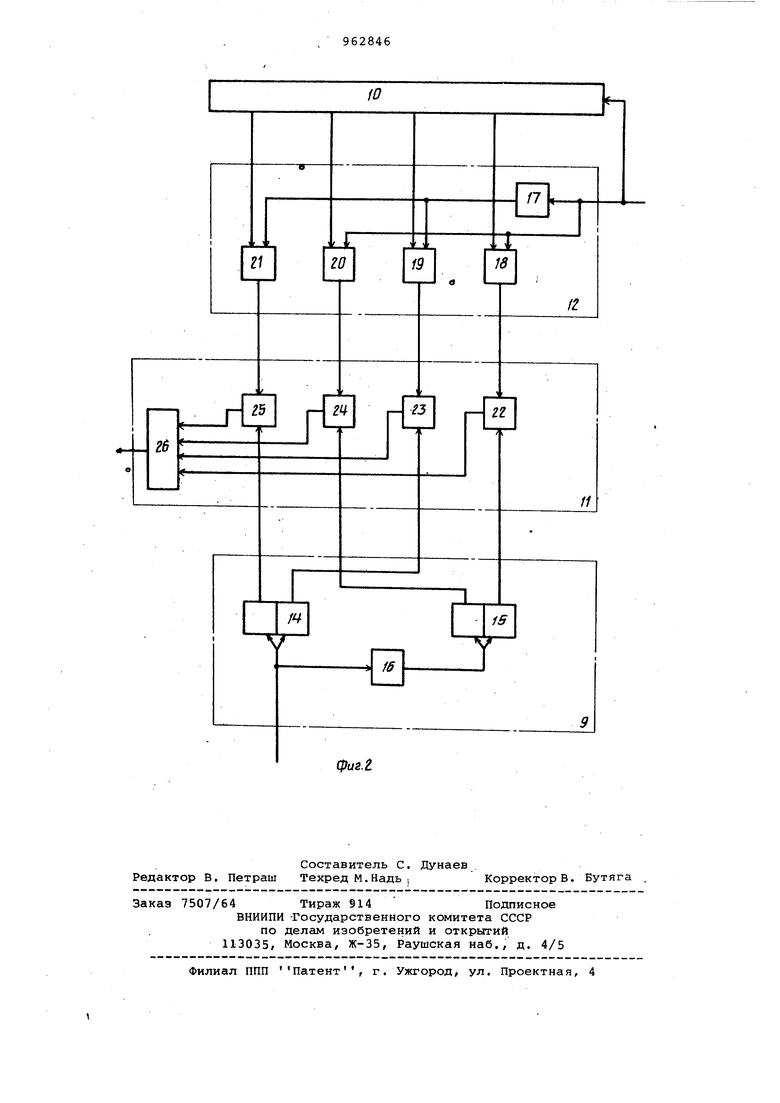

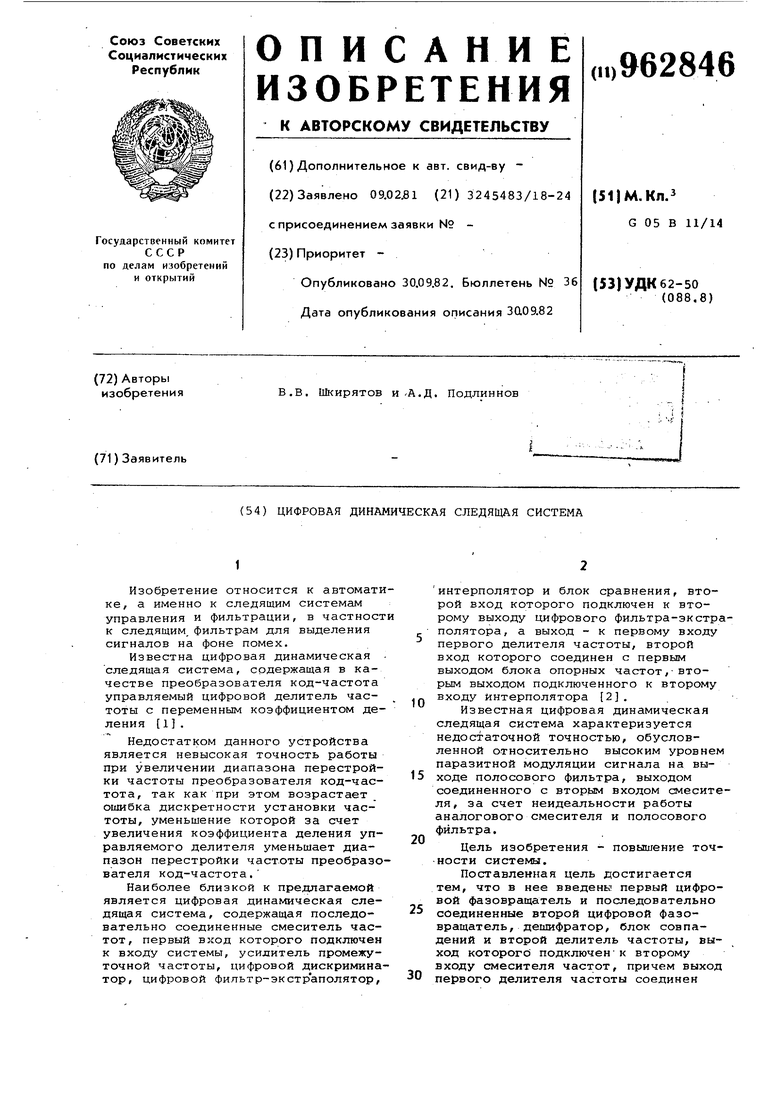

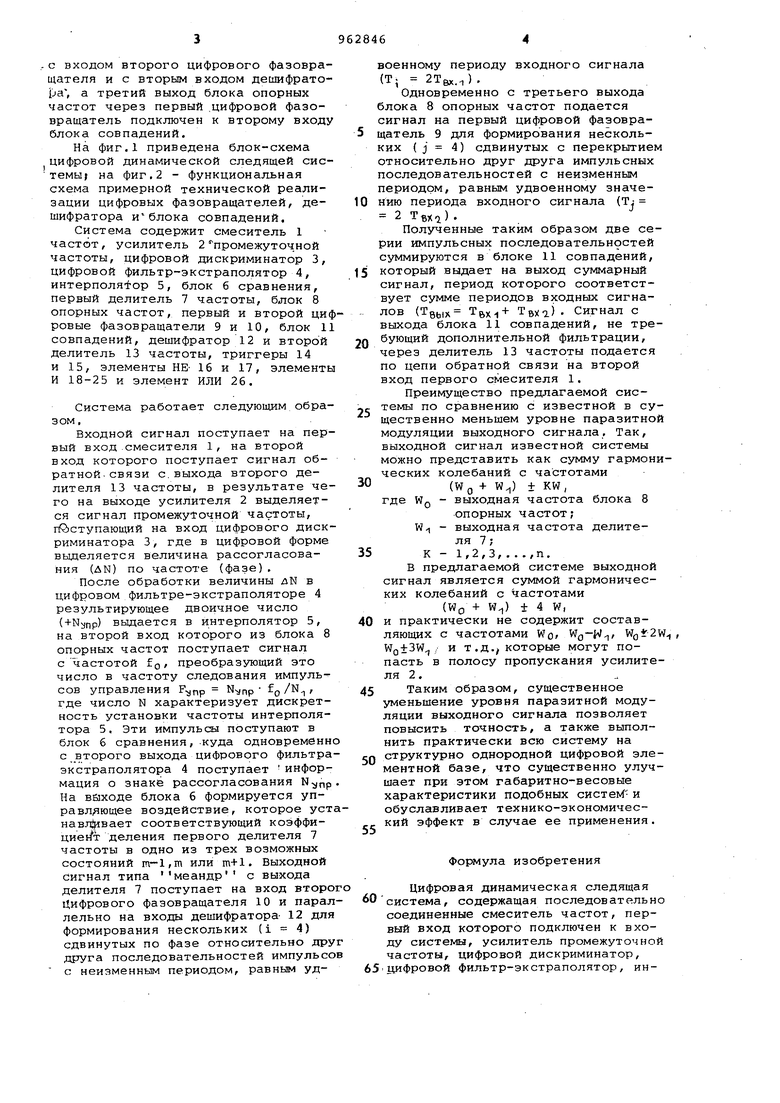

30 первого делителя частоты соединен с входом второго цифрового фазовра щателя и с вторым входом дешифрато ра, а третий выход блока опорных частот через первый .цифровой фазовращатель подключен к второму вход блока совпадений. На фиг.1 приведена блок-схема цифровой динамической следящей сис темы на фиг.2 - функциональная схема примерной технической реализации цифровых фазовращателей, дешифратора иблока совпадений. Система содержит смеситель 1 частот, усилитель 2промежуточ.ной частоты, цифровой дискриминатор 3, цифровой фильтр-экстраполятор 4, интерполятор 5, блок 6 сравнения, первый делитель 7 частоты, блок 8 опорных частот, первый и второй ци ровые фазовращатели 9 и 10, блок 1 совпадений, дешифратор 12 и второй делитель 13 частоты, триггеры 14 и 15, элементы НЕ 16 и 17, элемент И 18-25 и элемент ИЛИ 26. Система работает следующим обра зом. Входной сигнал поступает на пер вый вход .смесителя 1, на второй вход которого поступает сигнал обратной- связи с. выхода второго делителя 13 частоты, в результате че го на выходе усилителя 2 выделяется сигнал промежуточной частоты, поступающий на вход цифрового диск риминатора 3, где в цифровой форме выделяется величина рассогласования (ДЫ) по частоте (фазе), После обработки величины лН в цифровом фильтре-экстраполяторе 4 результирующее двоичное число (+Ыч)пр) выдается в интерполятор 5, на второй вход которого из блока 8 опорных частот поступает сигнал с частотой fg, преобразующий это число в частоту следования импульсов управления Ns,np где число N характеризует дискретность установки частоты интерполятора 5, Эти импульсы поступают в блок 6 сравнения, куда одновременн с второго выхода цифрового фильтра экстраполятора 4 поступает информация о знаке рассогласования На ваходе блока 6 формируется упpaвл ющee воздействие, которое уст навл 1вает соответствующий коэффицие т деления первого делителя 7 частоты в одно из трех возможных состояний т-1,т или т+1. Выходной сигнал типа меандр с выхода делителя 7 поступает на вход второ Цифрового фазовращателя 10 и парал лельно на входы дешифратора- 12 для формирования нескольких (i 4) сдвинутых по фазе относительно дру друга последовательностей импульс с неизменным периодом, равным удвоенному периоду входного сигнала (Т- 2Твх.), Одновременно с третьего выхода блока 8 опорных частот подается сигнал на первый цифровой фазовращатель 9 для формирования нескольких (j 4) сдвинутых с перекрытием относительно друг друга импульсных последовательностей с неизменным периодом, равным удвоенному значению периода входного сигнала 2 Твха). Полученные таким образом две серии импульсных последовательн9стей суммируются в блоке 11 совпадений, который выдает на выход суммарный сигнал, период которого соответствует сумме периодов входных сигналов (Теь1х Те,х1+ Твха)- Сигнал с выхода блока 11 совпадений, не требующий дополнительной фильтрации, через делитель 13 частоты подается по цепи обратной связи на второй вход первого смесителя 1. Преимущество предлагаемой системы по сравнению с известной в существенно меньшем уровне паразитной модуляции выходного сигнала. Так, выходной сигнал известной системы можно представить как сумму гармонических колебаний с частотами (Wg + W) ± KW, где WQ - выходная частота блока 8 опорных частот; W-, - выходная частота делителя 7; К - 1,2,3,...,п, В предлагаемой системе выходной сигнал является суммой гармонических колебаний с частотами (WQ + W) +4 W, и практически не содержит составляющих с частотами Wo/ WQ-H-,, Woir2W-, , WQ±3W / и т.д.которые могут попасть в полосу пропускания усилителя 2 . Таким образом, существенное уменьшение уровня паразитной модуляции выходного сигнала позволяет повысить точность, а также выполнить практически всю систему на структурно однородной цифровой элементной базе, что существенно улучшает при этом габаритно-весовые характеристики подобных систеМ и обуславливает технико-экономический эффект в случае ее применения. Формула изобретения Цифровая динамическая следящая система, содержащая последовательно соединенные смеситель частот, первый вход которого подключен к входу системы, усилитель промежуточной частоты, цифровой дискриминатор, uf Фpoвofl фильтр-экстраполятор, интерполятор и блок сравнения, второй вход которого подключен к второму выходу цифрового фильтра-экстраполятора, а выход - к первому входу первого делителя частоты, второй вход которого соединен с первым выходом блока опорных частот, вторым выходом подключенного к второму входу интерполятора, отличающаяся тем, что, с целью повышения точности, в нее введены первый цифровой фазовращатель и последовательно соединенные второй цифровой фазовращатель, дешифратор, блок совпадений и второй делитель частоты, выход которого подключен

к второму входу смесителя- частот, причем выход первого делителя частоты соединен с входом второго цифрового фазовращателя и с вторЬм входом дешифратора, а третий выход 5,блока опорных частот через первый цифровой фазовращатель подключен к второму входу блока совпадений.

Источники информации, 10 принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 348979, кл. G 05 В 11/14, 1970. , 2. Авторское свидетельство СССР по заявке 2902174,кл.С 05 В 11/14, 15,1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая динамическая следящая система | 1980 |

|

SU890358A1 |

| Цифровая динамическая следящая система | 1985 |

|

SU1290249A1 |

| Следящий измеритель частоты | 1978 |

|

SU766024A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368857A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368856A1 |

| Устройство синхронизации каналов связи | 1979 |

|

SU809624A1 |

| Устройство для фазовой автоподстройки частоты | 1977 |

|

SU680140A1 |

| Цифровая динамическая следящая система | 1985 |

|

SU1285428A1 |

| Следящий приемник | 1983 |

|

SU1092734A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

0-

Авторы

Даты

1982-09-30—Публикация

1981-02-09—Подача