Изобретение относится к автоматике и вычислительной технике и может быть ис- пользовано при построении устройств, реализующих произвольные системы булевых функций.

Цель изобретения - упрощение устройства за счет сокращения обьема оборудования.

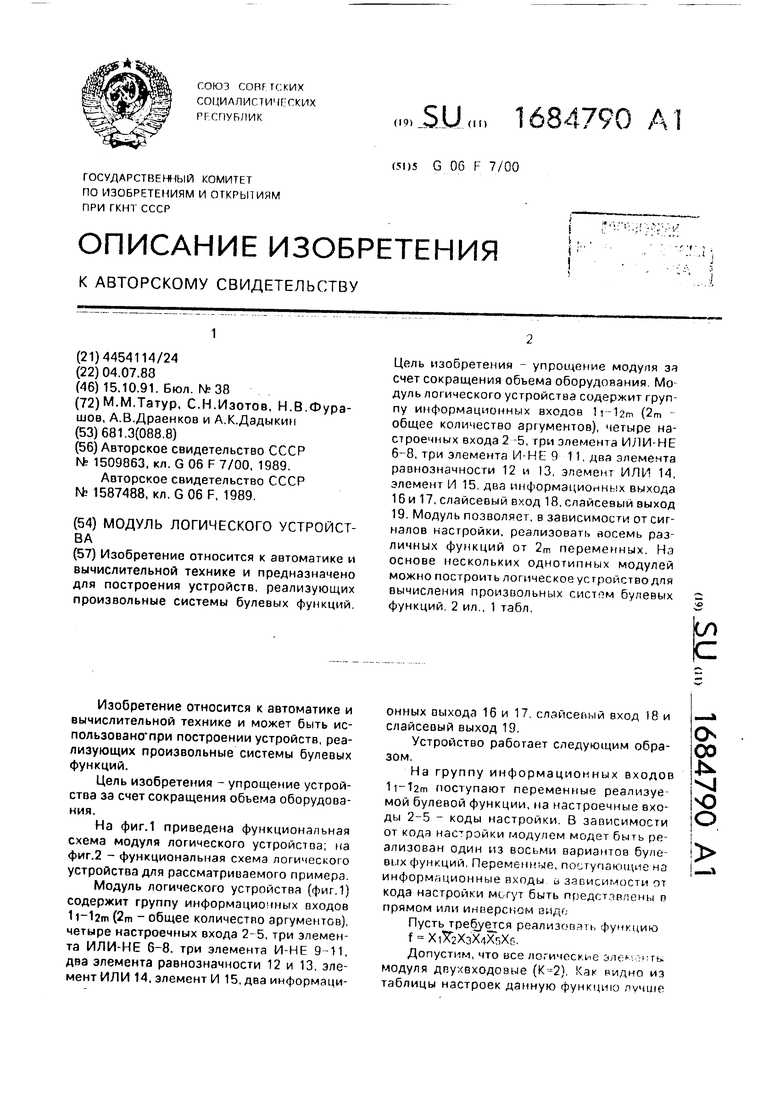

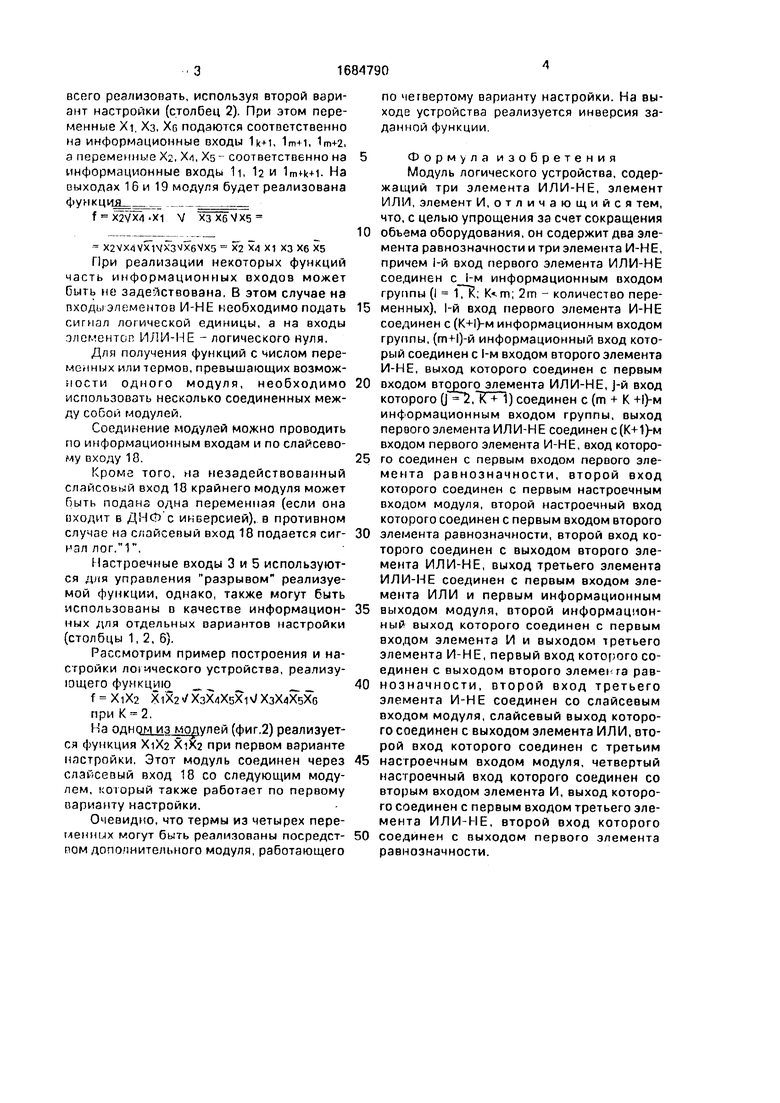

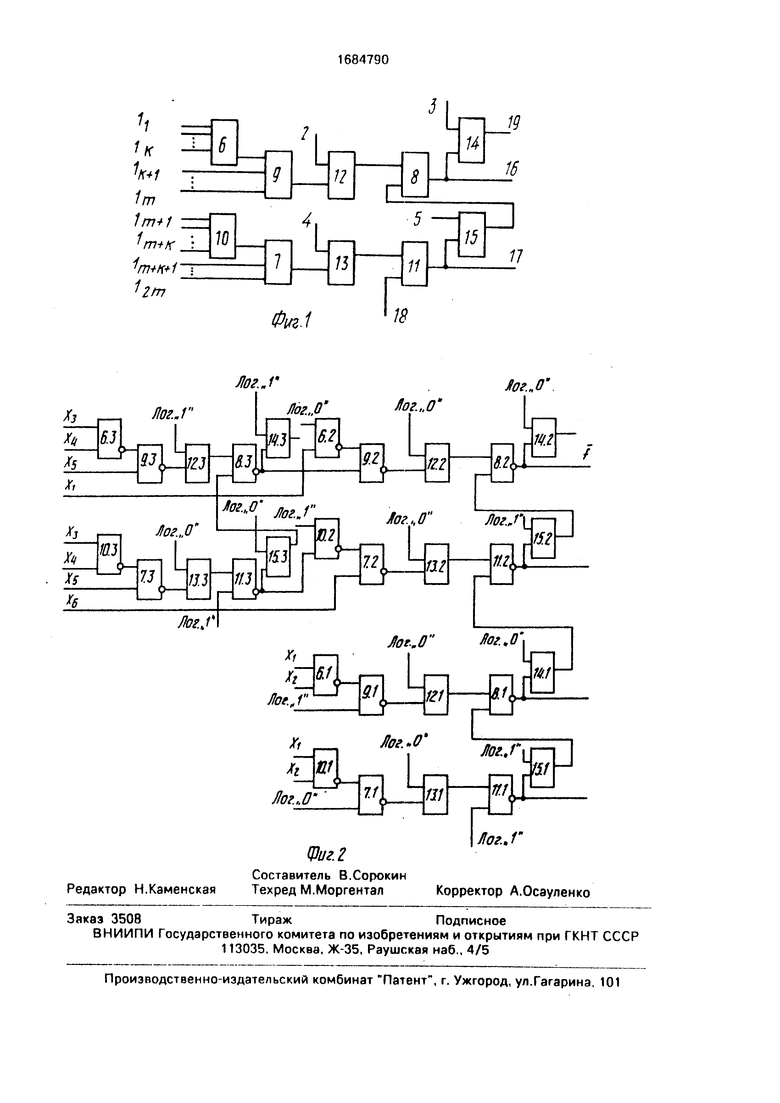

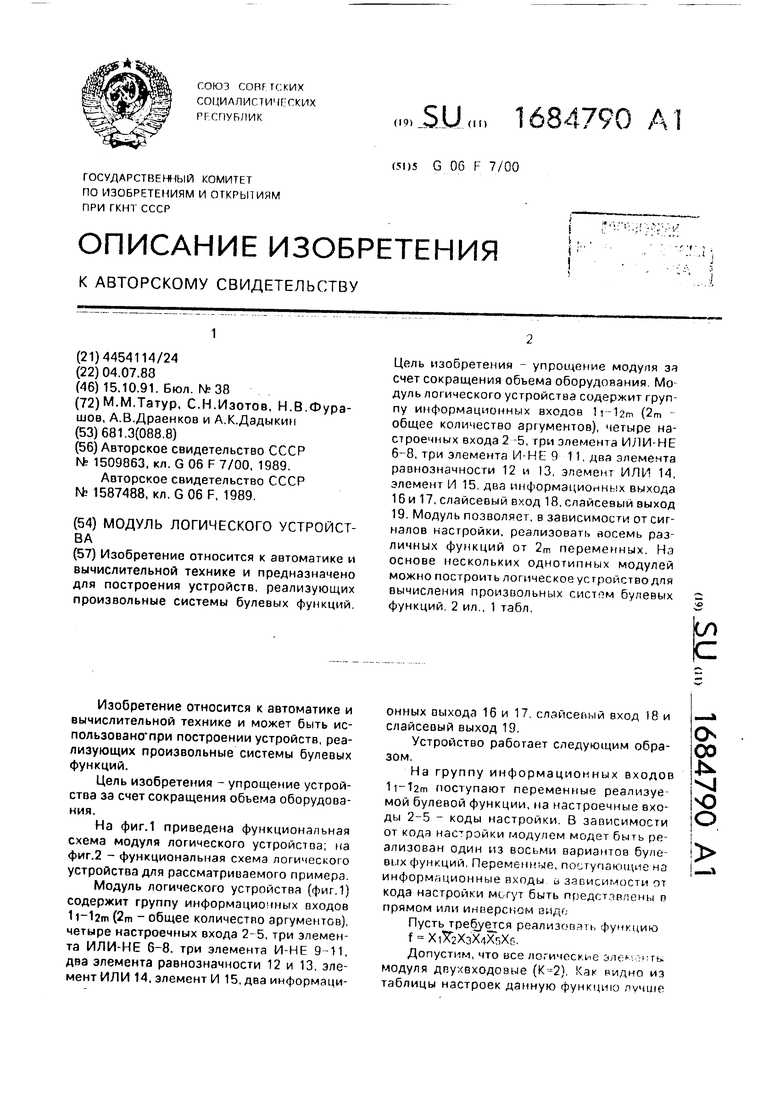

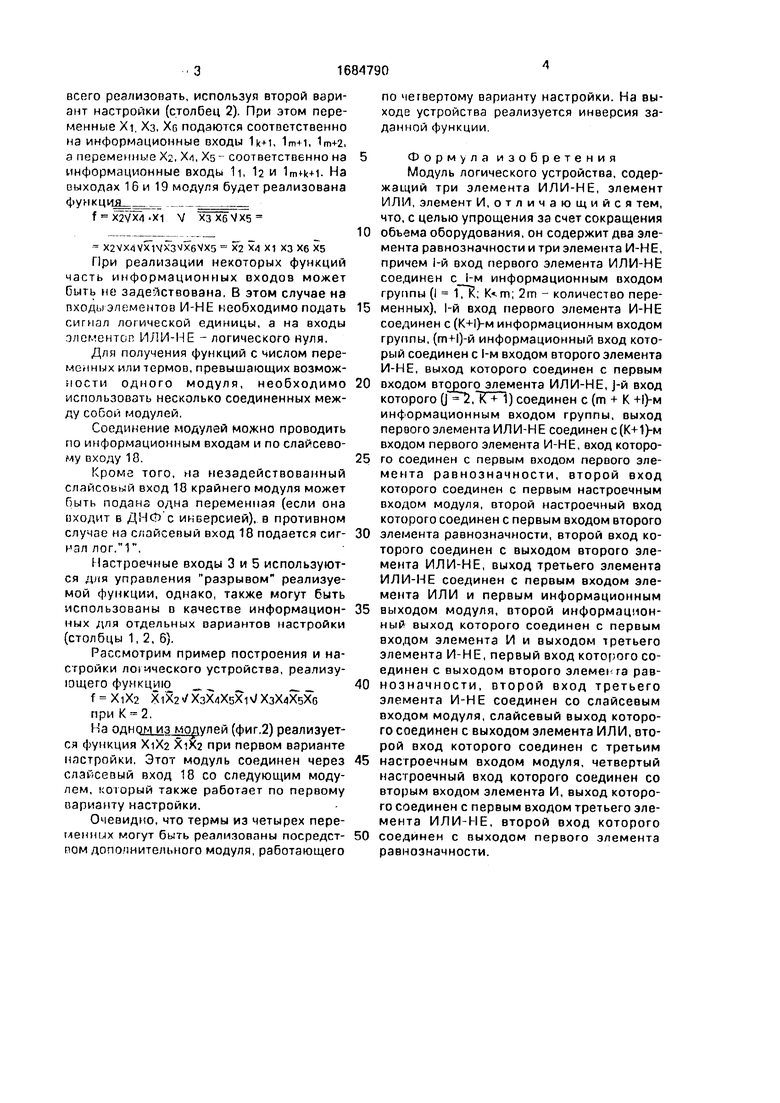

На фиг.1 приведена функциональная схема модуля логического устройства, на фиг.2 - функциональная схема логического устройства для рассматриваемого примера

Модуль логического устройства (фиг 1) содержит группу информационных входов 1 (2m - общее количество аргументов) четыре настроечных входа 2-5, три элемента ИЛИ-НЕ 6-8. три элемента И-НЕ 9-11, два элемента равнозначности 12 и 13, элемент ИЛИ 14, элемент И 15, два информационных выхода 16 и 17 слайсевый вход 18 и слайсевый выход 19

Устройство работает следующим образом

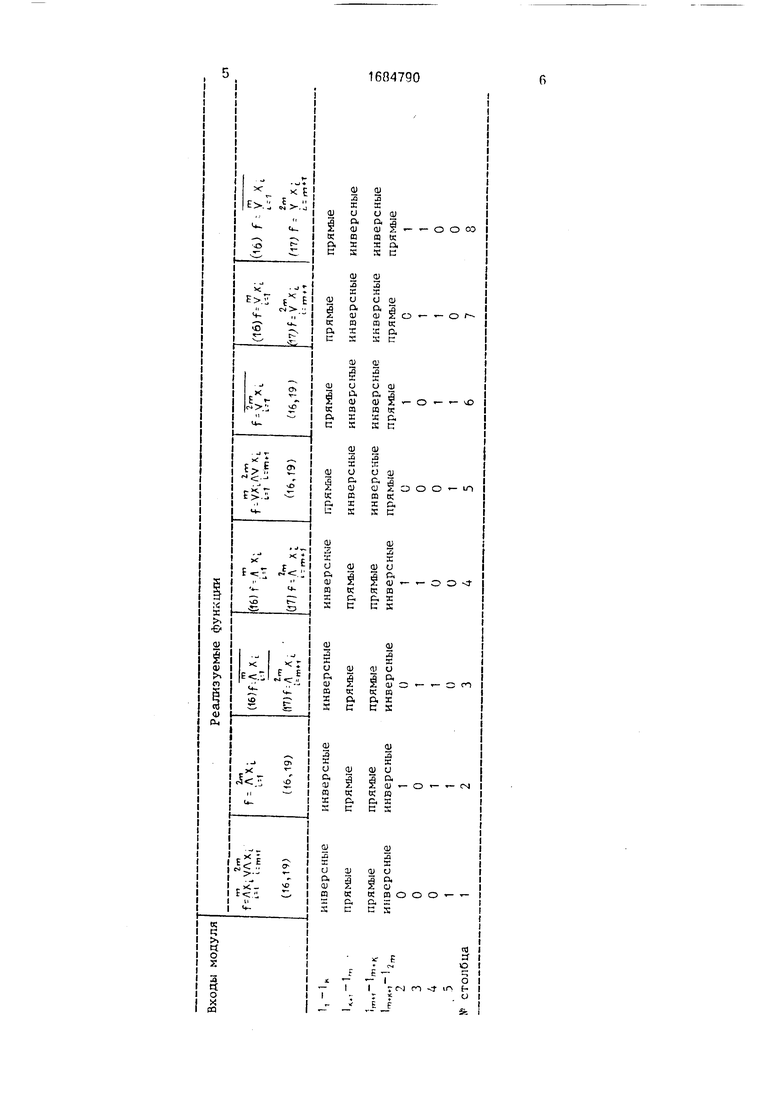

На группу информационных входов поступают переменные реализуе мой булевой функции, на настроечные входы 2-5 - коды настройки В зависимости от кода настройки модулем модет быть ре ализован один из восьми вариантов буле вих функций Переменные, поступающие на информпционные входы ь зависимости от кода настройки мегут быть предсттрлены п прямом или инперсьом видг

Пусть требуется реализовать функцию

f Х,Т2ХзХ4Х 5Х5

Допустим, что все логические эле гь. модуля двухвходозые () Как видно из таблицы настроек данную функцию лучше

О 00

4 1 О О

всего реализовать, используя второй вариант настройки (столбец 2). При этом переменные Xi. Хз, XG подаются соответственно на информационные входы 1k+i, Чт-м, 1т-кг, а переменные Х2. X/i, Хб - соответственно на информационные входы 1i, 12 и Imfk-n. На выходах 16 и 19 модуля будет реализована функция

f V ХЗ Х6 V Х5

X2VX4VX1VX3VX 6VX5 Х2 Х4 Х1 ХЗ Х6 Х5

При реализации некоторых функций часть информационных входов может Быть не задействована. В этом случае на пходы элементов И-НЕ необходимо подать сигнал логической единицы, а на входы элементов ИЛИ-НЕ - логического нуля.

Для получения функций с числом переменных или термов, превышающих возможности одного модуля, необходимо использовать несколько соединенных между собой модулей.

Соединение модулей можно проводить по информационным входам и по слайсево- му входу 18.

Кроме того, на незадействованный слайсовый вход 18 крайнего модуля может быть подана одна переменная (если она входит в ДЬЮ с инверсией), в противном случае на слайсевый вход 18 подается сиг- мал лог.1.

Настроечные входы 3 и 5 используются для управления разрывом реализуемой функции, однако, также могут быть использованы в качестве информационных для отдельных вариантов настройки (столбцы 1,2,6).

Рассмотрим пример построения и настройки логического устройства, реализующего функцию

f XiX2 Х1Х2 /Х3Х4Х5Х1 /ХзХ4Х5Хб

при К 2.

На одном из модулей (фиг.2) реализуется функция XiXa XiX2 при первом варианте настройки. Этот модуль соединен через слзйсеаый вход 18 со следующим модулем, коюрый также работает по первому варианту настройки.

Очевидно, что термы из четырех переменных могут быть реализованы посредст- пом дополнительного модуля, работающего

по четвертому варианту настройки. На выходе устройства реализуется инверсия заданной функции

Формула изобретения

Модуль логического устройства, содержащий три элемента ИЛИ-НЕ, элемент ИЛИ, элемент И, отличающийся тем, что, с целью упрощения за счет сокращения

объема оборудования, он содержит два элемента равнозначности и три элемента И-НЕ, причем 1-й вход первого элемента ИЛИ-НЁ соединен с 1-м информационным входом группы (I К.т; 2т - количество переменных), 1-й вход первого элемента И-НЕ соединен с (К+1)-м информационным входом группы, (гл+1)-й информационный вход который соединен с 1-м входом второго элемента И-НЕ, выход которого соединен с первым

входом второго элемента ИЛИ-НЕ, J-й вход которого О 2,) соединен с (т + К +)-м информационным входом группы, выход первого элемента ИЛИ-НЕ соединен с(К+1)-м входом первого элемента И-НЕ, вход которого соединен с первым входом первого элемента равнозначности, второй вход которого соединен с первым настроечным входом модуля, второй настроечный вход которого соединен с первым входом второго

элемента равнозначности, второй вход которого соединен с выходом второго элемента ИЛИ-НЕ, выход третьего элемента ИЛИ-НЕ соединен с первым входом элемента ИЛИ и первым информационным

выходом модуля, второй информационный выход которого соединен с первым входом элемента И и выходом третьего элемента И-НЕ, первый вход которого соединен с выходом второго элемента равнозначности, второй вход третьего элемента И-НЕ соединен со слайсевым входом модуля, слайсевый выход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с третьим

настроечным входом модуля, четвертый настроечный вход которого соединен со вторым входом элемента И, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого

соединен с выходом первого элемента равнозначности.

Лог.,1

MJ

A

9J

W

8.1

,,0

Ш

92

Лог.,.0

Лог.,.О

ь

...

Г

Е

Jtoj

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1985 |

|

SU1290289A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1684792A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1320808A1 |

| Универсальный логический модуль | 1986 |

|

SU1319019A1 |

| Программируемое устройство | 1991 |

|

SU1789979A1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Универсальный логический модуль | 1984 |

|

SU1218375A1 |

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1833860A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1681302A1 |

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для построения устройств, реализующих произвольные системы булевых функций Цель изобретения - упрощение модуля за счет сокращения обьема оборудования Мо дуль логического устройства содержит труп пу информационных входов Ь 12m (2m - общее количество аргументов), четыре настроечных входа 2 5, гри элемента ИЛИ-НЕ 6-8, три элемента И НЕ 9 11 два элемента равнозначности 12 и 13, элемент ИЛИ 14, элемент И 15 два информационных выхода 16 и 17, слайсевый вход 18, слайсевыи выход 19 Модуль позволяет, в зависимости от сигналов настройки, реализовал, восемь различных функций от 2т переменных Но основе нескольких однотипных модулей можно построить логическое устройство для вычисления произвольных систем булевых функций 2 ил , 1 табл (Л С

г //

Ак,1

r-zi

И /Гр/l

Лог.,О

|/..г

Щи г. г

Составитель В.Сорокин Редактор Н.Каменская Техред М.МоргенталКорректор А.Осауленко

Яог..О

L

nrw -л/Ць

./

г-, rff/

gbL

|/..г

| Устройство для вычисления систем логических функций | 1987 |

|

SU1509863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программируемое логическое устройство | 1988 |

|

SU1587488A1 |

Авторы

Даты

1991-10-15—Публикация

1988-07-04—Подача