Изобретение относится к вычислительной технике и может быть ис- пользовано в арифметических устройствах цифровых вьиислительных машин и систем.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения условий

для умножения двоичных чисел в ДОПОЛ

нительных кодах с произвольными знаками.

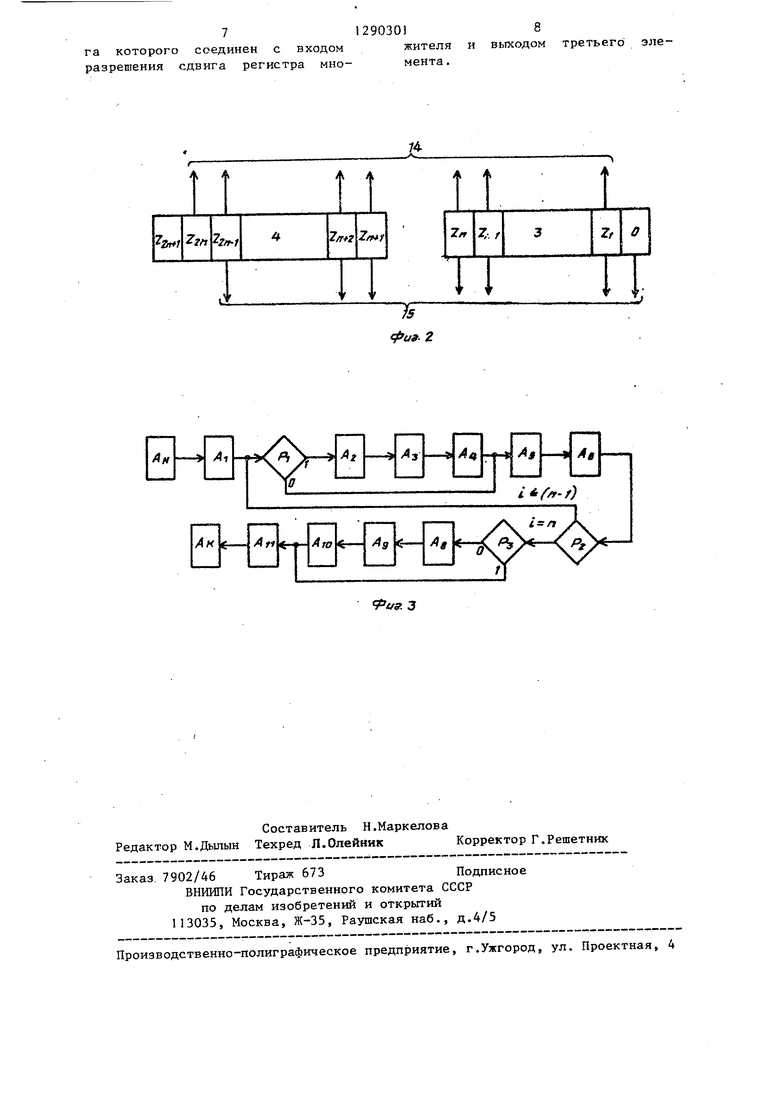

На фиг.1 приведена функциональная схема устройства для умножения; на фиг.2 - схема выходов результата при умножении целых или дробных чисел с фиксированной запятой; на фиг. 3 - граф алгоритма работы блока микропрограммного управления.

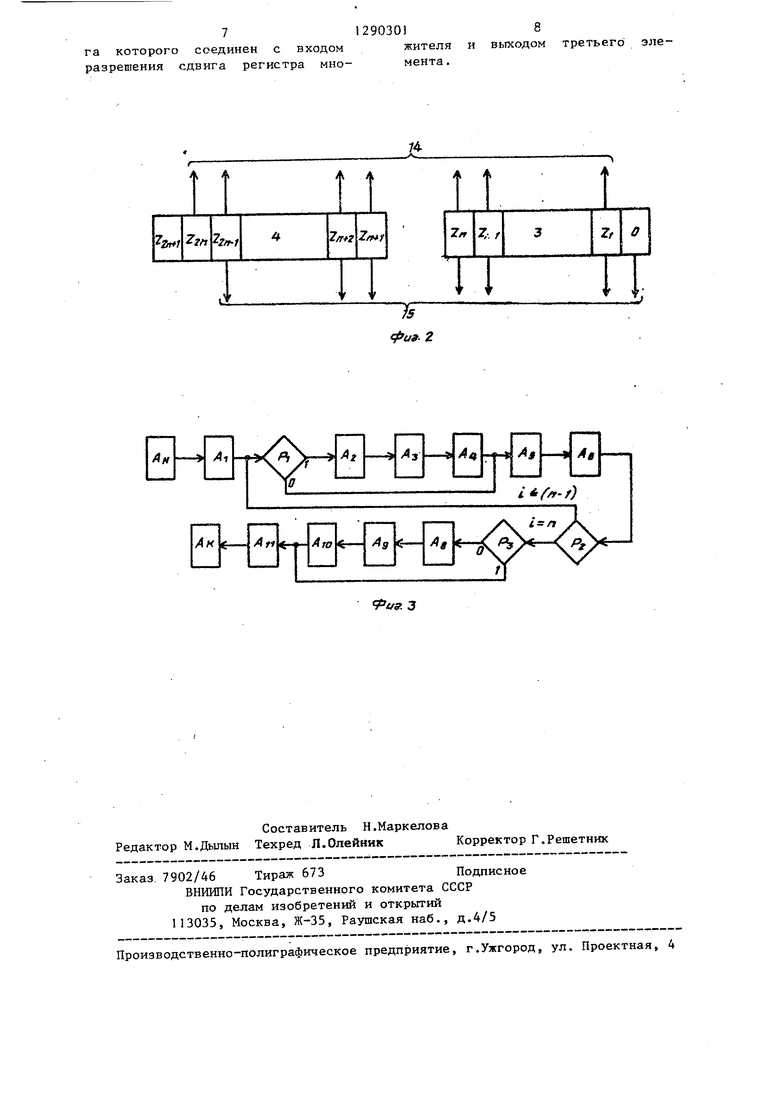

Устройство для у «1ножения (фиг . 1 и 2J содержит счетчик 1, блок 2 микропрограммного управления, регистр 3 множителя, регистр А результата, сумматор 5, регистр 6 множимого, элементы ИЛИ 7-9, вход 10 за- пуска устройства, выход 11 признака окончания операции умножения, входы 12-13 множимого и множителя соответственно, выход 14 результата при умножении целых двоичных чисел, вы- ход 15 результата при умножении дробных чисел с фиксированной запятой.

Устройство для .умножения двоичных чисел в дополнительных кодах реализу ет следующий алгоритм:

х .у„; х. О (I)

Z х-у;

У„ (у м 2 ;х «. О,

м

где X - числовое значение множителя; у - числовое значение множимого: Z - числовое значение произведения;

Хд- дополнительный код множителя; у - модифицированный дополнительный код множимого; Z - модифицированный дополнительШз1й код произведения; (-у) - модифицированный дополнительньй код величины (-у) т.е. числового значения множимого с обратным знаком; h - разрядность двоичных чисел

X, у.

Произведение z Х У является 2м- разрядным двоичным числом.

Устройство обрабатьшает двоичные числа с фиксированной запятой в дополнительном коде. .

Фо)эмула (I) соответствует алгоритму обработки целых двоичных чисел. Если использовать дробные числа с фиксированной запятой, то произведе- ние в дополнительных кодах целых и дробных значений сомножителей отличается только сдвигом на один разряд;

целое число z

4ti

1л-с -z, ;

дробнре число z z .. ,.

Так как процессы умножения целых и дробных чисел одинаковы , то описание устройства дается для случая целых двоичных чисел.

Введение модифицированного дополнительного кода двоичного числа приводит к увеличению разрядности чисел на единицу. В процессе умножения на каждом цикле вычислений производится алгебраическое сложение накоплений суммы частичных произведений со значением множителя, если состоянием разряда множителя, . на которой производится умножение, является 1. Так как в сумматор 5 сумма частичных произведений из регистра 4 и множимое из регистра 6 поступают в модифицированном дополнительном коде, то в сумматоре 5 переполнения не происходит и на его выходе вырабатывается новая сумма частичных произведений в модифицированном дополнительном коде. Вычисленная Новая сумма частичных произведений сдвигается вправо на один разряд,. При использовании модифицированного дополнительного кода арифметический сдвиг вправо должен быть модифицированным, т.е. освобождающийся разряд заполняется содержимым знакового разряда, состояние которого не изменяется.

Так как при увеличении разрядности на единицу сумма частичных произведений и множимого не приводит к искажению вырабатьшаемой новой суммы частичных произведений, то перемножение кодов двоичных чисел в этом случае не зависит от знака значения множимого у , т.е. использование модифицированного дополнительного кода позволяет автоматически учитывать поправку (-х)„-2 .

Из формулы (1) видно, что коррекция произведения z Х у на величину (у)ц 2 производится при Х . Так как в дополнительном коде X при знаковый разряд находится в состоянии , то коррекцию на величину

(-у)-2 можно совместить с умножения кодов сомножителей на знаковый разрлд множителя.

При умножении на знаковый разряд прибавляется к накопленной сумме час тичных произведений величина 2 затем прибавляется велш1ина (-у),

(-у) 2 (у),/ (2)

и-(

2

у .

м

Устройство для умножения двоичных чисел в дополнительных кодах, реализует алгоритм (1) с учетом соотношения (2J, т.е. производится (п-) циклов перемножения кодов по правилам умножения положительных двоичных кодов, д последний и-и цикл (умножение на знаковый разряд кода множ} теля k ) производится путем добавления к накопленной сумме частичных произнедений инверсно15

управления, который выра- батьюает на своем втором выходе сигнал, поступающий в счетчик 1 через первый вход. По этому сигналу счетчик устанавливается в начальное состояние, т.е. настраивается на выполнение (п-1) циклов вь гчислений. После этого в устройстве выполняется (п-1) циклов вычислений сут-5мы частичных произведений. В каждом L-M цикле, где i 1,2, ...,(п-1), вьтолняются следующие микрооперации:

1) выдача прямого кода регистра 4 Z . на первый информационный вход сумматора 5 по сигналу, вырабатываемому на пятом вькоде блока 2 при .

го кода множимого

ший разряд, так как (у)„ - У„ (правило изменения знака числа в дополнительном коде) .

Устройство обрабатывает и-разрядные двоичн111е числах ,V, в дополнительных кодах, а произведение 7. X . у вырабатьшается 2|,-разряд,- ным. Для обеспечения использования модифицированного дополнительного кода регистр 6 множимого, сумматор 5 и регистр 4 имеют (п+1) разрядов. Для того, чтобы устройство могло об- рабатьшать целые (выравненные справа) или дробные (выравненные слева) двоичные числа с фиксированной запятой, регистр 3 множителя также (п+1)- разрядный.

Устройство работает следующим образом.

Перед выполнением операции умножения устройство находится в начальном состоянии:

1)в регистре 3 множителя находится дополнительный код множителя N, при этом старший (п+1)-и разряд устанавливается в состояние О, остальные h разрядов отведены для кода X ;

2)ре гкстр 4 находится в нулевом состоянии;

3)в регистре 6 находится модифицированный дополнительный код множимого V ,

Вычисление произведения z ху начинается с поступлением управляющего сигнала в устройство по входу 10 через вход запуска блока 2 микропрог25

1

состоянии младшего разряда х регистра 3.;

.) вьщача прямого кода регистра 20 6 V|, на второй информационный вход

сумматора 5 по сигналу, вырабатывае- и 1 в млад- мому на одиннадцатым выходе блока - 2 при состоянии младшего разряда регистра 3;

3)вычисление новой суммы частичных произведений:

,-/Ум5

4)прием прямого кода новой суммы частичных произведений с выхода сум матора 5 в регистр 4 по сигналу, вырабатываемому на шестом выходе блока 2 при состоянии младшего разряда Кц 1 регистра 3;

5)модифицированньм арифметичес- 35 кий сдвиг вправо на один разряд содержимого регистров 3 и 4, -содержимое младшего разряда которого переносится в освобождаемый старший разряд регистра 3 по сигналу, выраба 0 тываемому на седьмом выходе блока 2 (младший разряд регистра 3 переходит в состояние, соответствующее процессу умножения на следующем (i+l)-M цикле);

45 6) увеличение состояния счетчика 1 на единицу по сигналу, вырабатываемому на четвертом выходе блока 2;

у) проверка счетчиком условия i (п-1) и при соблюдении этого

50 условия устройство переходит к выполнению следующего (i+l)-ro цикла вычислений. Операции 1-4 выполняются только при состоянии младшего разряда Х 1 регистра 3, операции 5 55 7 в каждом цикле вычислений.

После выполнения (п-1) циклов устройство переходит к п-му циклу вычисления окончательного результата .

с

2)

290301

оаммного

(

JO

15

управления, который выра- батьюает на своем втором выходе сигнал, поступающий в счетчик 1 через первый вход. По этому сигналу счетчик устанавливается в начальное состояние, т.е. настраивается на выполнение (п-1) циклов вь гчислений. После этого в устройстве выполняется (п-1) циклов вычислений сут-5мы частичных произведений. В каждом L-M цикле, где i 1,2, ...,(п-1), вьтолняются следующие микрооперации:

1) выдача прямого кода регистра 4 Z . на первый информационный вход сумматора 5 по сигналу, вырабатываемому на пятом вькоде блока 2 при .

1

сумма мому 2 при

3) ных п

В n-M цикле выполняются микроопе ации:

) вьщача прямого кода регистра 4 сумматор 5 по сигналу восьмого выода блока 2 при X |, 1 I

2)выдача инверсного кода У„ и 1 соответственно на второй информационный вход и на дополнительный вход ладшего разряда сумматора 5 по сигналу с одиннадцатого выхода блока 2 микропрограммного управления при

- I;

3)вычисление z у + I ;

4)прием прямого кода z, регистром 4 по сигналу с девятого выхода блока 2 при Хд 1;

5J модифицированный арифметический сдвиг вправо на один разряд содержимого регистров 3 и 4 с переносом содержимого младшего разряда из регистра 4 в старший разряд регистра 3 по сигналу, вырабатываемому

на десятом выходе блока 2. I

После выполнения и-го цикла в регистрах 4 (старшие разряды) и 3 (младшие разряды) будет находиться модифицированный дополнительный код

Z произведения z х-у, вычисленный в соответствии с алгоритмом (1) ,

Младший разряд регистра 3 после выполнения h сдвигов устанавливается в нулевое состояние.

Так как модифицированный дополнительный код двоичного числа отличается от обычного раздвоением знакового разряда регистра, то в регистрах 3 и 4 вырабатывается дополнительный Zn код произведения z ху.

При обработке целых двоичных чисел результат размещен в и младших разрядах регистра 4 (старшие разряды) и в П старших разрядах регистра 3 множителя,

При обработке дробных чисел (выравненных слева) результат размещен в (п-1) младших разрядах регистра 4 и во всех (п+1) разрядах регистра 3,

Схема выходов результата показана на фиг.2.

После вычисления произведения z ху на выходе 11 блока 2 выра- батьтается сигнал признака окончания работы устройства.

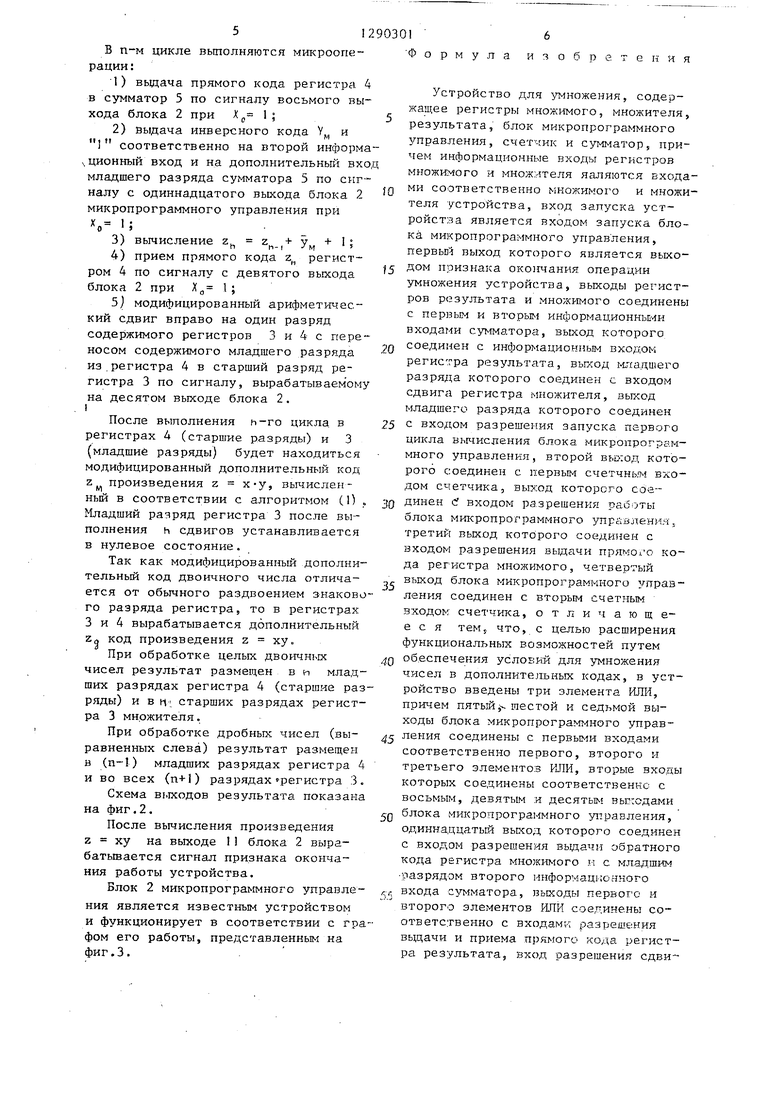

Блок 2 микропрограммного управления является известным устройством и функционирует в соответствии с графом его работы, представленным на фиг.З.

Формула изобр

е к и я

0

5

Устройство для умножения, содержащее регистры множимого, множителя, результата, блок микропрограммного управления, счетчик и cyi-iMarop, причем информационные входы регистров множи;у5ого и множителя яаляются входами соответственно множимого и множителя устройства, вход запуска устройства является входом запуска блока микропрограммного управления, первьп1 выход которого является вько- дом признака око 1чания операции умножения устройства, выходы регистров результата и множимого соединены с пер1зым и вторым информационньпу1и входами сумматора, выход которого соединен с информационным входом регистра результата, выход 1«1ладшего разряда которого соединен с входом сдвига регистра множителя, выход младшего разряда которого соединен с входом разрешения запуска первого цикла вычисления блока микропрограммного управления, второй вькод которого соединен с первым счетчнь.м входом счетчика, выход которого cdeiQ динен cf входом разрешения работы блока микропрограммного упрйвления. третий выход которого соединен с входом разрешения вьщачи прямох о кода регистра множимого, четвертый

вькод блока микропрограммного управления соединен с вторым счетным входом счетчика, отличающееся тем что, с целью расширения функциональных возможностей путем

д обеспечения условкй для умножения чисел в дополнительных кодах, в устройство введены три элемента ИЛИ, причем пятьй -- шестой и седьмой выходы блока микропрограммного управ.j ления соединены с первыми входами соответственно первого, второго и третьего элементов ИЛИ, вторые входы которых соединены соответственнс с восьмым, девятым и десятым вьп:одами

Q блока микропрограммного управления, одиннадцатый выход которого соединен с входом разрешения выдачи обратного кода регистра множимого i; с младшим разрядом второго информационного

г,г, входа сумматора, выходы первого и второго элементов ИЛИ соединены соответственно с входами разрешения вьщачи и приема прямого кода регистра результата, вход разрешения сдви7129030 8

га которого соединен с входом жителя и выходом третьего эле- разрешения сдвига регистра мно- мента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

Устройство для умножения относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и спецпроцессоffl ров. Целью изобретения является расширение функциональных возможностей за счет обеспечения условий для умножения чисел в дополнительных кодах. Устройство содержит регистры множителя 3, множимого 6, результата 4, сумматор 5, счетчик 1, блок 2 микропрограммного управления и три элемента ИЛИ 7-9. Увеличение на один разряд регистров множителя и множимого для размещения двоичных чисел в моди4 ицированном дополнительном коде позволяет производить умножение двух сомножителей с произвольными знаками по алгоритму, близкому к алгоритму умножения положительных чисел. 3 ил. (Л С .1

в

1 п

Составитель Н.Маркелова Редактор М.Дылын Техред Л.Олейник Корректор Г,Решетник

Заказ 7902/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

fvff. 3

| Устройство умножения в дополнительных кодах | 1982 |

|

SU1081640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Самофалов Г.К., Корнейчутс В.И | |||

| Тарасенко В.П | |||

| Цифровые электронные вычислительные машины | |||

| - Киев: Вища школа, 1983, с.288-289, рис.5.9. | |||

Авторы

Даты

1987-02-15—Публикация

1985-04-08—Подача