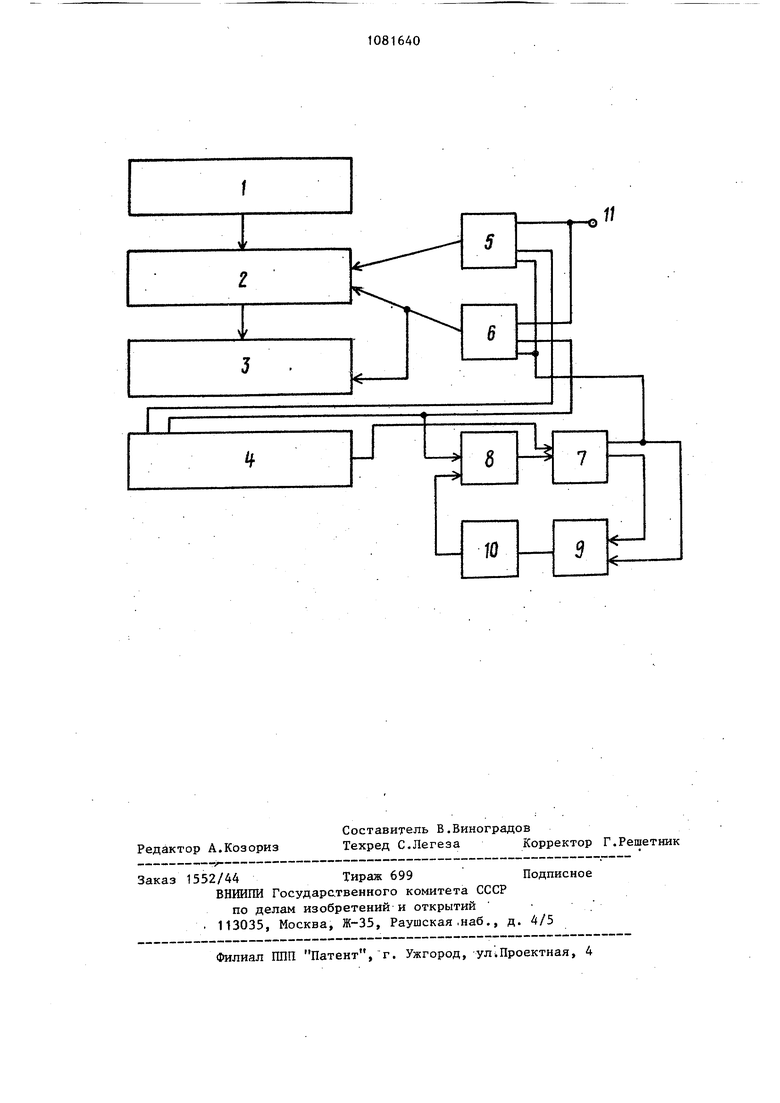

1 Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислительных машинах различного назначения. Известно устройство умножения в дополнительных кодах с двумя коррек тирующими шагами, содержащее два регистра, формирователь частичных произведений, схему коррекции и сум матор, причем выход первого регистра через формирователь частичных произведений соединен с входами сум матора и схемы коррекции, первый вы ход второго регистра соединен с вхо дом формирователя частичных произве дений, второй выход - с входом схемы коррекции, выход которой соедине с входом сумматора lj , В устройстве увеличивается время операции, так как коррекция требует выполнения двух дополнительных циклов. Необходимость коррекции усложняет устройство управления множи теля. Известно устройство умножения в дополнительных кодах путем последовательного преобразования множителя, содержащее два регистра, формирователь частичных произведений, сумматор и преобразователь множителя, причем выход первого регистра через формирователь частичных произ ведений соединен с входом сумматора выход второго регистра через преобразователь множителя соединен с вхо дом формирователя частичных произве дений 2 . В таком устройстве увеличиваются время умножения и расход оборудования. Первое обусловлено необходимостью выполнения дополнительного цикла умножения, второе - необходимостью преобразования множителя. I Наиболее близким по технической сущности к изобретению является уст ройство умножения в дополнительных кодах с одним корректирующим шагом, содержащее два регистра, сумматор, схему инверсии, два элемента И, причем выход первого регистра через схему присвоения знака соединен с входом сумматора, выход второго регистра - с первыми входами элементов И, вторые и третьи входы элементов И соед 1нены с входами устройства, выходы элементов И - с входами схемы инверсии 3j . 40 2 Недостаток известного устройства состоит в увеличении, времени умножения, так как необходим дополнительный цикл для выполнения коррекции произведения. Так как для управления устройством необходимы функциональные сигналы, управляющие режимом умножения, и сигналы, управляющие режимом коррекции, диаграмма управляющих сигналов усложняется, что приводит к усложнению устройства. Цель изобретения - повышение быстродействия устройства. Цель достигается тем, что в устройство, содержащее первый и второй регистры, две группы элементов И-НЕ, сумматор, первьй и второй элементы И, причем прямые выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ первой группы, вторые входы которых соединены с выходами первого элемента И, инверсные выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ второй группы, вторые входы которых соединены с выходом второго элемента И, выходы элементов И-НЕ первой и второй групп соединены с соответствующими разрядными входами сумматора, вход младшего разряда которого соединен с выходом первого элемента И, первые входы первого и второго элементов И соединены с входом устройства, введены полусумматор, третий элемент И, элемент ИЖ, элемент задержки, причем вторые входы первого и второго элементов И соединены соответственно с инверсным и прямым выходами знакового разряда второго регистра, выход младшего разряда которого соединен с первым входом полусумматора, второй вход которого соединен с выходом третьего элемента И, выход суммы полусумматора соединен с третьими входами первого и второго элементов И и первым входом элемента ИЛИ, выход переноса полусумматора соединен с вторым входом элемента ИЛИ, выход которого соединен с входом элемента задержки, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом знакового разряда второго регистра. На чертеже показана схема предагаемого устройства. 3. Схема содержит регистр 1 множив , схему 2 инверсии, сумматор 3, регистр 4 множителя, элементы И 5 и 6, полусумматор 7, элемент И 8, элемент ИЖ 9, элемент 10 задержки и вход 11 устрой:-тва. Прямые и инверсные выходы регист ра 1 соединены со схемой 2 инверсии представляющей собой две группы эле ментов И-НЕ, причем прямые выходы регистра 1 соединены с соответствую щими первыми входами элементов И-НЕ первой группы, вторые входы элементов И-НЕ которой соединены с выхода ми элемента И 6, инверсные выходы регистра 1 соединены с первыми вход ми элементов И-НЕ :второй группы, вт рые входы элементов И-НЕ которой со динены с выходом элемента И 5, Выхо элементов И-НЕ первой и второй груп соединены с соответствующими разряд ными входами сумматора 3, младщий разряд которого соединен с выходом элемента И 6, Первый и второй выходы регистра 4 соединены с вторыми входами элементов И 5 и 6. Третий выход регистра 4 соединены с первым входом полусумматора 7, второй вход которого соединен с выходом элемента И 8. Первый выход полусумматора 7 соединен с третьими входами элементов И 5 и 6 и с первым входо элемента ИЛИ 9, второй выход полусумматора 7 соединен с вторым входом элемента ИЛИ 9. Выход элемента ИЖ 9 через элемент 10 задержки соединен с первым входом элемента И 8, второй вход элемента И 8 соединен с первым выходом регистра 4 Первые входы элементов И 5 и .6 соединены с входом 11 устройства. Устройство работает следующим, образом. В регистр 1 записывается множимое в дополнительном коде, в регистр 4 - множитель, также в дополн тельном коде. Младший разряд множителя проходит через полусумматор 7 на выход суммы, поступает на входы элементов И 5 и 6, проходит через элемент ИЛИ 9 и запоминается в элементе 10 задержки. 404 Первый цикл умножения начинается с подачи синхронизирующего сигнала на вход устройства 11. Если младший разряд множителя равен 1, сигнал проходит на один из управляющих входов схемы инверсии. Если множитель положителе н,сигнал проходит через элемент И 5, если отрицателен через элемент И 6. Если множитель положителен, множимое передается из регистра 1 в сумматор 3 без изменения, если отрицателен, схема инверсии передает в сумматор 3 инверсию содержимого регистра 1. Одновременно с выхода элемента И 6 сигнал поступает на вход младщего разряда сумматора, т.е. в сумматор поступает дополнение содержимого регистра 1. Если младший разряд множителя равен нулю, сигнал не поступает на схему инверсии и последняя посылает на вход сумматора нулевой сигнал. После заверщения операции суммирования содержимое сумматора 3 и регистра 4 сдвигается на один разряд в сторону младших разрядов. Первый разряд множителя выходит из элемента задержки и, если множитель отрицателен, складывается с вторьм разрядом множителя в полусумматоре 7. Если множитель положителен, элемент И 8 закрыт и выход элемента задержки не подключается к входу полусумматора. При суммировании первого и второго разрядов множителя на вы ходах полусумматора формируется сумма или перенос. Сумма вновь поступает на элементы И 5 и 6. Сумма или перенос, объединенные элемен- - том ИЛИ 9, запоминаются в элементе 10 задержки. На этом выполнение цикла заканчивается. Затем на вход 11 вновь подается сигнал и аналогично выполняется второй цикл. Умножение заканчивается после отработки старшего значащего разряда множителя. Коррекция результата по завершении умножения не требуется.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в дополнительных кодах | 1988 |

|

SU1695307A2 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1982 |

|

SU1123031A1 |

| Устройство для умножения | 1981 |

|

SU1019442A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Последовательно-параллельное устройство для умножения чисел в дополнительном коде | 1985 |

|

SU1259252A1 |

УСТРОЙСТВО УМНОЖЕНИЯ ВДОПОЛНИТЕЛЬНЫХ КОДАХ, содержащее первый и второй регистры, две группы элементов И-НЕ, сумматор, первьй и второй элементы И, причем прямые выходы первого регистра соединены соответствено с первыми входами эле- . ментов И-НЕ первой группы, вторые входы которых соединены с выходами первого элемента И, инверсные выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ второй группы, вторые входы koTopbix соединены с выходом второго элемента И, выходы элементов И-НЕ первой и второй групп соединены с соответствующими разрядными входами сумматора, вход младшего разряда которого соединен с выходом первого элемента И, первые входы перг вого и второго элементов И соединены с входом устройства, отличающ. е е с я тем, что, с целью повьщ1ения быстродействия устройства, в него введены полусумматор, третий элемент И, элемент ИЛИ, элемент задержки, причем вторые входы первого и второго элементов И соединены соответственно с инверсным и прямым выходами знакового разряда второго ре( гистра, выход младшего разряда кото(Л рого соединен с первым входом полусумматора, второй вход которого соединен с выходом третьего элемента И, выход еуммы полусумматора соединен с .третьими входами первого и второго элементов И и первым входом элемента ИЛИ, выход переноса полусумматоэо ра соединен с вторым входом элемента ИЛИ, выход которого соединен с f входом элемента задержки, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом знакового разярда второго регистра.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Устройство для нахождения генерирующих точек контактного детектора | 1923 |

|

SU472A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметика цифровых машин | |||

| М., Наука, 1969, G | |||

| ВОДЯНОЙ ЦЕПНОЙ ДВИГАТЕЛЬ | 1923 |

|

SU481A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Двухколесный автомобиль для формовки кирпичей из разлитой по полю сушки торфяной массы | 1923 |

|

SU478A1 |

Авторы

Даты

1984-03-23—Публикация

1982-07-02—Подача