fO

15

Изобретение относится к вычислиельной технике и может быть исользовано в высокопроизводительных нформационно-вычислительных систеах, создаваемых на основе больших нтегральных схем, применяемых в комлексах физического эксперимента и правления быстропротеканлцими про- ессами.

Цель изобретения - повышение быстродействия .

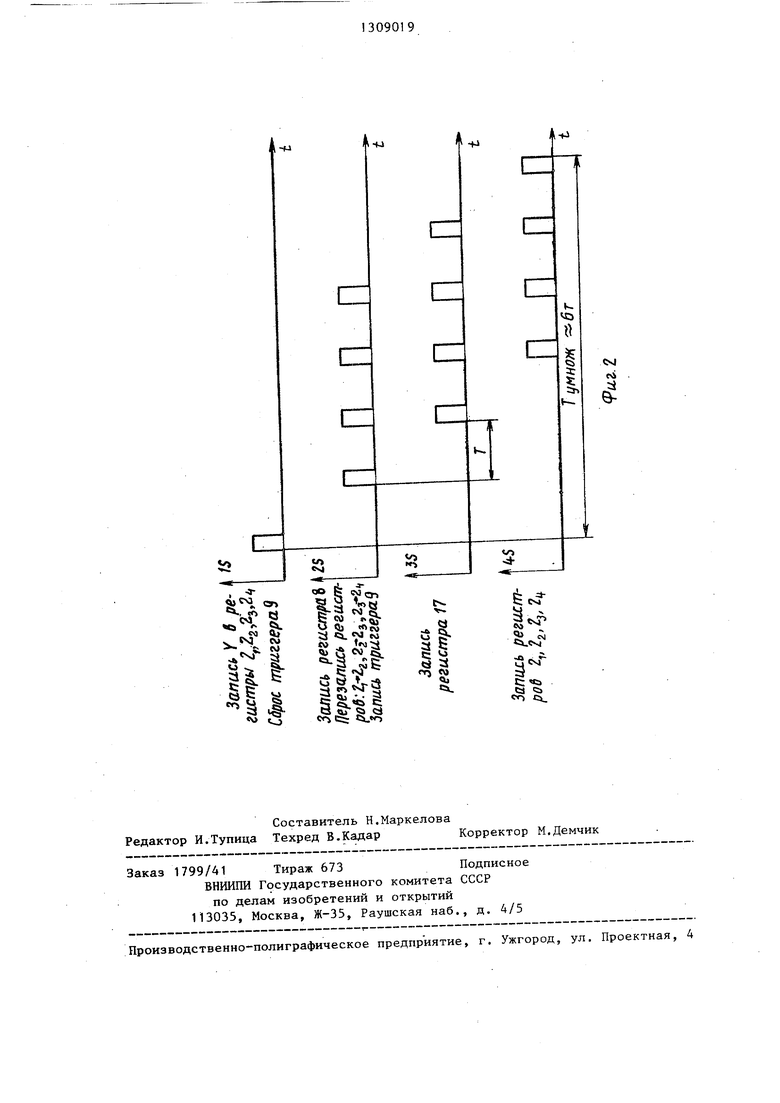

На фиг. 1 представлена функциональная схема устройства, на фиг.2 - временная диаграмма работы распреде7 лителя импульсов умножителя.

Устройство для умножения (фиг.1) содержит коммутатор 1, предназначенный дпя передачи множителя /Y/, регистр 2,-24 множителя, узел 3 суммирования, элемент ИЖ 4, элемент И 5, блок 6 микропрограммного управления, в состав которого входят программируемая логическая матрица (ГШМ) 7 и регистр 8 хранения микроопераций, триггер 9, вход 10 множителя, вход 11 множимого, дополнительный коммутатор 12, блок 13 инверсии, узел 14 сдвига, сумматор 15 дополнительный узел 16 сдвига, буферный регистр 17, накапливающий сумматор 18, в состав которого входят сумматор 19 и регистр 20,-204, распределитель 21 импульсов вход 22 запуска.

Регистр 2 имеет возможность по сигналам распределителя 21 импульсов отключать выходные шины регистра 2д- 24 от его входов и предназначен.для перезаписи содержимого одной тетрады множителя в следующую.

Узел 3, триггер 9, элементы 4 и 5 предназначены для формирования коррекции тетрады, загруженной в тетраду регистра 2„ множителя.

Блок 6 микропрограммного управления, состоящий из ПЛМ, предназначен- ной для формирования управляющих сигналов (команд операций), и регистра, управляемого распределителем 21 и предназначенного для записи управляющих сигналов (команд операций), осуществляет управление работой устройства.

5

20

2-5

30

J5

40

50

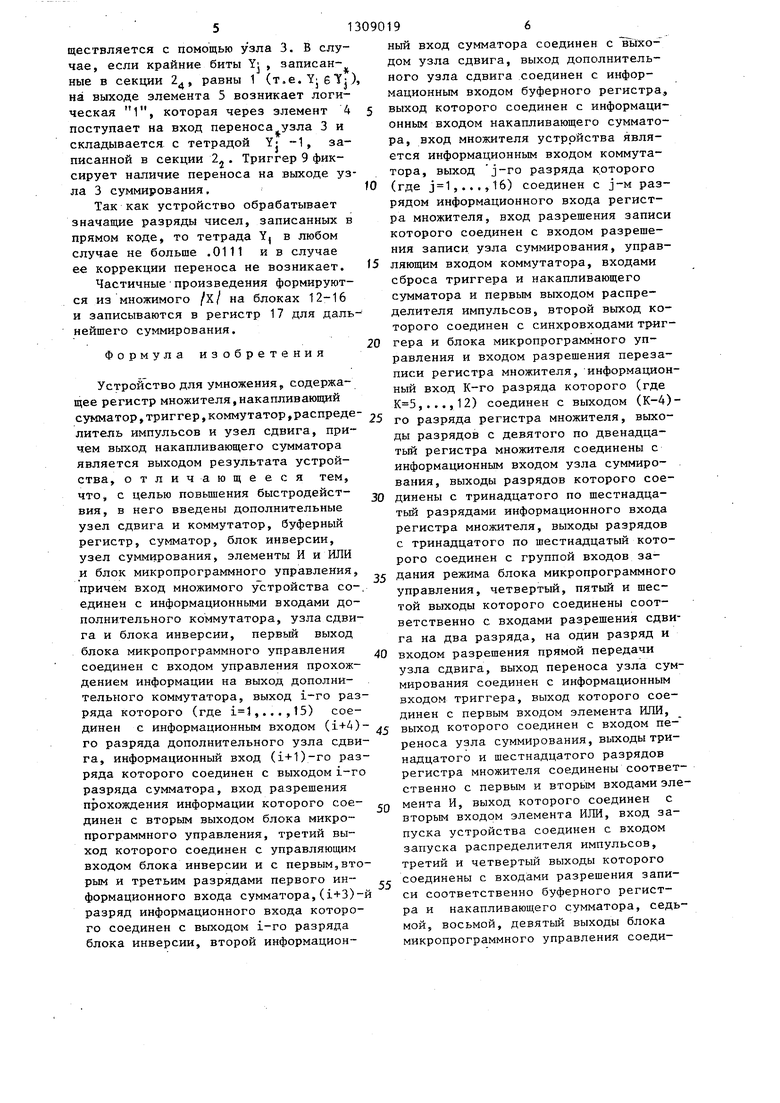

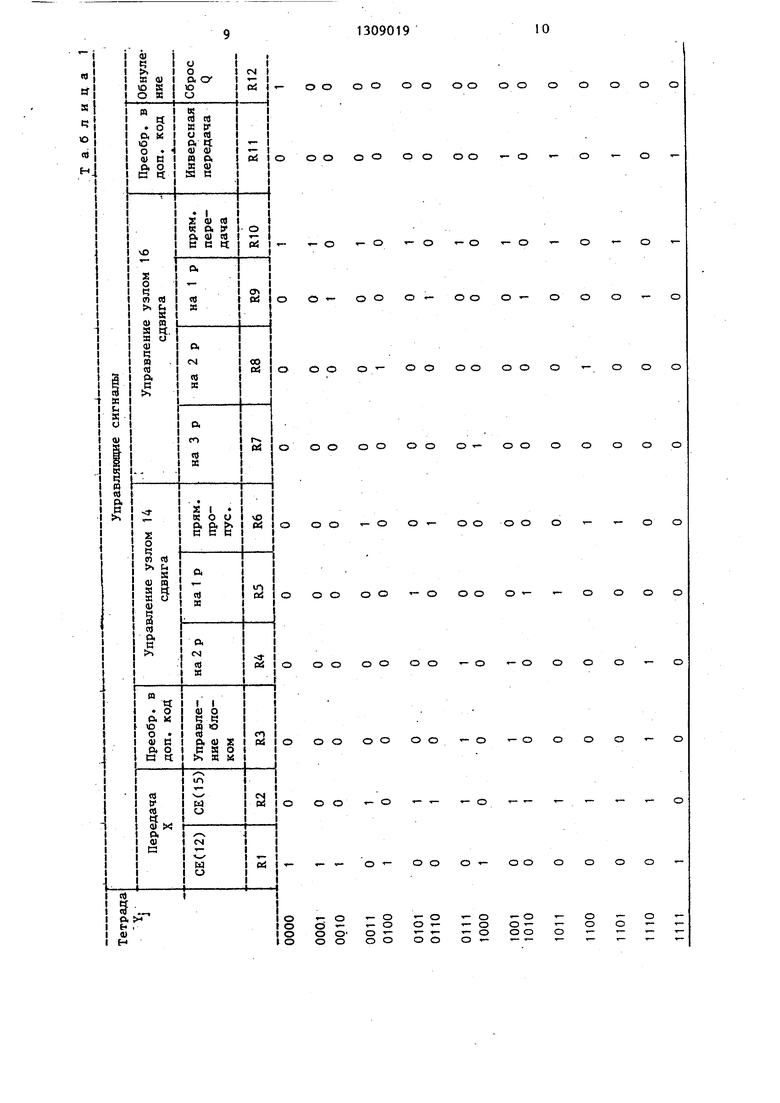

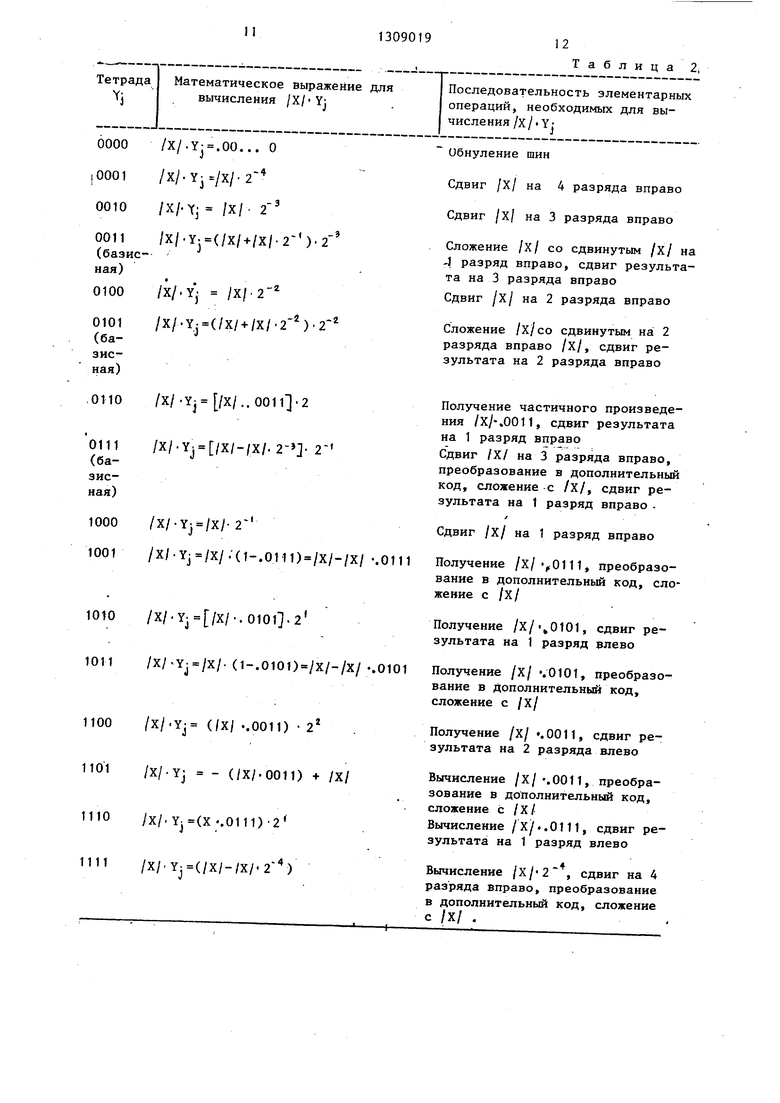

Зависимость между входной информацией ПЛМ 7 (тетрады) и ее выходной информацией (управляющие сигналы блока 6 управления R1-R12) приведена в табл. 1.

fO

15

309019--2

Коммутатор 1 предназначен для передачи множимого и способен переводить свои выходы в нулевое и третье состояние по сигналам R12, R1 блока 5 6. Коммутатор 1 может быть построен на логических элементах И, элементе НЕ и двунаправленных ключах.

Сумматор 15 предназначен для суммирования входных кодов и способен переводить свои выходы в третье состояние по сигналу блока 6. Управляемый инвертор 13 предназначен для инвертирования множимого по сиг6, для сдвига множимого /X/.

налу R3 блока 6, узел 14 предназначен

.,, при- 19 средиУзел 14 сдвига может быть построен с помощью трех групп коммутирующих ключей (по три ключа в группе) и

0 трех групп заземляющих ключей. Ключи управляются сигналами R4, R5, R6 блока 6.

Накапливающий сумматор 18 состоит из сумматора 19, предназначенного дли

-5 суммирования частичных произведений, записанных в регистры 17 и 20, чем вход переноса сумматора нен с выходом сигнала R11, записанного в регистр 17, и регистров-нако0 пителей , предназначенных для хранения младщих разрядов результата, не участвующих в дальнейшем выполнении операций, причем старшие 15 разрядных выходных шин и выходная шина

5 знакового разряда регистра 20, соединены с входными шинами второго слагаемого сумматора 19 следующим образом. Шина знакового разряда с выхода регистра 20 соединена с входной шиной знакового разряда и четырьмя входными шинами старших разрядов, выходные шины регистра 20, с 1 по 15 соединены с входными шинами второго слагаемого сумматора 19 соответственно с 5 по 19, все выходные шины регистров- накопителей 20,-20 соединены с выходами устройства соответственно старшинству разрядов результата, записанного в них.

0

Устройство позволяет умножать двоичные шестнадцатиразрядные числа представленные в прямом коде. Устройство позволяет осуществлять выполнение алгоритма умножения двух чисел X и Y, который сводится к четырем тактам суммирования частичных произведений, полученных разбиением множителя Y на группы по 4 бита и ум31

ножением каждой из групп на множимое /X/.

Алгоритм вычисления частичных про изведений вида /X/ Y: приведен в табл. ;2.

Устройство работает следующим образом.

Пусть необходимо вычислить произведение двух шестнадцатиразрядных чисел X и Y, представленных в прямом коде с фиксированной запятой, причем , /Y/ 1.

Пусть Х Х..Х

Y Y..Y, ( f где X , Y - знаковые разряды чисел

X и Y, Х Y

...16 - значащие разряды чисел X и Y.

16

.1 „-«

16

Тогда ,Y ZY 2-

(,)

Разобьем /Y/. на группы по 4 бита (тетрады), начиная со старших разрядов. Обозначим тетрады через Y, ,2,3,4. Очевидно, что старший раз ряд Y всегда равен О,

Алгоритм умножения состоит в преобразовании произведения модулей сомножителей для получения модуля результата в прямом коде, знак результата получается суммированием знаковых разрядов сомножителей по модулю 2.

Преобразуем выражение (1) следующим образом:

/X/./YHX/.I.Y . .(ГУ. )

/Х/. ((( 2-UY3),) 2-%Y,

(0+/X|.Y4)-2- +/X/.Y,1 r

+ |Xf.Y 2- -b/X/ Y,(2)

Sgn (X Y) Sgn (X) ® Sgn (Y) (3)

.Как видно из выражения (2), алгоритм умножения на каждом шаге можно представить в виде последовательности следующих операдий: вычисление вы ражения вида /X/ Y:; сложение с содержимым накопителя, вычисленным на предьщущем шаге и сдвинутым на 4 разряда вправо, запись полученной суммы в накопитель.

Функционирование устройства основано на том, что, используя набор б азисных чисел из множества /X/;Yj l можно получить любое частичное произ

090194

ведение /Х/- YJ за один такт сложения (обращения к суммирующему элементу). В табл. 2 показано как можно, используя набор базисных чисел 0011, 5 0101, 0111, операции сложения, сдвига, преобразования в дополнительный код, получить всевозможные частичные произведения вида /X/ Yi (для всех комбинаций YJ ).

Ш Множимое /Х| и множитель /Y/ поступают на входы устройства.

Множитель YJ поступает на входы регистра 2 -2 .

Вьтходы регистра 2, и 2 и узла 3 f5 поддерживаются в отключенном (третьем) состоянии до момента записи тетрад в соответствующие секции по импульсу распределителя 21. Затем на все время преобразования выходы ком- 0 мутатора 1 отключаются от своих выходных шин, а выходы секций 2 и 2 и узла 3 подключаются, соответствен- ; но, к входам секций .

После записи множителя во входной 5 регистр множителя младшая тетрада

поступает на вход ПЛМ 7, которая формирует на выходах совокупность управляющих сигналов, определяющую режим работы устройства на данном шаге 0 вычисления. Эта совокупность сигналов записывается в регистр 8 по импульсу распределителя 21. Каждая последующая тетрада, поступающая в секцию регистра 2 множителя, адресует 5 в каждом такте ПЛМ 7 и на ее выходах формируются соответствующие управляющие сигналы, которые затем переписываются в регистр &.

Четыре тетрады из 16 возможных, 0 а именно (табл. 2)j Y (.1001; .1101; 1011, 1111) образуют частичные произведения /Х/ Y., которые получаются косвенным путем, а именно, через тетрады Yj I-Y, т.е. /X/-Y (табл.2) представляется как /X/ ( ) /X/-/X/ Yj . Вычисление вьфажения /X/ Y сводится к следующему: на данном шаге фopмиpyefcя частичное произведение /Х|- Yj, выраженное в 0 дополнительном коде, а недостающее /X/ учитывается прибавлением единицы в младший разряд тетрады, используемой для получения частичного произведения на следующем шаге.

Во время получения команды операций, адресованной i-й тетрадой, к (1-1)-й прибавляется единица в младший разряд, если Yj YJ , это осу5

ществляется с помощью узла 3. В случае, если крайние биты Y , записанные в секции 2, равны 1 (т.е.У бТ: на выходе элемента 5 возникает логическая 1, которая через элемент 4 поступает на вход переноса узла 3 и складывается с тетрадой Y; -1, записанной в секции Zj. Триггер 9 фиксирует наличие переноса на выходе уз ла 3 суммирования.

Так как устройство обрабатывает значащие разряды чисел, записанных в прямом коде, то тетрада Y, в любом случае не больше .0111 ив случае ее коррекции переноса не возникает.

Частичные произведения формируются из множимого /X/ на блоках 12-16 и записываются в регистр 17 для даль нейшего суммирования.

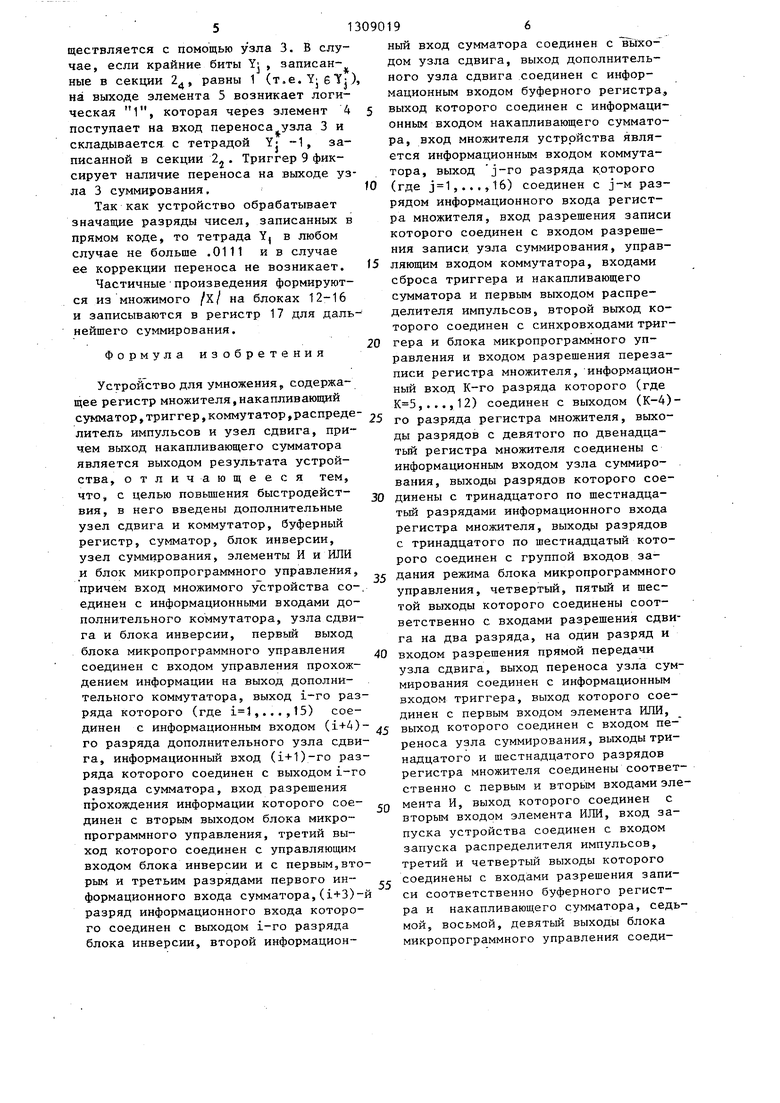

Формула изобретения

Устройство для умножения, содержащее регистр множителя,накапливающий сумматор,триггер,коммутатор,распреде литель импульсов и узел сдвига, причем выход накапливающего сумматора является выходом результата устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены дополнительные узел сдвига и коммутатор, буферный регистр, сумматор, блок инверсии, узел суммирования, элементы И и ИЛИ и блок микропрограммного управления, причем вход множимого устройства соединен с информационными входами дополнительного коммутатора, узла сдвига и блока инверсии, первый выход блока микропрограммного управления соединен с входом управления прохождением информации на выход дополнительного коммутатора, выход i-ro разряда которого (где ,...,15) сое

ный вход сумматора соединен с вйхо- дом узла сдвига, выход дополнительного узла сдвига соединен с информационным входом буферного регистра, выход которого соединен с информационным входом накапливающего сумматора, вход множителя устройства является информационным входом коммутатора, выход j-ro разряда к.оторого (где ,...,16) соединен с j-м разрядом информационного входа регистра множителя, вход разрешения записи которого соединен с входом разрешения записи узла суммирования, управляющим входом коммутатора, входами сброса триггера и накапливающего сумматора и первым выходом распределителя импульсов, второй выход которого соединен с синхровходами триггера и блока микропрограммного управления и входом разрешения перезаписи регистра множителя, информационный вход К-го разряда которого (где ,...,12) соединен с выходом (К-4)- го разряда регистра множителя, выходы разрядов с девятого по двенадца- тьй регистра множителя соединены с информационным входом узла суммирования, выходы разрядов которого соединены с тринадцатого по шестнадцатый разрядами информационного входа регистра множителя, выходы разрядов с тринадцатого по шестнадцатый которого соединен с группой входов за- 35 Дания режима блока микропрограммного управления, четвертый, пятый и шестой выходы которого соединены соответственно с входами разрешения сдвига на два разряда, на один разряд и входом разрешения прямой передачи узла сдвига, выход переноса узла суммирования соединен с информационным входом триггера, выход которого соединен с первым входом элемента ИЛИ,

динен с информационным входом (i+A)- выход которого соединен с входом пего разряда дополнительного узла сдвига, информационный вход (i+1)-ro разряда которого соединен с выходом i-ro разряда сумматора, вход разрешения прохождения информации которого соединен с вторым выходом блока микропрограммного управления, третий выход которого соединен с управляющим входом блока инверсии и с первым,вторым и третьим разрядами первого информационного входа сумматора,(i+3)-и разряд информационного входа которого соединен с выходом i-ro разряда блока инверсии, второй информацион50

55

реноса узла суммирования, выходы тринадцатого и шестнадцатого разрядов регистра множителя соединены соответственно с первым и вторым входами эле мента И, выход которого соединен с вторым входом элемента ИЛИ, вход запуска устройства соединен с входом запуска распределителя импульсов, третий и четвертый выходы которого соединены с входами разрешения записи соответственно буферного регистра и накапливающего сумматора, седьмой, восьмой, девятьш выходы блока микропрограммного управления соеди,

10

15

20

30

25 , 3090196

ный вход сумматора соединен с вйхо- дом узла сдвига, выход дополнительного узла сдвига соединен с информационным входом буферного регистра, выход которого соединен с информационным входом накапливающего сумматора, вход множителя устройства является информационным входом коммутатора, выход j-ro разряда к.оторого (где ,...,16) соединен с j-м разрядом информационного входа регистра множителя, вход разрешения записи которого соединен с входом разрешения записи узла суммирования, управляющим входом коммутатора, входами сброса триггера и накапливающего сумматора и первым выходом распределителя импульсов, второй выход которого соединен с синхровходами триггера и блока микропрограммного управления и входом разрешения перезаписи регистра множителя, информационный вход К-го разряда которого (где ,...,12) соединен с выходом (К-4)- го разряда регистра множителя, выходы разрядов с девятого по двенадца- тьй регистра множителя соединены с информационным входом узла суммирования, выходы разрядов которого соединены с тринадцатого по шестнадцатый разрядами информационного входа регистра множителя, выходы разрядов с тринадцатого по шестнадцатый которого соединен с группой входов за- 35 Дания режима блока микропрограммного управления, четвертый, пятый и шестой выходы которого соединены соответственно с входами разрешения сдвига на два разряда, на один разряд и входом разрешения прямой передачи узла сдвига, выход переноса узла суммирования соединен с информационным входом триггера, выход которого соединен с первым входом элемента ИЛИ,

40

- выход которого соединен с входом пе0

5

реноса узла суммирования, выходы тринадцатого и шестнадцатого разрядов регистра множителя соединены соответственно с первым и вторым входами элемента И, выход которого соединен с вторым входом элемента ИЛИ, вход запуска устройства соединен с входом запуска распределителя импульсов, третий и четвертый выходы которого соединены с входами разрешения записи соответственно буферного регистра и накапливающего сумматора, седьмой, восьмой, девятьш выходы блока микропрограммного управления соедийены соответственно с входами разрешения сдвига на три, на два и на один разряды дополнительного узла сдвига, входы разрешения передачи прямого и инверсного кодов которого соединены соответственно с десятым и одиннадцатым выходами блока микропрограммного управления, одиннадцатый и двенадцатый выходы которого соединены соответственно с входом знакового

разряда буферного регистра и управляющим входом дополнительного коммутатора, вход восемнадцатого разряда сумматора соединен с первым разрядом информационного входа дополнительного узла сдвига и с входом логического нуля устройства, выход знакового разряда буферного регистра соединен с входом переноса накапливающего сумматора.

Тетрада Yi

Математическое выражение для вычисления /X/ Y;

/X/.Y;.00... О

J

/X/. Yj /X/-2

/X/-YJ /X/ 2

/X/-Y.(/X/ + /X/-2 )

/X/-YJ Д/ 2

/X/ Y: (/X/ + /X/-2 2

/X/Yj /X/..

/X/.Yj /X/-/X/. 2,/X/.Yj /X/-2- /X/-Yj /X/.(1-.0111) /X/-/X/ -.0111

/X/..010l.2

/X/-Yj /X/- (1-.010O /X/-/X/ -.0101

/X/ Yj (/X/ ..0011) 2

«

/X/ Yj - (/X/.0011) + /X/

/X/. Yj(X-.0111)-2

/X/.Yj(/X/-/X/.2)

Т а б л и ц а 2i

Последовательность элементарных операций, необходимых для вычисления /X/ Y:

Обнуление шин

Сдвиг /X/ на 4 разряда вправо

Сдвиг /X/ на 3 разряда вправо

Сложение /X/ со сдвинутым /X/ на -J разряд вправо, сдвиг результата на 3 разряда вправо

Сдвиг /X/ на 2 разряда вправо

Сложение /Х/со сдвинутым на: 2 разряда вправо /X/, сдвиг результата на 2 разряда вправо

Получение частичного произведения /Х/-.0011, сдвиг результата на 1 разряд вправо Сдвиг /X/ на 3 разряда вправо, преобразование в дополнительный код, сложение с /X/, сдвиг результата на 1 разряд вправо .

/

Сдвиг /X/ на 1 разряд вправо

Получение , преобразование в дополнительный код, сложение с /X/

Получение , сдвиг результата на 1 разряд влево

Получение /X/ .0101, преобразование в дополнительный код, сложение с /X/

Получение /X/ . 0011, сдвиг результата на 2 разряда влево

Вычисление /X/ -.ООП, преобразование в дополнительный код, сложение с /X/

Вычисление /X/.0111, сдвиг результата на 1 разряд влево

Вычисление /Х/ 2 , сдвиг на 4 разряда вправо, преобразование в дополнительный код, сложение с /X/ .

Составитель Н.Маркелова Редактор И.Тупица Техред В.Кадар Корректор М.Демчик

Заказ 1799/41 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

см

CNJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

Изобретение относится к вычислительной технике и представляет собой умножитель двоичных шестнадцатиразрядных чисел со знаком, выраженных в прямом коде, может быть использовано в высокопроизводительных вычислительных системах физического эксперимента. Цель изобретения - повышение быстродействия - достигается за счет того, что в устройстве, содержащем коммутатор 1, регистр множителя 2i - 2 ly, узел суммирования 3, элементы ИЛИ 4 и И 5, блок микропрограммного управления 6, состоящий из программируемой логической матрицы 7 и регистра 8, триггер 9, дополнительный коммутатор 12,- блок инверсии 13, узел 14 сдвига, сумматор 15, буферньш регистр 17, дополнительный узел сдвига 16, накапливающий сумматор 18 и распределитель 21 импульсов, осуществляется умножение двух чисел с помощью частичных произведений, которые вычисляются в ходе операции умножения и представляют собой числа, полученные умножением множимого, поступающего на вход 11« на четыре разряда множителя, поступающего на вход 10. 2 табл., 2 ил. с (Л z со .}

| Карцев М.А., | |||

| Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| - М.: Радио и связь, 1981, с | |||

| Ленточный тормозной башмак | 1922 |

|

SU337A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Там же, с | |||

| Джино-прядильная машина | 1922 |

|

SU173A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-05—Подача