Изобретение относится к радиотехнике и может быть использовано в радиоприемных, радиопередающих и измерительных устройствах.

Целью изобретения является расширение диапазона выходных частот.

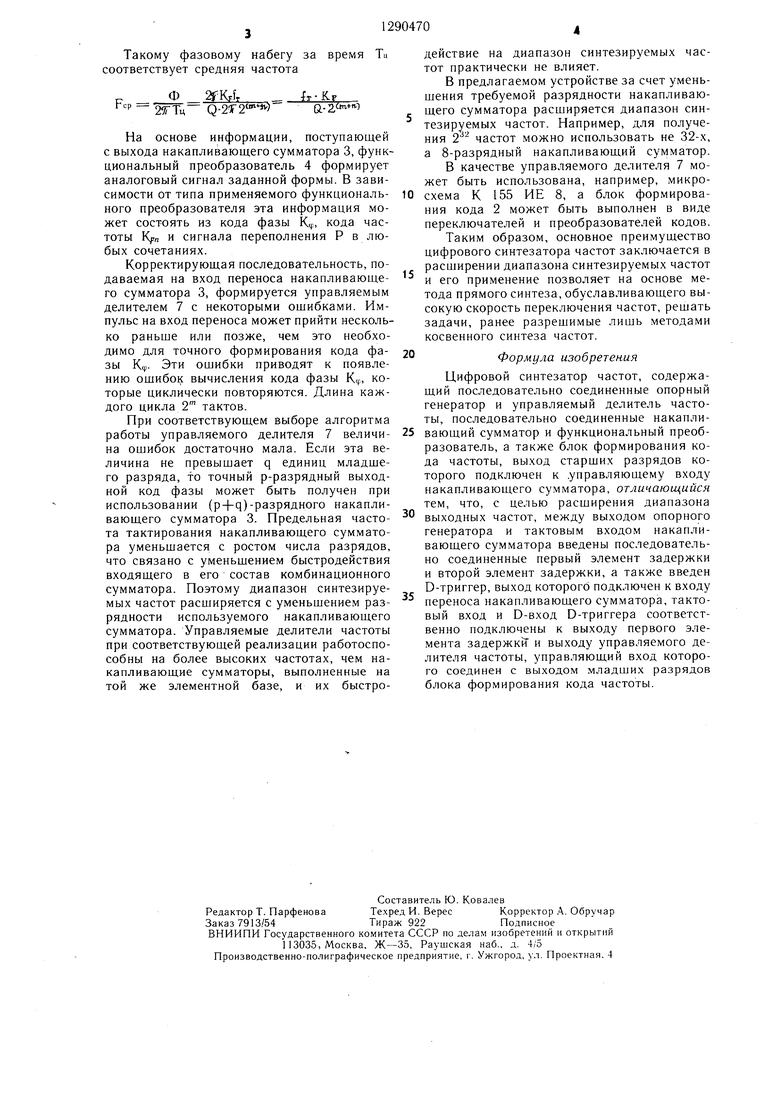

На чертеже представлена электрическая структурная схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит

вала Тг. Первый и второй элементы задержки 5 и 6 компенсируют задержки в управляемом делителе частоты 7 и D-тригге- ре 8, обеспечивая необходимое временное соответствие сигналов.

Блок формирования кода 2 вырабатывает (т + п)-разрядный код частоты Кр.

Очевидно Кр Кр„ + . Равномерная последовательность с частотой т поступает на тактовый вход ш-разрядного

опорный генератор 1, блок формирования ° управляемого делителя 7, который под дейкода 2 частоты, накапливающий сумматор 3, функциональный преобразователь 4, первый элемент задержки 5, второй элемент задержки 6, управляемый делитель 7 частоты, D-триггер 8.

Цифровой синтезатор частот работает следующим образом.

В накапливающем сумматоре 3 при подаче на его тактовый вход импульсов синхронизации формируется код фазы синтезируемого колебания . Информация с вы- 20 ходов накапливающего сумматора 3 преобразуется функциональным преобразователем 4 в аналоговый сигнал нужной формы (например, синусоидальный). При этом функствйем управляющего кода Kfm преобразует ее в неравномерную последовательность со средней частотой

FCP-klKbs

I ср

от

пропуская на выход Крт импульсов из каждых 2. Выходная последовательность управляемого делителя 7, импульсы которой из-за внутренних задержек запаздывают по отнощению к соответствующим импульсам выходной последовательности опорного генератора 1 на время туд, поступает на D-вход триггера 8. На тактовый вход (С-вход) которого с выхода первого элемента задержки 5 поступает последовательность импульциональныи преобразователь 4 может состо- опорного генератора 1, задержанная отять либо из последовательно соединенных„осительно исходной на т, т.д + 1„, где

блока управления, линии задержки, делите- подготовки D-триггера 8. Таким

ля частоты и фильтра нижних частот, ли-образом обеспечивается устойчивое формибо из последовательно соединенных постоян-рование выходного сигнала D-триггера 8.

ного запоминающего устройства, цифроана-Равномерная последовательность частоты логового преобразователя и фильтра нижних до ,, задержанная на (т, + тг) относительно частот (на чертеже не показаны).

Принцип действия цифрового синтезатора частот основан на том, что количество разрядов п кода Кф, необходимого для работы функционального преобразователя 4, меньвыходнои последовательности опорного генератора 1, формируется на выходе второго элемента задержки б (вносимая им задержка Т2 равна времени задержки переключения D-триггера 8) и поступает на таквыходнои последовательности опорного генератора 1, формируется на выходе второго элемента задержки б (вносимая им задержка Т2 равна времени задержки переключения D-триггера 8) и поступает на такше количества разрядов управляющего кода 35 товый вход п-разрядного накапливающего Krtm+. с выходов блока формирования ко-сумматора 3. В каждом такте к содержимода 2. Обычно п не превыщает 8-10 разрядов, в то время как величина (т + п), определяемая требуемым количеством синтезируемых частот, может достигать 32 и более - выхоца триггера 8 пос- разрядов. Разрядность накапливающего сум- 40

матора 3 равна требуемой разрядности п„ ереноса «единица Полная емность накода фазы К,.. При этом на управляющий вход накапливающего сумматора 3 поступает

му накапливающего сумматора 3 прибавляется двоичное число КРП, если на вход переноса накапливающего сумпереноса «единица.

капливающего сумматора 3 соответствует фазе 2SV7Q, где Q - целое число, определяе„мое конкретной структурой функциональнодами управляющего кода Число возможных 5 преобразователя 4. Поэтому на каждом

OiTOiiQLJTJtJl/i no К-VМгтппгчпч/исшигт

такте фаза синтезируемого колебания увеличивается на фо 2jfKFn/Q-2 или на ф| 2jr(Kp,+ l)/Q-2 .

В течение цикла работы синтезатора, т.е. 2( тактов (Тц 2 + Ьт) с выхода пульсы. В эти такты к содержимому накап- 50 О-триггера 8 поступает X, 2.Кг. «еди- ливающего сумматора 3 прибавляется не ) и Хо

Крп, а (Крп + 1), за счет чего средняя. v тм/и

скорость накопления кода фазы и синтезируемая частота повыщаются.

Формирование корректирующей последовательности выполняет управляемый делитель 7. D-триггер 8 служит для обеспечекод Kf/i, образованный п старшими разрязначений кода Крл - 2. Для получения нужного количества синтезируемых частот на вход переноса накапливающего сумматора 3 в oпpeдeлeV ныe тактовые моменты подаются корректирующие единичные имниц ( из каждых Г ) и ло 2 () «нулей. Тогда XQ раз фаза увеличивается на фо и Х: раз - на ф. Полная фаза за цикл равна

Ф

Фохо + ф,х, - -2 (2- Кг4+

ния длительности корректирующих импуль- -fK ).2S- v сов, равной длительности тактового интер- у Q л . вала Тг. Первый и второй элементы задержки 5 и 6 компенсируют задержки в управляемом делителе частоты 7 и D-тригге- ре 8, обеспечивая необходимое временное соответствие сигналов.

Блок формирования кода 2 вырабатывает (т + п)-разрядный код частоты Кр.

Очевидно Кр Кр„ + . Равномерная последовательность с частотой т поступает на тактовый вход ш-разрядного

управляемого делителя 7, который под действйем управляющего кода Kfm преобразует ее в неравномерную последовательность со средней частотой

FCP-klKbs

I ср

от

пропуская на выход Крт импульсов из каждых 2. Выходная последовательность управляемого делителя 7, импульсы которой из-за внутренних задержек запаздывают по отнощению к соответствующим импульсам выходной последовательности опорного генератора 1 на время туд, поступает на D-вход триггера 8. На тактовый вход (С-вход) которого с выхода первого элемента задержки 5 поступает последовательность импуль опорного генератора 1, задержанная отРавномерная последовательность частоты ,, задержанная на (т, + тг) относительно

выходнои последовательности опорного генератора 1, формируется на выходе второго элемента задержки б (вносимая им задержка Т2 равна времени задержки переключения D-триггера 8) и поступает на тактовый вход п-разрядного накапливающего сумматора 3. В каждом такте к содержимотовый вход п-разрядного накапливающего сумматора 3. В каждом такте к содержимо - выхоца триггера 8 пос-

му накапливающего сумматора 3 прибавляется двоичное число КРП, если на вход переноса накапливающего сумВ течение цикла работы синтезатора, т.е. 2( тактов (Тц 2 + Ьт) с выхода О-триггера 8 поступает X, 2.Кг. «еди- ) и Хо

. v тм/и

ниц ( из каждых Г ) и ло 2 () «нулей. Тогда XQ раз фаза увеличивается на фо и Х: раз - на ф. Полная фаза за цикл равна

Ф

Фохо + ф,х, - -2 (2- Кг4+

Такому фазовому набегу за время Ти соответствует средняя частота

2rK,f. д-2 Г2 ° -)

JT-KF

g.2teitn.-)

На основе информации, поступающей с выхода накапливающего сумматора 3, функциональный преобразователь 4 формирует аналоговый сигнал заданной формы. В зависимости от типа применяемого функционального преобразователя эта информация может состоять из кода фазы Кф, кода частоты Kfn и сигнала переполнения Р в любых сочетаниях.

Корректирующая последовательность, подаваемая на вход переноса накапливающего сумматора 3, формируется управляемым делителем 7 с некоторыми ощибками. Импульс на вход переноса может прийти несколько раньще или позже, чем это необходимо для точного формирования кода фазы Кф. Эти ощибки приводят к появлению ощибо вычисления кода фазы Кср, которые циклически повторяются. Длина каждого цикла тактов.

При соответствующем выборе алгоритма работы управляемого делителя 7 величина ошибок достаточно мала. Если эта величина не превышает q единиц младще- го разряда, то точный р-разрядный выходной код фазы может быть получен при использовании (р+Ч)-разрядного накапливающего сумматора 3. Предельная частота тактирования накапливающего сумматора уменьшается с ростом числа разрядов, что связано с уменьшением быстродействия входящего в его состав комбинационного сумматора. Поэтому диапазон синтезируемых частот расширяется с уменьшением разрядности используемого накапливающего сумматора. Управляемые делители частоты при соответствующей реализации работоспособны на более высоких частотах, чем накапливающие сумматоры, выполненные на той же элементной базе, и их быстро5

действие на диапазон синтезируемых частот практически не влияет.

В предлагаемом устройстве за счет умень- щения требуемой разрядности накапливающего сумматора расширяется диапазон синтезируемых частот. Например, для получения 2 частот можно использовать не 32-х, а 8-разрядный накапливающий сумматор.

В качестве управляемого делителя 7 может быть использована, например, микро- 0 схема К 155 ИЕ 8, а блок формирования кода 2 может быть выполнен в виде переключателей и преобразователей кодов.

Таким образом, основное преимущество цифрового синтезатора частот заключается в расширении диапазона синтезируемых частот и его применение позволяет на основе метода прямого синтеза, обуславливающего высокую скорость переключения частот, решать задачи, ранее разрешимые лишь методами косвенного синтеза частот.

Формула изобретения

Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор и управляемый делитель частоты, последовательно соединенные накапли- 5 вающий сумматор и функциональный преобразователь, а также блок формирования кода частоты, выход старших разрядов которого подключен к .управляющему входу накапливающего сумматора, отличающийся тем, что, с целью расширения диапазона выходных частот, между выходом опорного генератора и тактовым входом накапливающего сумматора введены последовательно соединенные первый элемент задержки и второй элемент задержки, а также введен D-триггер, выход которого подключен к входу переноса накапливающего сумматора, тактовый вход и D-вход D-триггера соответственно подключены к выходу первого элемента задержки и выходу управляемого делителя частоты, управляющий вход которого соединен с выходом младших разрядов блока формирования кода частоты.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| ЦИФРОВОЙ ГЕНЕРАТОР ДЛЯ ЦИФРОВЫХ СЛЕДЯЩИХ СИСТЕМ КОРРЕЛЯЦИОННОЙ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2180125C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1684906A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| Цифровой синтезатор частоты | 1979 |

|

SU855935A1 |

| Цифровой синтезатор частоты прямого действия | 1989 |

|

SU1621170A2 |

| Цифровой синтезатор частоты | 1980 |

|

SU966849A2 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

Изобретение относится к радиотехнике и обеспечивает расширение диапазона выходных частот. Цифровой синтезатор содержит опорный генератор 1, блок 2 формирования кода частоты, накапливающий сумматор (НС) 3, функциональный преобразователь 4, элементы задержки 5 и 6, управляемый делитель 7 частоты и D-триггер 8. Блок 2 формирует управляющий код частоты Кг п старших разрядов кода Кг поступают на управляющий вход НС 3, а m млад- щих разрядов - на управляющий вход управляемого делителя 7. В НС 3 формир-уется код фазы К( синтезируемого колебания. Предельная тактовая частота определяется числом разрядов п. Информация с НС 3 преобразуется функциональным преобразователем 4 в аналоговый сигнал нужной формы. Разрядность кода K:f меньше разрядности управляющего кода Kf. Код Кф имеет не более 8-10 разрядов, а разрядность кода Kf может достигать 32. Для получения нужного количества синтезируемых частот на вход переноса НС 3 в определенные тактовые моменты подаются корректирующие единичные импульсы. Формирование корректирующей последовательности выполняет управляемый делитель 7. D-триггер 8 обеспечивает требуемую длительность корректирующих импульсов. 1 ил. to (Л to со о 4

| Гнашек Ю., Р | |||

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям | |||

| Изд-во Радио и связь, 1982, с | |||

| Гудок | 1921 |

|

SU255A1 |

| Авторское свидетельство СССР № 1157641, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-22—Подача