112

Изобретение относится к вычислительной технике и может найти применение в многомашинных вычислительных комплексах.

Цель изобретения - увеличение быстродействия.

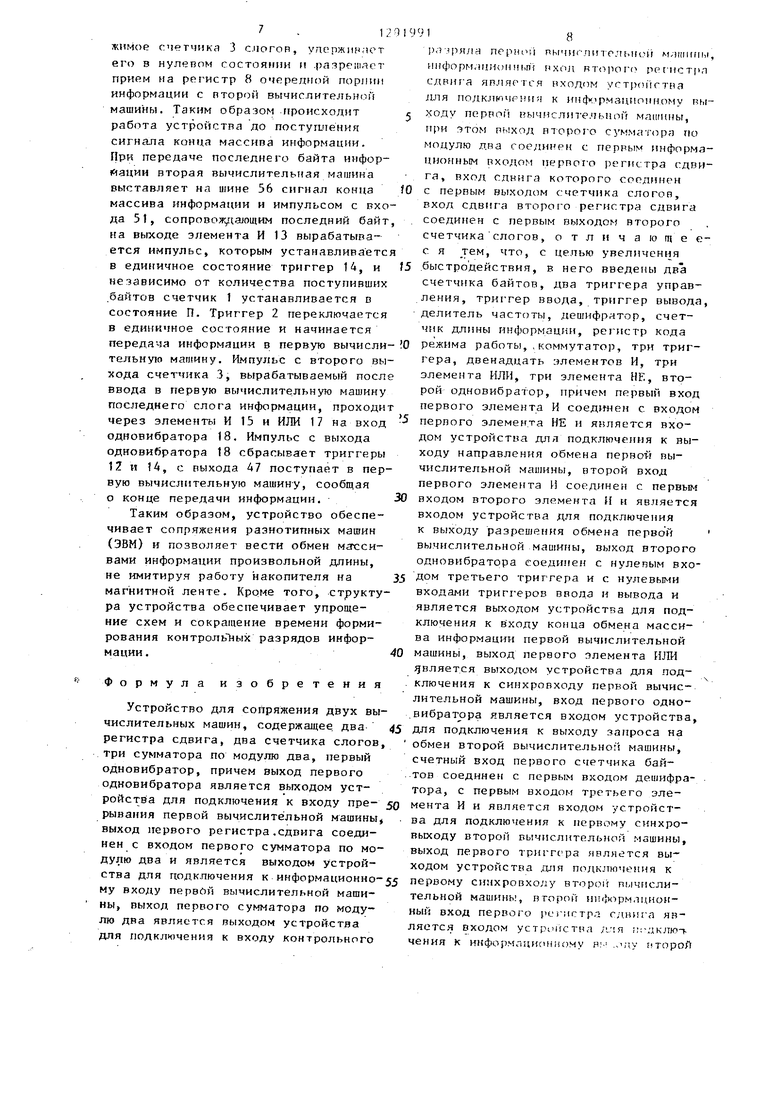

На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит первый счетчик 1 байтов, первый триггер 2 ления, первый счетчик 3 слогов, первый одновибратор 4, дешифратор 5 первый тригг;ер 6,. седьмой элемент И 7, первый регистр 8 сдвига, первый сумматор 9. по модулю два, второй сумма- тор 10 по модулю два, делитель 11 частоты, триггер 12 вывода, элемент И 1-, третий триггер 1А, шестой и девятый элементы И 15 и 16, второй элемент ИЛИ 17, второй одно- вибратор 18, первый элемент И 19, первый элемент НЕ 20, четвертый элемент И 21, счетчик 22 длины информации, девятый, второй, пятый элементы И 23 - 25, регистр 26 кода режима работы, второй элемент НЕ 27, триггер. 28 ввода, третий cy fмaтop 29 по модулю два, коммутатор 30, третий элемент ИЛИ 31, второй регистр 32 сдвига, первый элемент ИЛИ 33, второ триггер 34, одиннадцатый, восьмой, двенадцатый элементы И 35 - 37, третий элемент НЕ 38, второй счетчик 39 байтов, второй триггер 40 управления второй счетчик 41 слогов, выходы 42 прерывания, первый информационный Bui ход 43, выход 44 контрольного разряд слог а, вход 45 направления обмена, , вход 46 разрешения обмена, первый выход 47 конца массива информации, первый синхровыход 48, первый инфор- мационныИ вход 49, вход 50 запроса на обмен, первый синхровход 51, второй синхровыход 52, второй информационный вход 53, .вход 54 контрольного разряда байта, вход 55 синхроимпульсов, вход 56 конца массива информации, второй выход 57 конца массива информации, выход 58 эапроса на обме второй синхровход 59, второй инфо.р- мационный выход 60, выход 61 контролного разряда байта, третий синхровыход 62.

Устройство работает следун)щим об- разом.

В исходном по:гожении триггер 2, 6 12, 14, 28, 34 и 40, счетчики 1,3, 22 и 41, сумматор 10 и рег истр 8 находятся н нулевом состоянии. Нулевое состояние триггера 40 удержипает второй счетчик 39 байтов в состоянии П, где - число, равное объему регистра сдвига в байтах..

При наличии в первой вычислительной машине массива информации, подготовленного для передачи во вторую вычислительную машину, на первый информационный вход 49 подается первый слог информации, а на шинах 45 и 46 устанавливают сигналы направле(ия и разрешения обмена, которые вырабатывают на выходе элемента И 24 потенциал, соответствующий логической едини.- це и устанавливают триггер ввода 28 в единичное состояние. При единичном состоянии триггера 28 через элемент И 36 проходят синхроимпульсы, которые поступают на вход прямого счета счетчика 41 . Нулевое состояние триггера 40 разрешает работу счетчика 41. Каждый импульс увеличивает состояние счетчика-41 на единицу. При состоянии последнего, равном единице на его первом выходе вырабатывается импульс, который производит запись первого слога информации со сдвигом на один разряд. При состоянии счетчика 41 , тавном двум, на его втором кы- ходе вырабатывается импульс, котор 1 й через элемент ИЛИ 33 по шине 48 выдается в качестве сигнала подтверждения приема устройством перво- го слога информации.

I ..

После этого первая вычислительная

машина на входе 49 выставляет второй слог информации. Третий и четвертый синхроимпульсы обеспечивают прием второго слога и таким образом продолжается прием остальных слогов до заполнения ре-гистра 32 полным машинным словом. При переполнении счетчика 41 слогов на его третьем выходе вырабатывается сигнал, соответствующий логической един1 це. Первое слово массива информации является управляющим словом для устройства сопряжения, В момент приема управляющего слова содержимое счетчика 22 равно нулю и сигнал с его второго выхода разрешает прохождение импульса, вырабатъ - вающегося на третьем выходе счетчика 41 слогов, через элемент И 23. Импульс с выхода элемента И 23 обеспечивает запись в счетчик 22 из регистра 32 части управляющего слова, указывающей длину передаваемого массива

31

информации в бяйтах, запись в регистр 26 части управляющего слова, содержащей код режима работы, и переводит счетчик А1 слогов в начальное состояние. После этого, на регистр 32 принимается второе машинное слово,

В начале обмена идет режим установления связи. Поэтому в регистр 26 Записывается код установления связи, а в счетчик 22 - единица, так как ад pec процессора-абонента определяется одним байтом. При этом на выходе 58 устанавливается потенциал, соответствующий логической единице. Сам же адрес содержится в старших разрядах второго машин ного слова. При не нулевом состоянии счетчика 22 длины информации на его втором выходе вырабатывается потенциал, разрешающий работу элемента -И 35, А при состоя- НИИ счетчика 22, меньшем или равном сигнал с первого его выхода разрешает работу элемента И 16, После прием на регистр 32 второго машинного слов импульс третьего выхода счетчика 41 слогов проходит через элементы И 16 и ИЛИ 17 на вход второго одновибрато ра 18 и, приходя через элемент И 35, устанавливает триггер 40 в единичное состояние. Импульс с выхода одновиб- ратора 18/устанавливавт триггер 28: ввода в начальное состояние и через выход 47 поступает в первую вычислительную машину. Приняв этот сигнал, первая вычислительная машина снимает с шин 45 и 46 сигналы направления и разрешения обмена. Единичное состояние триггера 40 разрешает работу счетчика 39 байтов. Первый выход счечика 39 управляет работой коммул-атор При состоянии П счетчика 39 байтов с выхода коммутатора I на второй информационный выход 60 выставляется старший байт слова, содержащегося в регистре 32, При этом на выходе 61 выставляется контрольньй разряд по четности для информации на выходе 60 Сигнал с второго выхода счетчика 39 разрешает работу элемента И 37. Потенциал с единичного выхода триггера 40 устанавливает триггер 34-в единичное состояние. Сигнал с единичного выхода триггера 34 передается с выхода 62 во вторую вычислительную машину в качестве импульса сопровождения информации на выходах 60, 61 и 58. Сигнал запроса на обмен на выходе 58 указывает на то, что на выходе 60 стоит байт, указывающий ад

O 5 0 чика

рес процессора, с которым усгячаплч- Е ается связь. На импульс с выхода 62 вторая вычислительная машина отвечает по шине 59 импульсом подтверждения .приема информации. Этот импульс поступает на вычитающие входы счетчиков 22 и 39, уменьшая их содержимое на , на нулевой вход триггера 34 и, приходя через элементы If 25 и ИЛИ 31, устанавливает триггер 40 в пулевое состояние. Если вторая вычислительная машина готова . к обмену по шине 50 поступает сигнал, -по которому одновибратор 4 вырабатывает импульс прерывания. Этот импульс с выхода 42 поступает в первую вычислительную машину. После этого первая вычислительная машина выставляет на шинах 45 и 46 сигналы направления и разрешения обмена и производит выдачу массива информации.

В начале массива информации идет управляющее слово. В счетчик 22 записывается число, соотве тствующее ко- -5 личеству байтов информации, передаваемых во вторую вычислительную наfO/5 20 О чика

30

шину. Б регистр 26 записывается код режима передачи информации. При. этом второй выход регистра имеет единичное значение. После приема в регистр 32 второго машинного слова потенциал на втором выходе счетчика 22 разрешает работу элемента И 35. Импульс с третьего выхода счетчика 41, выра35 батывающийся в момент его переполнения, устанавливает триггер 40 в единичное состояние. Единичное состояние триггера 40 запрещает работу счетчика 41 и разрешает работу счет39 и элемента И 37. Так как состояние счетчика 39 равно П, то . первым на выходе коммутатора 30 выставляется старший байт машинного слова, содержащегося в регистре 32.

5 Во всех состояниях счетчик 39, отличных от нулевого, на его втором выходе устанавливается потенциал, соответствующий логическому нулю. Поэтому триггер 34 устанавливается в единичное состояние, на выходе 62 устройства вырабатывается импульс сопровождения информации на шинах 60 и 61. Вторая вычислительная машина отвечает по шиИе 59 импульсом подтверждения приема информации, который отвечает по шине 59 импульсом подтпержденяя приема информации, который уменьшает содержимое счетчиков 22 и 39 на единицу. Затем во вторун) машину переда0

5

отся (П-1)ый байт и таким образом продолжается выдача,всех остальньгх байтов с регистра 32 до обнуления содержимого счетчика 39, При нулевом состоянии счетчика 39 импульс с его второго выхода, проходя через элемент ИЛИ 3, устанавливает триггер 40 в нулевое состояние. Начинается прием на регистр 32 третьего машинного сло

гистра 8 и коитрольгюго рлчрпда v с от8етсткую11 ий. счетным триггер форлги рователя, а импульс с втгфог о ныход дешифратора 5 переводит триггер 6 в состояние. Тригтер 6 рабатывает импульс ответа о приеме байта, который выдается с выхода 52 во вторую вычислительную машину для сброса имяульса сопровождения иква и таким образом процесс продолжа- tO Формации и возвращается в исходное

состояние. Каждый импульс сопровождения информации увеличивает содержимое счетчика 1 байтов на единицу, При переполнении счетчика 1 иа его втором выходе вырабатывается импуль который производит запись контрол ь- Khix разрядов машинного слова с выхода сумматора 10 в регистр 8 и пер водит триггер 2 управления в единич ное состояние. Потенциал, соответствующий логической едргкице с единичного выхода триггера 2 сбрасывае содержимое счетчика. 1 и удерживает его в нулевом состоянии. Потенциал, соответствующий логическому нудю с нулевого выхода триггера 2 запрещ ет работу дешифратора 5 и разрешлйт работу счетчика слогов 3. Когда т первой вычислительной машине управление г ерейдет к. программе обрабстк прерывания по запросу на обмен, на шинах 45 и 46 выставляются сигналы направления и разрешения обмена, ко торые через элемент И 19 устапаБ;:Н- вают триггер 12 вывода в единичное состояние. Единичное состояние триг гера 12 разрешает прохождение синхроимпульсов через элемент И 7 на вход прямого счета счетчика 3 слого При работе счетчика 3 на его третьем и первом выходах поочередно, выра батываются импульсы. Импульс с третьего выхода .счетчика 3 через элемент ИЛИ 33 с выхода 48 выдается в первую вычислительную машину и стробирует каждый слог и его контрольный разряд, выдаваемые по шинам 43 и 44. Импульс с первого выхода счетчика 3 реализуют сдвиг содержи

20

25

ется до обнуления содержимого счетчика длины ин4юрмации 22, При вводе в регистр 32 последнего машинного слова, содержимое счетчика 22 равно или меньше П, иа первом ныходе. счетчика . 5 22 устанавливается сигнал высокого уровня. После приема в регистр 32 последнего слова Импульс с третьего выхода счетчика 41 слогов проходит через элементы И 16 и ИЛИ 17 на вход одиовибратора 18. Импульс .с выхода последнего устанавливает триггер 28 ввода в начальное состояние и по выходу 47 поступает в первую вычислительную машину в качестве сигнала конца массива информации. В момент вывода во вторую машину последнего байта информации содержимое счетчика 22 равно единице и на выходе 57 устройства устанавливается потенциал, соответствующий логической единице. Импульс подтверждения приема байта с входа 59 проходит через элементы И 25 и ИЛИ 31 и устанавливает триггер АО в исходное состояние. После 35 завершения передачи информации из первой-машины во вторую может идти режим передачи информации из второй машины в первую, либо на этом завершается обмен.40

При обмене информацией по инициативе второй вычислительной машины на вход 50 поступает сигнал запроса на обмен. При этом одновибратор 4 вырабатывает импульс прерывания, который 45 с выхода 42 подается в первую вычислительную машину. По шинам 51, 53 и 54 поступают импульс сопровождения информации, байт информации и его

30

состояние. Каждый импульс сопрово дения информации увеличивает соде жимое счетчика 1 байтов на единиц При переполнении счетчика 1 иа ег втором выходе вырабатывается импу который производит запись контрол Khix разрядов машинного слова с вы хода сумматора 10 в регистр 8 и п водит триггер 2 управления в един ное состояние. Потенциал, соответ ствующий логической едргкице с ед ничного выхода триггера 2 сбрасыв содержимое счетчика. 1 и удерживае его в нулевом состоянии. Потенциа соответствующий логическому нудю с нулевого выхода триггера 2 запр ет работу дешифратора 5 и разрешл работу счетчика слогов 3. Когда т первой вычислительной машине упра ление г ерейдет к. программе обрабс прерывания по запросу на обмен, н шинах 45 и 46 выставляются сигнал направления и разрешения обмена, торые через элемент И 19 устапаБ; вают триггер 12 вывода в единично состояние. Единичное состояние тр гера 12 разрешает прохождение син хроимпульсов через элемент И 7 на вход прямого счета счетчика 3 сло При работе счетчика 3 на его трет ем и первом выходах поочередно, вы батываются импульсы. Импульс с тр тьего выхода .счетчика 3 через эле мент ИЛИ 33 с выхода 48 выдается в первую вычислительную машину и стробирует каждый слог и его конт рольный разряд, выдаваемые по шин 43 и 44. Импульс с первого выхода счетчика 3 реализуют сдвиг содерж

контрольный разряд. При приеме инфор- 50 ° регистра 8 на один разряд к

мации с второй вычислительной машины в регистр 8 счетчик 1 байтов считает от О до П. Импульс с первого выхода дешифратора 5, вырабатываемый в момент поступления на его первый вход импульса сопровождения информации, обеспечивает запись в зависимости от состояния счетчика 1 байта информации в г(-;ответствующие рйзрядь рет

/:919916

гистра 8 и коитрольгюго рлчрпда v со- от8етсткую11 ий. счетным триггер форлги- рователя, а импульс с втгфог о ныходя дешифратора 5 переводит триггер 6 в состояние. Тригтер 6 рабатывает импульс ответа о приеме байта, который выдается с выхода 52 во вторую вычислительную машину для сброса имяульса сопровождения икФормации и возвращается в исходное

состояние. Каждый импульс сопровождения информации увеличивает содержимое счетчика 1 байтов на единицу, При переполнении счетчика 1 иа его втором выходе вырабатывается импульс, который производит запись контрол ь- Khix разрядов машинного слова с выхода сумматора 10 в регистр 8 и переводит триггер 2 управления в единичное состояние. Потенциал, соответствующий логической едргкице с единичного выхода триггера 2 сбрасывает содержимое счетчика. 1 и удерживает его в нулевом состоянии. Потенциал, соответствующий логическому нудю с нулевого выхода триггера 2 запрещает работу дешифратора 5 и разрешлйт работу счетчика слогов 3. Когда т первой вычислительной машине управление г ерейдет к. программе обрабсткк , прерывания по запросу на обмен, на шинах 45 и 46 выставляются сигналы направления и разрешения обмена, которые через элемент И 19 устапаБ;:Н- вают триггер 12 вывода в единичное состояние. Единичное состояние триггера 12 разрешает прохождение синхроимпульсов через элемент И 7 на вход прямого счета счетчика 3 слогов. При работе счетчика 3 на его третьем и первом выходах поочередно, вырабатываются импульсы. Импульс с третьего выхода .счетчика 3 через элемент ИЛИ 33 с выхода 48 выдается в первую вычислительную машину и стробирует каждый слог и его контрольный разряд, выдаваемые по шинам 43 и 44. Импульс с первого выхода счетчика 3 реализуют сдвиг содержи

подготавливают тем самым к выдаче следующий слог информации. С передачей последнего слога на втором вы- .ходе счетчика 3 вырабатывается им- 5 пульс, который переводит триггер 2 управления в нулевое состояние, сбрасывает содержимое регистра 8 и сумматора 10, Триггер 2 управления своим нулевым выходом сбрасывает содержимое спетчнка 3 слогов, упепжинает его в нулевом состоянии я .разрешает прием на регистр 8 очередной порнии информации с второй вычислительной машины. Таким образом происходит работа устройстпа до постуштения сигнала конца массива информации. При передаче последнего байта информации вторая вычислительная машина выставляет на шине 56 сигнал конца массива информации и импульсом с входа 51, сопровож;(ая)щнм последний байт на выходе элемента И 13 вырабатывается импульс, которым устанавливаетс в единичное состояние триггер 14, и независимо от количества поступивших .байтов счетчик 1 устанавливается в состояние П. Триггер 2 переключается в единичное состояние и начинается

передача информации в первую вычисли- 0 режима работы, .коммутатор, три триг- тельную машину. Импульс с второго вы- гера, двенадцать элементов И, три хода счетчика 3, вырабатываемый после элемента ИЛИ, три элемента НЕ, вто- ввода в первую вычислительную машину последнего слога информации, проходит

рой одновибратор, причем первый вход первого элемента И соедт1ен с входом

через элементы И 15 и ИЛИ 17 на вход первого элемента НЕ и является вхоодновибратора 18. Импульс с выхода одновибратора 18 сбрасывает триггеры 12 и М, с выхода 47 поступает в первую вычислительную машину, сообщая о конце передачи информации.

Таким образом, устройство обеспечивает сопряжения разнотипных машин (ЭВМ) и позволяет вести обмен мах:си- вами информации произвольной длины, не имитируя работу накопителя на магнитной ленте. Кроме того, структура устройства обеспечивает упрощение схем и сокращение времени формирования контроль 1ых разрядов информации.

Формула изобретения

является выходом устройства для под- . ключения к синхровходу первой вычислительной машины, вход первого одно- .вибратрра является входом устройства для подключения к выходу запроса на обмен второй вычислительной машины, счетный вход первого счетчика байтов соединен с первым входом дешифра тора, с первым входом третьего элеУстройство для сопряжения двух вычислительных машин, содержащее, два 45 регистра сдвига, два счетчика слогов, три сумматора по модулю два, первый одновибратор, причем выход первого одновибратора является выходом устройства для подключения к входу пре- 50 мента И и является входом устройст- рывания первой вычислительной машины, . ва для подключения к первому синхро- выход первого регистра .сдвига соеди- выходу второй вычислительной машины, ней с входом первого сумматора по мо- выход первого триггс-ра является вы- дулю два и является выходом устрой- ходом устройства для подключения к ства для подключения к информационно-55 первому синхровхолу второй пычпсли- му входу первйй вычислительной маши- тельной машины, второй ииформ.чционны, выход первого сумматора по модулю два является выходом устройства для подключения к входу контрольного

1) г.1ряла nepiUMi пычяглитольн(.П1 млшкги,,

ИНфорМ,И ИСИННЫ7Ч ЛХОЛ RTdllOrC 1ПП-ИСТ)Л

сдвига япляртся нходом устройгтяа для подключения к инф .рмациопр1ому выходу nopnofi вычисл11те. 7ьной маигины, мри этом пыход нюрого сумматора по модулю два coe/iMHf-M{ с перрым информационным входом перпог о регистра сдвига, вход сдвига которого соодинен

с первым выходом счетчика слогов, вход сдвига второг о регистра сдвига соединен с первым выходом второго счетчика слогов, отличающее- с я тем, что, с целью увеличения

быстродействия, в него введены два счетчика байтов, два триггера управления, триггер ввода, триггер вывода, делитель частоты, дешифратор, счетчик длины информации, регистр кода

режима работы, .коммутатор, три триг- гера, двенадцать элементов И, три элемента ИЛИ, три элемента НЕ, вто-

рой одновибратор, причем первый вход первого элемента И соедт1ен с входом

дом устройства для подключения к выходу направления обмена первой вычислительной машины, второй вход первого элемента И соединен с первым

входом второго элемента И и является входом устройства для подключения к выходу разрешения обмена первой вычислительной маишпы, выход второго одновибратора соединен с нулевым входом третьего триггера и с нулевьпчи входами триггеров ввода и вывода и является выходом устройства для подключения к в ходу конца обмена массива информации первой вычислительной

машины, выход первого элемента ИЛИ

является выходом устройства для под- ключения к синхровходу первой вычислительной машины, вход первого одно- .вибратрра является входом устройства, для подключения к выходу запроса на обмен второй вычислительной машины, счетный вход первого счетчика байтов соединен с первым входом дешифратора, с первым входом третьего элемента И и является входом устройст- ва для подключения к первому синхро- выходу второй вычислительной машины, выход первого триггс-ра является вы- ходом устройства для подключения к первому синхровхолу второй пычпсли- тельной машины, второй ииформ.чционный вход первого регистра сдвига является входом ycrpiufCTna лчя ;;;-лклю-т. чения к инфор. -итциониому н. - ...ту нтороЛ

912

вычислительно машины, перяый вход второго сумматора по модулю два япля ется входом устройства для подключения к выходу контрольного разряд-а байта второй вычислительной машины, второй вход третьего 3J eMenTa И яв- Д тется входом устройства для подключения к выходу конца обмена MaccHFja информации второй вычислительной машины, выход четвертого элемента И является-выходом устройства для подключения к входу конца обмена массива информация второй вычислительной MauiHHbi, нервьш выход рег истра кода режима работы является выходом устройства для подключения к входу за- hpoca на обмен второй вычислительной машины, счетш1 1 вход счетчика длины информации соединен с первым входом пятого элемента И, с у.Г1евь м ;.ходом второго триггера, со счетным входом второго счетчика байтов и явл яется входом устройст.ва для подключения

к второму СИНХРОВЫХОДУ второй П1,ЧИС

лительной машины, выход коммутатора соединен с входом третьего сумматора по модулю два и является выходом устройства для подключения к информационному Входу второй вычислительной машины, выход третьего сyr-iMaтора по моду.чю два является выходом устройства для Г1с1дкл1очепия к входу контрольного разряда байта второй вычислительной машины, выход B l oporo триггера является выходом устройства для подключения к второму сипхровходу второй вычислительной машины, вход делителя частоты соединен с син- хровходами первого и второго триггеров управления, первого, второг о и третьего триггеров и является входом устройства для подключения к выходу генератора c лнxpoи шyльcoв, при этом первый иых(;д первого счетчика байтов соединен с нторым входом дешифратора, трет1-нЧ вход которого соединен с устгтмоиочнымц яхода- ми первого счетчика слогов и с нулевым выходом первого триггера уг рав- ления, единичный выход которого соединен с установочным входом первог о счетчика байтов, второй выход которого соединен с первым входом записи первого регистра сдвига и с единичным входом первого триггера управления, нулевой вход которого С осдннен с вторым выходом первого счетчика слогов, с вторым входом BTOpoi o сумматора по мг.чцулю дла, г nepi bir-s irxo- 5

19Ч110

дом iiiecTor o элемента И и с установочным входом регистра сдвига, второй лход записи которого и третий вход зторого сумматора по модул два соединены с первым выходом дешифратора, второй выход которого соединен с единичным .входом первого тригтера, нулевой пход которого соединен с шиной единичного потенциала устройства, O вход записи первого счетчика байтов соединен с выходом третьего элемента И и единичным входом третьего триггера, выход которого соединен с вторым входом шестого элемента И, 15 выход которого соединен с первьм входом второго элемента ИЛИ, выход которого соединенс входом второго од- новибратора, выход делителя частоты соединен с первыми входами седьмого. 0 и восьмого элементов И, с синхровхо- дами Tpvirrepa ввода и триггера вьшо- да, выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с счетными входом первого четчика слогов, третий выход которого соединен с первым входом первого элемента.ИЛИ, второй вход которого соединен с вторы - выходом второго счетчика слогов, счетный вход 30 которогс соединен с выходом восьмого эле.мента И, второй вход которого соединен с выходом триггера ввода единичный вход которого соединен с выходом второго элемента И, второй вход 35 которого соединен с выходом первого элемента НЕ,, выход первого элемента И соединен с единичным входом триггера вывода, второй вход второго элемента ИЛИ соединен с выходом девятого 40 элемента И, первый вход которого соединен с первым выходом счетчика длины И 1формации5 второй выход которого соединен с первым входом десятого элемента И и с вхоДом второго элемен- 45 та НЕ, выход которого соединен с первым входом одиннадцатого элемента И, второй вход которого соединен с вторыми входами девятого и десятого 3Jie- мента И и с третьим выходом второго 50 счетчика слогов, установочный вход которого соединен с выходом десятого элемента И, с синхровходом счетчика дпяны информации и с синхровходами регистра кода режима работы, мнформа- 55 ционный вход которого -соедмнен с информационными входом счетчика длины информации, с выходом второго регистра сдвига и: с информационным входом коммутатора управляющий пко1 кото11

poro соединен с перпым выходом второго счетчика байтов, пторой выход которого соединен с первым входом третьего элемента ИЛИ и с входом тре- тьего элемента НЕ, выход которого со- единен с первым входом двенадцатого элемента И, выход которого соединен с единичным входом второго триггера, Ьторой выход регистра кода режима работы соединен с первым входом чет- вертого элемента И, второй вход которого соединен с третьим выходом счетчика длины информации и с вторым вхо5 О 199112

дом пятого элемента Н, нцход которого соединен с вторим входом третьег о элемента ИЛИ, пыход которого соединен с нулевым сходом второго триггера управления, единичный вход которого соединен с выходом одиннадцатого эле- мер1та И, вход записи второго счетчика слогов соединен с нулевым выходом второго триггера управления, единичный выход которого соединен с входом записи второго счетчика байтов и с вторым входом двенадцатого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1979 |

|

SU849191A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1983 |

|

SU1198529A1 |

| УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ Л1ЕЖДУ АБОНЕНТАМИ И ЦВМ | 1973 |

|

SU368607A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

Изобретение относится к вычислительной технике и может найти при енение в многомашинных вычислительных комплексах. Основной целью изобретения является увеличение быстродействия и упрощение устройства. Устройство содержит два регистра 8 32 сдвига, два счетчика 3., 41 слогов, три сумматора 9, 10, 24 по модулю два, два одновибратора 4/ 18, два счетчика 1, 39 байтов,- два триггера 3, 40 управления, триггер 28 ввода, триггер, 12 вывода, делитель частоты 11, дешифратор 5, счетчик 22 длины информации, регистр 26 кода режима работы, коммутатор 30, три триггера 6, 14, 38, двенадцать элементов И 7, 13,. 15, 16, 21, 23-25, 35- 37, 19, три элемента ИЛИ 33, 17, 31, три 20, 27, 38 .элемента НЕ. 1 ил. о S (Л С

| Устройство для сопряжения вычислительных машин | 1977 |

|

SU732845A1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1976 |

|

SU634265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-08-13—Подача