Изобретение относится к вычислительной технике и может быть использовано при создании высокопроизводительных вычислительных систем.

Цель Изобретения - повышение быстродействия и надежности устройства.

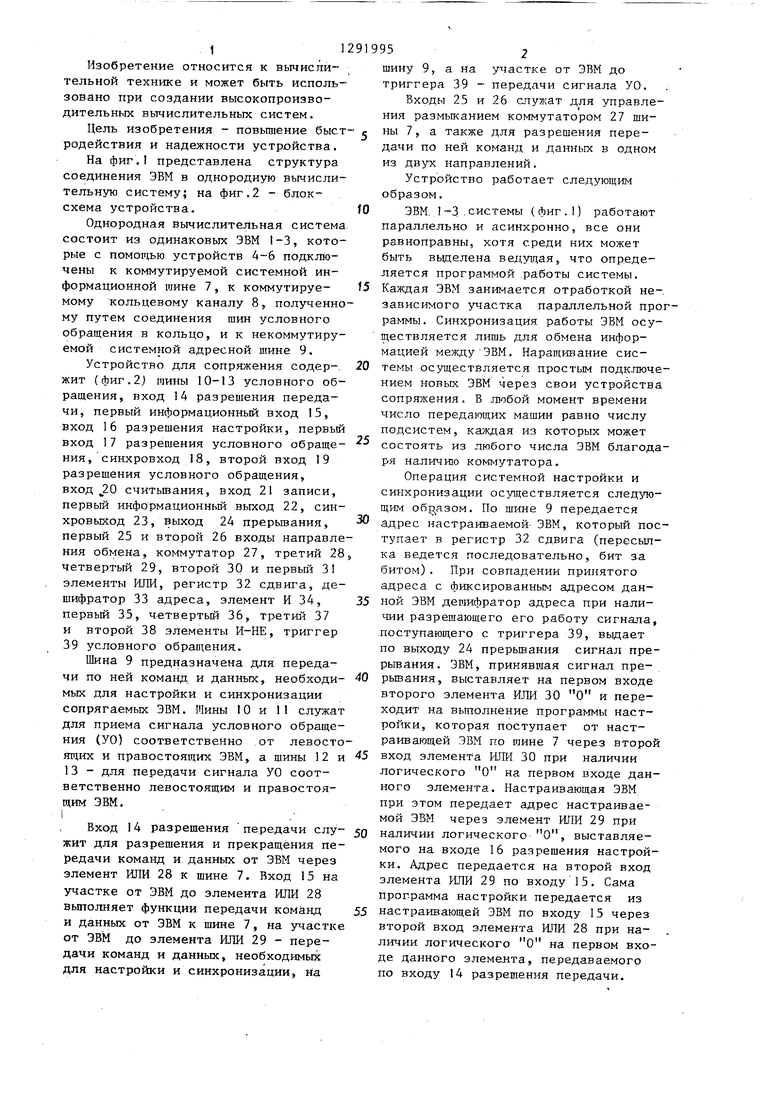

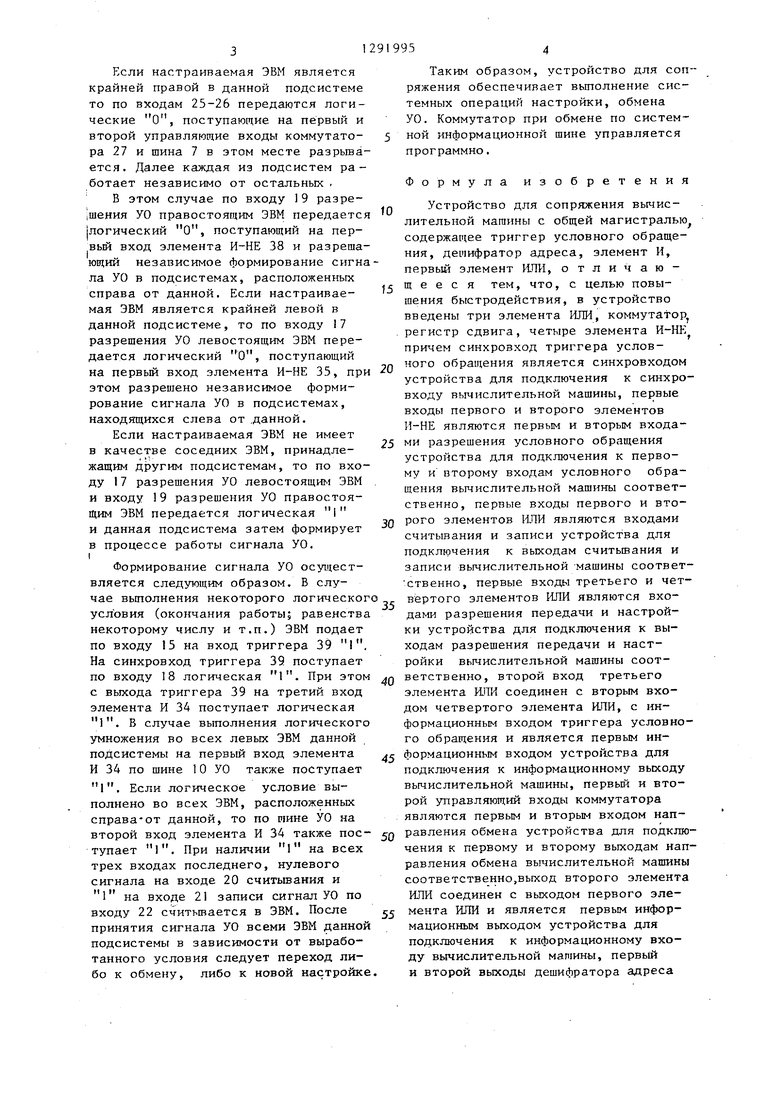

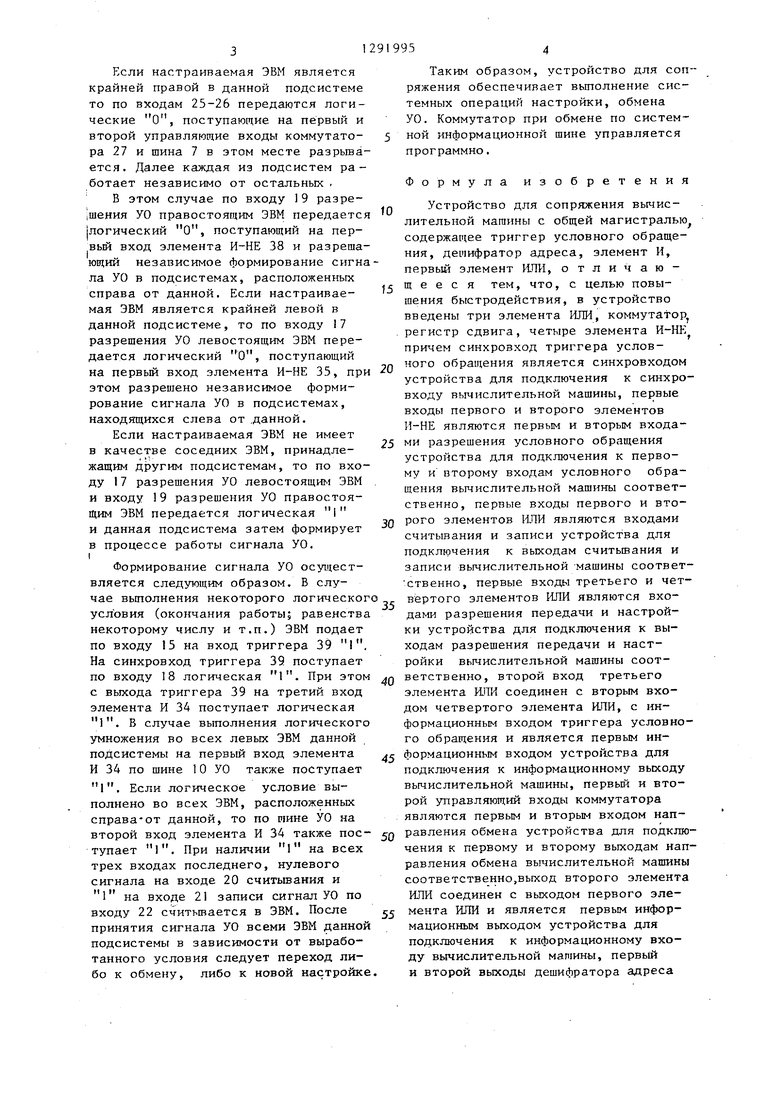

На фиг.1 представлена структура соединения ЭВМ в однородную вычислительную систему; на фиг.2 - блок- схема устройства.

Однородная вычислительная система состоит из одинаковых ЭВМ 1-3, которые с помощью устройств 4-6 подключены к коммутируемой системной информационной шине 7, к коммутируемому кольцевому каналу 8, полученному путем соединения шин условного обращения в кольцо, и к некоммутируемой системной адресной шине 9.

Устройство для сопряжения содер-. жит (фиг.2) шины 10-13 условного обращения, вход 14 разрешения передачи, первый информационный вход 15, вход 16 разрешения настройки, первый

вход 17 разрешения условного обращения, с инхровход 18, второй вход 19 разрешения условного обращения, вход 20 считьюания, вход 21 записи, первый информационный выход 22, син- хровыход 23, выход 24 прерьгоания, первый 25 и второй 26 входы направления обмена, коммутатор 27, третий 28 четвертый 29, второй 30 и первьм 3 элементы ИЛИ, регистр 32 сдвига, дешифратор 33 адреса, элемент И 34, первый 35, четвертый 36, третий 37 и второй 38 элементы И-НЕ, триггер 39 условного обращения.

Шина 9 предназначена для передачи по ней команд и данных, необходимых для настройки и синхронизации сопрягаемых ЭВМ. Шины 10 и 11 служат для приема сигнала условного обращения (УО) соответственно от левосто и правостоящих ЭВМ, а шины 12 и 13 - для передачи сигнала УО соответственно левостоящим и правостоя- щим ЭВМ.

Вход 14 разрешения передачи служит для разрешения и прекращения передачи команд и данных от ЭВМ через элемент ИЛИ 28 к шине 7. Вход 15 на участке от ЭВМ до элемента ИЛИ 28 вьтолняет функции передачи команд и данных от ЭВМ к шине 7, на участке от ЭВМ до элемента ИЛИ 29 - передачи команд и данных, необходимых для настройки и синхронизации, на

5

0

5

0

5

S

шину 9, а на участке от ЭВМ до триггера 39 - передачи сигнала УО.

Входы 25 и 26 служат для управления размыканием коммутатором 27 шины 7, а также для разрешения передачи по ней команд и данных в одном из двух направлений,

Устройство работает следующим образом.

ЭВМ, 1-3 .системы (фиг.1) работают параллельно и асинхронно, все они равноправны, хотя среди них может быть вьщелена ведущая, что определяется программой .работы системы. Каждая ЭВМ занимается отработкой независимого участка параллельной программы. Синхронизация работы ЭВМ осуществляется лишь для обмена информацией между ЭВМ. Наращивание системы осуществляется простым подк.гаоче- нием новых ЭВМ через свои устройства сопряжения. В любой момент времени число передающих машин равно числу подсистем, каждая из которых может состоять из любого числа ЭВМ благодаря наличию коммутатора.

Операция системной настройки и синхронизации осуществляется следующим o6ija3OM. По шине 9 передается адрес настраиваемой- ЭВМ, который поступает в регистр 32 сдвига (пересылка ведется последовательно, бит за битом). При совпадении принятого адреса с фиксированным адресом данной ЭВМ дешифратор адреса при наличии разрешающего его работу сигнала, поступающего с триггера 39, выдает по выходу 24 прерьшания сигнал прерывания. ЭВМ, принявшая сигнал прерывания, выставляет на первом входе второго элемента ИЛИ 30 О и переходит на выполнение программы настройки, которая поступает от настраивающей ЭВМ по шине 7 через второй вход элемента И1Ы 30 при наличии логического О на первом входе данного элемента. Настраивающая ЭВМ при этом передает адрес настраиваемой ЭВМ через элемент ИЛИ 29 при наличии логического О, выставляемого на входе 16 разрешения настройки. Адрес передается на второй вход элемента ИЛИ 29 по входу 15. Сама Программа настройки передается из 5 настраивающей ЭВМ по входу 15 через второй вход элемента ИЛИ 28 при наличии логического О на первом входе данного элемента, передаваемого по входу 14 разрешения передачи.

0

0

Если настраиваемая ЭВМ является крайней правой в данной подсистеме то по входам 25-26 передаются логические О, поступающие на первый и второй управляющие входы коммутато- ра 27 и шина 7 в этом месте разрьша ется. Далее каждая из подсистем работает независимо от остальных ,

В этом случае по входу 19 разре- |шения УО правостоящим ЭВМ передаетс логический О, поступающий на пер- |Вый вход элемента И-НЕ 38 и разрешающий независимое формирование сигнла УО в подсистемах, расположенных справа от данной. Если настраивав- мая ЭВМ является крайней левой в данной подсистеме, то по входу 17 разрешения УО левостоящим ЭВМ передается логический О, поступающий на первый вход элемента И-НЕ 35, пр этом разрешено независимое формирование сигнала УО в подсистемах, находящихся слева от .данной.

Если настраиваемая ЭВМ не имеет в качестве соседних ЭВМ, принадлежащим другим подсистемам, то по входу 17 разрещения УО левостоящим ЭВМ и входу 19 разрешения УО правостоя- Щим ЭВМ передается логическая 1

и данная подсистема затем формирует в процессе работы сигнала УО.

Формирование сигнала УО осугцест- вляется следующим образом. В случае выполнения некоторого логическог условия (окончания работы; равенства некоторому числу и т.п.) ЭВМ подает по входу 15 на вход триггера 39 1. На синхровход триггера 39 поступает по входу 18 логическая 1. При этом с выхода триггера 39 на третий вход элемента И 34 поступает логическая 1. В случае выполнения логического умножения во всех левых ЭВМ данной подсистемы на первый вход элемента И 34 по шине 10 УО также поступает 1. Если логическое условие выполнено во всех ЭВМ, расположенных справа-от данной, то по иине УО на второй вход элемента И 34 также пос- тупает 1. При наличии 1 на всех трех входах последнего, нулевого сигнала на входе 20 считывания и 1 на входе 21 записи сигнал УО по входу 22 считывается в ЭВМ. После принятия сигнала УО всеми ЭВМ данной подсистемы в зависимости от выработанного условия следует переход либо к обмену, либо к новой настройке

5

0

5

0

5

Q 0

Таким образом, устройство для сопряжения обеспечивает вьтолнение системных операций настройки, обмена УО. Коммутатор при обмене по системной информационной шине управляется программно.

Формула изобретения

Устройство для сопряжения вычислительной машины с общей магистралью содержащее триггер условного обращения, дешифратор адреса, элемент И, первый элемент ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены три элемента ИЛИ, коммутатор регистр сдвига, четыре элемента И-НЕ причем синхровход триггера условного обращения является синхровходом устройства для подключения к синхро- входу вычислительной машины, первые входы первого и второго элементов И-НЕ являются первым и вторым входами разрешения условного обращения устройства для подключения к первому и второму входам условного обращения вычислительной машины соответственно, первые входы первого и второго элементов ИПИ являются входами считывания и записи устройства для подключения к выходам считьюания и записи вычислительной машины соответ- ственно, первые входы третьего и четвертого элементов ИЛИ являются входами разрешения передачи и настройки устройства для подключения к выходам разрешения передачи и настройки вычислительной машины соответственно, второй вход третьего элемента ИЛИ соединен с вторым входом четвертого элемента ИЛИ, с информационным входом триггера условного обращения и является первым информационным входом устройства для подключения к информационному выходу вычислительной машины, первый и второй управляющий входы коммутатора являются первым и вторым входом направления обмена устройства для подключения к первому и второму выходам направления обмена вычислительной машины соответственно.выход второго элемента ИЛИ соединен с выходом первого элемента ИЛИ и является первым информационным выходом устройства для подключения к информационному входу вычислительной машины, первьй и второй выходы дешифратора адреса

51

являются синхропыходом и выходом прерывания устройства для подключения к синхровходу и входу прерывания вычислительной машины соответственно, выход третьего элемента ИЛИ и второй вход второго элемента ИЛИ являются вторыми информационными выходом и входом устройства соответственно для подключения к системной информационной шине общей магистрали, выход четвертого элемента ИЛИ и информационный вход регистра сдвига являются адресными выходом и входом устройства соответственно для Подключения к системной адресной шине общей магистрали, первый и второй информационные входы/выходы коммутатора являются первым и вторым инфо{ 1ационньми входами/выходами устройства для подключения к системной информационной шине обП7 i

Редактор В.Петращ

Составитель С.Пестмал Техред Л. Сердюкова

Закаэ 273/49 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

919956

щей магистрали, выходы первого и второго элементов И-FJE являются первым и вторым выходами условно -о обращения устройства, первый вход элемента

5 И соединен с первым входом третьего элемента И-НЕ и является первым входом условного обращения устройства, второй вход элемента И соединен с первым входом четвертого элемента

Ю И-НЕ и является вторым входом условного обращения устройства, при этом управляю1 5ий вход дешифратора адреса соединен с третьим входом элемента И

с выходом триггера условного обращения и с вторыми входами третьего и четвертого элементов И-НЕ, выходы которых соединены с вторыми входами второго и первого элементов И-НЕ соответственно, выход элемента И соединен с вторым входом первого элемента ИЛИ.

7

Корректор Л.Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения для однородной вычислительной системы | 1981 |

|

SU1068928A1 |

| Устройство для подключения ЭВМ к системной шине | 1986 |

|

SU1361571A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1986 |

|

SU1365090A2 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения | 1986 |

|

SU1327116A2 |

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1273940A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании высокопроизводительных вычислительных систем. Цельк) изобретения является повышение быстродействия устройства. Устройство содержит триг- рег 39 условного обращения, регистр 32 сдвига, дешифратор 33 адреса, коммутатор 27, четыре элемента ИЛИ 28, 29, 30, 31, четыре элемента И-НЕ, элемент И 34. 2 ил. W J5 9 . i (Л N3 СО СП 2526

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для сопряжения вычислительных машин в однородной вычислительной системе | 1981 |

|

SU1076893A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-09-05—Подача