1 12937

Изобретение относится к вычислительной технике, может быть использовано в высокопроиэводительнь х вычислительных системах и наибо; ее эффективно в системах с автоматически перестраиваемой, динамической архитектурой.

Цель изобретения - повышение быстродействия.

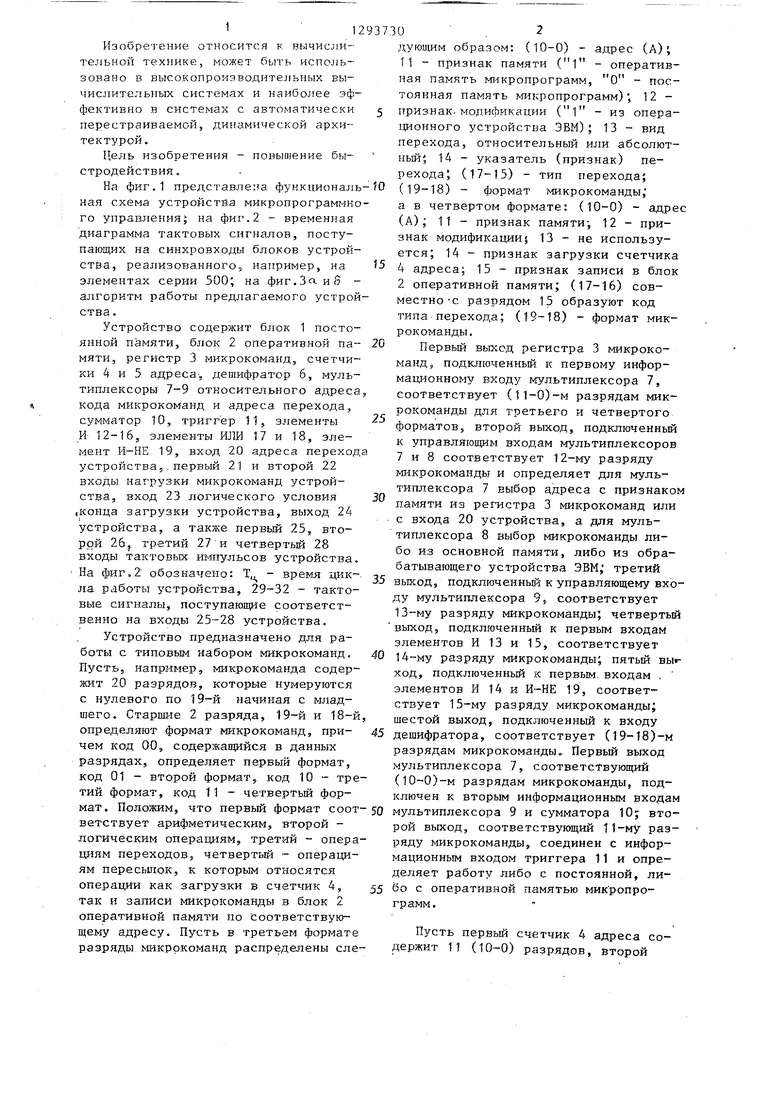

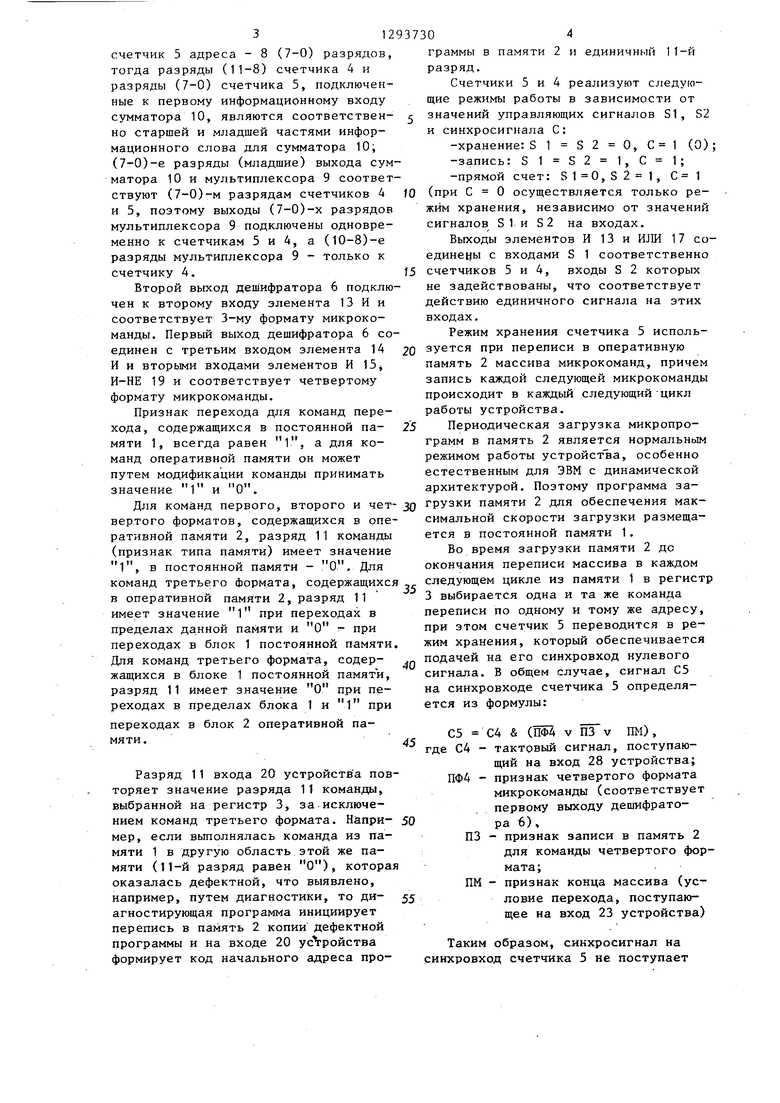

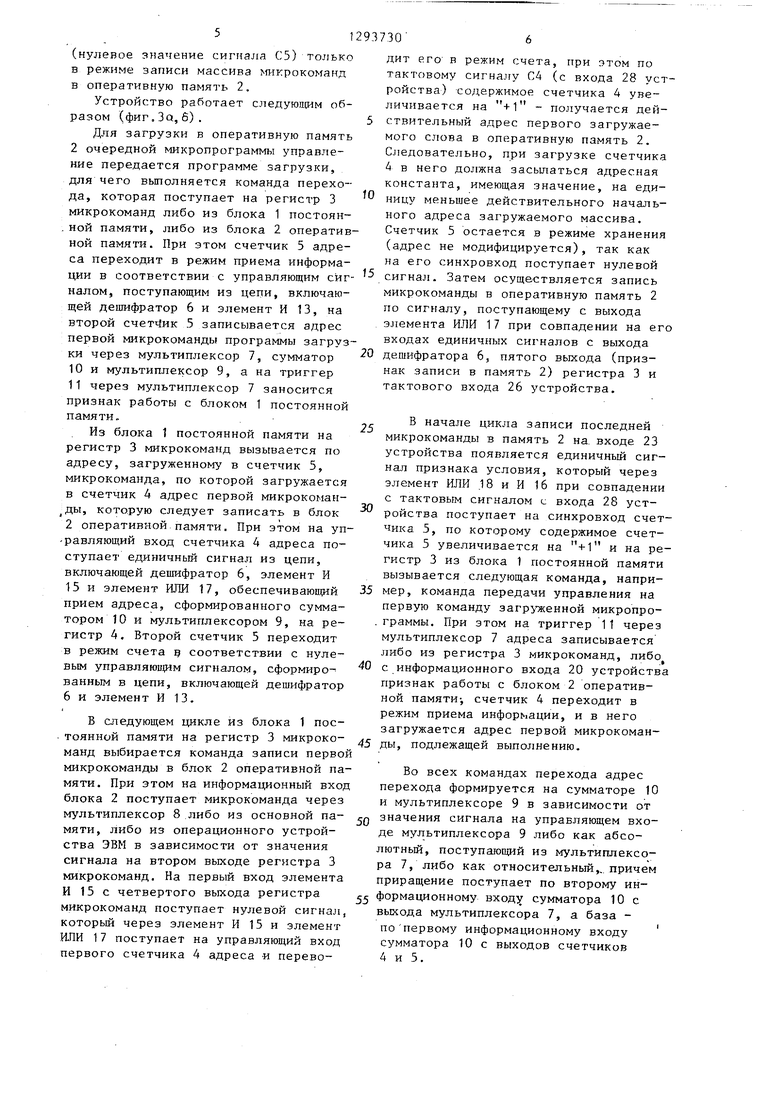

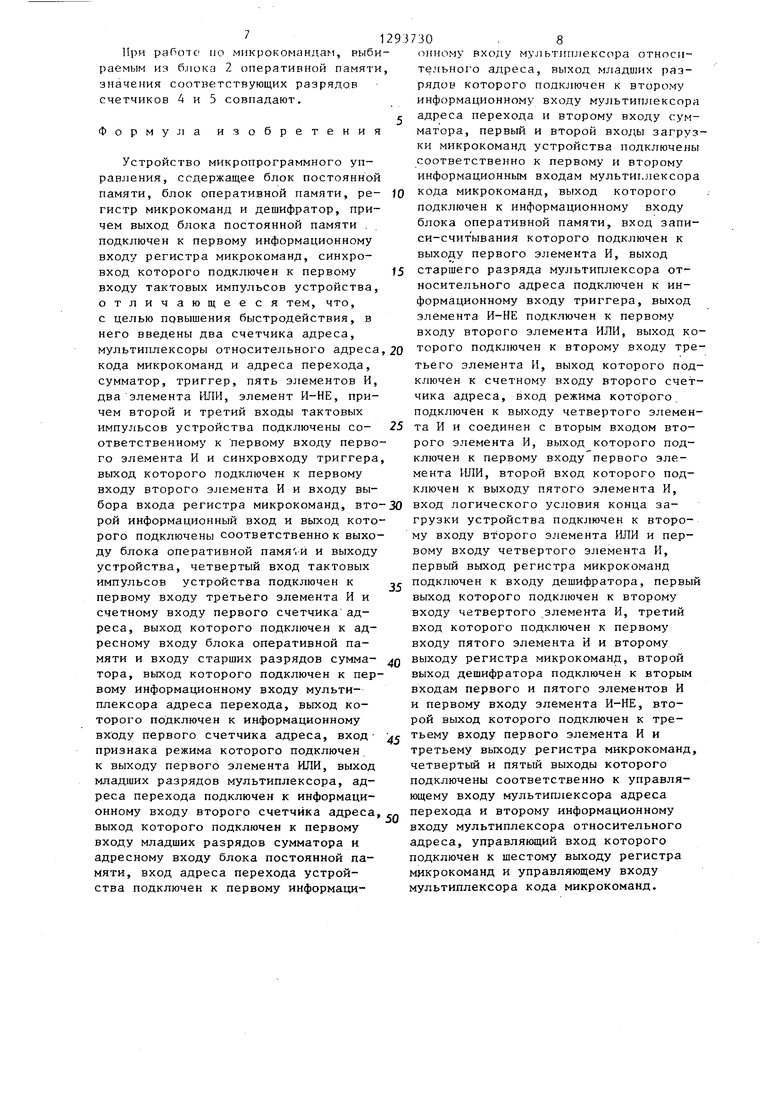

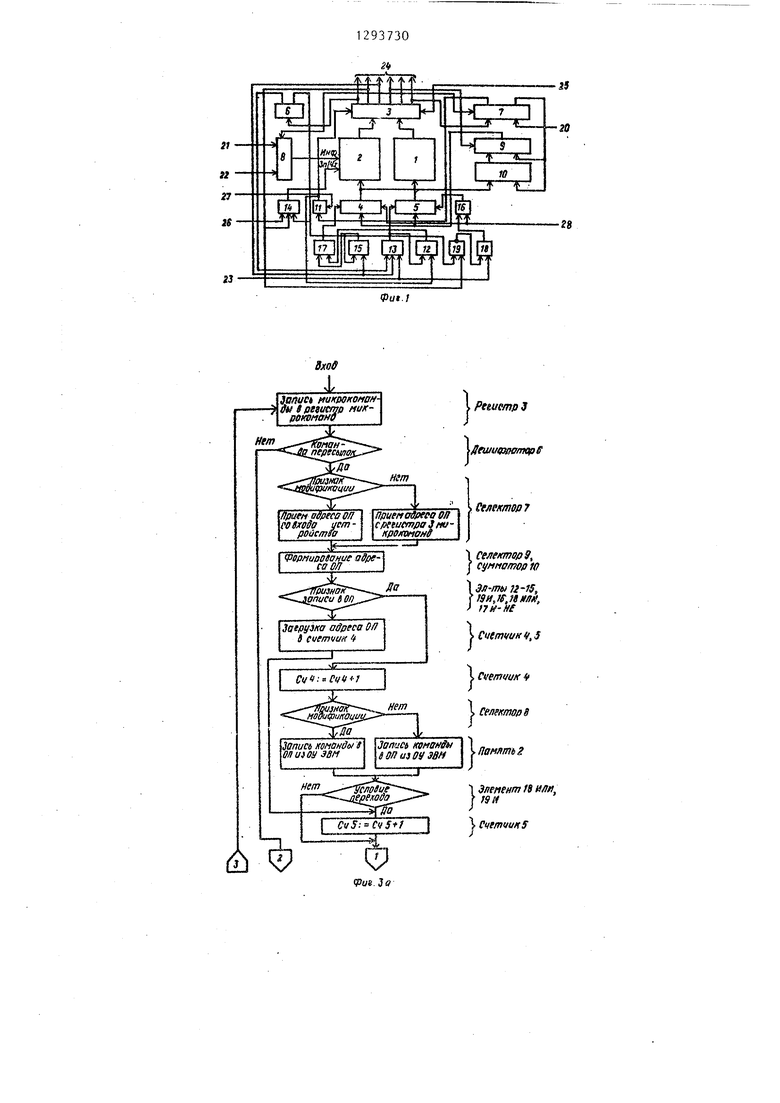

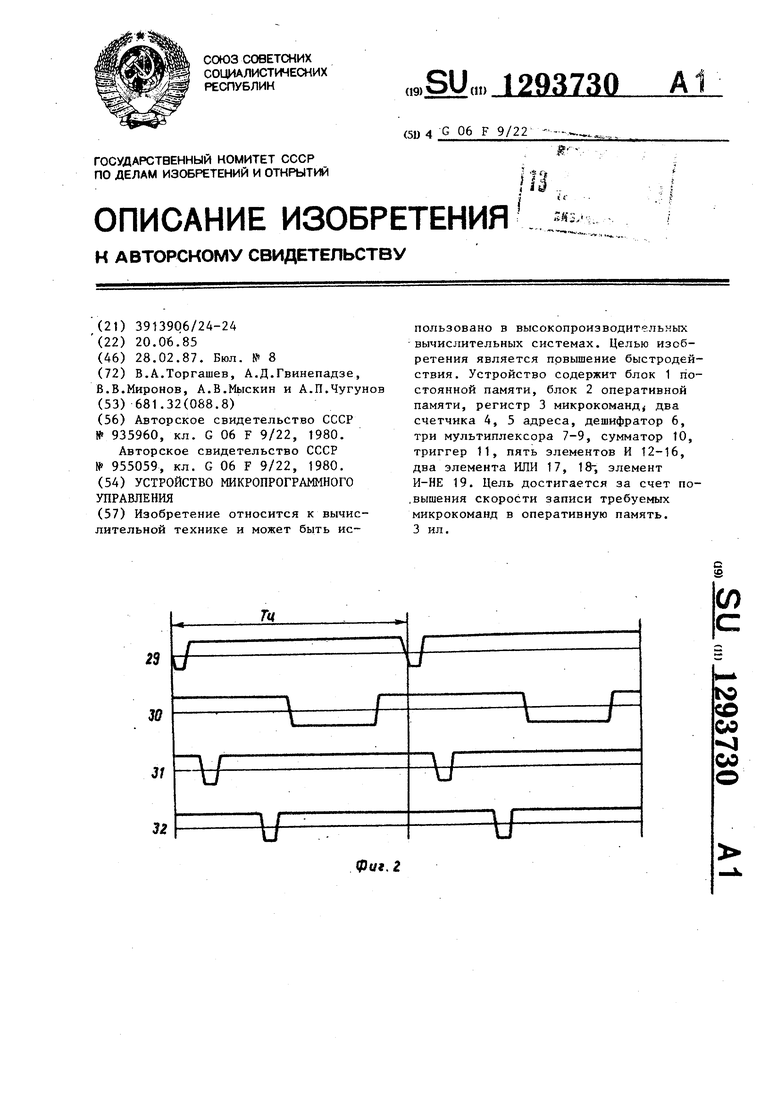

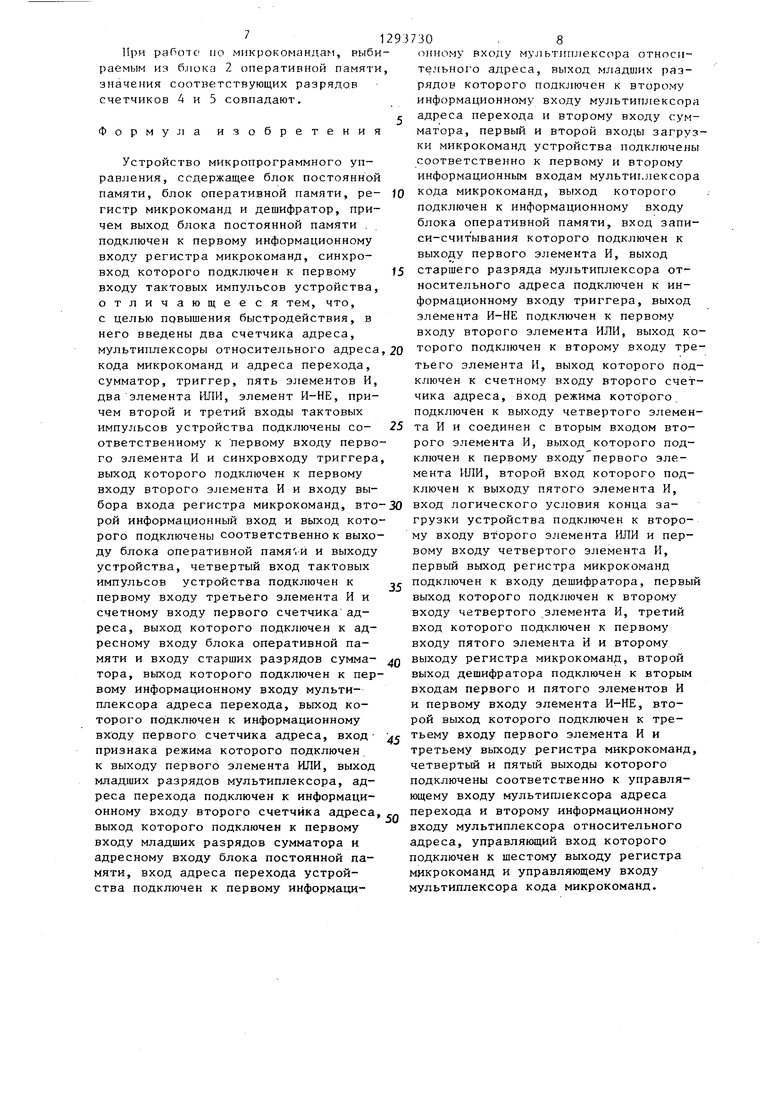

На фиг.1 представлена функциональ-Ш ная схема устройства микропрограммного управления; на фиг.2 - временная диаграмма тактовых сигналов, поступающих на синхровходы блоков устройства, реализованного, например, на 55 элементах серии 500; на фиг.3л и $ - алгоритм работы предлагаемого устройства .

Устройство содержит блок 1 постоянной памяти, блок 2 оперативной па- 20 мяти, регистр 3 микрокоманд, счетчики 4 и 5 адреса-, дешифратор 6, мультиплексоры 7-9 относительного адреса, кода микрокоманд и адреса перехода, сумматор 10, триггер 11, злементы И 12-16, элементы ИЛИ 17 и 18, элемент И-НЕ 19, вход 20 адреса перехода устройства,. первый 21 и второй 22 входы нагрузки микрокоманд устройства, вход 23 логического условия 30 конца загрузки устройства, выход 24 устройства, а также первый 25, второй 26J третий 27 и четвертый 28 входы тактовых иг- Шульсов устройства. На фиг.2 обозначено: Т - время дик- j ла работы устройства, 29-32 - тактовые сигналы, поступающие соответственно на входы 25-28 устройства.

Устройство предназначено для работы с типовым набором микрокоманд. 40 Пусть, например, микрокоманда содержит 20 разрядов, которые нумеруются с нулевого по 19-й начиная с младшего. Старшие 2 разряда, 19-й и 18-й, определяют формат микрокоманд, при- 45 чем код 00, содержащийся в даннь х разрядах, определяет первый формат, код 01 - второй формат, код 10 - третий формат, код 11 - четвертый формат. Положим, что первый формат соот-50 ветствует арифметическим, второй - логическим операциям, третий - операциям переходовS четвертый - операциям пересьиок, к которым относятся операции как загрузки в счетчик 4, 55 так и записи микрокоманды в блок 2 оперативной памяти по соответствующему адресу. Пусть в третьем формате разряды шкppкoмaнд распределены сле0 . 2 дующим образом: (10-0) - адрес (А); 11 - признак памяти (1 - оперативная память микропрограмм, О - постоянная память микропрограмм); 12 - признак, модификации (1 - из операционного устройства ЭВМ); 13 - вид перехода, относительный или абсолютный , 14 - указатель (признак) перехода (17-15) - тип перехода; (19-18) - формат микрокоманды, а в четвертом формате: (10-0) - адрес (А); 11 - признак памяти-, 12 - признак модификации} 13 - не используется; 14 - признак загрузки счетчика 4 адреса; 15 - признак записи в блок 2 оперативной памяти; (17-16) совместно -с разрядом 15 образуют код типа-перехода; (19-18) - формат микрокоманды.

Первый выход регистра 3 микрокоманд, подключенньй к первому информационному входу мультиплексора 7, соответствует (11-0)-м разрядам микрокоманды для третьего и четвертого, форматов, второй выход, подключенньй к управляющим входам мультиплексоров 7 и 8 соответствует 12-му разряду микрокоманды и определяет для мультиплексора 7 выбор адреса с признаком памяти из регистра 3 микрокоманд или с входа 20 устройства, а для мультиплексора 8 выбор микрокоманды либо из основной памяти, либо из обрабатывающего устройства ЭВМ; третий выход, подключенньй к управляющему вхоу мультиплексора 9, соответствует 13-му разряду микрокоманды; четвертый выход, подключенный к первым входам элементов И 13 и 15, соответствует 14-му разряду микрокоманды; пятый вы«- ход, подключенный к первым, входам - элементов И 14 и И-НЕ 19, соответствует 15-му разряду микрокоманды; шестой выход, подключенный к входу дешифратора, соответствует (19-18)-м разрядам микрокоманды.. Первый выход мультиплексора 7, соответствующий (10-0)-м разрядам микрокоманды, подключен к вторым информационным входам мультиплексора 9 и сумматора 10; второй выход, соответствующий 11-му разряду микрокоманды, соединен с информационным входом триггера 11 и определяет работу либо с постоянной, либо с оперативной памятью микропрограмм.

Пусть первый счетчик 4 адреса содержит 11 (10-0) разрядов, второй

счетчик 5 адреса - 8 (7-0) разрядов, тогда разряды (11-8) счетчика 4 и разряды (7-0) счетчика 5, подключенные к первому информационному входу сумматора 10, являются соответствен- но старшей и младшей частями информационного слова для сумматора 10; (7-0)-е разряды (младшие) выхода сумматора 10 и мультиплексора 9 соответствуют (7-0)-м разрядам счетчиков 4 10 и 5, поэтому выходы (7-0)-х разрядов мультиплексора 9 подключены одновременно к счетчикам 5 и 4, а (10-8)-е разряды мультиплексора 9 - только к счетчику 4.

Второй выход де111ифратора 6 подключен к второму входу элемента 13 И и соответствует 3-му формату микрокоманды. Первый выход дешифратора 6 соединен с третьим входом элемента 14 20 И и вторыми входами элементов И 15 И-НЕ 19 и соответствует четвертому формату микрокоманды.

Признак перехода для команд перехода, содержащихся в постоянной па- 25 мяти 1, всегда равен 1, а для команд оперативной памяти он может путем модификации команды принимать

граммы в памяти 2 и единичный 1 1-й разряд.

Счетчики 5 и 4 реализуют следующие режимы работы в зависимости от значений управляющих сигналов S1, S2 и синхросигнала С:

-хранение: S 1 S 2 О, С 1 (0) -запись: , -прямой счет: ,, (при С О осуществляется только режим хранения, независимо от значений сигналов S1 и S2 на входах.

Выходы элементов И 13 и ИЛИ 17 со единецы с входами S 1 соответственно счетчиков 5 и 4, входы S 2 которых не задействованы, что соответствует действию единичного сигнала на этих входах.

Режим хранения счетчика 5 используется при переписи в оперативную память 2 массива микрокоманд, причем запись каждой следующей микрокоманды происходит в каждый следующий цикл работы устройства.

Периодическая загрузка микропрограмм в память 2 является нормальньм режимом работы устройстЪа, особенно естественным для ЭВМ с динамической архитектурой. Поэтому программа зазначение 1 и О,

Для команд первого, второго и чет- ЗО грузки памяти 2 для обеспечения мак- вертого форматов, содержащихся в one- симальной скорости загрузки размеща- ративной памяти 2, разряд 11 команды (признак типа памяти) имеет значение 1, в постоянной памяти - О. Для команд третьего формата, содержащихся в оперативной памяти 2, разряд 11

35

имеет значение

rt II

при переходах в пределах данной памяти и О - при переходах в блок 1 постоянной памяти. Для команд третьего формата, содержащихся в блоке 1 постоянной памяти, разряд 11 имеет значение О при переходах в пределах блока 1 и l при

переходах в блок 2 оперативной памяти.

40

45

ется в постоянной памяти 1.

Во время загрузки памяти 2 до окончания переписи массива в каждом следующем цикле из памяти 1 в регистр 3 выбирается одна и та же команда переписи по одному и тому же адресу, при этом счетчик 5 переводится в режим хранения, который обеспечивается подачей на его синхровход нулевого сигнала. В общем случае, сигнал С5 на синхровходе счетчика 5 определяется из формулы:

С5 С4 & (ПФА V nFv ИМ), где С4 - тактовый сигнал, поступающий на вход 28 устройства; ПФ4 - признак четвертого формата микрокоманды (соответствует первому выходу дешифратора 6) , ПЗ - признак записи в память 2

Разряд 11 входа 20 устройства повторяет значение разряда 11 команды, выбранной на регистр 3, за.исключением команд третьего формата. Напри- мер, если вьтолнялась команда из памяти 1 в другую область этой же памяти (11-й разряд равен О), которая оказалась дефектной, что выявлено, например, путем диагностики, то ди- агностирующая программа инициирует перепись в память 2 копии дефектной программы и на входе 20 устройства формирует код начального адреса программы в памяти 2 и единичный 1 1-й разряд.

Счетчики 5 и 4 реализуют следующие режимы работы в зависимости от значений управляющих сигналов S1, S2 и синхросигнала С:

-хранение: S 1 S 2 О, С 1 (0) -запись: , -прямой счет: ,, (при С О осуществляется только режим хранения, независимо от значений сигналов S1 и S2 на входах.

Выходы элементов И 13 и ИЛИ 17 со единецы с входами S 1 соответственно счетчиков 5 и 4, входы S 2 которых не задействованы, что соответствует действию единичного сигнала на этих входах.

Режим хранения счетчика 5 используется при переписи в оперативную память 2 массива микрокоманд, причем запись каждой следующей микрокоманды происходит в каждый следующий цикл работы устройства.

Периодическая загрузка микропрограмм в память 2 является нормальньм режимом работы устройстЪа, особенно естественным для ЭВМ с динамической архитектурой. Поэтому программа загрузки памяти 2 для обеспечения мак- симальной скорости загрузки размеща-

ется в постоянной памяти 1.

Во время загрузки памяти 2 до окончания переписи массива в каждом следующем цикле из памяти 1 в регистр 3 выбирается одна и та же команда переписи по одному и тому же адресу, при этом счетчик 5 переводится в режим хранения, который обеспечивается подачей на его синхровход нулевого сигнала. В общем случае, сигнал С5 на синхровходе счетчика 5 определяется из формулы:

С5 С4 & (ПФА V nFv ИМ), где С4 - тактовый сигнал, поступающий на вход 28 устройства; ПФ4 - признак четвертого формата микрокоманды (соответствует первому выходу дешифратора 6) , ПЗ - признак записи в память 2

для команды четвертого формата;

ПМ - признак конца массива (условие перехода, поступающее на вход 23 устройства)

Таким образом, синхросигнал на синхровход счетчика 5 не поступает

fO

51293730

(нулевое значение сигнала С5) только в режиме записи массива шкpoкo faнд в оперативную память 2.

Устройство работает следуюп1им образом (фиг. За, 6) .

Для загрузки в оперативную память 2 очередной микропрограммы управление передается программе загрузки, для чего выполняется команда перехода, которая поступает на регистр 3 микрокоманд либо из блока 1 постоян- ной памяти, либо из блока 2 оперативной памяти. При этом счетчик 5 адреса переходит в режим приема информации в соответствии с управляющим сигналом, поступающим из цепи, включающей дешифратор 6 и элемент И 13, на второй 5 записывается адрес первой микрокоманды программы загрузки через мультиплексор 7, сумматор

10и мультиплексор 9, а на триггер

11через мультиплексор 7 заносится признак работы с блоком 1 постоянной памяти.

Из блока 1 постоянной памяти на регистр 3 микрокоманд вызывается по адресу, загруженному в счетчик 5, микрокоманда, по которой загружается в счетчик 4 адрес первой микрокоманды, которую следует записать в блок 2 оперативной памяти. При этом на управляющий вход счетчика 4 адреса поступает единичный сигнал из цепи, включающей дешифратор 6, элемент И 15 и элемент ИЛИ 17, обеспечивающий прием адреса, сформированного сумматором 10 и мультиплексором 9, на регистр 4. Второй счетчик 5 переходит в режим счета соответствии с нулевым ут1равпяют1у1м сигналом, сформированным в цепи, включающей дешифратор 6 и элемент И 13.

дит так рой лич ств мог Сле 4 в кон ниц ног Сче (ад на

5 сиг мик по эле вхо

20 деш нак так

25

30

мик уст нал эле с т рой чик чик гис выз 35 мер

пер . гра мул либ с и при ной реж заг

40

первую команду загруженной . граммы. При этом на тригге мультиплексор 7 адреса зап либо из регистра 3 микроко с информационного входа 20 признак работы с блоком 2 ной памяти-, счетчик 4 пере режим приема информации, и загружается адрес первой м

В следующем цикле из блока 1 постоянной памяти на регистр 3 микроко- 5 ды, подлежащей выполнению, манд выбирается команда записи первой

микрокоманды в блок 2 оперативной памяти. При этом на информационный вход блока 2 поступает микрокоманда через мультиплексор 8 либо из основной памяти, либо из операционного устройства ЭВМ в зависимости от значения сигнала на втором выходе регистра 3 микрокоманд. На первый вход элемента И 15 с четвертого выхода регистра микрокоманд поступает нулевой сигнал, который через элемент И 15 и элемент ROM 17 поступает на управляющий вход первого счетчика 4 адреса и перево

дит его в режим счета, при этом по тактовому сигна:гу С4 (с входа 28 устройства) содержимое счетчика 4 увеличивается на +1 - получается действительный адрес первого загружаемого слова в оперативную память 2. Следовательно, при загрузке счетчика 4 в него должна засылаться адресная константа, имеющая значение, на единицу меньшее действительного начального адреса загружаемого массива. Счетчик 5 остается в режиме хранения (адрес не модифицируется), так как на его синхровход поступает нулевой

сигнал. Затем осуществляется запись микрокоманды в оперативную память 2 по сигналу, поступающему с выхода элемента ИЛИ 17 при совпадении на его входах единичных сигналов с выхода

дешифратора 6, пятого выхода (признак записи в память 2) регистра 3 и тактового входа 26 устройства.

5

0

В начале цикла записи последней микрокоманды в память 2 на. входе 23 устройства появляется единичный сигнал признака условия, который через элемент ИЛИ ,18 и И 16 при совпадении с тактовым сигналом с входа 28 устройства поступает на синхровход счетчика 5, по которому содержимое счетчика 5 увеличивается на +1 и на регистр 3 из блока 1 постоянной памяти вызывается следующая команда, напри- 35 мер, команда передачи управления на

первую команду загруженной микропро- . граммы. При этом на триггер 11 через мультиплексор 7 адреса записывается либо из регистра 3 микрокоманд, либо с информационного входа 20 устройства признак работы с блоком 2 оперативной памяти-, счетчик 4 переходит в режим приема информации, и в него загружается адрес первой микрокоман40

5 ды, подлежащей выполнению,

50

Во всех командах перехода адрес перехода формируется на сумматоре 10 и мультиплексоре 9 в зависимости от значения сигнала на управляющем входе мультиплексора 9 либо как абсолютный, поступающий из мультиплексора 7, либо как относительный,, причем приращение поступает по второму ин- 5 формационному входу сумматора 10 с выхода мультиплексора 7, а база - по первому информационному входу сумматора 10 с выходов счетчиков 4 и 5.

При раГ отс но микрокомандам, выбираемым из блока 2 оперативной памяти значения соответствующих разрядов счетчиков 4 и 5 совпадают,

Формула изобретения

Устройство микропрограммного управления, содержащее блок постоянной памяти, блок оперативной памяти, ре- гистр микрокоманд и дешифратор, причем выход блока постоянной памяти . подключен к первому информационному входу регистра микрокоманд, синхро- вход которого подключен к первому входу тактовых импульсов устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены два счетчика адреса, мультиплексоры относительного адреса кода микрокоманд и адреса перехода, сумматор, триггер, пять элементов И, два элемента ИЛИ, элемент И-НЕ, причем второй и третий входы тактовых импульсов устройства подключены со- ответственному к первому входу первого элемента И и синхровходу триггера выход которого подключен к первому входу второго элемента И и входу выбора входа регистра микрокоманд, вто-30 вход логического условия конца зарой информационный вход и выход которого подключены соответственно к выходу блока оперативной памя .и и выходу устройства, четвертый вход тактовых импульсов устройства подключен к первому входу третьего элемента И и счетному входу первого счетчика адреса, выход которого подключен к адресному входу блока оперативной памяти и входу старших разрядов сумматора, выход которого подключен к первому информационному входу мультиплексора адреса перехода, выход которого подключен к информационному входу первого счетчика адреса, вход признака режима которого подключен к выходу первого элемента ИЛИ, выход младших разрядов мультиплексора, адреса перехода подключен к информационному входу второго счетчика адреса выход которого подключен к первому входу младших разрядов сумматора и адресному входу блока постоянной памяти, вход адреса перехода устройства подключен к первому информациоиному входу мультиплексора относи- те.чьного адреса, выход младших разрядов которого подключен к второму информационному входу мультиплексора адреса перехода и второму входу сумматора, первый и второй входы загрузки микрокоманд устройства подключены соответственно к первому и второму информационным входам мультиплексора кода микрокоманд, выход которого подключен к информационному входу блока оперативной памяти, вход запи- си-счит ывания которого подключен к выходу первого элемента И, выход старшего разряда мультиплексора относительного адреса подключен к информационному входу триггера, выход элемента И-НЕ подключен к первому входу второго элемента ИЛИ, выход которого подключен к второму входу третьего элемента И, выход которого подключен к счетному входу второго счетчика адреса, вход режима которого, подключен к выходу четвертого элемента И и соединен с вторым входом второго элемента И, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И,

5

0

грузки устройства подключен к второму входу второго элемента {1ЛИ и первому входу четвертого элемента И, первый выход регистра микрокоманд подключен к входу дешифратора, первый выход которого подключен к второму входу четвертого элемента И, третий вход которого подключен к первому входу пятого элемента И и второму выходу регистра микрокоманд, второй выход дешифратора подключен к вторым входам первого и пятого элементов И и первому входу элемента И-НЕ, второй выход которого подключен к тре- тьему входу первого элемента И и

третьему выходу регистра микрокоманд, четвертый и пятый выходы которого подключены соответственно к управляющему входу мультиплексора адреса перехода и второму информационному входу мультиплексора относительного адреса, управляющий вход которого подключен к шестому выходу регистра микрокоманд и управляющему входу мультиплексора кода микрокоманд.

0

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1200289A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Многоканальное буферное запоминающее устройство | 1985 |

|

SU1280453A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных системах. Целью изобретения является повышение быстродействия. Устройство содержит блок 1 постоянной памяти, блок 2 оперативной памяти, регистр 3 микрокоманд два счетчика 4, 5 адреса, дешифратор 6, три мультиплексора 7-9, сумматор 10, триггер 11, пять элементов И 12-16, два элемента ИЛИ 17, 18-, элемент И-НЕ 19. Цель достигается за счет по- .вышения скорости записи требуемых микрокоманд в оперативную память. 3 ил. фиг. 2

Вход 1.

Sawct ttaKDOKOftoff- дн Iptiutrvs Mu/f- роквномд

Заерузка адреса Off S cuemvuff

I Pt&uemp J MeuiaipDamape

.Craex/noff

Селектор 9, ( су MHO mop 10

Э11-тып-15, 9и,№.}в ИМ, па-не

Сч(тчиШ1,5

I CvemwK I Селекторе

Памтъ

Эленент Г8 или, J jait

СчетткУ

нет

Q

I Л шита- r mops

Элементы J3,15fl

Абс.

Отн.

Селектор 9, сумпаторю

nofly fHus относи/пелмоео адреоа

перехвоа

Запись 6 счетчики

f,5 абреср пеоехово

Tpueeepff

Запись Scvemta/ff 5 адреса nepexi

CvfmwKu.S

-Ж.

fV«:«rv /

Чтение квманд UiOff

Л.

Пост.,

Tputttfiri

f

Чтение ( UJ ffff

J

П(т/ипл1,2

Редактор Л.Пчолинская

Заказ 387/53Тираж 673.Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ut.Sf

Составитель М.Силин Техред И.Попович

Корректор Е.Сирохман

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955059A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-28—Публикация

1985-06-20—Подача