СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

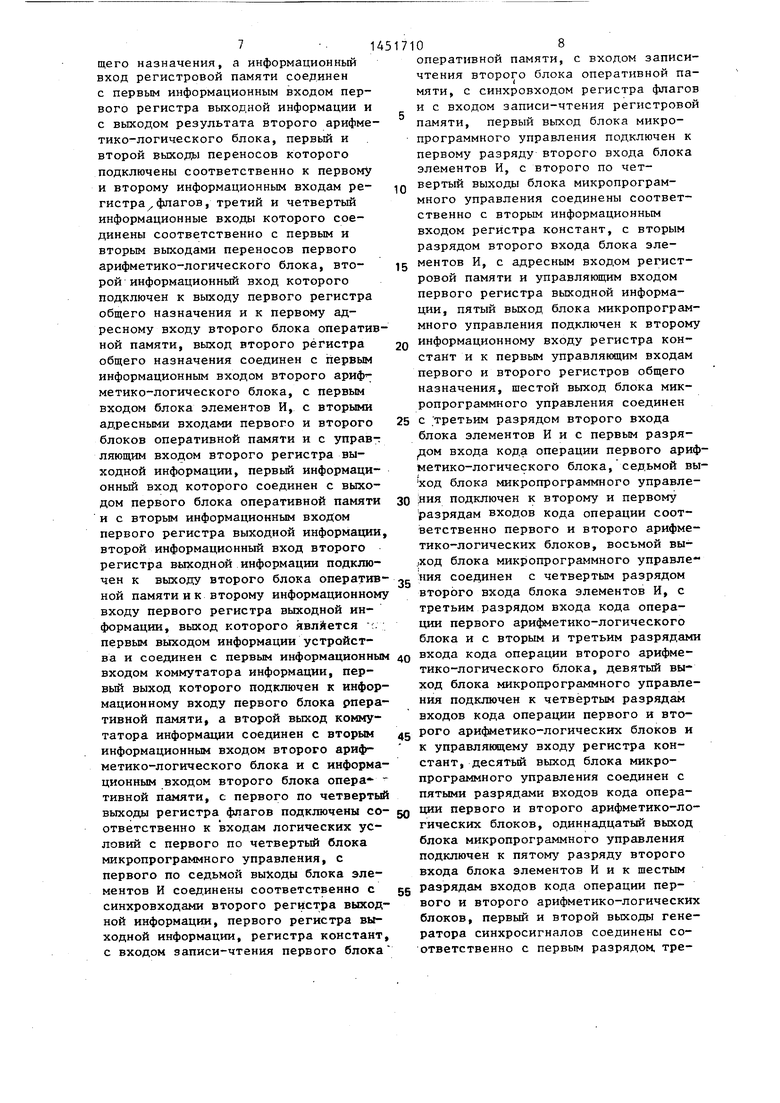

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных цифровых вычислительных машинах. Целью изобретения является повышение производительности. Поставленная цель достигается тем, что в устройство, содержащее блок 1 оперативной памяти, коммутатор 3 информации, регистры 4, 5 выходной информации, арифметико-логический блок 6, регистр 8 общего назначения, регистр 11 констант, блок 14 микропрограммного управления и генератор 15 синхросигналов, введены регистровая память 10, блок 2 оперативной памяти, арифметико-логический блок 7, регистр 9 общего назначения, регистр 12 ф,па- гоз и блок 13 элементов И, а также благодаря оригинальной организации связей между блоками. 6 ил. Q (Л

сриг.1

Изобретение относится к вычислительной технике и может быть использовано в универсальных и. специализированных цифровых вычислительных машинах.

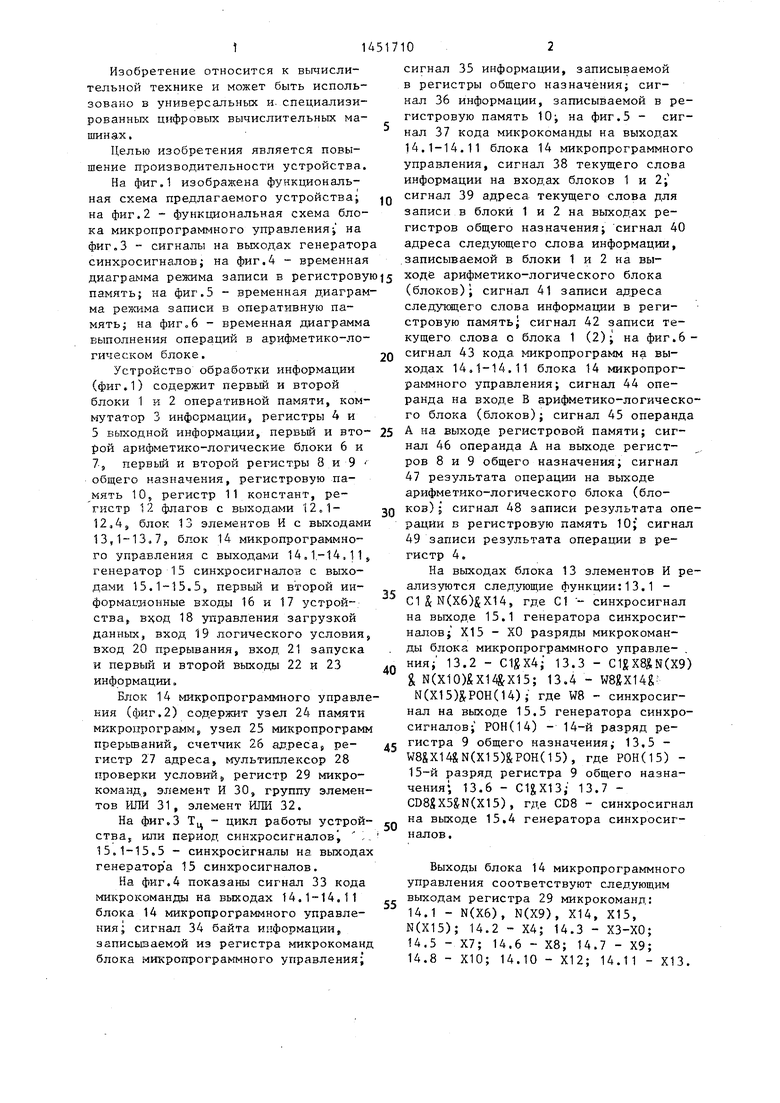

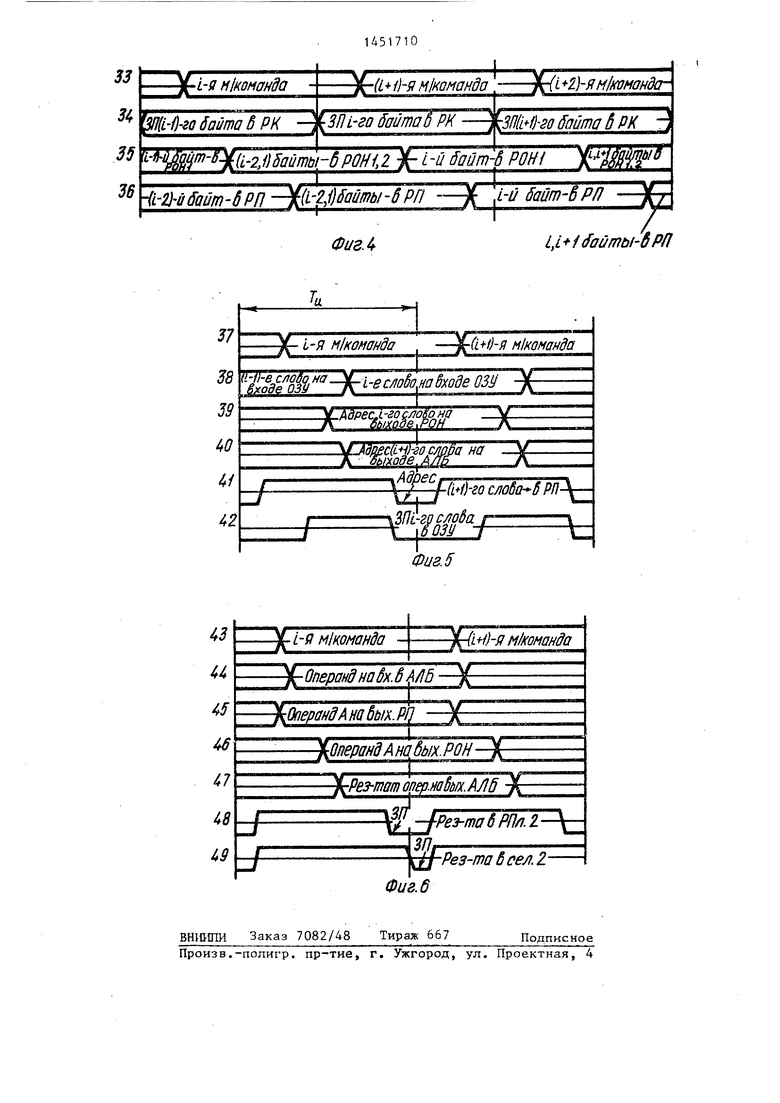

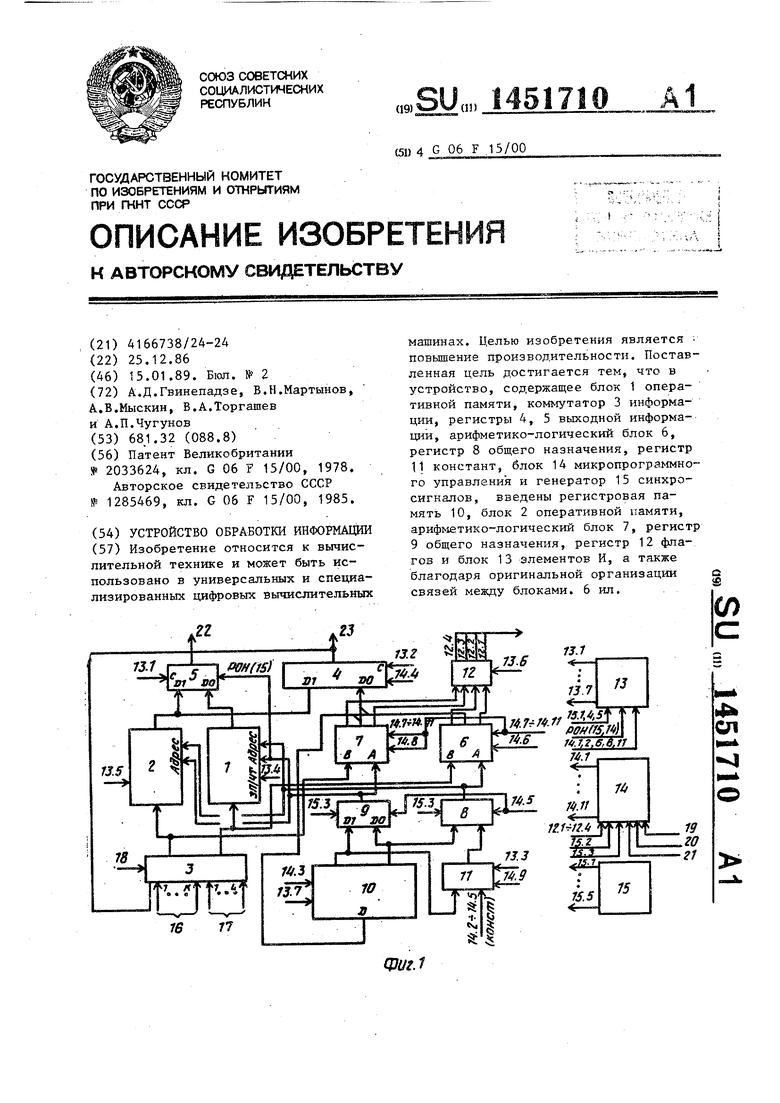

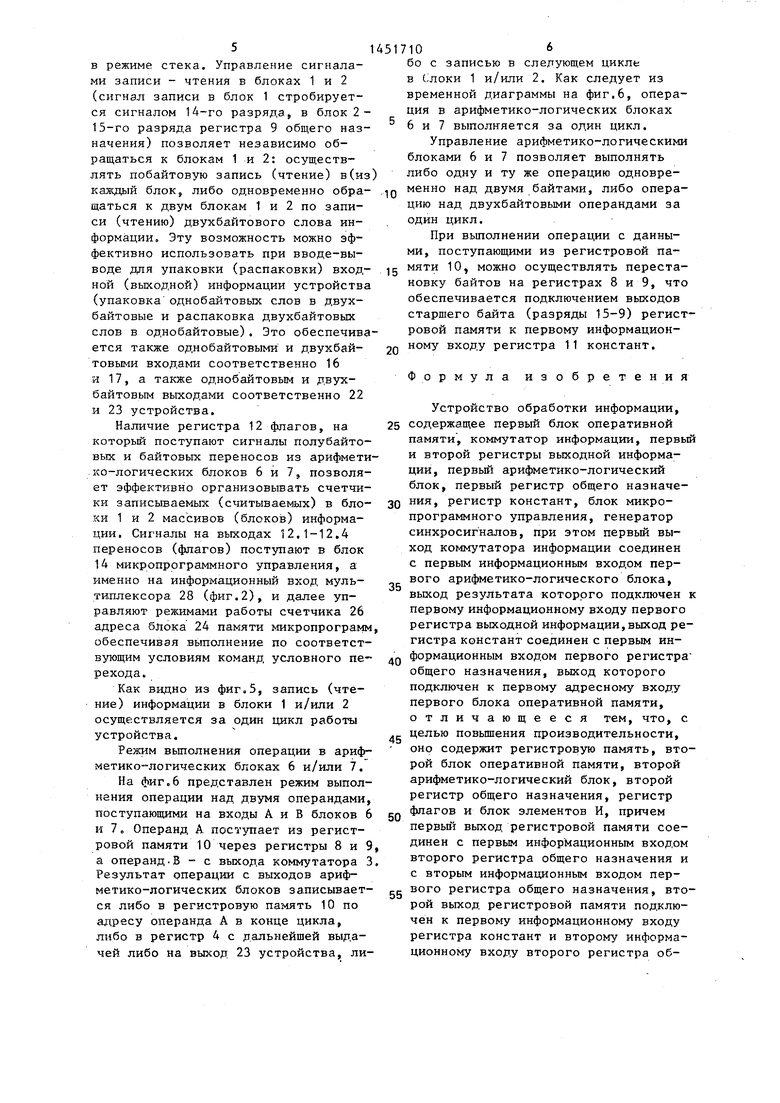

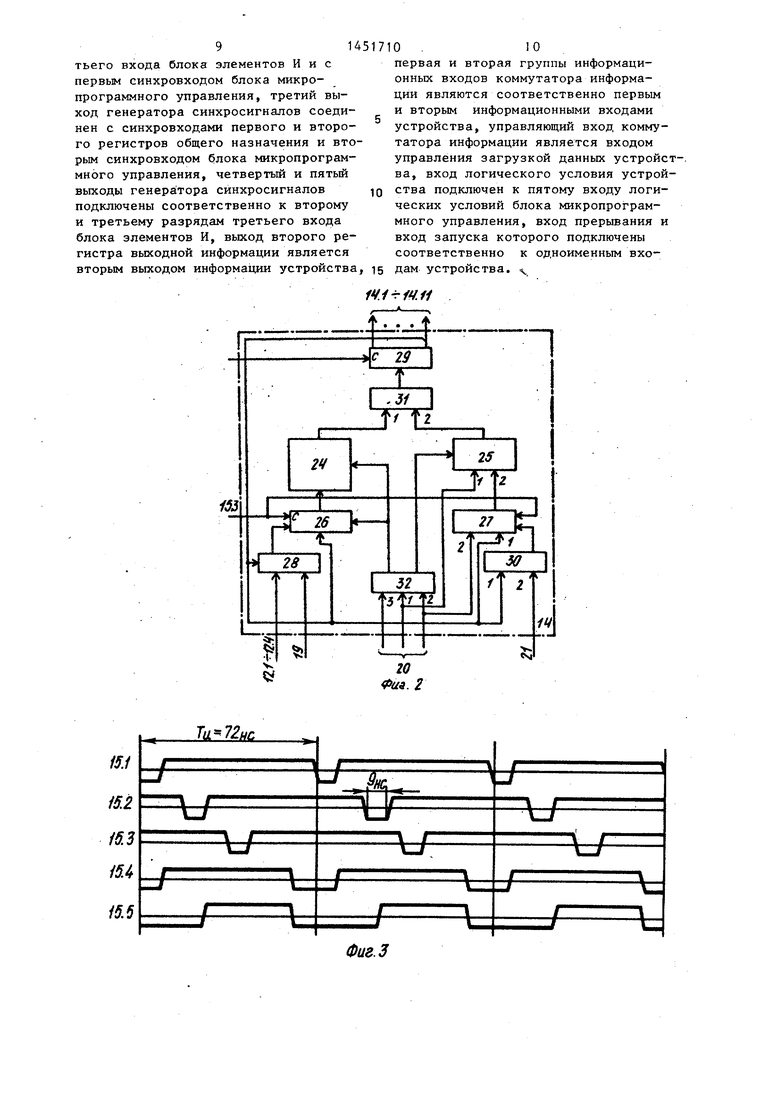

Целью изобретения является повышение производительности устройства. На фиг,1 изображена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока микропрограммного управления-, на фиг.З сигналы на выходах генератор синхросигналов; на фиг.4 - временная диаграмма режима записи в регистрову память; на фиг.З - временная диаграмма режима записи в оперативную память; на фиг„6 - временная диаграмма выполнения операций в арифметико-логическом блоке.

Устройство обработки информации (фиг.1) содержит первьй и второй блоки 1 и 2 оперативной памяти, коммутатор 3 информации, регистры 4 и 5 выходной информации, первьй и вто- рой арифметико-логические блоки 6 и 7-5 первьй и второй регистры 8 и 9 общего назначения, регистровую память 10, регистр 11 констант, регистр 12 флагов с выходами 12„1-

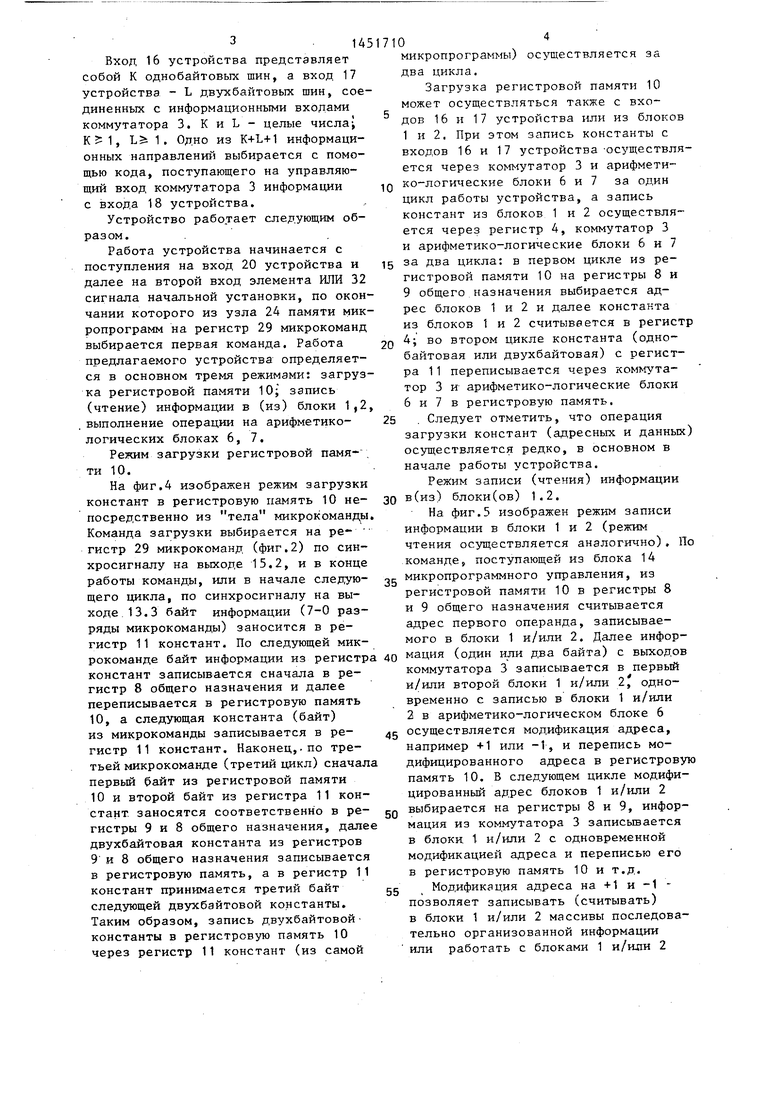

Блок 14 микропрограммного управления (фиг.2) содержит узел 24 памяти микропрограммS узел 23 микропрограмм прерьтаний, счетчик 26 адреса, ре- гистр 27 адреса, мультиплексор 28 проверки условий,, регистр 29 микрокоманд, элемент И 30, группу элементов ШШ 31, элемент ИЛИ 32.

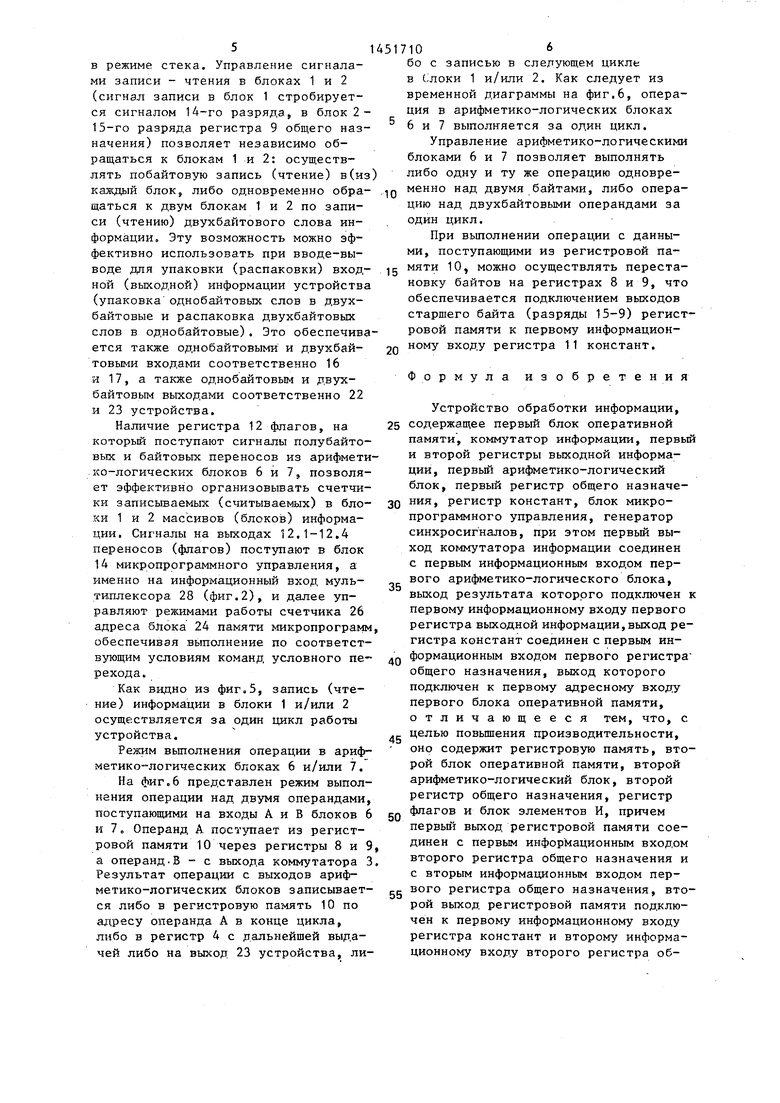

На фиг.Э Тц - цикл работы устрой- ства, или период, синхросигналов ,, 15.1-15,3 - синхросигналы на. выходах генератор а 13 синхросигналов.

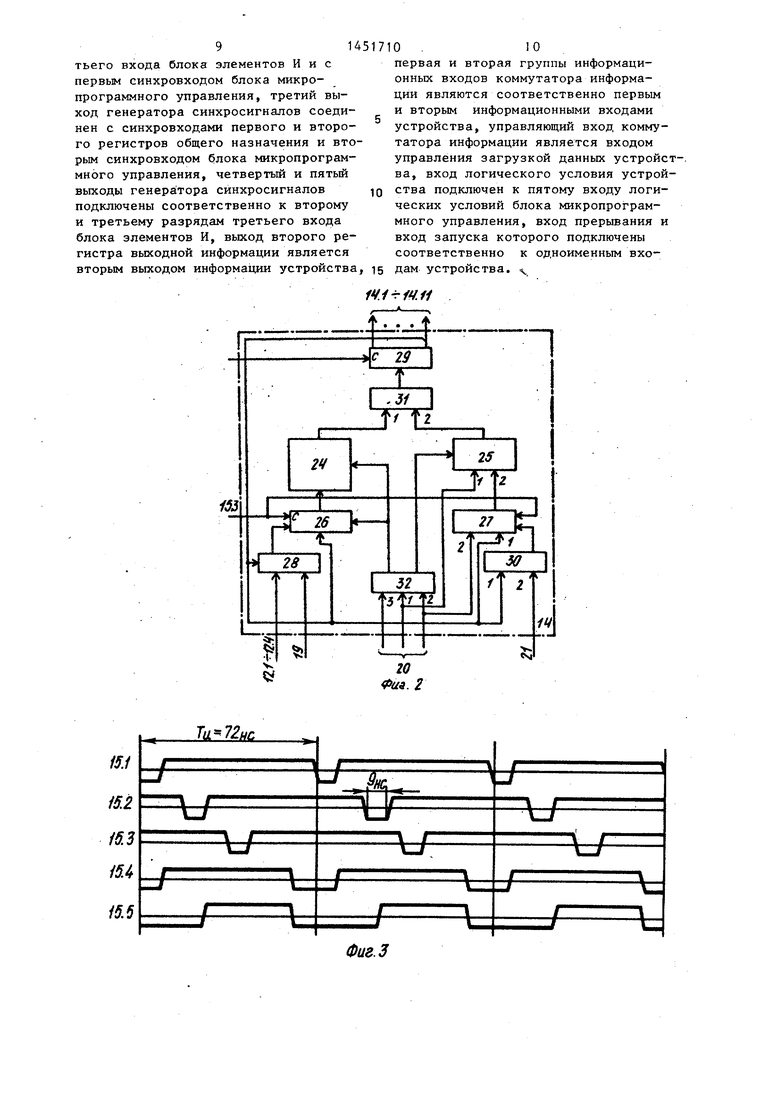

На фиг.4 показань сигнал 33 кода микрокоманды на выходах 14,1-14.11 блока 14 микропрограммного управления; сигнал 34 байта информации, записьшаемой из регистра микрокоманд блока микропрогра гиного управления;

Q 5 0

5 g

дп

45

гп

5

55

сигнал 35 информации, записываемой в регистры общего назначения; сигнал 36 информации, записываемой в регистровую память 10-, на фиг.5 - сигнал 37 кода микрокоманды на выходах 14.1-14.11 блока 14 микропрограммного управления, сигнал 38 текущего слова информации на входах блоков 1 и 2; сигнал 39 адреса текущего слова для записи в блоки 1 и 2 на выходах регистров общего назначения; сигнал 40 адреса следующего слова информации, записываемой в блоки 1 и 2 на выходе арифметико-логического блока (блоков); сигнал 41 записи адреса следутацего слова информации в регистровую память; сигнал 42 записи текущего слова о блока 1 (2); на фиг,6- сигнал 43 кода микропрограмм на выходах 14.1-14.11 блока 14 микропрограммного управления; сигнал 44 операнда на входе В арифметико-логического блока (блоков); сигнал 43 операнда А на выходе регистровой памяти; сигнал 46 операнда А на выходе регистров 8 и 9 общего назначения; сигнал 47 результата операции на выходе арифметико-логического блока (блоков) ; сигнал 48 записи результата операции в регистровую память 10; сигнал 49 записи результата операции в регистр 4,

На выходах блока 13 элементов И реализуются следующие функции:13,1 - С1 & N(X6)SX14, где С - синхросигнал на выходе 13,1 генератора синхросигналов; XI3 - ХО разряды микрокоманды блока микропрограммного управле- . ния; 13,2 - C1gX4; 13.3 - C1XX8XN(X9) N(X10)&Xl4&xi3; 13,4 - W8&Xl4g N(X13)JPOH(14); где W8 - синхросигнал на выходе 13.3 генератора синхросигналов; РОН(14) - 14-й разряд регистра 9 общего назначения; 13,5 - W8&X14&N(X13)&POH(13), где РОН(15) - 13-й разряд регистра 9 общего назначения , 13.6 - C1gX13; 13,7 - CD8gX5JN(X13), где CDS - синхросигнал на выходе 15,4 генератора синхросигналов.

Выходы блока 14 микропрограммного управления соответствуют следующим выходам регистра 29 микрокоманд: 14.1 - N(X6), N(X9), Х14, Х13, N(X15); 14.2 - Х4; 14.3 - ХЗ-ХО; 14,3 - Х7; 14,6 - Х8; 14,7 - Х9; 14.8 - Х10; 14.10 - Х12; 14.11 - Х13.

3,45

Вход 16 устройства представляет собой К однобайтовых щин, а вход 17 устройства - L двухбайтовых щин, соединенных с информационными входами коммутатора 3. К и L - целые числа-, , 1 . Одно из K+L+1 информационных направлений выбирается с помощью кода, поступающего на управляющий вход коммутатора 3 информации с входа 18 устройства.

Устройство работает следующим образом.

Работа устройства начинается с поступления на вход 20 устройства и далее на второй вход элемента ИЛИ 32 сигнала начальной установки, по окончании которого из узла 24 памяти микропрограмм на регистр 29 микрокоманд выбирается первая команда. Работа предлагаемого устройства определяется в основном тремя режимами: загрузка регистровой памяти 10; запись (чтение) информации в (из) блоки 1,2 выполнение операции на арифметико- логических блоках 6, 7,

Режим загрузки регистровой памя- , ти 10.

На фиг.4 изображен режим загрузки констант в регистровую память 10 непосредственно из тела микрокомандь Команда загрузки выбирается на ре- гистр 29 микрокоманд (фиг.2) по синхросигналу на выходе 15.2, и в конце работы команды, или в начале следующего цикла, по синхросигналу на выходе 13.3 байт информации (7-0 разряды микрокоманды) заносится в регистр 11 констант. По следующей микрокоманде байт информации из регистр констант записывается сначала в регистр 8 общего назначения и далее переписывается в регистровую память 10, а следующая константа (байт) из микрокоманды записывается в регистр 11 констант. Наконец,-по третьей микрокоманде (третий цикл) сначал первьш байт из регистровой памяти 10 и второй байт из регистра 11 констант заносятся соответственно в регистры 9 и 8 общего назначения, дале двухбайтовая константа из регистров 9 и 8 общего назначения записывается в регистровую память, а в регистр 11 констант принимается третий байт следующей двухбайтовой константы. Таким образом, запись двухбайтовой- константы в регистровую память 10 через регистр 11 констант (из самой

микропрограммы) осуществляется за

два цикла.

Загрузка регистровой памяти 10 может осуществляться также с вхоДОН 16 и 17 устройства или из блоков 1 и 2, При этом запись константы с входов 16 и 17 устройства -осуществляется через коммутатор 3 и арифметико-логические блоки 6 и 7 за один цикл работы устройства, а запись констант из блоков 1 и 2 осуществляется через регистр 4, коммутатор 3 и арифметико-логические блоки 6 и 7

за два цикла: в первом цикле из регистровой памяти 10 на регистры 8 и 9 общего назначения выбирается адрес блоков 1 и 2 и далее константа из блоков 1 и 2 считывается в регистр

4; во втором цикле константа (одно- байтовая или двухбайтовая) с регистра 11 переписывается через комк{ута- тор 3 и арифметико-логические блоки 6 и 7 в регистровую память,

Следует отметить, что операция загрузки констант (адресных и данных) осуществляется редко, в основном в начале работы устройства.

Режим записи (чтения) информации

в(из) блоки(ов) 1.2.

На фиг.5 изображен режим записи информации в блоки 1 и 2 (режим чтения осуществляется аналогично) По команде, поступающей из блока 14 микропрограммного управления, из регистровой памяти 10 в регистры 8 и 9 общего назначения считывается адрес первого операнда, записываемого в блоки 1 и/или 2. Далее информация (один или два байта) с выходов коммутатора 3 записывается в первый и/или второй блоки 1 и/или 2, одновременно с записью в блоки 1 и/или 2 в арифметико-логическом блоке 6

осуществляется модификация адреса, например +1 или -1, и перепись модифицированного адреса в регистровую память 10. В следующем цикле модифицированный адрес блоков 1 и/или 2

выбирается на регистры 8 и 9, информация из коммутатора 3 записьшается в блоки 1 и/или 2 с одновременной модификацией адреса и переписью его в регистровую память 10 и т.д.

Модификация адреса на +1 и -1 - позволяет записывать (считывать) в блоки 1 и/или 2 массивы последовательно организованной информации или работать с блоками 1 и/или 2

в режиме стека. Управление сигналами записи - чтения в блоках 1 и 2 (сигнал записи в блок 1 стробирует- ся сигналом 14-го разряда, в блок 2- 15-го разряда регистра 9 общего назначения) позволяет независимо обращаться к блокам 1 и 2: осуществлять побайтовую запись (чтение) в(из каждый блок, либо одновременно обращаться к двум блокам 1 и 2 по записи (чтению) двухбайтового слова информации. Эту возможность можно эффективно использовать при вводе-выводе для упаковки (распаковки) входной (выходной) информации устройства (упаковка однобайтовых слов в двухбайтовые и распаковка двухбайтовых слов в однобайтовые), Это обеспечивается также однобайтовыми и двухбайтовыми входами соответственно 16 и 17, а также однобайтовым и двухбайтовым выходами соответственно 22 и 23 устройства.

Наличие регистра 12 флагов, на которьй поступают сигналы полубайтовых и байтовых переносов из арифметико-логических блоков 6 и 7, позволяет эффективно организовывать счетчики записываемых (считываемых) в блоки 1 и 2 массивов (блоков) информации. Сигналы на выходах 12.1-12.4 переносов (флагов) поступают в блок 14 микропрограммного управления, а именно на информационный вход мультиплексора 28 (фиг.2), и далее управляют режимами работы счетчика 26 адреса блока 24 памяти MHKponporpaNiM обеспечивая вьгаолнение по соответствующим условиям команд условного перехода.

Как видно из фиг,5, запись (чтение) информации в блоки 1 и/или 2 осуществляется за один цикл работы устройства.

Режим вьшолнения операции в арифметико-логических блоках 6 и/или 7.

На фиг.6 представлен режим выполнения операции над двумя операндами, поступающими на входы А и В блоков 6 и 7. Операнд А поступает из регистровой памяти 10 через регистры 8 и 9 а операнд.В - с выхода коммутатора 3 Результат операции с выходов арифметико-логических блоков записывается либо в регистровую память 10 по адресу операнда А в конце цикла, либо в регистр 4 с дальнейшей выдачей либо на выход 23 устройства, либо с записью в следующем цикле в Слоки 1 и/или 2. Как следует из временной диаграммы на фиг,6, операция в арифметико-логических блоках 6 и 7 выполняется за один цикл.

Управление арифметико-логическими блоками 6 и 7 позволяет выполнять либо одну и ту же операцию одновременно над двумя байтами, либо операцию над двухбайтовыми операндами за один цикл.

При выполнении операции с данными, поступающими из регистровой паg мяти 10, можно осуществлять перестановку байтов на регистрах 8 и 9, что обеспечивается подключением выходов старшего байта (разряды 15-9) регистровой памяти к первому информационQ ному входу регистра 11 констант.

Формула изобретения

Устройство обработки информации,

5 содержащее первый блок оперативной памяти, коммутатор информации, первый и второй регистры выходной информации, первьй арифметико-логический блок, первый регистр общего назначе0 ния, регистр констант, блок микропрограммного управления, генератор синхросигналов, при этом первый выход коммутатора информации соединен с первым информационным входом первого арифметико-логического блока, выход результата которого подключен к первому информационному входу первого регистра выходной информации,выход регистра констант соединен с первым инQ формационным входом первого регистра общего назначения, выход которого подключен к первому адресному входу первого блока оперативной памяти, отличающееся тем, что, с .g целью повьшения производительности, оно содержит регистровую память, второй блок оперативной памяти, второй арифметико-логический блок, второй регистр общего назначения, регистр

-j флагов и блок элементов И, причем первьш выход регистровой памяти соединен с первым информационным входом второго регистра общего назначения и с вторым информационным входом пер вого регистра общего назначения, второй выход регистровой памяти подключен к первому информационному входу регистра констант и второму информационному входу второго регистра об5

щего назначения, а информационный вход регистровой памяти соединен с первым информационным входом первого регистра выходной информации и с выходом результата второго арифметико-логического блока, первьй и второй выходы переносов которого подключены соответственно к первому и второму информационным входам регистра флагов, третий и четвертый информационные входы которого соединены соответственно с первым и вторым выходами переносов первого арифметико-логического блока, второй информационный вход которого подключен к выходу первого регистра общего назначения и к первому адресному входу второго блока оперативной памяти, выход второго регистра общего назначения соединен с первым информационным входом второго ариф - метико-логического блока, с первым входом блока элементов И, с вторыми адресными входами первого и второго блоков оперативной памяти и с управ-: ляющим входом второго регистра выходной информации, первьй информационный вход которого соединен с выходом первого блока оперативной памяти и с вторым информационным входом первого регистра выходной информации, второй информационный вход второго регистра выходной информации подключен к выходу второго блока оперативной памяти и к второму информационному входу первого регистра выходной информации, выход которого явлйется ;. первым выходом информации устройстоперативной

памяти, с входом записи10

15

20

25

30

35

чтения второго блока оперативной памяти, с синхровходом регистра флагов и с входом записи-чтения регистровой памяти, первый выход блока микропрограммного управления подключен к первому разряду второго входа блока элементов И, с второго по четвертый выходы блока микропрограммного управления соединены соответственно с вторым информационным входом регистра констант, с вторым разрядом второго входа блока элементов И, с адресным входом регистровой памяти и управляющим входом первого регистра выходной информации, пятый выход блока микропрограммного управления подключен к второму информационному входу регистра констант и к первым управляющим входам первого и второго регистров общего назначения, шестой выход блока микропрограммного управления соединен с третьим разрядом второго входа блока элементов И и с первым разрядом входа кода операции первого ариф метико-логического блока, седьмой вы ход блока микропрограммного управления подключен к второму и первому разрядам входов кода операции соответственно первого и второго арифметико-логических блоков, восьмой вы- .,ход блока микропрограммного управления соединен с четвертым разрядом второго входа блока элементов И, с третьим разрядом входа кода операции первого арифметико-логического блока и с вторым и третьим разрядами

ва и соединен с первым информационным до входа кода операции второго арифме- входом коммутатора информации, пер- тико-логического блока, девятый выход блока микропрограммного управления подключен к четвертым разрядам входов кода операции первого и второго ари(|метико-логических блоков и к управляющему входу регистра констант, десятый выход блока микропрограммного управления соединен с пятыми разрядами входов кода операции первого и второго арифметико-логических блоков, одиннадцатый выход блока микропрограммного управления подключен к пятому разряду второго входа блока элементов И и к щестым разрядам входов кода операции первого и второго арифметико-логических блоков, первый и второй выходы генератора синхросигналов соединены соответственно с первым разрядок тревый выход которого подключен к информационному входу первого блока рпера- тивной памяти, а второй выход коммутатора информации соединен с вторым информационным входом второго арифметико-логического блока и с информационным входом второго блока опера- тивной памяти, с первого по четвертый выходы регистра флагов подключены со- ответственно к входам логических условий с первого по четвертый блока микропрограммного управления, с первого по седьмой выходы блока элементов И соединены соответственно с синхровходами второго регистра выходной информации, первого регистра выходной информации, регистра констант, с входом записи-чтения первого блока

710

оперативной

памяти, с входом записи

5

0

5

0

5

чтения второго блока оперативной памяти, с синхровходом регистра флагов и с входом записи-чтения регистровой памяти, первый выход блока микропрограммного управления подключен к первому разряду второго входа блока элементов И, с второго по четвертый выходы блока микропрограммного управления соединены соответственно с вторым информационным входом регистра констант, с вторым разрядом второго входа блока элементов И, с адресным входом регистровой памяти и управляющим входом первого регистра выходной информации, пятый выход блока микропрограммного управления подключен к второму информационному входу регистра констант и к первым управляющим входам первого и второго регистров общего назначения, шестой выход блока микропрограммного управления соединен с третьим разрядом второго входа блока элементов И и с первым разрядом входа кода операции первого арифметико-логического блока, седьмой вы- ход блока микропрограммного управления подключен к второму и первому разрядам входов кода операции соответственно первого и второго арифметико-логических блоков, восьмой вы- .,ход блока микропрограммного управления соединен с четвертым разрядом второго входа блока элементов И, с третьим разрядом входа кода операции первого арифметико-логического блока и с вторым и третьим разрядами

входа кода операции второго арифме- тико-логического блока, девятый выход блока микропрограммного управления подключен к четвертым разрядам входов кода операции первого и второго ари(|метико-логических блоков и к управляющему входу регистра констант, десятый выход блока микропрограммного управления соединен с пятыми разрядами входов кода операции первого и второго арифметико-логических блоков, одиннадцатый выход блока микропрограммного управления подключен к пятому разряду второго входа блока элементов И и к щестым разрядам входов кода операции первого и второго арифметико-логических блоков, первый и второй выходы генератора синхросигналов соединены соответственно с первым разрядок тре9145

тьего входа блока элементов И и с первым синхровходом блока микропрограммного управления, третий выход генератора синхросигналов соединен с синхровходами первого и второго регистров общего назначения и вторым синхровходом блока микропрограммного управления, четвертый и пятый выходы генера тора синхросигналов подключены соответственно к второму и третьему разрядам третьего входа блока элементов И, выход второго регистра выходной информации является вторым выходом информации устройства,

Фиг.З

0 .10

первая и вторая группы информационных входов коммутатора информации являются соответственно первым и вторым информационными входами устройства, управляющий вход коммутатора информации является входом управления загрузкой данных устройства, вход логического условия устройства подключен к пятому входу логических условий блока микропрограммного управления, вход прерывания и вход запуска которого подключены соответственно к одноименным входам устройства. V

..ii

J4 35 36

Фиг4

j(Tg Af//fg//g// g

м(к

Операнд на 5х. -

-j aHdMQ ibiK.Pfl --jf

ОйерандА нобш.РОН Нг

Рез-тат ошнаёш АЩ

Рез-таёРП/i.

Рез-тадсел

ВНШШИ Заказ 7082/48 Тираж 667

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Ц- 1 аиты-бРЛ

м(команда

Рез-таёРП/i.ZРез-тадсел.Фив. 6

Подписное

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАГНИТНОГО ПОЛЯ | 1990 |

|

RU2033624C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1285469A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1986-12-25—Подача