1

Изобретение относится к вычислительной технике и может быть использовано для построения надежных вычислительных систем на базе микропроцессорных наборов.

Цель изобретения - повышение быстродействия, в частности, операции контроля дублированной вычислительной системы и расширение области применения за счет асинхронных вычислительных систем, работающих в асинхронном режиме обмена по магистрали и тактируемых либо от независимых источников тактовых импульсов, либо вообще не имеющих внешних тактовых генераторов.

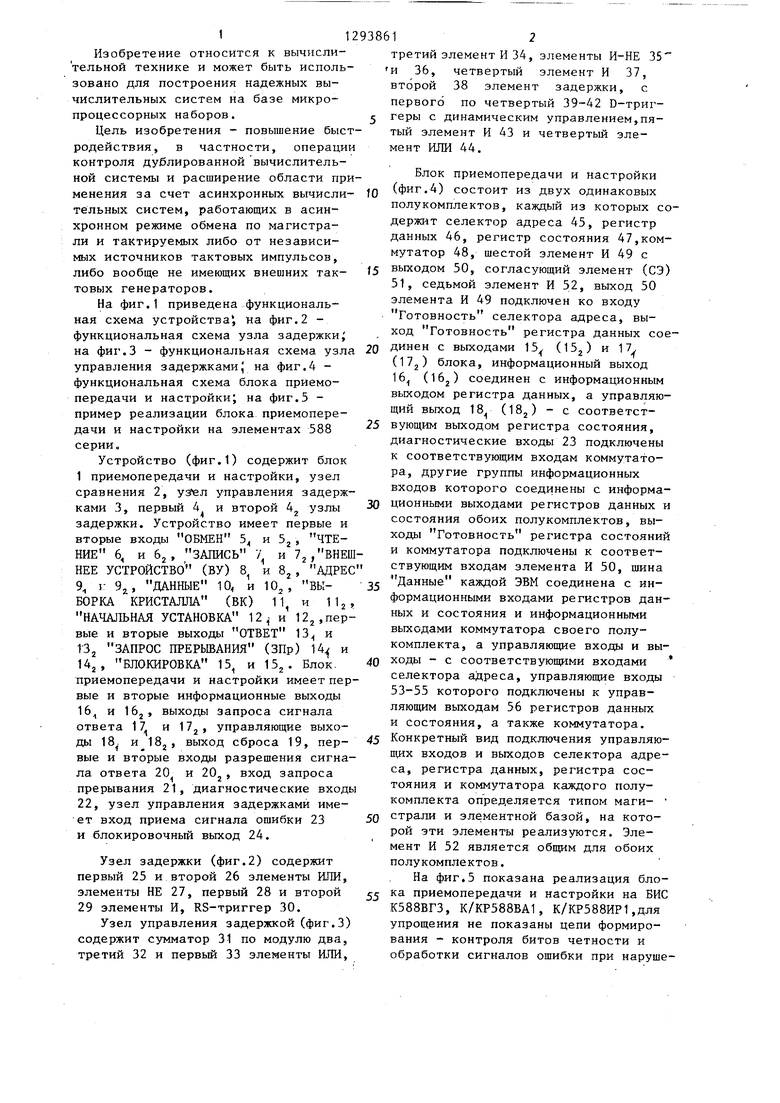

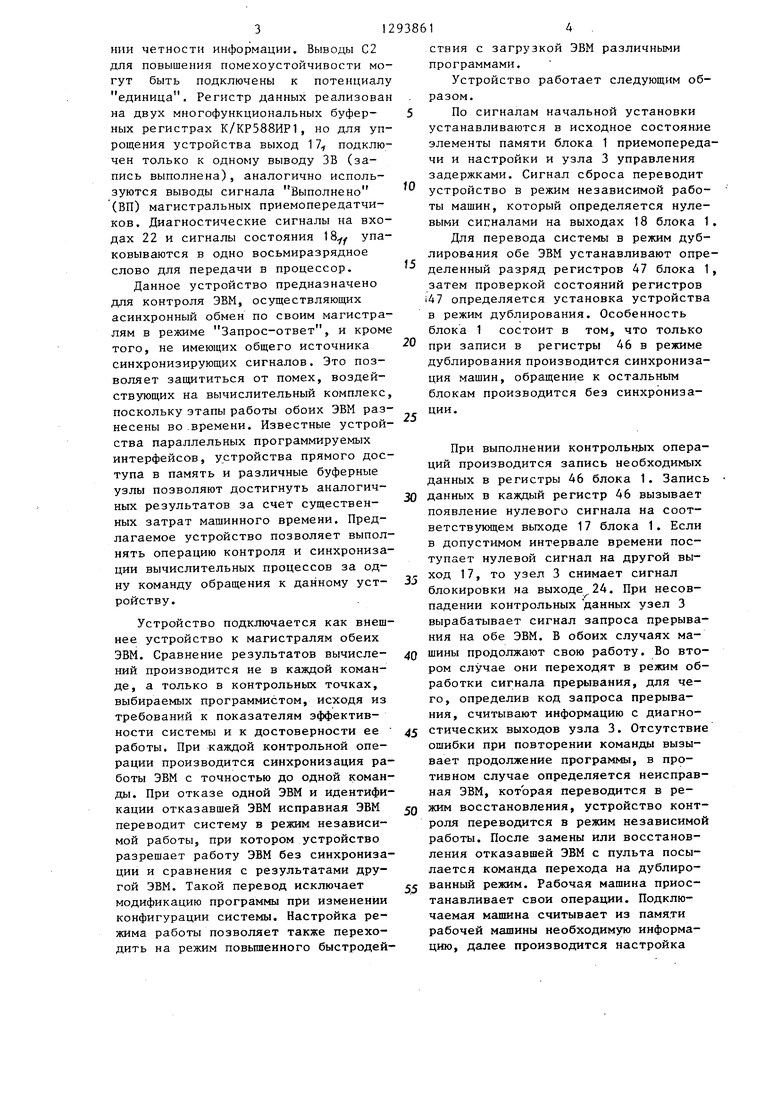

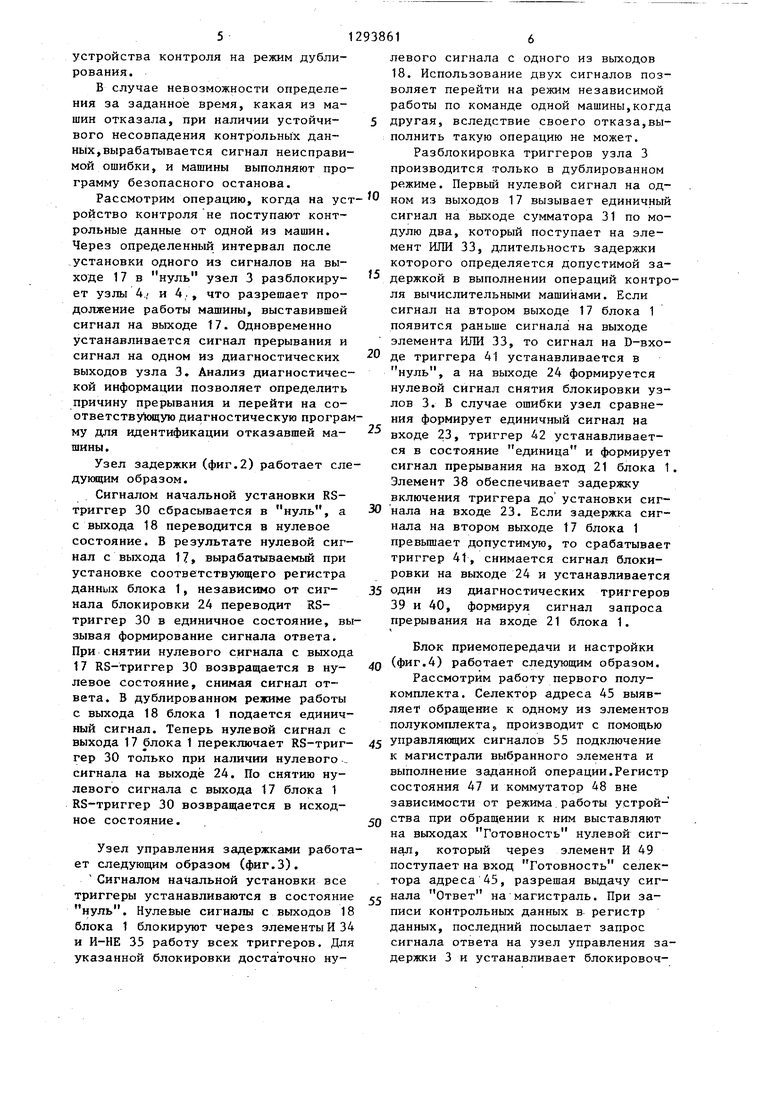

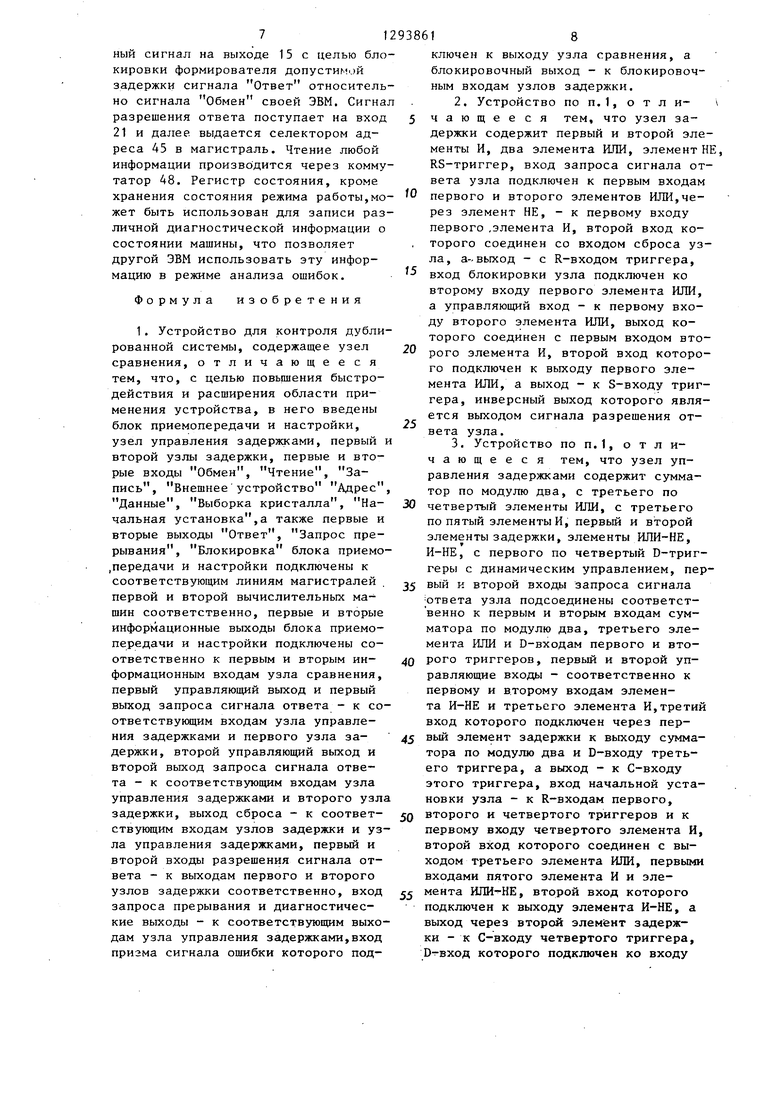

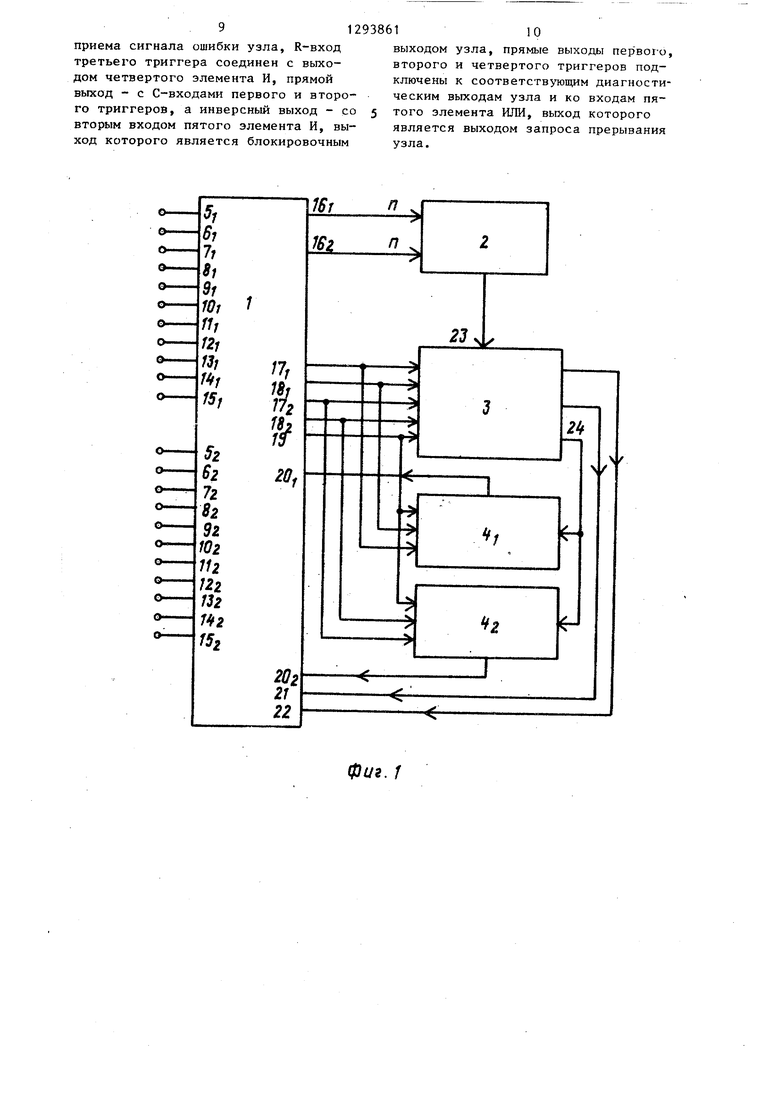

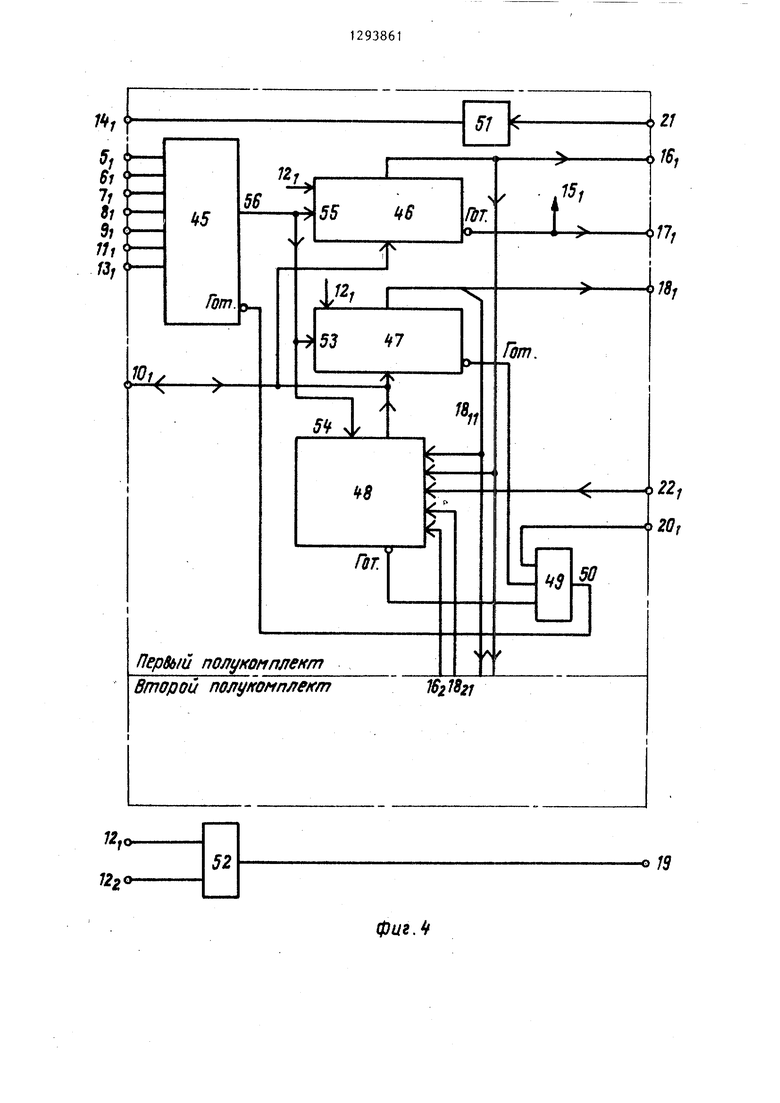

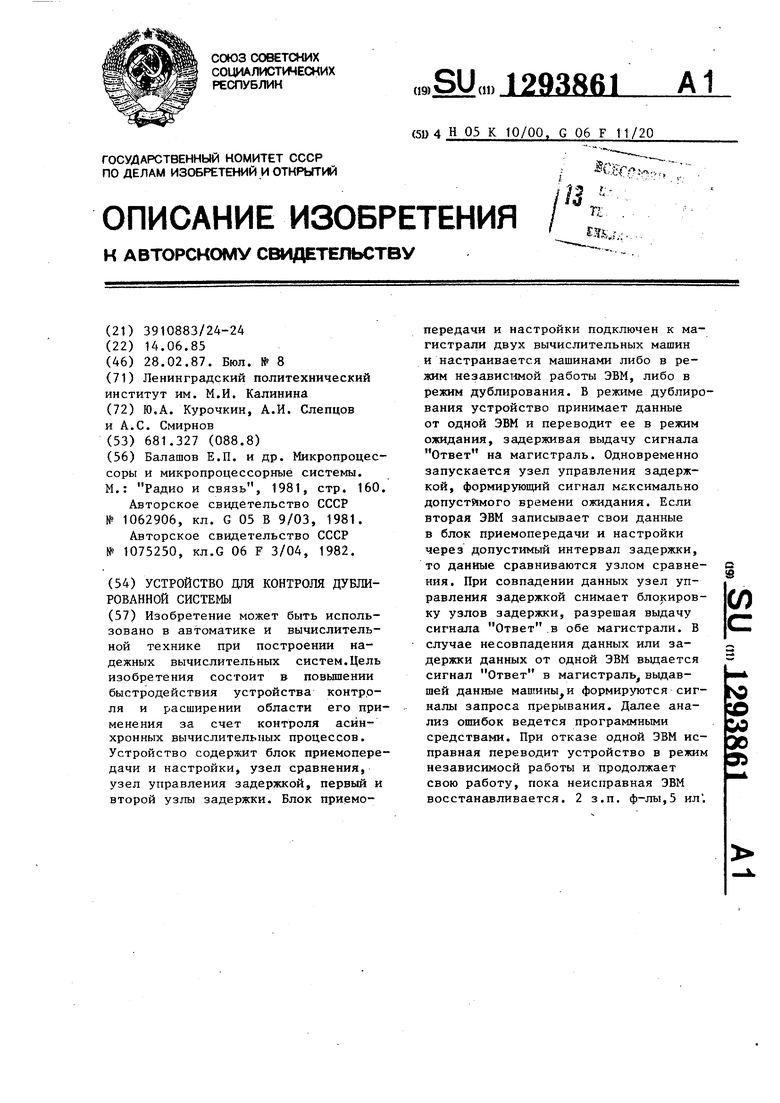

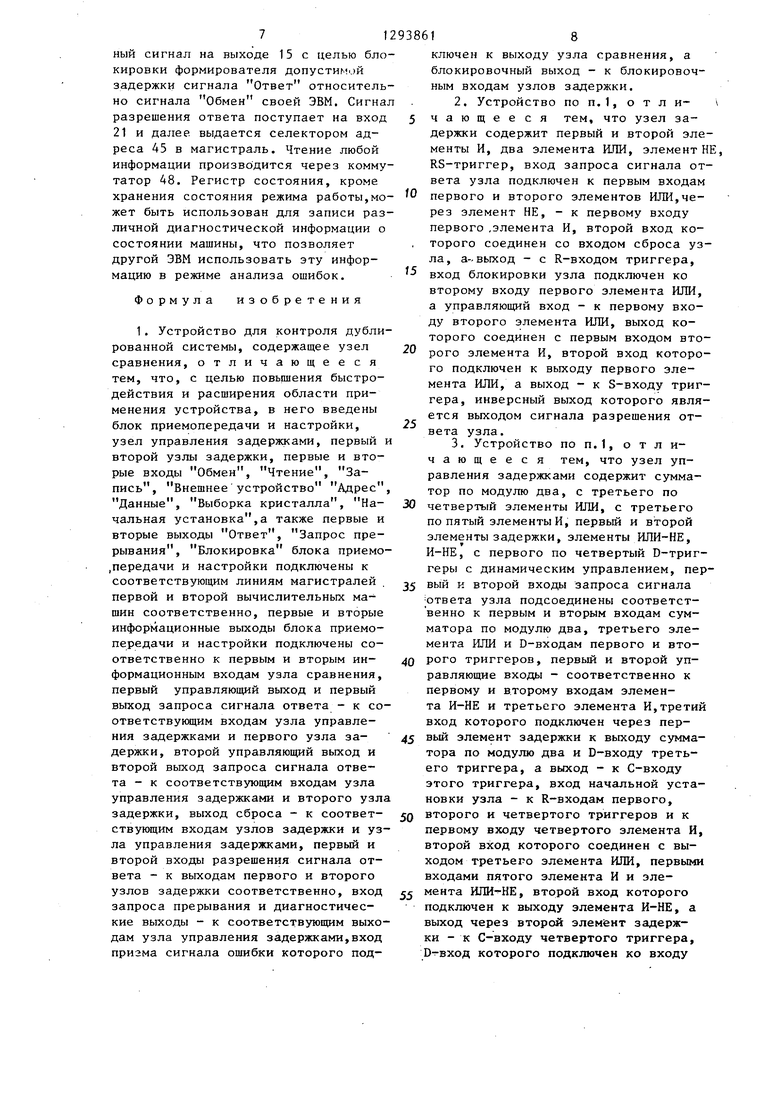

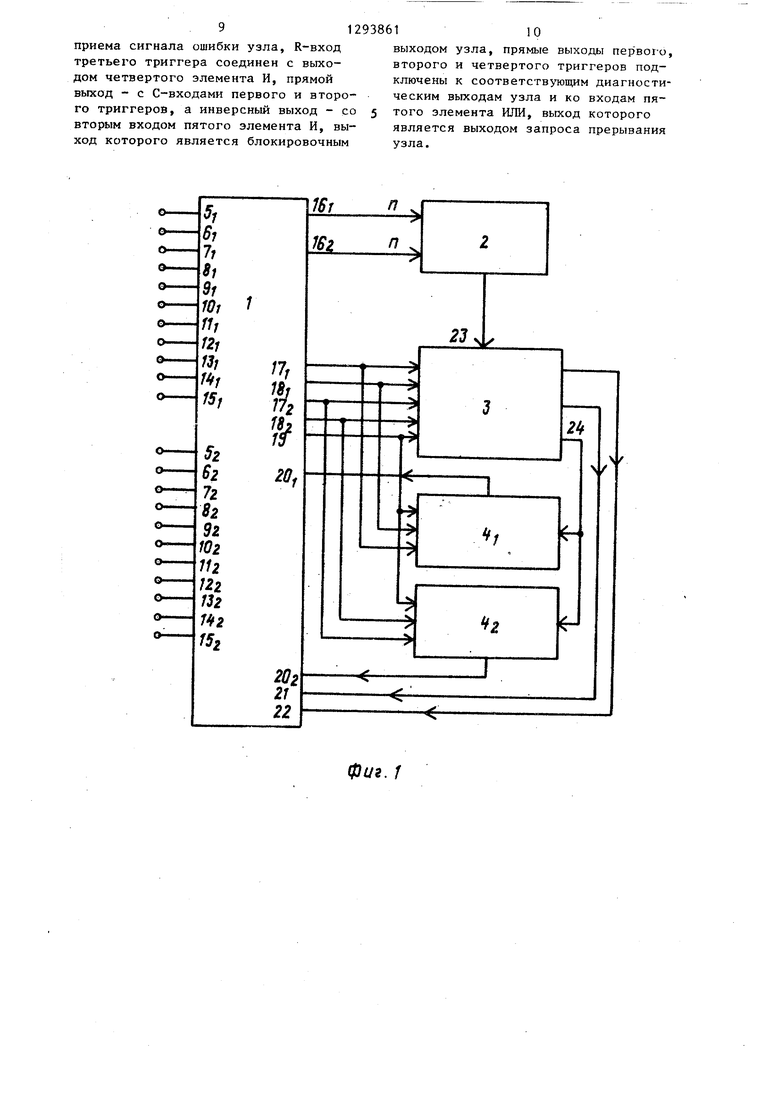

На фиг.1 приведена функциональная схема устройства , на фиг. 2 - функциональная схема узла задержки на фиг.З - функциональная схема узла управления задержками} на фиг.4 - функциональная схема блока приемо- передачи и настройки; на фиг.5 - пример реализации блока приемопере- дачи и настройки на элементах 588 серии.

Устройство (фиг.1) содержит блок 1 приемопередачи и настройки, узел сравнения 2, управления задержками 3, первый 4 и второй 4 узлы задержки. Устройство имеет первые и вторые входы ОБМЕН 5 и 5j, ЧТЕНИЕ 6, и 6, ЗАПИСЬ / и 72,ВНЕШНЕЕ УСТРОЙСТВО (ВУ) 8, и 8 , АДРЕС 9, 1- 9,,, ДАННЫЕ 10, и 10,,, ВЫБОРКА КРИСТАЛЛА (ВК) 11, и 11j, НАЧАЛЬНАЯ УСТАНОВКА 12 и 12,,,первые и вторые выходы ОТВЕТ 13 и rSj ЗАПРОС ПРЕРЫВАНИЯ (ЗПр) и 14j, БЛОКИРОВКА 15 и IS. Влок. приемопередачи и настройки имеет первые и вторые информационные выходы 16 и 16j, выходы запроса сигнала ответа 17, и 17 , управляющие выходы 18 и 18j, выход сброса 19, первые и вторые входы разрешения сигнала ответа 20 и 20, вход запроса прерывания 21, диагностические входы 22, узел управления задержками имеет вход приема сигнала ошибки 23 и блокировочный выход 24.

Узел задержки (фиг.2) содержит первый 25 и второй 26 элементы ИЛИ, элементы НЕ 27, первый 28 и второй 29 элементы И, RS-триггер 30.

Узел управления задержкой (фиг.З) содержит сумматор 31 по модулю два, третий 32 и первый 33 элементы ИЛИ,

12938612

третий элемент И 34, элементы И-НЕ 35 и 36, четвертый элемент И 37, второй 38 элемент задержки, с первого по четвертый 39-42 D-триг- геры с динамическим управлением,пятый элемент И 43 и четвертый элемент ИЛИ 44.

fO

f5

20

30

35

40

Блок приемопередачи и настройки (фиг.4) состоит из двух одинаковых полукомплектов, каждый из которых со держит селектор адреса 45, регистр данных 46, регистр состояния 47,коммутатор 48, шестой элемент И 49 с выходом 50, согласующий элемент (СЭ) 51, седьмой элемент И 52, выход 50 элемента И 49 подключен ко входу Готовность селектора адреса, выход Готовность регистра данных сое динен с выходами 15 (IS) и 17 (17) блока, информационный выход 16 (16j) соединен с информационным выходом регистра данных, а управляющий выход 18 (18) - с соответст25 вующим выходом регистра состояния, диагностические входы 23 подключены к соответствующим входам коммутатора, другие группы информационных входов которого соединены с информационными выходами регистров данных и состояния обоих полукомплектов, выходы Готовность регистра состояний и коммутатора подключены к соответствующим входам элемента И 50, шина Данные каждой ЭВМ соединена с информационными входами регистров данных и состояния и информационными выходами коммутатора своего полукомплекта, а управляющие входы и выходы - с соответствующими входами селектора адреса, управляющие входы 53-55 которого подключены к управляющим выходам 56 регистров данных и состояния, а также коммутатора.

45 Конкретный вид подключения управляю- пщх входов и выходов селектора адреса, регистра данных, регистра состояния и коммутатора каждого полукомплекта определяется типом маги-

50 страли и элементной базой, на которой эти элементы реализуются. Элемент И 52 является общим для обоих полукомплектов.

На фиг.5 показана реализация бло55 ка приемопередачи и настройки на БИС К588ВГЗ, К/КР588ВА1, К/КР588ИР1,для упрощения не показаны цепи формирования - контроля битов четности и обработки сигналов ошибки при наруше

Блок приемопередачи и настройки (фиг.4) состоит из двух одинаковых полукомплектов, каждый из которых содержит селектор адреса 45, регистр данных 46, регистр состояния 47,коммутатор 48, шестой элемент И 49 с выходом 50, согласующий элемент (СЭ) 51, седьмой элемент И 52, выход 50 элемента И 49 подключен ко входу Готовность селектора адреса, выход Готовность регистра данных соединен с выходами 15 (IS) и 17 (17) блока, информационный выход 16 (16j) соединен с информационным выходом регистра данных, а управляющий выход 18 (18) - с соответствующим выходом регистра состояния, диагностические входы 23 подключены к соответствующим входам коммутатора, другие группы информационных входов которого соединены с информационными выходами регистров данных и состояния обоих полукомплектов, выходы Готовность регистра состояний и коммутатора подключены к соответствующим входам элемента И 50, шина Данные каждой ЭВМ соединена с информационными входами регистров данных и состояния и информационными выходами коммутатора своего полукомплекта, а управляющие входы и выходы - с соответствующими входами селектора адреса, управляющие входы 53-55 которого подключены к управляющим выходам 56 регистров данных и состояния, а также коммутатора.

Конкретный вид подключения управляю- пщх входов и выходов селектора адреса, регистра данных, регистра состояния и коммутатора каждого полукомплекта определяется типом маги-

страли и элементной базой, на которой эти элементы реализуются. Элемент И 52 является общим для обоих полукомплектов.

На фиг.5 показана реализация блока приемопередачи и настройки на БИС К588ВГЗ, К/КР588ВА1, К/КР588ИР1,для упрощения не показаны цепи формирования - контроля битов четности и обработки сигналов ошибки при нарушеНИИ четности информации. Выводы С2 для повышения помехоустойчивости могут быть подключены к потенциалу единица. Регистр данных реализован на двух многофункциональных буферных регистрах К/КР588ИР1, но для упрощения устройства выход 17 подключен только к одному выводу ЗВ (запись выполнена), аналогично используются выводы сигнала Выполнено (ВП) магистральных приемопередатчиков. Диагностические сигналы на входах 22 и сигналы состояния 18 упаковываются в одно восьмиразрядное слово для передачи в процессор.

Данное устройство предназначено для контроля ЭВМ, осуществляющих асинхронный обмен по своим магистралям в режиме Запрос-ответ, и кроме того, не имеющих общего источника синхронизирующих сигналов. Это позволяет защититься от помех, воздействующих на вычислительный комплекс, поскольку этапы работы обоих ЭВМ разнесены во .времени. Известные устройства параллельных программируемых интерфейсов, устройства прямого доступа в память и различные буферные узлы позволяют достигнуть аналогичных результатов за счет существенных затрат машинного времени. Предлагаемое устройство позволяет выполнять операцию контроля и синхронизации вычислительных процессов за одну команду обращения к данному устройству.

Устройство подключается как внешнее устройство к магистралям обеих ЭВМ. Сравнение результатов вычислений производится не в каждой команде, а только в контрольных точках, выбираемых программистом, исходя из требований к показателям эффективности системы и к достоверности ее работы. При каждой контрольной операции производится синхронизация работы ЭВМ с точностью до одной команды. При отказе одной ЭВМ и идентификации отказавшей ЭВМ исправная ЭВМ переводит систему в режим независимой работы, при котором устройство разрешает работу ЭВМ без синхронизации и сравнения с результатами другой ЭВМ. Такой перевод исключает модификацию программы при изменении конфигурации системы. Настройка режима работы позволяет также переходить на режим повьш1енного быстродей2938614 .

ствия с загрузкой ЭВМ различными

o

5

0

5

0

5

0

5

0

программами.

Устройство работает следующим образом.

По сигналам начальной установки устанавливаются в исходное состояние элементы памяти блока 1 приемопереда- чи и настройки и узла 3 управления задержками. Сигнал сброса переводит устройство в режим независимой работы машин, который определяется нулевыми сигналами на выходах 18 блока 1.

Для перевода системы в режим дублирования обе ЭВМ устанавливают определенный разряд регистров 47 блока 1, затем проверкой состояний регистров i47 определяется установка устройства в режим дублирования. Особенность блока 1 состоит в том, что только при записи в регистры 46 в режиме дублирования производится синхронизация машин, обращение к остальным блокам производится без синхронизации.

При выполнении контрольнь1Х операций производится запись необходимых данных в регистры 46 блока 1. Запись данных в каждый регистр 46 вызывает появление нулевого сигнала на соответствующем выходе 17 блока 1. Если в допустимом интервале времени поступает нулевой сигнал на другой выход 17, то узел 3 снимает сигнал блокировки на выходе 24. При несовпадении контрольных данных узел 3 вырабатывает сигнал запроса прерывания на обе ЭВМ. В обоих случаях машины продолжают свою работу. Во втором случае они переходят в режим обработки сигнала прерывания, для чего, определив код запроса прерывания, считывают информацию с диагностических выходов узла 3. Отсутствие ошибки при повторении команды вызывает продолжение программы, в противном случае определяется неисправная ЭВМ, которая переводится в режим восстановления, устройство контроля переводится в режим независимой работы. После замены или восстановления отказавшей ЭВМ с пульта посылается команда перехода на дублированный режим. Рабочая машина приостанавливает свои операции. Подключаемая машина считывает из памяти рабочей машины необходимую информацию, далее производится настройка

устройства контроля на режим дублирования.

В случае невозможности определения за заданное время, какая из машин отказала, при наличии устойчивого несовпадения контрольных данных, вырабатывается сигнал неисправимой ошибки, и машины выполняют программу безопасного останова.

левого сигнала с одного из выходов 18. Использование двух сигналов позволяет перейти на режим независимой работы по команде одной машины,когда другая, вследствие своего отказа,выполнить такую операцию не может.

Разблокировка триггеров узла 3 производится только в дублированном режиме. Первьй нулевой сигнал на одРассмотрим операцию, когда на уст- ном из выходов 17 вызывает единичный

ройство контроля не поступают контрольные данные от одной из машин. Через определенный интервал после .установки одного из сигналов на выходе 17 в нуль узел 3 разблокирует узлы 4., и 4.., что разрешает продолжение работы машины, выставившей сигнал на выходе 17. Одновременно устанавливается сигнал прерывания и сигнал на одном из диагностических выходов узла 3, Анализ диагностической информации позволяет определить причину прерывания и перейти на соответствующую диагностическую программу для идентификации отказавшей машины .

Узел задержки (фиг.2) работает сле- дукмцим образом.

Сигналом начальной установки RS- триггер 30 сбрасывается в нуль, а с выхода 18 переводится в нулевое состояние. В результате нулевой сигнал с выхода 11, вырабатываемый при установке соответствующего регистра данных блока 1, независимо от сигнала блокировки 24 переводит RS- триггер 30 в единичное состояние, вызывая формирование сигнала ответа. При снятии нулевого сигнала с выхода 17 RS-триггер 30 возвращается в нулевое состояние, снимая сигнал ответа. В дублированном режиме работы с выхода 18 блока 1 подается единичный сигнал. Теперь нулевой сигнал с

15

20

25

сигнал на выходе сумматора 31 по модулю два, который поступает на элемент ИЛИ 33, длительность задержки которого определяется допустимой задержкой в выполнении операций контро ля вычислительными машинами. Если сигнал на втором выходе 17 блока 1 появится раньше сигнала на выходе элемента ИЛИ 33, то сигнал на D-BXO- де триггера 41 устанавливается в нуль, а на выходе 24 формируется нулевой сигнал снятия блокировки узлов 3. В случае ошибки узел сравнения формирует единичный сигнал на входе 23, триггер 42 устанавливается в состояние единица и формирует сигнал прерывания на вход 21 блока 1 Элемент 38 обеспечивает задержку включения триггера до установки сигнала на входе 23. Если задержка сигнала на втором выходе 17 блока 1 превышает допустимую, то срабатывает триггер 41, снимается сигнал блокировки на выходе 24 и устанавливается 35 один из диагностических триггеров 39 и 40, формируя сигнал запроса прерывания на входе 21 блока 1.

Блок приемопередачи и настройки Q (фиг.4) работает следующим образом.

Рассмотрим работу первого полукомплекта. Селектор адреса 45 выявляет обращение к одному из элементов полукомштекта,, производит с помощью

30

выхода 17 блока 1 переключает RS-триг- 45 Управляющих сигналов 55 подключение

к магистрали выбранного элемента и выполнение заданной операции.Регистр состояния 47 и коммутатор 48 вне зависимости от режима работы устройства при обращении к ним выставляют на выходах Готовность нулевой сигнал, который через элемент И 49 поступает на вход Готовность селектора адреса 45, разрешая вьщачу сигнала Ответ на магистраль. При записи контрольных данных в регистр данных, последний посылает запрос сигнала ответа на узел управления за держки 3 и устанавливает блокировочгер 30 только при наличии нулевого . сигнала на выходе 24. По снятию нулевого сигнала с выхода 17 блока 1 RS-триггер 30 возвращается в исходное состояние.

Узел управления задержками работает следующим образом (фиг.З).

Сигналом начальной установки все триггеры устанавливаются в состояние нуль. Нулевые сигналы с выходов 18 блока 1 блокируют через элементы И 34 и И-НЕ 35 работу всех триггеров. Для указанной блокировки достаточно нулевого сигнала с одного из выходов 18. Использование двух сигналов позволяет перейти на режим независимой работы по команде одной машины,когда другая, вследствие своего отказа,выполнить такую операцию не может.

Разблокировка триггеров узла 3 производится только в дублированном режиме. Первьй нулевой сигнал на од5

0

5

сигнал на выходе сумматора 31 по модулю два, который поступает на элемент ИЛИ 33, длительность задержки которого определяется допустимой задержкой в выполнении операций контроля вычислительными машинами. Если сигнал на втором выходе 17 блока 1 появится раньше сигнала на выходе элемента ИЛИ 33, то сигнал на D-BXO- де триггера 41 устанавливается в нуль, а на выходе 24 формируется нулевой сигнал снятия блокировки узлов 3. В случае ошибки узел сравнения формирует единичный сигнал на входе 23, триггер 42 устанавливается в состояние единица и формирует сигнал прерывания на вход 21 блока 1. Элемент 38 обеспечивает задержку включения триггера до установки сигнала на входе 23. Если задержка сигнала на втором выходе 17 блока 1 превышает допустимую, то срабатывает триггер 41, снимается сигнал блокировки на выходе 24 и устанавливается 5 один из диагностических триггеров 39 и 40, формируя сигнал запроса прерывания на входе 21 блока 1.

Блок приемопередачи и настройки Q (фиг.4) работает следующим образом.

Рассмотрим работу первого полукомплекта. Селектор адреса 45 выявляет обращение к одному из элементов полукомштекта,, производит с помощью

0

45 Управляющих сигналов 55 подключение

50

55

к магистрали выбранного элемента и выполнение заданной операции.Регистр состояния 47 и коммутатор 48 вне зависимости от режима работы устрой ства при обращении к ним выставляют на выходах Готовность нулевой сигнал, который через элемент И 49 поступает на вход Готовность селектора адреса 45, разрешая вьщачу сигнала Ответ на магистраль. При записи контрольных данных в регистр данных, последний посылает запрос сигнала ответа на узел управления задержки 3 и устанавливает блокировоч712

ный сигнал на выходе 15 с целью блокировки формирователя допустимой задержки сигнала Ответ относительно сигнала Обмен своей ЭВМ. Сигнал разрешения ответа поступает на вход 21 и далее выдается селектором адреса 45 в магистраль. Чтение любой информации производится через коммутатор 48. Регистр состояния, кроме хранения состояния режима работы,может быть использован для записи различной диагностической информации о состоянии машины, что позволяет другой ЭВМ использовать эту информацию в режиме анализа ошибок.

Формула изобретения

1. Устройство для контроля дублированной системы, содержащее узел сравнения, отличающее ся тем, что, с целью повьпиения быстродействия и расширения области применения устройства, в него введены блок приемопередачи и настройки, узел управления задержками, первый второй узлы задержки, первые и вторые входы Обмен, Чтение, Запись, Внешнее устройство Адрес Данные, Выборка кристалла, На- чальная установка,а также первые и вторые выходы Ответ, Запрос прерывания, Блокировка блока приемо ,передачи и настройки подключены к соответствующим линиям магистралей первой и второй вычислительных машин соответственно, первые и вторые информационные выходы блока приемопередачи и настройки подключены соответственно к первым и вторым ин- формационным входам узла сравнения, первый управляющий выход и первый выход запроса сигнала ответа - к соответствующим входам узла управления задержками и первого узла за- держки, второй управляющий выход и второй выход запроса сигнала ответа - к соответствующим входам узла управления задержками и второго узл задержки, выход сброса - к соответ- ствующим входам узлов задержки и узла управления задержками, первый и второй входы разрешения сигнала ответа - к выходам первого и второго узлов задержки соответственно, вход запроса прерывания и диагностические выходы - к соответствующим выходам узла управления задержками,вход приэма сигнала ошибки которого под8

0

5

5

0 5 0 0 5 Q

ключен к выходу узла сравнения, а блокировочный выход - к блокировочным входам узлов задержки.

2.Устройство по п.1, о т л и- чающееся тем, что узел задержки содержит первый и второй элементы И, два элемента ИЛИ, элемент НЕ, RS-триггер, вход запроса сигнала ответа узла подключен к первым входам первого и второго элементов ИЛИ,через элемент НЕ, - к первому входу первого .элемента И, второй вход которого соединен со входом сброса узла, а-выход - с R-входом триггера, вход блокировки узла подключен ко второму входу первого элемента ИЛИ,

а управляющий вход - к первому входу второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к S-входу триггера, инверсный выход которого является выходом сигнала разрешения ответа узла.

3.Устройство по П.1, отличающееся тем, что узел управления задержками содержит сумматор по модулю два, с третьего по четвертый элементы ИЛИ, с третьего по пятый элементы И, первый и второй элементы задержки, элементы ИЛИ-НЕ, И-НЕ, с первого по четвертый D-триг- геры с динамическим управлением, первый и второй входы запроса сигнала ответа узла подсоединены соответственно к первым и вторым входам сумматора по модулю два, третьего элемента ИЛИ и D-входам первого и второго триггеров, первый и второй управляющие входы - соответственно к первому и второму входам элемента И-НЕ и третьего элемента И,третий вход которого подключен через первый элемент задержки к выходу сумматора по модулю два и D-входу третьего триггера, а выход - к С-входу этого триггера, вход начальной установки узла - к R-входам первого, второго и четвертого триггеров и к первому входу четвертого элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, первыми входами пятого элемента И и элемента ИЛИ-НЕ, второй вход которого подключен к выходу элемента И-НЕ, а выход через второй элемент задержки - к С-входу четвертого триггера, D-вход которого подключен ко входу

приема сигнала ошибки узла, R-вход третьего триггера соединен с выходом четвертого элемента И, прямой выход - с С-входами первого и второго триггеров, а инверсный выход - со вторым входом пятого элемента И, выход которого является блокировочным

/7;

f/.

20,

202

21

22

выходом узла, прямые выходы пер вого, второго и четвертого триггеров подключены к соответствующим диагностическим выходам узла и ко входам пятого элемента ИЛИ, выход которого является выходом запроса прерывания узла.

2д

2ft

V/

- -

2

Н

фиг. 1

Lfl

w

На20

-о

иг,2

0ut.3

«5

Гот.

J

56

55

г

51

e

п 161

6

fbl

/

. .75,

t

г

4l8i

7

Wi

S f

Пер8ый полукомплект

Второй полукомплект

/г

fO

122,0

52

Гвт.

/ ч

/А

//

8

22,

20 i

Гот.

1- 43

50

1621 В21

0/5

фиг Л

Составитель В, Максимов Редактор И. Сегляник Техред А.Кравчук Корректор А. Зимокосов

398/60

Тираж 802 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, .Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРО-ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2000 |

|

RU2209462C2 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1587524A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

Изобретение может быть использовано в автоматике и вычислительной технике при построении надежных вычислительных систем.Цель изобретения состоит в повышении быстродействия устройства контроля и расширении области его применения за счет контроля асинхронных вычислительных процессов. Устройство содержит блок приемопере- дачи и настройки, узел сравнения, узел управления задержкой, первый и второй узлы задержки. Блок приемопередачи и настройки подключен к магистрали двух вычислительных машин и настраивается машинами либо в режим независимой работы ЭВМ, либо в режим дублирования. В режиме дублирования устройство принимает данные от одной ЭВМ и переводит ее в режим ожидания, задерживая выдачу сигнала Ответ на магистраль. Одновременно запускается узел управления задержкой, формирующий сигнал максимально допустимого времени ожидания. Если вторая ЭВМ записывает свои данные в блок приемопередачи и настройки через допустимый интервал задержки, то данные сравниваются узлом сравнения. При совпадении данных узел управления задержкой снимает блокировку узлов задержки, разрешая выдачу сигнала Ответ.в обе магистрали. В случае несовпадения данных или задержки данных от одной ЭВМ выдается сигнал Ответ в магистраль вьщав- шей данные машины и формируются сигналы запроса прерывания. Далее анализ ошибок ведется программными средствами. При отказе одной ЭВМ исправная переводит устройство в режим независимосй работы и продолжает свою работу, пока неисправная ЭВМ восстанавливается. 2 з.п. ф-лы,5 ил . с 9 (Л o ;о :о х

| Балашов Е.П | |||

| и др | |||

| Микропроцессоры и микропроцессорные системы | |||

| М.: Радио и связь, 1981, стр | |||

| Счетная линейка для вычисления объемов земляных работ | 1919 |

|

SU160A1 |

| Дублированная система управления | 1982 |

|

SU1062906A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для сопряжения двухмашинной вычислительной системы | 1982 |

|

SU1075250A1 |

Авторы

Даты

1987-02-28—Публикация

1985-06-14—Подача