Изобретение относится к вычислиельной технике, может быть использоано при построении специализированых устройств, работающих в избыточой системе счисления, и является совершенствованием изобретения по . вт.св. № 1242925.

Цель изобретения - расширение обасти применения за счет умножения на коэффициенты, выраженные в двоичной форме.

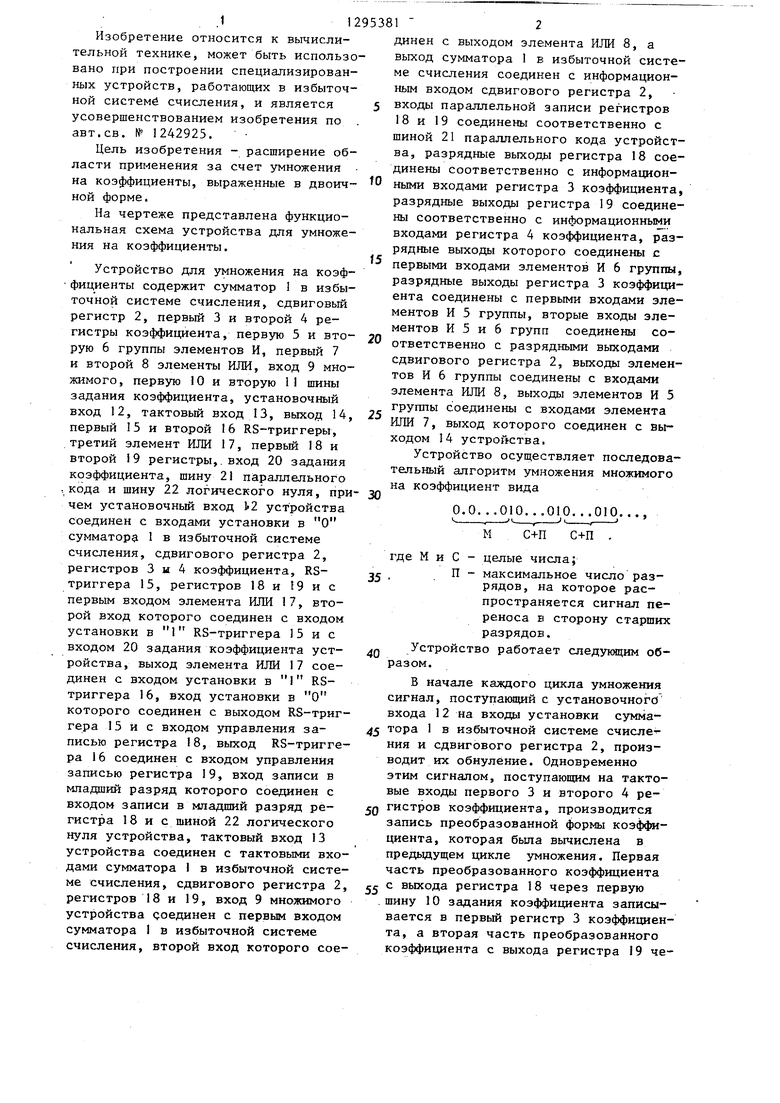

На чертеже представлена функциональная схема устройства для умножения на коэффициенты.

Устройство для умножения на коэф- фициенты содержит сумматор 1 в избыточной системе счисления, сдвиговый регистр 2, первый 3 и второй 4 регистры коэффициента, первую 5 и вторую 6 группы элементов И, первый 7 и второй 8 элементы ИЛИ, вход 9 множимого , первую 10 и вторую 1I шины задания коэффициента, установочный вход 12, тактовый вход 13, выход 14, первый 15 и второй 16 RS-триггеры, третий элемент ИЛИ 17, первый 18 и второй 19 регистры,. вход 20 зада1дая коэффициента, шину 21 параллельного кода и шину 22 логического нуля, при чем установочный вход Ь2 устройства соединен с входами установки в О сумматора 1 в избыточной системе счисления, сдвигового регистра 2, регистров 3 н 4 коэффициента, RS- триггера 15, регистров 18 и 19 и с первым входом элемента ИЛИ 17, второй вход которого соединен с входом установки в 1 RS-триггера 15 и с входом 20 задания коэффициента устройства, выход элемента ИЛИ 17 соединен с входом установки в I RS- триггера 16, вход установки в О которого соединен с выходом RS-триггера 15 и с входом управления записью регистра 18, выход RS-триггера 16 соединен с входом управления записью регистра 19, вход записи в младший разряд которого соединен с входом записи в младший разряд регистра 18 и с шиной 22 логического нуля устройства, тактовый вход 13 устройства соединен с тактовыми входами сумматора 1 в избыточной системе счисления, сдвигового регистра 2, регистров 18 и 19, вход 9 множимого устройства соединен с первым входом сумматора I в избыточной системе счисления, второй вход которого соеfO

динен с выходом элемента Р1ЛИ 8, а выход сумматора 1 в избыточной системе счисления соединен с информационным входом сдвигового регистра 2, входы параллельной записи регистров 18 и 19 соединены соответственно с шиной 21 параллельного кода устройства, разрядные выходД) регистра 18 соединены соответственно с информационными входами регистра 3 коэффициента, разрядные выходы регистра 19 соединены соответственно с информационными входами регистра 4 коэффициента, разрядные выходы которого соединены с первыми входами элементов И 6 группы, разрядные выходы регистра 3 коэффициента соединены с первыми входами элементов И 5 группы, вторые входы элементов И 5 и 6 групп соединены соответственно с разрядными выходами сдвигового регистра 2, выходы элементов И 6 группы соединены с входами элемента ИЛИ 8, выходы элементов И 5 группы Соединены с входами элемента ИЛИ 7, выход которого соединен с выходом 14 устройства.

Устройство осуществляет последовательный алгоритм умножения множимого на коэффициент вида

20

25

30

0.0. .„010..,ОШ. ..010...,

f

с+п

м

с+п

где М и С - ц(5лые числа;

, П - максимальное число разрядов, на которое распространяется сигнал переноса в сторону старших р 1зрядов.

Устройство работает следукнцим образом.

В начале каждого цикла умножения сигнал, поступающий с установочного входа 12 на входы установки сумматора 1 в избыточной системе счисле- ния и сдвигового регистра 2, производит их обнуление. Одновременно этим сигналом, поступающим на тактовые входы первого 3 и второго 4 регистров коэффициента, производится запись преобразованной формы коэффициента, которая была вычислена в предьщущем цикле умножения. Первая часть преобразованного коэффициента

с выхода регистра 18 через первую шину 10 задания коэффициента записывается в первый регистр 3 коэффициента, а вторая часть преобразованного коэффициента с выхода регистра 19 че

.-

3129

рез вторую шину 11 задания коэффициента - во второй регистр 4 коэффициента.

Каждая из частей преобразованного коэффициента является унитарным ко- дом. Позиция единицы во второй части преобразованного коэффициента, записанной во второй регистр 4 коэффициента, определяет число нулей С в коэффициенте, на который производит- ся умножение, а позиция единицы в первой части преобразованного коэффициента, записанной в первый регист 3 коэффициента, определяет число нулей М в коэффициенте.Затем с тактового входа 13 на тактовые входы сумматора 1 в избыточной системе счисления и сдвигового регистра 2 начинают поступать тактирующие; импульсы. Причем количество так тов в каждом цикле вычисления равно К + П (К - разрядность множимого), что обусловлено задержкой распространения одноименных бит числа на выхо- де сумматора 1 в избыточной системе счисления относительно, чисел на его входе на П тактов.

На вход первого слагаемого сумматора 1 в избыточной системе счислв- ния последовательно поступают биты числа множимого, начиная со старшего разряда. На выходе сумматора 1 в

избыточной системе счисления формируется результат, который можно ий- терпретировать как результат умножения, так и как накапливающую сумму частичных произведений. Рассмотрим этот результат как сумму частичных произведений.

Сумма частичных произведений с выхода сумматора 1 в избыточной системе счисления поступает на информационный вход сдвигового регистра 2. Записанная в сдвиговый регистр 2 ин- формация в каждом такте вычисления продвигается в сдвиговом регистре 2 на один разряд. Так как выходы сдвигового регистра 2 соединены с вторыми входами одноименных элементов И второй группы элементов И 6, а на первые входы каждого из элементов И второй группы элементов И 6 поступает унитарный код второй части преобразованного коэффициента с выхода второго регистра 4 коэффициента, то на выходе только одного из элементов И второй группы элементов И 6 присутствует сигнал, соответствующий значе15

20

5 у

30

35 40

455055нию частичных произведений, задержанной на С тактов (С определяется унитарным кодом второй части преобразованного коэффициента) по отношению к значению суммы частичных произведений на информационном входе сдвигового регистра 2. Сигнал с выхода второй группы элементов И 6 через второй элемент ИЛИ 8 поступает на вход второго слагаемого сумматора 1 в избыточной системе счисления.

Таким образом, суммарная задержка появления бит суммы частичных произведений на входе второго слагаемого сумматора 1 в избыточной системе счисления относительно появления одноименных бит множимого на входе.первого слагаемого с учетом внутренней задержки сумматора в избыточной сие- теме счисления в П тактов составляет С + П тактов.

Сумма частичных произведений, поступающая на вход второго слагаемого сумматора 1 в избыточной системе счисления, совместно с множимым, поступающим на вход первого слагаемого, участвуют в формировании новой суммы частичных произведений.

Рассмотрим результат вычисления сумматора 1 в избыточной системе счисления как произведение множимого на вторую часть преобразованного коэффициента. 1

Так как выходы сдвигового регистра 2 соединены с вторыми входами одноименных элементов И первой группы элементов И 5, а на первые входы каждого из элементов И первой группы элементов И 5 поступает унитарный код первой части преобразованного коэффициента с выхода первого регистра 3 коэффициента, то на выходе только одного из элементов И первой группы элементов И 5 присутствует сигнал, соответствующий значению произведения множимого на вторую часть преобразованного коэффициента, которое задержано на М тактов (М определяется унитарным кодом первой части преобразованного коэффициента) по отношению к значению произведения множимого на вторую часть преобразованного коэффициента, которое присутствует на информационном входе сдвигового регистра 2. Учитывая, что в начале каждого цикла умножения сдвиговый регистр 2 обнуляется, то указанная процедура равносильна присваиванию старшим М

разрядом произведения множимого на полный коэффициент (полное значение которого определяется первой и второй частями преобразованного коэффициента, хранящимся в первом и втором регистрах 3 и 4 коэффициента соответственно) нулевых значений, т.е. умножению произведения множимого на вторую часть преобразованного коэффициента на , где R - основание системы счисления.

Сигнал произведения с выхода первой группы элементов И 5 через первый элемент ИЛИ 7 поразрядно поступает на вь1ход 14 устройства.

После подачи на вход первого слагаемого всех К бит множимого сумматор 1 в избыточной системе счисления еще П тактов продолжает довычислять результат произведения. В течение этих П тактов на вход первого слагаемого сумматора 1 в избыточной системе счисления необходимо подавать нули или сигнал, приводящий к формиро- ванию округления результата умножения. Конкретный вид сигнала определяется в зависимости от того, какая именно система счисления применяется

В начале каждого цикла умножения сигнал, поступающий с установочного входа 12 на тактовые входы первого 3 и второго 4 регистров коэффициента, производит перезапись в них первой и второй частей преобразованного коэффициента, которые были вычислены в предыдущем цикле умножения, из соответственно первого 18 и второго 19 регистров.

Одновременно этот сигнал, поступающий на входы установки первого 18 и второго 19 регистров, переводит последние в режим параллельной записи. С приходом на тактовый вход первого и второго регистров 18 и 19 так тового сигнала с тактового входа 13 устройства в регистры 18 и 19 с шины 21 параллельного кода производится параллельная запись кода 00...001 (единица в младшем разряде).

Сигнал, поступйкмций с установочного входа 12 устройства на R-вход первого RS-триггера 15 и через третий элемент ИЛИ 17 на S-вход второго RS-триггера 16, переводит первый RS- триггер 15 в нулевое состояние, а второй RS-триггер 16 - в единичное .состояние .

с

0

0

-

5

После прекращения действия сигнала установки, поступающего с входа 12 устройства, нулевой потенциал, поступающий с выхода первого RS-триггера I5 на управляющий вход первого регистра 18, переводит последний в режим последовательной записи и сдвига, а единичный потенциал, поступающий с выхода второго RS-триггера 16 на управляющий вход второго регистра 9, переводит последний в режим хранения информации.

Затем одновременно с поступлением на вход сумматора в избыточной системе счисления с входа 9 множимого последовательного кода множимого, тактируемого сигналаг-ш с тактового входа 13,-на вход 20 задания .коэффициента последовательно поступает код коэффициента, начиная со старших разрядов, на который производится умножение в следующем цикле умножения.

В течение М тактов, пока на вход 20 задания коэффициента поступает М первых нулевых разрядов коэффициента, первьш регистр 18 работает в режиме последовательной записи и сдвига информации. При этом логическая единица, записанная в него в такте установки устройства, последовательно продвигается в сторону старших разрядов, а младпше разряда заполняются нулями с входа последовательной записи, который подключен к шине 22 логического нуля устройства.

В момент прихода на вход 20 задания коэффициента первой единицы в коде коэффициента потенциал Лог.1 с входа 20 задания коэффициента поступает на иМпульсньй S-вход первого RS-триггера 15 и через третий элемент ИЛИ 17 на потещщал1зный S-вход второго RS-триггера 16 и не изменяет их состояние. В момент прихода на вход 20 коэффициента следующего нуля в коде коэффициента (после единицы в коде коэффициента всегда следует) нуль) отрицательный перепад на импульсном S-входе перЕюго RS-триггера 15 переводит его в единичное состояния. Потенциал Лог.1, поступающий с выхода первого RS-триггера 15 на управляющий вход первого регистра 18, переводит последний в режим хранения информации. В этот момент времени формирование первой части преобразованного коэффициента заканчивается.

Передний фронт сигнала, поступаю- .щего с выхода первого RS-триггера 15 на импульсный R-вход второго RS-триггера 16 переводит его в нулевое состояние. Потенциал Лог.О с выхода второго RS-триггера 16 поступает на управляющий вход второго регистра 19 и переводит его в режим последовательной записи и сдвига информации, В течение следующих П-С тактов до прихода следующей единицы в коде коэффициента (1) во втором регистре 19 происходит потактовый сдвиг Лог.1, записанной в такте уста- ;новки устройства, в сторону старших разрядов и заполнение младших разрядов нулями с входа последовательной записи, подключенного к шине 22 логического нуля устройст- ва.

В момент прихода на вход 20 задания коэффициента второй единицы в коде коэффициента потенциал Лог.1 с входа 20 задания коэффициента через третий элемент ИЛИ 17 поступает на S-вход второго RS-триггера 16 и переводит его в единичное состояние, а потенциал Лог.1, поступающий с его выхода на управляющий вход второго регистра 19, переводит последний в режим хранения информации. На этом формирование обеих частей преобразованного коэффициента заканчивается. ;Поступающий затем код на вход 20 задания коэффициента на дальнейшую работу устройства влияния не оказывает.

Редактор И.Шулла

Составитель В.Гусев Техред Л.Сердюкова

Заказ 617/54 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

0

Формула изобретения

Устройство для умножения на коэффициенты по авт.св. № 1242925, отличающееся тем, что, с целью расширения области применения за счет умножения на коэффициенты, выраженные в двоичной форме, в него введены перв.ьй и второй RS-триггеры, первый и второй регистры и третий элемент ИЛИ, причем разрядные выходы первого и второго регистров соединены соответственно с первой и второй шинами задания коэффициентов устройства, входы управления записью первого и второго регистров соединены соответственно с выходами первого и второго RS-триггеров, выход первого RS-триггера соединен с входом установки в О второго RS-триггера, вход установки в 1 которого соедц- нен с выходом третьего элемента ИЛИ, первый вход которого соединен с входом установки в 1 первого RS-тригс гера и является входом задания коэффициента устройства, тактовый вход устройства соединен с тактовыми входами первого и второго регистров, установочный вход устройства соединен с вторым входом третьего элемента ИЛИ, входом установки в О первого RS-триггера и входом установки первого и второго регистров, входы параллельной записи которых соединены соответственно с шиной параллель5 ного кода устройства, входы записи в младший разряд первого и второго регистров соединены с шиной логического нуля устройства.

0

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1291966A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1985-09-19—Подача