Изобретение относится к вычислительной технике и может быть использовано для умножения многоразрядных последовательных кодов в системе счисления золотой пропорции или в двоичной знакоразрядной системе счисления.

Цель изобретения - расширение функщ-юнапьных возможностей за счет обеспечения выполнения операции умножения в двоичной знакоразрядной системе счисления.

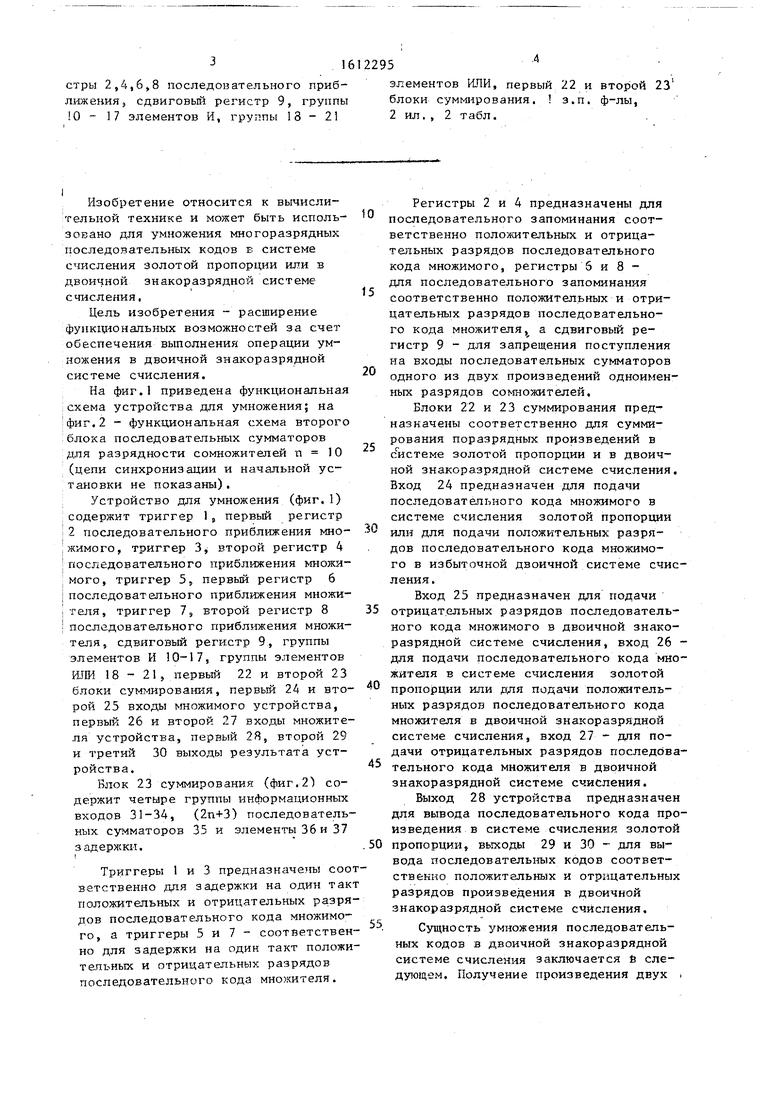

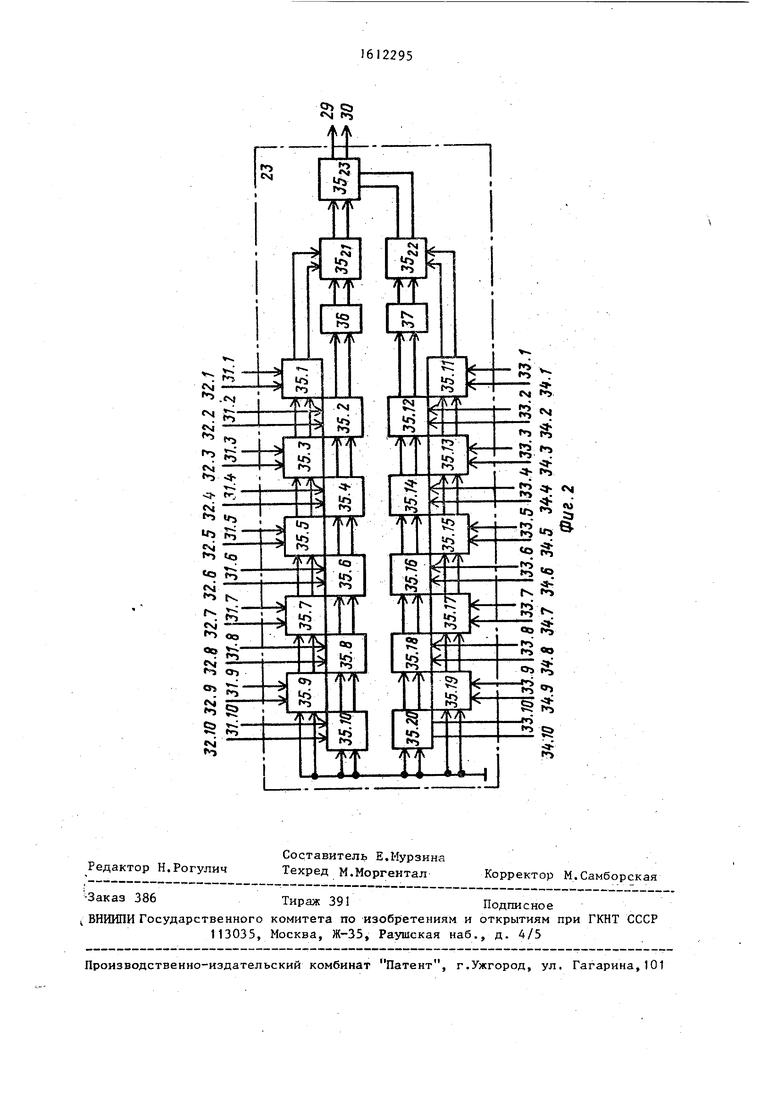

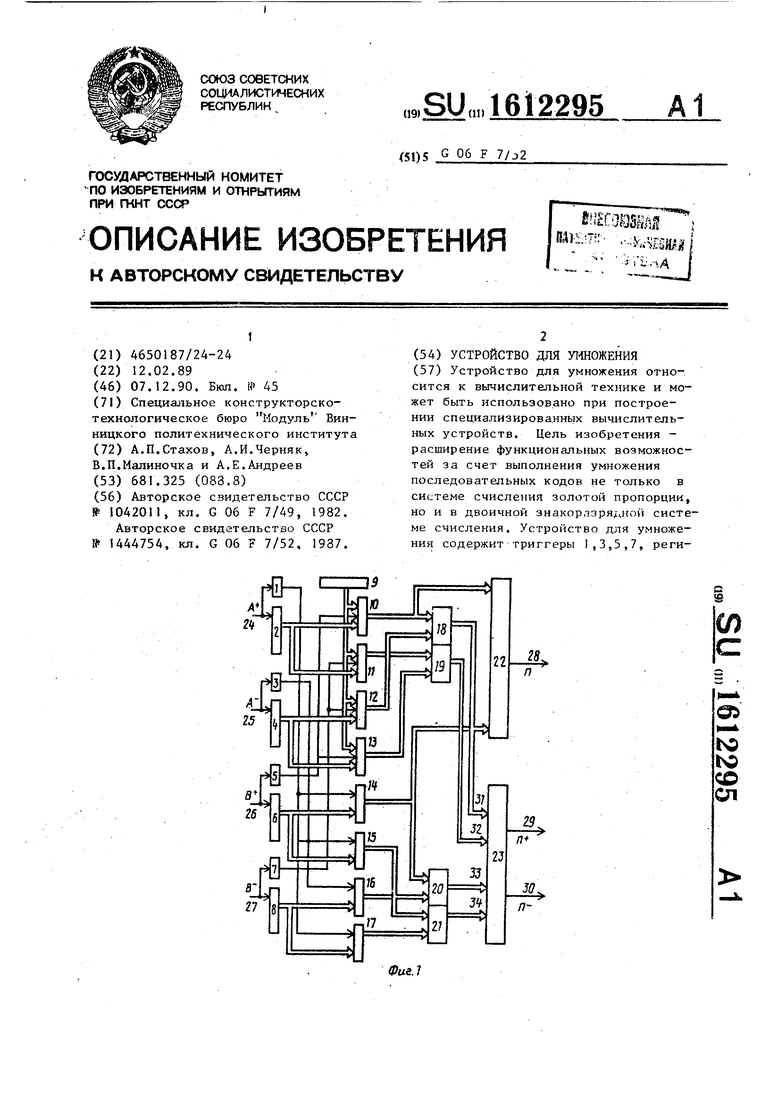

На фиг.1 приведена функциональная схема устройства для умножения; на фиг.2 - функциональная схема второго блока последовательных сумматоров для разрядности сомножителей п 10 (цепи синхронизации и начальной установки не показаны).

Устройство для умножения (фиг.1) содержит триггер 1, первый регистр 2 последовательного приближения множимого, триггер ЗУ второй регистр f последовательного приближения множимого, триггер 55 первый регистр 6 последовательного приближения множителя, триггер 7j второй регистр 8 последовательного приближения множителя, сдвиговый регистр 9, группы элементов И 10-17, группы элементов ИЛИ 18 - 21, первый 22 и второй 23 блоки суммирования, первый 2А и второй 25 входы множимого устройства, первый 26 и второй 27 входы множителя устройства, первый 2Я, второй 29 и третий 30 выходы результата устройства.

Блок 23 суммирования (фиг.2) содержит четыре группы информационных входов 31-34, (2п+3) последовательных сумматоров 35 и элементы 36 и 37 3 адерх(ки.

Триггеры 1 и 3 предназначены соответственно для задержки на один такт положительных и отрицательных разрядов последовательного кода множимо- го, а триггеры 5 и 7 - соответственно для задержки на один такт положи- тепьных и отрицательных разрядов последовательного кода множителя.

5

0

5

0

5

0

5

50

,

Регистры 2 и 4 предназначены для последовательного запоминания соответственно полохсительных и отрицательных разрядов последовательного кода множимого, регистры 6 и 8 - для последовательного запоминания соответственно положительных и отрицательных разрядов последовательного кода множителя, а сдвиговый регистр 9 - для запрещения поступления на входы последовательных сумматоров одного из двух произведений одноименных разрядов сомножителей.

Блоки 22 и 23 суммирования предназначены соответственно для суммирования поразрядных произведений в с истеме золотой пропорции и в двоичной знакоразрядной системе счисления. Вход 24 предназначен для подачи последовательного кода множимого в системе счисления золотой пропорции или для подачи положительных разрядов последовательного кода множимого в избыточной ДВОИЧНО) системе счисления.

Вход 25 предназначен для подачи отрицательных разрядов последовательного кода множимого в двоичной знакоразрядной системе счисления, вход 26 - для подачи последовательного кода множителя в системе счисления золотой пропорции или для подачи положительных разрядов последовательного кода множителя в двоичной знакоразрядной системе счисления, вход 27 - для подачи отрицательных разрядов последовательного кода множителя в двоичной знакоразрядной системе счисления.

Выход 28 устройства предназначен для вывода последовательного кода произведения в системе счисления золотой пропорции, выходы 29 и 30 - для вывода последовательных кодов соответственно положительных и отрицательных разрядов произведения в двоичной знакоразрядной системе счисления.

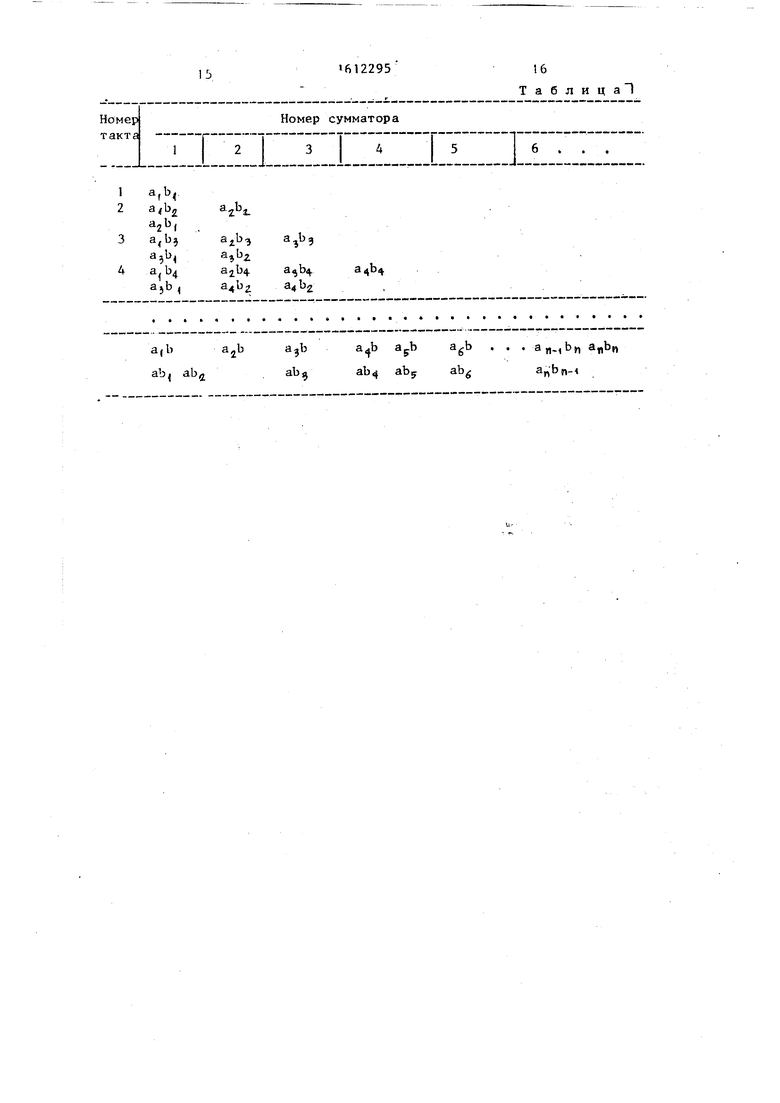

Сущность умножения последовательных кодов в двоичной знакоразрядной системе счисления заключается 6 следующем. Получение произведения двух i

1612295

кодов АЙВ можно представить мер разряда, i 1, 2, 3,..,п| п - как сумму частичных произведений разрядность.

вида П А-Ь;, где Ь; - значение Произведение двух кодов можно Ч-го разр яда сомножителя В ; i - но- 5 представить ив следующем виде:

а aj а а ... ап, а

bj ...

а, bn а2.Ь„ a,bn .. .а„., Ь„а„Ь,

+ .

n-t ,. ..an.,bn-, а„Ьп-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двух @ -разрядных чисел | 1987 |

|

SU1439581A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

Устройство для умножения относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств. Цель изобретения - расширение функциональных возможностей за счет выполнения умножения последовательных кодов не только в системе счисления золотой пропорции, но и в двоичной знакоразрядной системе счисления. Устройство для умножения содержит триггеры 1, 3, 5, 7, регистры 2, 4, 6, 8 последовательного приближения, сдвиговый регистр 9, группы 10 - 17 элементов И, группы 18 - 21 элементов ИЛИ, первый 22 и второй 23 блоки суммирования. 1 з.п. ф-лы, 2 ил, 2 табл.

a,b4.a2b4a, ... а„., а,Ц а,Ьз ... а„, а,Ь, , ajb-i ,.. а„.,

a,b, , , ... a.b, .

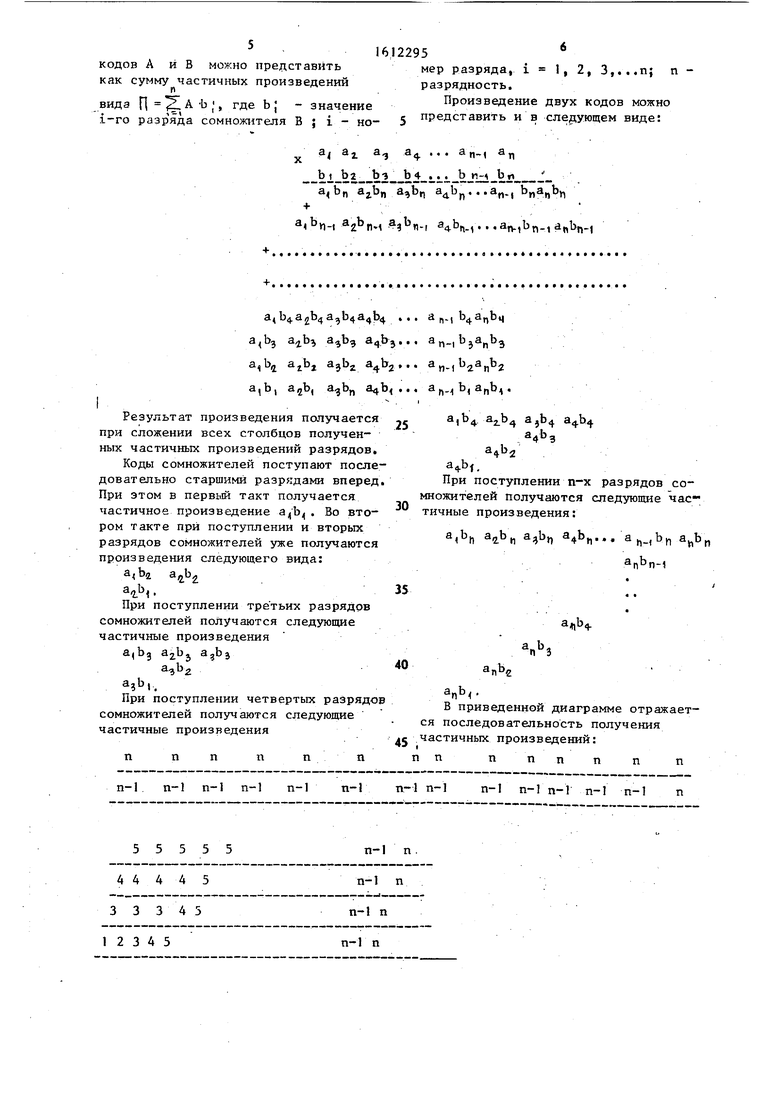

Результат произведения папучается -, а,Ьф }Ь4 при сложении всех столбцов получен- 4 з

нык частичных произведений разрядов,

Коды сомножителей поступают после- i-bf.

довательно старшими разрядами вперед. При поступлении п-х разрядов со- При этом в первый такт получается множителей получаются следующие час- частичное произведение . Во ВТО- тичные произведения: ром такте при поступлении и вторыхi к i к

разрядов сомножителей уже получаются произведения следующего вида:a bp-i

,.35..

При поступлении третьих разрядов

сомножителей получаются следующие ti

частичные произведения

а,Ьз 3

.

aibi,

„ a-b..

При поступлении четвертых разрядовD

сомножителей получаются следующие приведенной диаграмме отражаетчастичные произведенияся последовательность получения

д5частичных произведений:

пп ппппппппп п пп

п-1 п-1 п-1 п-1 п-1 п-1 п-1 п-1 п-1 п-1 п-1 п-1 п-1 п

55555п-1 п

44445п-1 п

33345п-1 п

12345п-1 п

гд 1 - соотцетствующее частичное

произведение при поступлении первых разрядов сомножителей 2 - соответствующие частичные произведения при поступлении вторых разрядов сомножителей;

п - соответствующие частичные произведения при поступлении п-х разрядов сомножителей.

Таким образом, за п тактов получаются все частичные произведения п-х разрядов сомножителей. Для сложения получаемых углов частичных произведений необходимо иметь п последовательно соединенных последовательных сумматоров для трех слагаемых или 2п последовательных сумматоров для двух слагаемых. При применении последовательных сумматоров для двух слагаемых на первые входы каждой пары сумматоров поступают частичные произведения сторон углов. На вторые входы каждой пары сумматоров поступают выходы сумм из предыдущих пар сумматоров. С каждым тактом по мере поступления очередных разрядов слагаемых происходит одновременный сдвиг промежуточных сумм последовательных сумматоров. На входы первой пары сумматоров поступают последовательно во времени частичные произведения а«Ь, , ., а,Ьз,. . ., П-, , , , а,,Ь , a4b,,. . ., ап.,Ь,, а Ь . На выходы второй пары сумматоров поступают последовательно во времени частичные произведения а2:Ь2, ,Ь,

алЬ

Un.,jCl2.Uf|

алЬ„ и а,,Ь.

-2.

,

,, ..., а f,.;, Ь2, af)b2 . На входы i-й пары сумматоров поступают последовательно во времени частичные произведения a,-bj, a b;, , a;b , i - n

а ,Ч( о : и а

Ь.,% а ,

,

. . ., а , Ь , а,Ь. . Причем частичные произведения а b | поступают только на один из входов i-й пары последовательных сумматоров.

В табл.1 приведен процесс поступления частичных произведений на входы последовательных сумматоров.

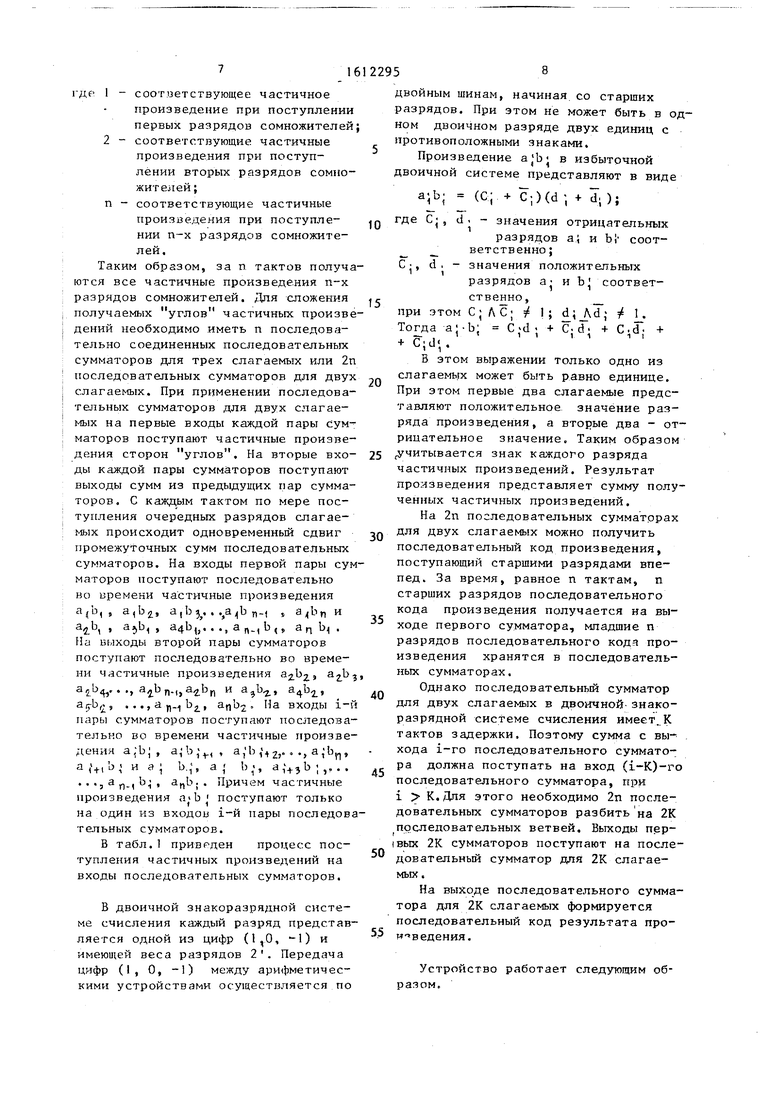

В двоичной знакоразрядной системе счисления каждый разряд представляется одной из цифр (1,0, -1) и имеющей веса разрядов 2. Передача цифр (I, О, -1) между арифметическими устройствами осуществляется по

двойным шинам, начиная со старших разрядов. При этом не может быть в одном двоичном разряде двух единиц с противоположными знаками.

Произведение ajb; в избыточной двоичной системе представляют в виде

а;Ь;

(С; C;)(d; d, );

где С-, d, - значения отрицательных

С;, d.

1

разрядов а; и соответственно ;

значения положительных разрядов а- и bj соответ

ственно,

при этом С; Л С; 1; 1. Тогтха а;-Ь; C;d ; + С; d;

Cid.

-f C.d;

в этом выражении только одно из слагаемь х может быть равно единице. При этом первые два слагаемые представляют положительное значение разряда произведения, а вторые два - отрицательное значение. Таким образом учитывается знак каждого разряда частичных произведений. Результат произведения представляет сумму полученных частичных произведений.

На 2п последовательных сумматорах для двух слагаемых можно получить последовательный код произведения, поступающий старшими разрядами впе- пед. За время, равное п тактам, п старших разрядов последовательного кода произведения получается на выходе первого сумматора, мпадшие п разрядов последовательного кода произведения хранятся в последовательных суммат ор ах.

Однако последовательньм сумматор для двух слагаемых в двоичной- знакоразрядной системе счисления имеет. К тактов задержки. Поэтому сумма с выхода i-ro последовательного сумматора должна поступать на вход (i-K)-ro последовательного сумматора, при i К.Для этого необходимо 2п последовательных сумматоров разбить на 2К последовательных ветвей. Выходы пер- 1ВЫХ 2К сумматоров поступают на последовательный сумматор для 2К слагаемых.

На выходе последовательного сумматора для 2К слагаемых формируется последовательный код результата про- и- ведения.

Устройство работает следующим образом.

10

При умножении чисел.представленных кодами в системе счисления золотой пропорции, на входы 24 и 26 устройства поступают последовательные коды сомножителей. На элементах 10 и 14 групп происходит образование поразрядных частичных произведений, которые складываются в блоке 22 в системе счисления золотой пропорции..На выходе 28 устройства формируется последовательный код произведения,начиная со старших разрядов. Последовательное устройство для умножения работает аналогично известному устрой- 15 ству.

При умножении чисел, представлен ных.в двоичной знакоразрядной системе счисления, на входы 24 и 25 устройства поступают соответственно по- ложительные и отрицательные разряды первого сомножителя, а на входы 26 и 27 - разряды второго сомножителя. На элементах И 0 группы образуются

20

группы формируются положительные значения разрядов частичных произведений разрядов множителя на i-й разряд множимого. На элементах 1ШИ 21 группы формируются отрицательные значения разрядов частичных произведений i разрядов множителя на х-й разряд mio жимого.

Частичные произведения, получаемые в каждом i-M такте работы устройства, складываются в блоке 23 в двоичной знакоразрядной системе счисления. На выходах 29 и 30 устройства формируют ся соответственно положительные и отрицательные разряды последовательного кода произведения,начиная со старших разрядов.

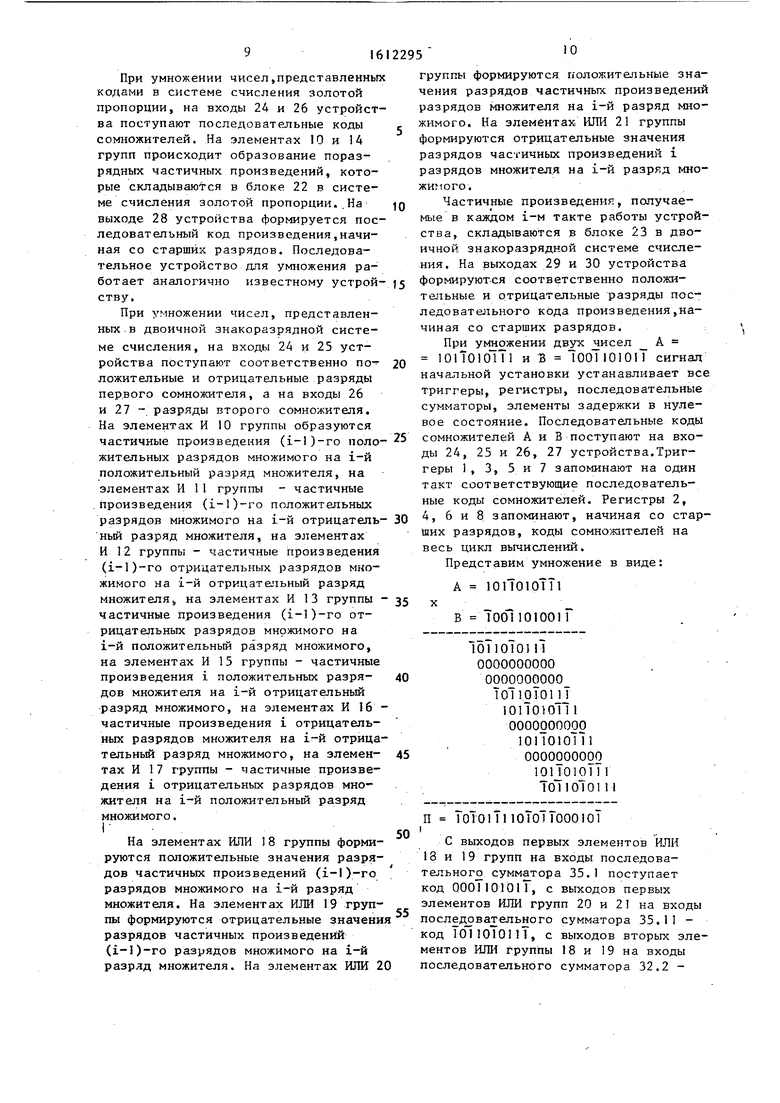

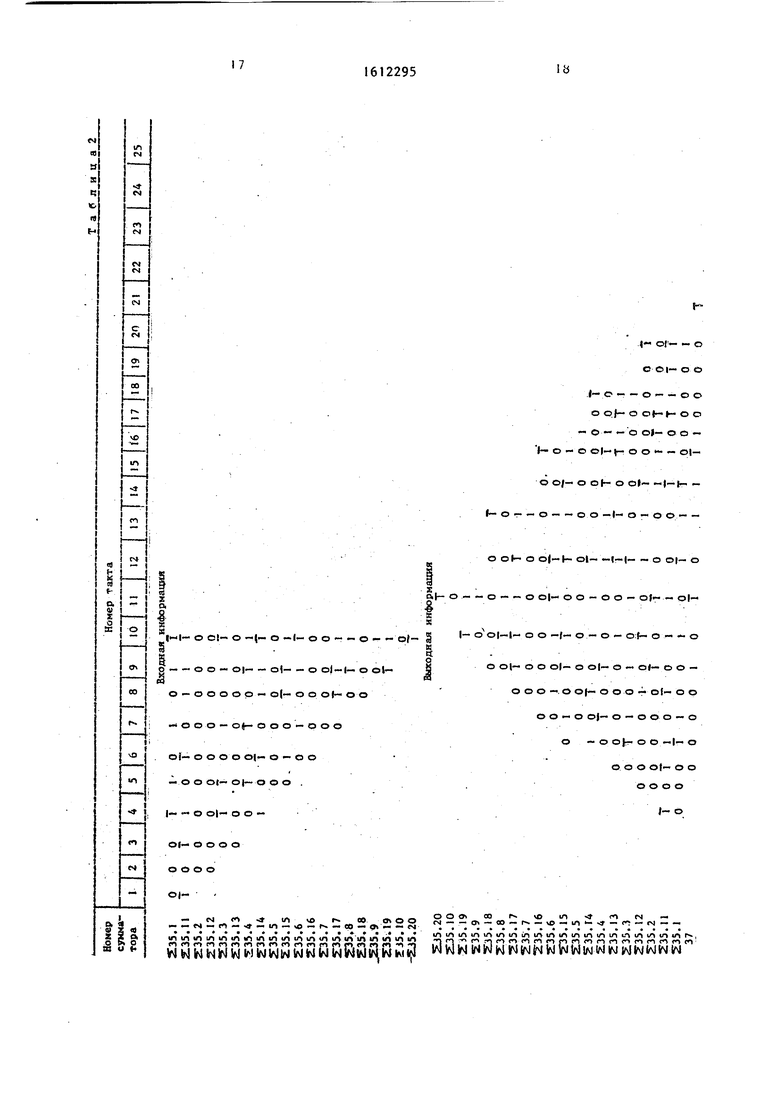

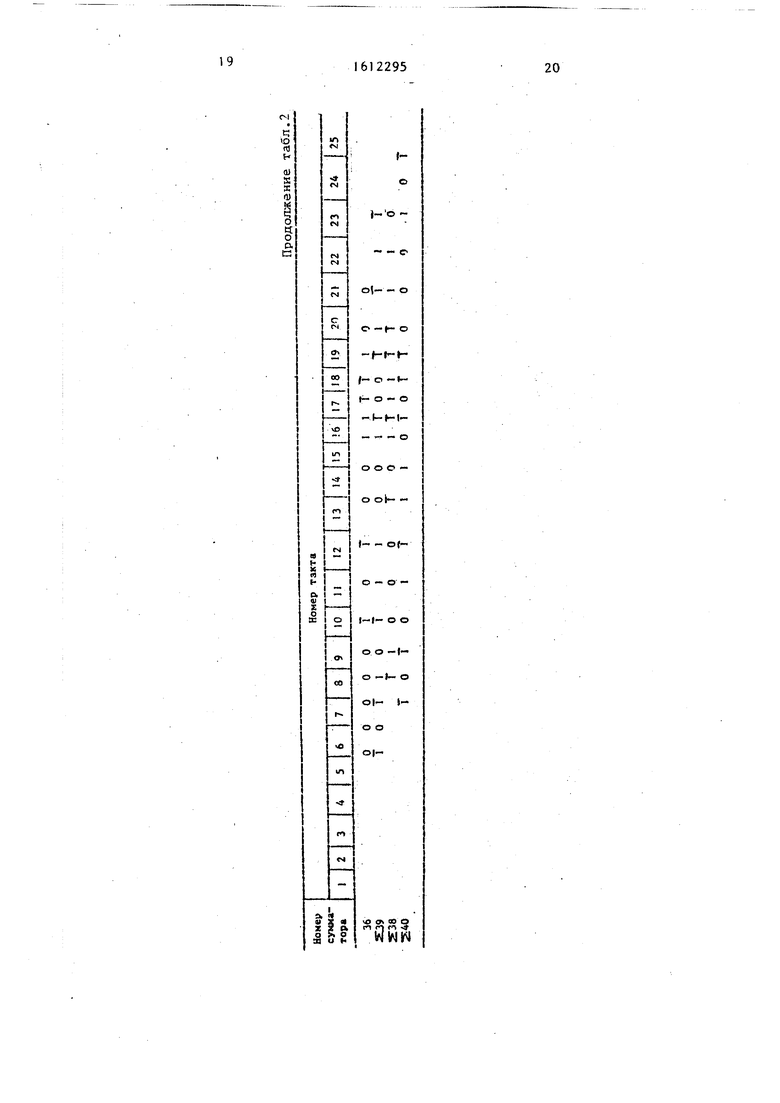

При умн жении двух чисел А lOlTOIOlTl и В 1001101011 сигнал начальной установки устанавливает все триггеры, регистры, последовательные сумматоры, элементы задержки в нулевое состояние. Последовательные коды

частичные произведения (i-l)-го поло- 25 сомножителей А и В поступают на входы 24, 25 и 26, 27 устройства.Триггеры 1 , 3, 5 и 7 запоминают на один такт соответствующие последовательные коды сомножителей. Регистры 2, 4, 6 и 8 запоминают, начиная со стар ших разрядов, коды сомножителей на весь цикл вычислений.

ительных разрядов множимого на i-й положительный разряд множителя, на элементах И 11 группы - частичные

произведения (i-t)-ro положительных разрядов множимого на i-й отрицатель- 30

ный разряд множителя, на элементах И 12 группы - частичные произведения (i-l)-ro отрицательных разрядов множимого на i-й отрицательный разряд множителя,, на элементах И 13 группы - 35 астичные произведения (i-)-ro отрицательных разрядов множимого на i-й положительный разряд множимого, на элементах И 15 группы - частичные произведения i положительных разря- 40 дев множителя на i-й отрицательный разряд множимого, на элементах И 16 - частичные произведения i отрицательных разрядов множителя на i-й отрицательный разряд множимого, на элемен- 45 тах И 17 группы - частичные произведения i отрицательных разрядов множителя на i-й положительный разряд множимого.

На элементах ИЛИ 18 группы формируются положительные значения разрядов частичных произведений (i-l)-ro разрядов множимого на i-й разряд множителя. На элементах ИЛИ 19 группы формируются отрицательные значения разрядов частичных произведений (i-l)-ro разрядов множимого на i-й разряд множителя. На элементах ИЛИ 20

5

0

группы формируются положительные значения разрядов частичных произведений разрядов множителя на i-й разряд множимого. На элементах 1ШИ 21 группы формируются отрицательные значения разрядов частичных произведений i разрядов множителя на х-й разряд mio жимого.

Частичные произведения, получаемые в каждом i-M такте работы устройства, складываются в блоке 23 в двоичной знакоразрядной системе счисления. На выходах 29 и 30 устройства формируют ся соответственно положительные и отрицательные разряды последовательного кода произведения,начиная со старших разрядов.

При умн жении двух чисел А lOlTOIOlTl и В 1001101011 сигнал начальной установки устанавливает все триггеры, регистры, последовательные сумматоры, элементы задержки в нулевое состояние. Последовательные коды

сомножителей А и В поступают на входы 24, 25 и 26, 27 устройства.Триггеры 1 , 3, 5 и 7 запоминают на один такт соответствующие последовательные коды сомножителей. Регистры 2, 4, 6 и 8 запоминают, начиная со старших разрядов, коды сомножителей на весь цикл вычислений.

Представим умножение в виде:

А lOlTOloTTl

X

В Tool 10100 if

10110Ю111 0000000000 0000000000

То 1101 он г ionoioili

0000000000

loiToioTli oooooooogo loiToioiTi Tonoioni

П ToToiTiloToTToooioT

1

с выходов первых элементов ИЛИ 18 и 19 групп на входы последова- тельног сумматора 35.1 поступает код 0001101011, с выходов первых элементов ИЛИ групп 20 и 21 на входы последовательного сумматора 35.11 - код 1011010111, с выходов вторых элементов ИЛИ группы 18 и 19 на входы последовательного сумматора 32.2 код OQOOOOOOO, с выходов вторых элементов ИЖ групп 20 и 21 на входы последовательного сумматора 35 .-2 - код 000000000, с выходов третьих элементов ИЛИ 18 и 19 групп на входы последовательного сумматора 35.3 - код ОТЮЮП, с выходов третьих элементов ИЛИ 20 и 21 групп на входы последовательного сумматора 35.13-- код 00000000, с выходов четвертьпс элементов ВДИ 18 и 19 групп на входы последовательного сумматора 35.4 г код OloToTl, с выходов четвертых элементов ИЛИ 20 и 21 групп на вхо- ды последовательного сумматора 35.14- код ШТОПТ. Этот и дальнейший процесс умножения представлен в табл.2.

Формула изобретения

5

0

ствующих элементов и второй группы, а выход - с первым входом результата устройства, входы синхронизации и начальной установки которого соединены соответственно с входами синхронизации и начальной установки первого и второго триггеров, первых регистров последовательного приближения множимого и множителя, сдвигового регистра и первого блока суммирования, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения выполнения операции умножения в двоичной знакоразрядной системе счисления, в него введены второй регистр последовательного приближения множимого, второй регистр последовательного приближения ъшожителя, третий и четвертый триггеры, с третьей по восьмую группы по п элементов И, четыре группы по п элементов ИЛИ и второй блок суммирования, причем второй вход множимого устройства соединен с информационными входами третьего триггера и второго регистра последовательного приближения множимого, разрядные выходы которого соединены с первыми входами соответствующих элементов И третьей и четвертой групп, вторые входы .которых соединены с соответствующими разрядными выходами сдвигового регистра и первыми входами соответствующих элементов И пятой группы, вторые входы которых соединены с соответствующими разрядными выходами первого регистра последовательного приближения множимого, второй вход гдаожителя устройства соединен с информационными входами четвертого триггера и второго регистра последовательного приближения множителя, разрядные выходы которого соединены с первыми входами соответствующих элементов И шестой и седьмой групп, выходы которых соединены с первыми входами соответствующих элементов ИЛИ первой и второй групп, выход первого триггера соединен с вторыми входами элементов И седьмой группы, выход второго триггера соединен с третьими входами элементов И четвертой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ первой и второй групп, выход первого триггера соединен с вторыми входами элементов И седьмой группы, выход второго

5

40

45

50

55

триггера соединен с третьими входам элементов И четвертой группы,выходы которых соединены с первыми входами соответствующих элементов ИЛИ третье группы, вторые входы которых соединены с выходами соответствующих элементов И пятой группы, третьи входы которых соединены с выходом четвертого триггера и третьими входами соответствующих элементов И третьей группы, выходы которых соединены с первыми входаг и соответствующих элементов И четвертой группы, вторые входы которых соединены с выходами соответ ствующих элементов И первой группы,, разрядные выходы первого регистра последовательного приближения множителя соединены с первыми входами соответствующих элементов И восьмой группы, выход третьего триггера соединен с вторыми входами элементов И шестой и восьмой групп, выходы элементов И второй и восьмой групп соединены с вторыми входами соответствующих элементов ИЛИ первой и второй групп, выходы элементов ИЛИ первой, второй, третьей и четвертой групп соединены соответственно с информационными входами первой, второй, третьей и четвертой групп второго блока суммирования, первый и второй выходы которого соединены соответственно с вторым и третьим выходами результата устройства, входы синхронизации и начальной установки которого соединены соответственно с входами синхронизации и на 4альной установки третьего и четвертого триггеров, вторых регистров последовательного приближения множимого и множи- .теля и второго блока суммирования. 2, Устройство по п. 1 ,. о т л и - чающееся тем, что второй блок суммирования содержит (2п+3) последовательных сумматоров и два элемента задержки, причем первьш и второй информационные входы i-ro последовательного сумматора (i 1,.. ,,,,п) соединены с соответствующими информационными входами первой и второй групп блока, информационные входы третьей и четвертой групп которого соединены соответственно с первым и вторым информационными входами j -го последовательного сумматора (J п+1,..,2п) , первый и второй выходы каждого (2К+1)-го последовательного сумматора (К ,...,n-l) кроме (п+1)-го последовательного сумматора, соединены соответственно с третьим и четвертым информационными входами каждого. (2К-1)-го последова- .тельного сумматора, первый и второй выходы каждого (2п+2)-го последовательного сумматора, кроме (п+2)-го последовательнох-о сумматора, соединены соответственно с третьим и четвертым информационными входами 2К-го последовательного сумматора, третьи

и четвертые входы (n-l)-ro , п-го, (2п-1)-го, 2п-го последовательных сумматоров соединены с входом логи-: ческого нуля устройства,, первый и второй выходы второго и (п+2)-го

последовательных сумматоров соединены соответственно с первыми и вторыми входами первого и второго элементов задержки, первый и второй выходы первого последовател-ьного сумматора

соединены соответственно с первым и вторым информационными входами (2п+1)-го последовательного сумматора, третий и четвертый информационные входы которого соединены соответственно с первым и вторым выходами первого элемента задержки, первьп и второй выходы (п+1)-го последовательного сумматора соединены соответственно с первым и вторым информационными входами (2п+2)-го последовательного сумматора, третий и четвертью информационные входы которого соединены соответственно с первым и вторым выходами второго элемента задержки, первый и второй выходы (2п+1)-го последовательного сумматора соединены соответственно с первым и вторым информационными входами (2п+2)-го последовательного сумматора, третий и

четвертый информационные входы которо- го соединены соответственно с первым и вторым выходами (2п+2)-гопоследовательного сумматора, первый и второй выходы (2п-1-3)-го последовательного сумматора соединены соответственно с первым и вторым выходами блока, входы синхронизации и начальной установки которого соединены соответственно с входами синхронизации и начальной установки всех посл.едов-а- тельных сумматоров и первого и второго элементов задержки.

Таблица

2

оо

п

I Г4 I

2

I

а I

I 2

X

о,

I

о 01- о 0(-Ь- 01- |-(001-0

ah- оооо|- оо - оо - of- - о1-

|w|- о о -(- о -(- о о - - о - - of- § ° 01-1- о о -f- о - о - О - - О

1 V

э - - о о - О|о|о о|-(- о о1-

3 о - ооооо о(- о о о(- о о

- OJ- ООО - ООО

о1- о о о о о - о о - о о 01-о|-о о о .

I- - о о|- о о -

о(- о о о о о о о о

lia

SR о и f

- ej «л . ifi о - (ч - сл - « - ш - чо -

00 0« о о 00 - о, - tsi

OOOt00r Оiri СЧ-

Г4 - .- СУ - - - - rj- -

ЙЯЯЯЯЙЙЯЯЙЯ Я«ЯЯ{ЯЯ 5Й Ч;Ч й;5ЯЙЙ ЙЯ 5 5 5 WWWwRwWWWWWwfiwWwf Rw NWlMWNnWlNfNWflWwWWlMWWWW

- or- - о

о 01-00

.(-о - - о - - о о

о Qf- о о о

- О - - о о|- о о -

I- о - о 0|- J- о о - - 0|-

о о/- о оК- о 01- (-|- - I- о го - - о о -I- о - о о - -

о 01- о 0(-Ь- 01- |-(001-0

h- оооо|- оо - оо - of- - о1-

о1- о о о(- о о|- о - о1- о о -

ООО-. ОО(- ОООг-01- 00

о о - о oj- о - о о о - о о - о о|г-о о -I-о

о о о of- о о о о о о

1-0

OOOt00r Оiri СЧ-

Г4 - .- СУ - - - - rj- -

оН о

о

сэ1- о о о

-1-1- f- о -I(i. о - о

-I-HI- о о о -

I001-14

н

о,

V

о

|«

I и и

I- - 0(о - о -

1-(- о о

о о - I- о -I- о

01- Jо о

а о о п П гл

ИМИ1

| Сумматор в избыточной двоичной системе счисления | 1982 |

|

SU1042011A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Последовательное устройство для умножения | 1987 |

|

SU1444754A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-07—Публикация

1989-02-12—Подача