Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано ,в устройствазс для цифровой обработки сигналов (в частности, изображений), а также в устройствах кодирования, принцип действия которых базируется на теории конечных колец.

Цель изобретения - сокращение аппаратурных затрат.

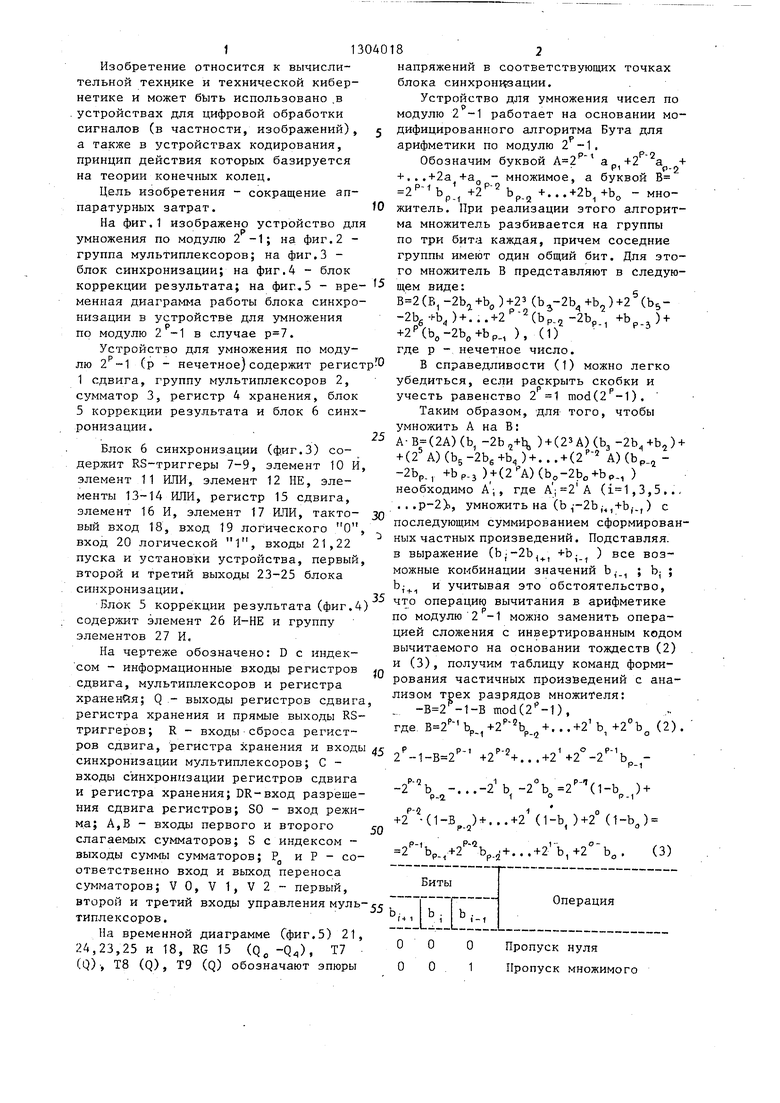

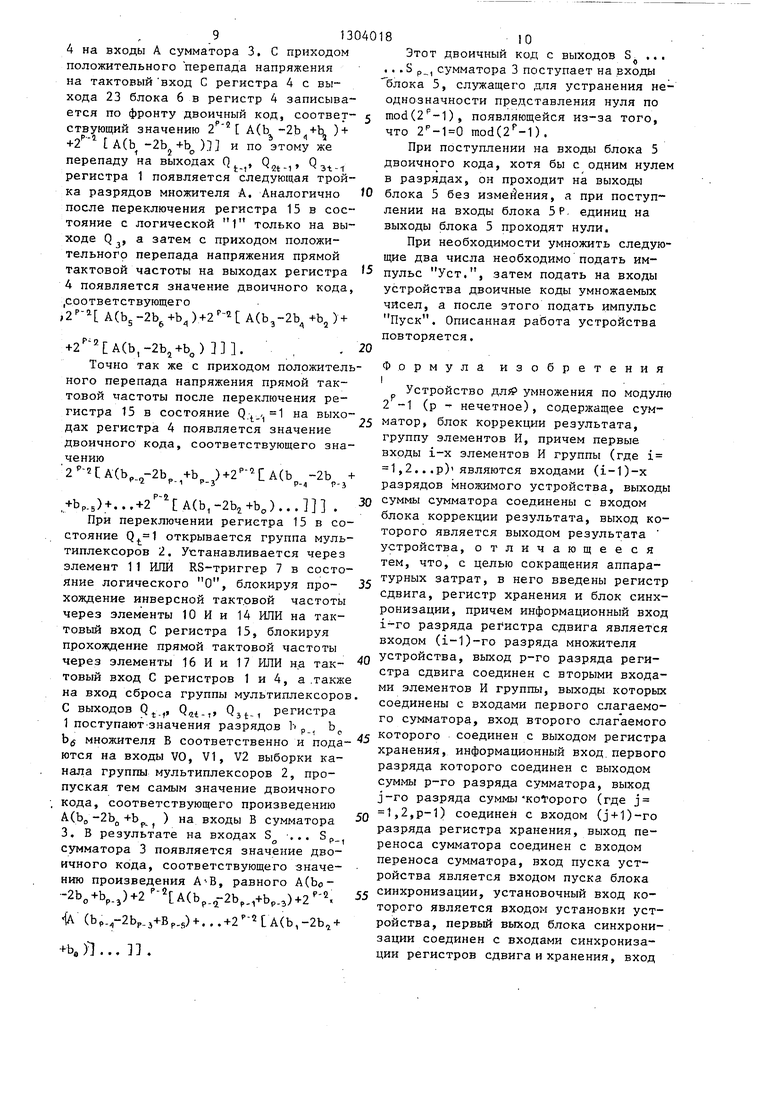

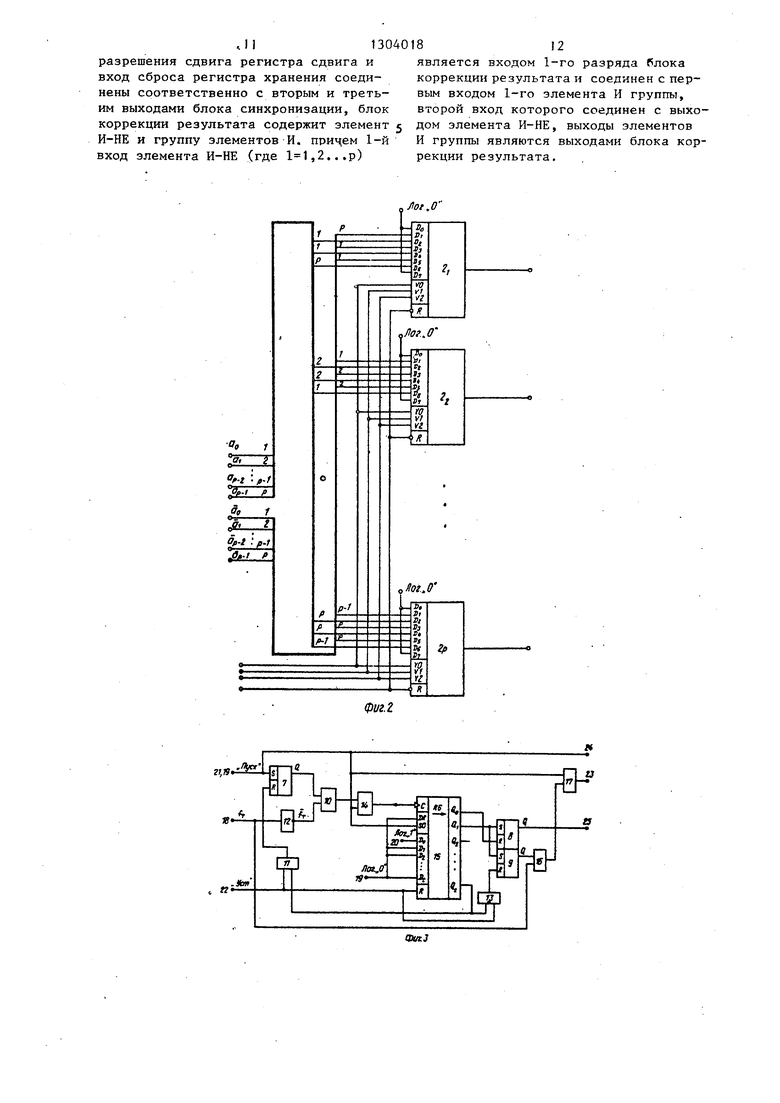

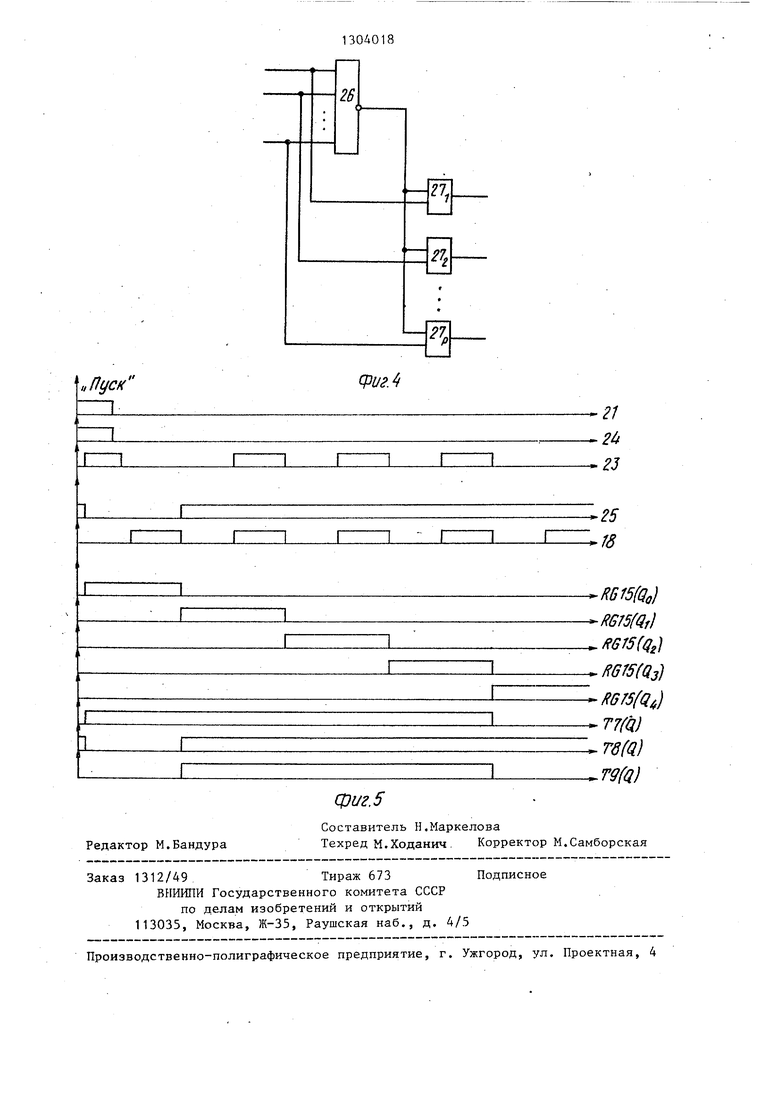

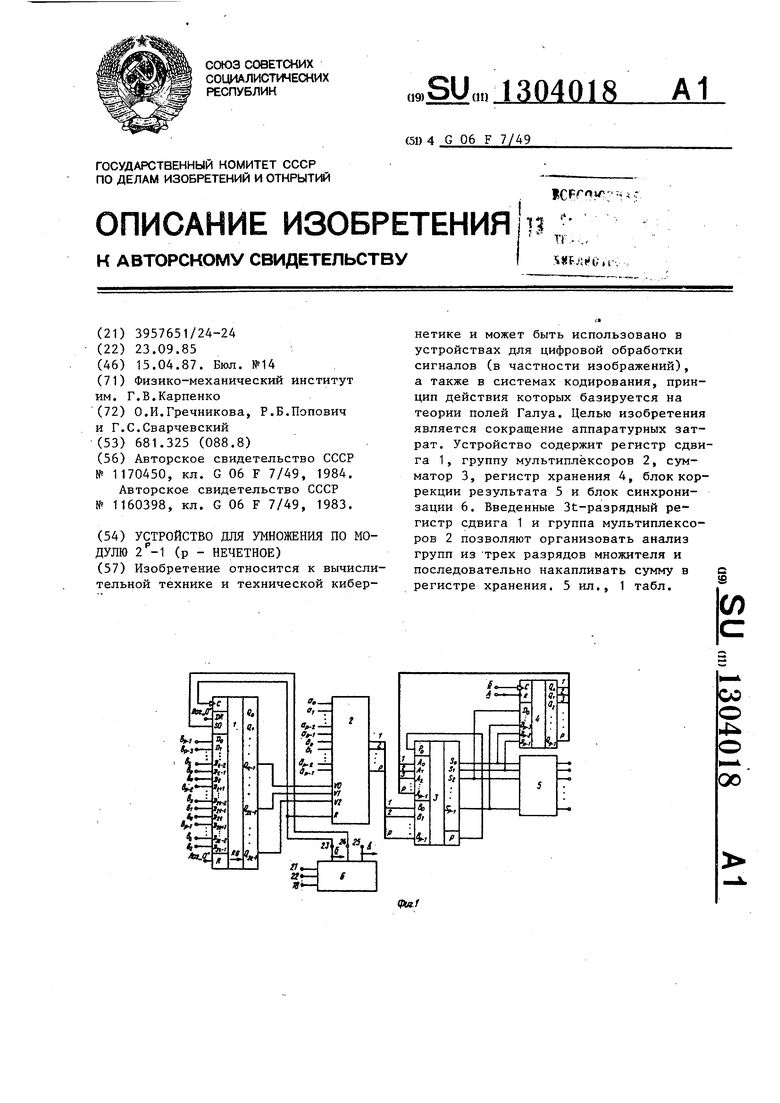

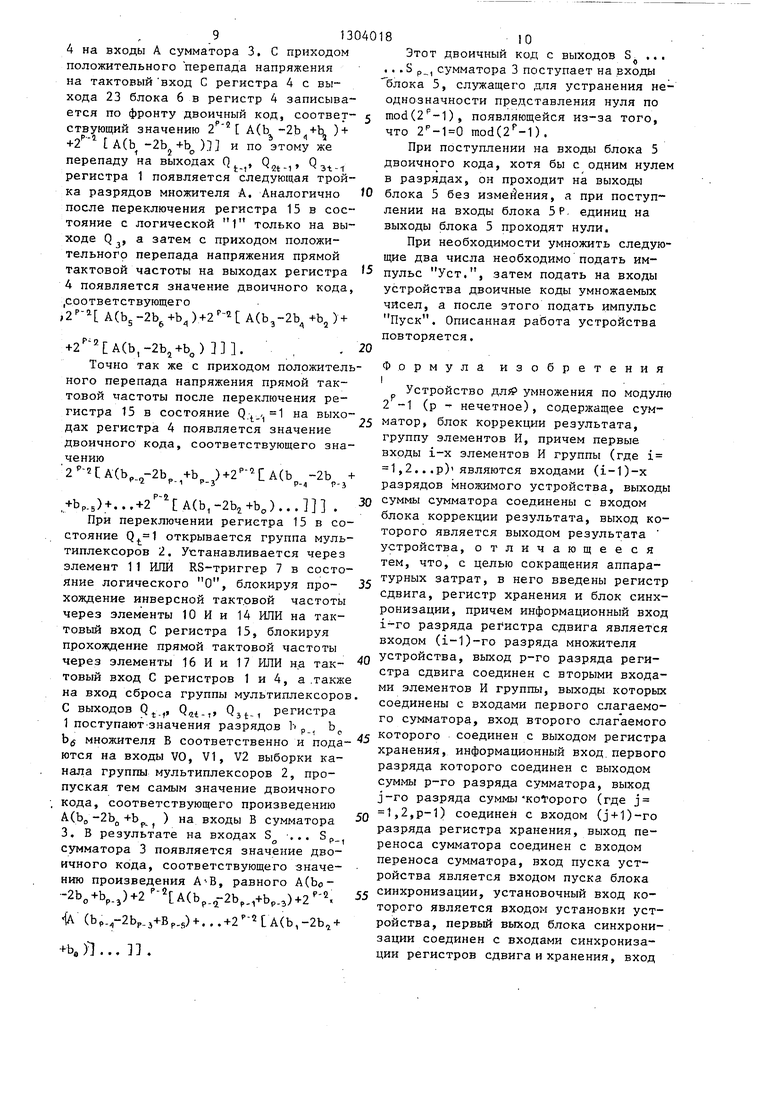

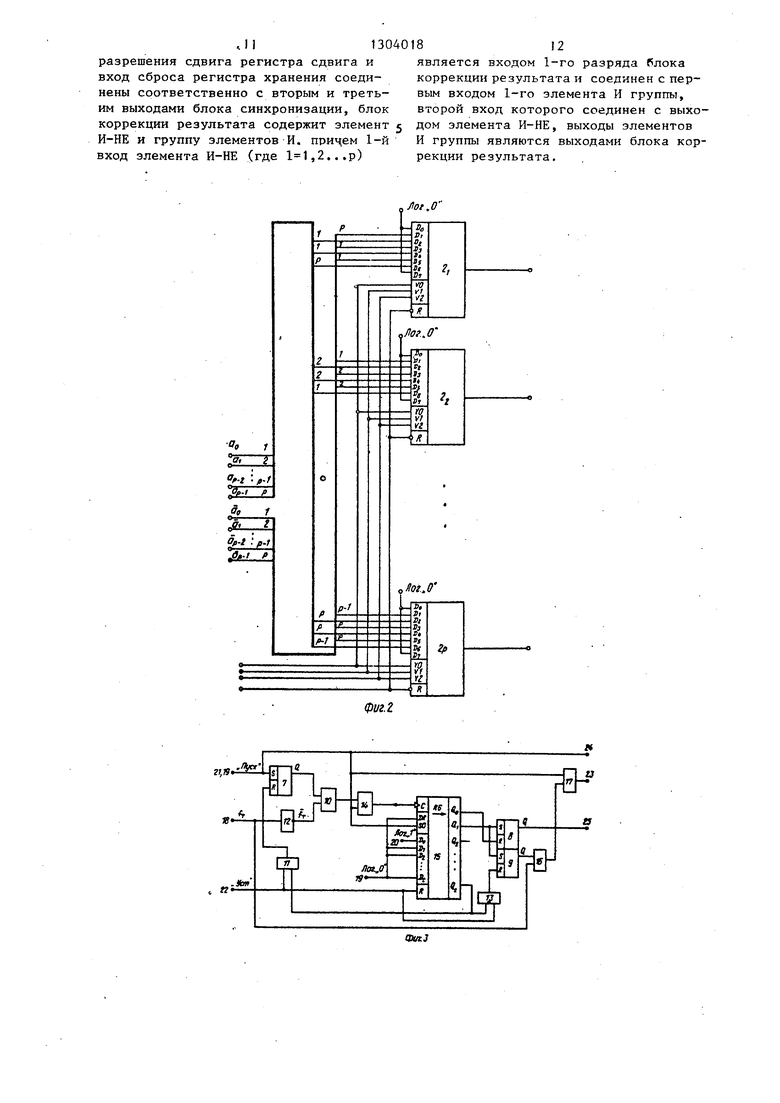

На фиг.1 изображено устройство для

Р

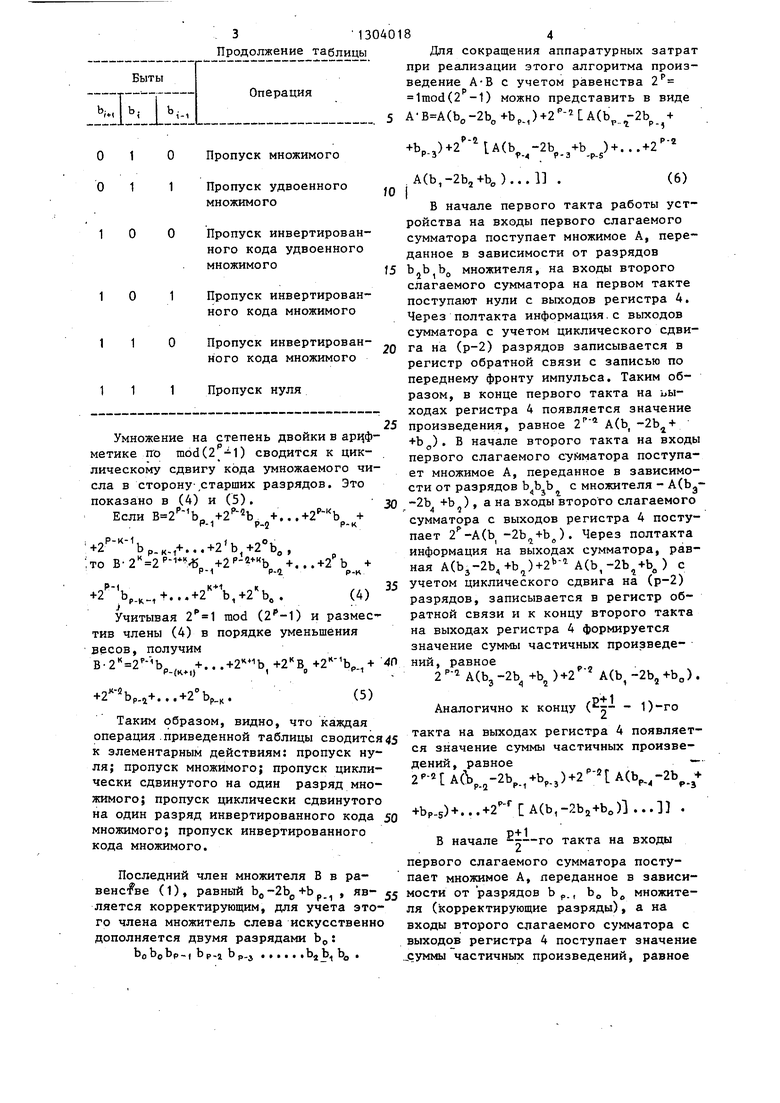

умножения по модулю 2 -1; на фиг.2 - группа мультиплексоров; на фиг.З - блок синхронизации; на фиг.4 - блок

напряжений в соответствующих точках блока синхронр зации.

Устройство для умножения чисел п модулю 2 -1 работает на основании м дифицированного алгоритма Бута для арифметики по модулю 2 -1.

Обозначим буквой а + ...+2а +а - множимое, а буквой В

2

p-i

Ю

bp-t +2

р. 5

Р-2

+ .. .+2Ь +Ь(, - мно

житель. При реализации этого алгори ма множитель разбивается на группы по три бита каждая, причем соседние группы имеют один общий бит. Для эт го множитель В представляют в следу

коррекции результата; на фиг,5 - вре- 5 щем виде:

менная диаграмма работы блока синхро- (В,)+2з(bj-2b +Ь)+2 (Ь -2bg-Hb, ) + . ..H-2 ;(bp.2-2bp.,

Ьр-з)

низации в устройстве для умножения

р

по модулю 2 -1 в случае .

Устройство для умножения по модулю (р - нечетное) содержит регистр О 1 сдвига, группу мультиплексоров 2, сумматор 3, регистр 4 хранения, блок 5 коррекции результата и блок 6 синхронизации.

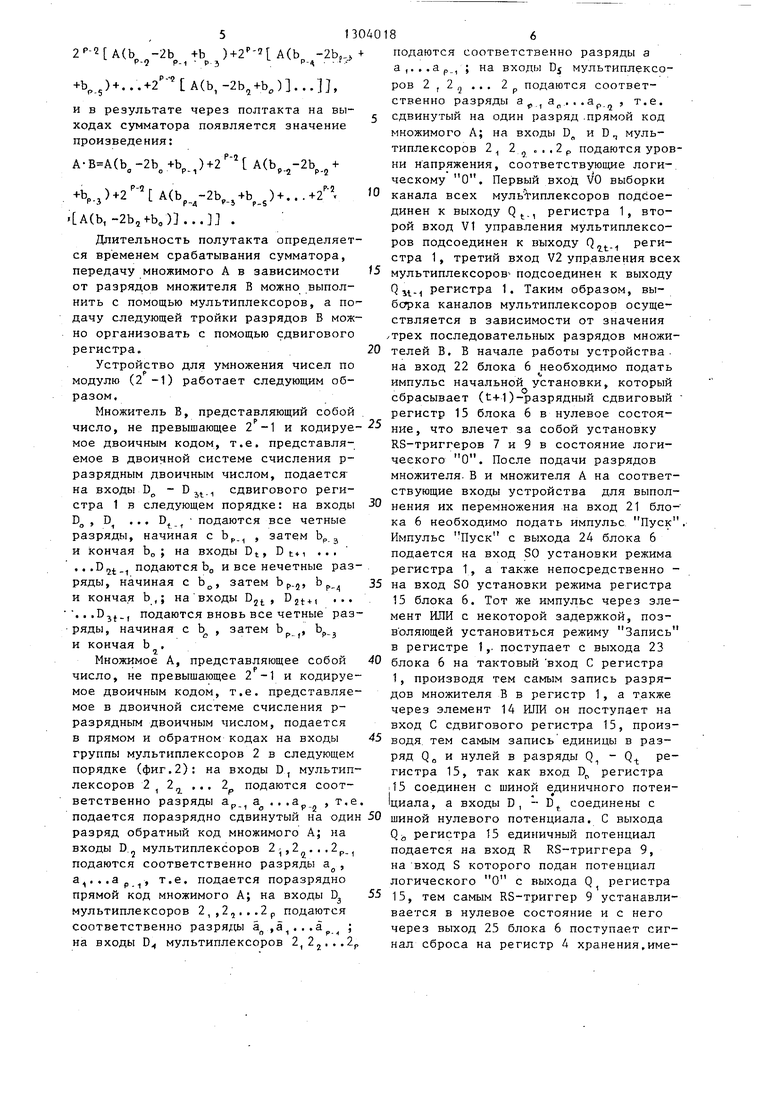

Блок 6 синхронизации (фиг.З) содержит RS-триггеры 7-9, элемент 10 И элемент 11 ИЛИ, элемент 12 НЕ, элементы 13-14 ИЛИ, регистр 15 сдвига, элемент 16 И, элемент 17 ИЛИ, тактовый вход 18, вход 19 логического О вход 20 логической 1, входы 21,22 пуска и установки устройства, первый второй и третий выходы 23-25 блока синхронизации.

Блок 5 коррекции результата (фиг.4 содержит элемент 26 И-НЕ и группу элементов 27 И.

На чертеже обозначено: D с индек- сом - информационные входы регистров сдвига, мультиплексоров и регистра хранения; Q .- выходы регистров сдвига регистра хранения и прямые выходы RS- триггеров; R - входы - сброса регистров сдвига, регистра хранения и входы синхронизации мультиплексоров; С - входы синхронизации регистров сдвига и регистра хранения; DR-вход разрешения сдвига регистров; SO - вход режима; А,В - входы первого и второго

слагаемых сумматоров; S с индексом - выходы суммы сумматоров; Р и Р - соответственно вход и выход переноса сумматоров; V О, V 1, V 2 - первый, второй и третий входы управления муль типлексоров.

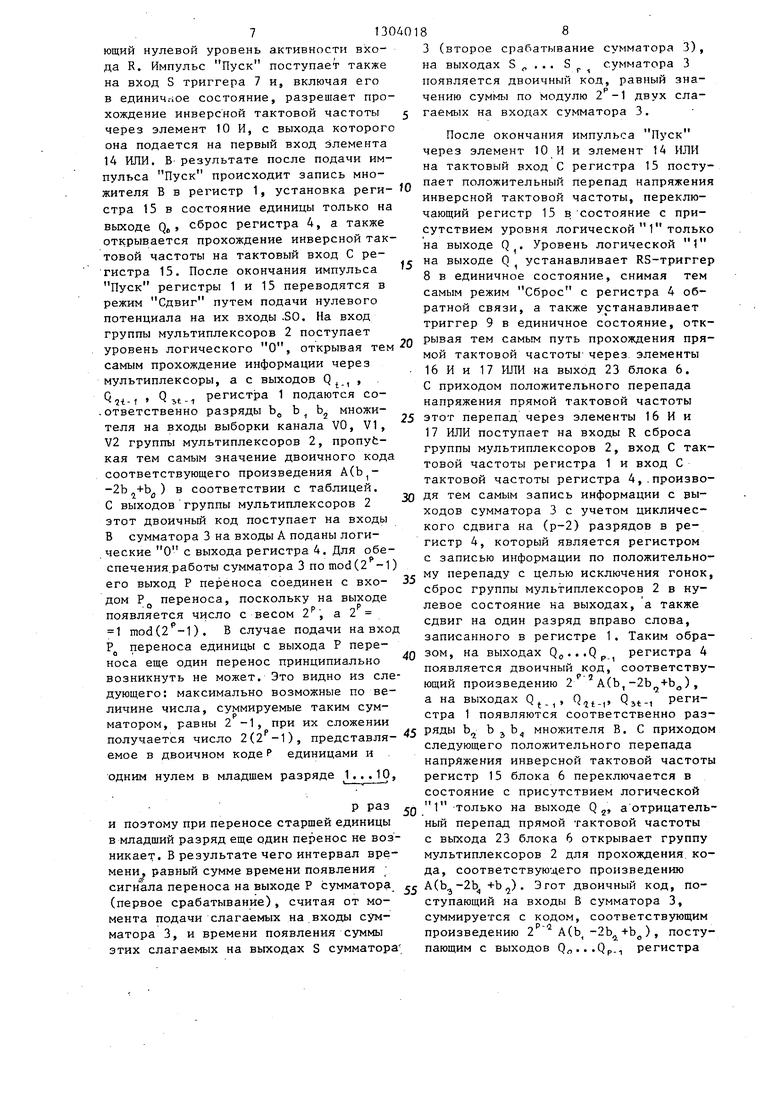

На временной диаграмме ( фиг.5) 21 24,23,25 и 18, RG 15 (Q -Q), Т7 (Q) , Т8 (Q), Т9 (Q) обозначают эпюры

напряжений в соответствующих точках блока синхронр зации.

Устройство для умножения чисел по модулю 2 -1 работает на основании модифицированного алгоритма Бута для арифметики по модулю 2 -1.

Обозначим буквой а + + ...+2а +а - множимое, а буквой В

2

p-i

bp-t +2

р. 5

Р-2

+ .. .+2Ь +Ь(, - множитель. При реализации этого алгоритма множитель разбивается на группы по три бита каждая, причем соседние группы имеют один общий бит. Для этого множитель В представляют в следуюВ 2(В,)+2з(bj-2b +Ь)+2 (

-2bg-Hb, ) + . ..H-2 ;(bp.2-2bp.,

Ьр-з)

+2 (b,-2b,+bp., ), (1) где р - нечетное число.

В справедливости (1) можно легко убедиться, если раскрыть скобки и учесть равенство 2 1 inod(2-1).

Таким образом, для того, чтобы умножить А на В:

А-В(2А)(Ц ) + (23А)(Ьз-2Ь,+Ь5) + + (2 A)(b,-2b,+b, ) + ... + (2 А)(Ьр., р-а

2Ьр., +Ьр.з ) + ()(., ) необходимо А ;, где А ; 2 А (,3,5.., . , .p-2)i, умножить на (Ъ ,-2b,-4,+b,.., ) с последующим суммированием сформированных частных произведений. Подставляя. в выражение (b;-2b, -i возможные комбинации значений Ь,-., ; bj ; i+ и учитывая это обстоятельство,

что операцию вычитания в арифметике по модулю 2 -1 можно заменить операцией сложения с инвертированным кодом вычитаемого на основании тождеств (2) . и (3), получим таблицу команд формирования частичных произведений с анализом трех разрядов множителя:

-1-В mod(), где В 2 - Ьр,+2 - Ьр,+...+2Ч

+2°Ъ (2).

....н-2Ч2°-2 - ь,.-...-2

Р-2

-2°Ь: 2 - 1-Ь.,).

+2 (1-В)-(-...+2 (1-Ь, )+2 (1-bJ

1

1

О

Пропуск множимого

Пропуск удвоенного множимого

Пропуск инвертированного кода удвоенного множимого

о

1

1

Пропуск инвертированного кода множимого

Пропуск инвертированного кода множимого

Пропуск нуля

Умножение на степень двойки в арцф- метике по mod(2 1) сводится к циклическому сдвигу кода умножаемого числа в сторону,старших разрядов. Это показано в (4) и (5).

Если В 2 Ь„ +. ..+2 Ь +

Р-1 р-2 Р-к

+2 bp.«.,+ ...+2 b +2 Ь„,

:то В-2 2 - 6 н-2Р- Ь +...+2Ч «Р 1Р-1Р-К

2 Ч-к-1+- +2 ь,+2Ч, . (4)

Учитывая 2 1 mod (2-1) и размес- тив члены (4) в порядке уменьшения весов, получим В-2 2 - Ьр + .. .,+2 В +2

Ьр.,+

+2 bp.,+...,

р-к

Таким образом, видно, что каждая операция.приведенной таблицы сводится45 к элементарным действиям: пропуск нуля; пропуск множимого; пропуск циклически сдвинутого на один разряд множимого; пропуск циклически сдвинутого на один разряд инвертированного кода 50 множимого; пропуск инвертированного кода множимого.

Последний член множителя В в равенстве (1), равный Ьо-2Ьд+Ьр , яв- 55 ляется корректирующим, для учета этого члена множитель слева искусственно дополняется двумя разрядами Ьр

Ь„Ь

о о

Ьр-( bp-i Ьр.дbjb Ъд .

при реализации этого алгоритма произведение А-В с учетом равенства 2 1mod(2 -1) можно представить в виде

5 (Ь„-2Ь„+Ь,.,)(Ь -2Ь

,Р-г

+Ь,.,)-ь2 U(b.-2b.+b,J + ...2 . А(Ь,-2Ь,,+Ь„ ),.. .

р-2

(6)

f5

20

25

30

35

4f

45 50

В начале первого такта работы устройства на входы первого слагаемого сумматора поступает множимое А, переданное в зависимости от разрядов b, множителя, на входы второго слагаемого сумматора на первом такте поступают нули с выходов регистра 4. Через полтакта информация.с выходов сумматора с учетом циклического сдвига на (р-2) разрядов записывается в регистр обратной связи с записью по переднему фронту импульса. Таким образом, в конце первого такта на ьы- ходах регистра 4 появляется значение произведения, равное 2 А(Ь, -2Ь + +Ь). В начале второго такта на входы первого слагаемого суйматора поступает множимое А, переданное в зависимости от разрядов с множителя - -2Ъ +Ь ), а на входы второго слагаемого сумматора с выходов регистра 4 поступает 2 -А(Ь ). Через полтакта информация на выходах сумматора, равная А(Ь-2Ь,+Ь)+2 A(b,) с учетом циклического сдвига на (р-2) разрядов, записывается в регистр обратной связи и к концу второго такта на выходах регистра 4 формируется значение суммы частичных произведений, равное

2 - А(ЬЗ -2Ь +Ь ) А(Ь, -2Ь, +Ь„) .

Аналогично к концу ( п 1)

го

такта на выходах регистра 4 появляется значение суммы частичных произведений, равное- 2-П А(-2Ь,.,-.Ь,.,)2 -П A(bp.-2b.+

+bp.5) + ...+2 A(b,-2bj+bjl ... .

p+l В начале ---го такта на входы

первого слагаемого сумматора поступает множимое А, переданное в зависимости от разрядов Ьр., bo b множителя (корректирующие разряды), а на входы второго слагаемого сумматора с выходов регистра 4 поступает значение ,суммы частичных произведений, равное

2 -2 A(b -2b +b )+2 -4A(b -Zb,,, +

P-9 p-1 - р-з - P- - - f.--

+b p-. .. A(b, -2b,+bJ ...,

и в результате через полтакта на выходах сумматора появляется значение произведения:

(Ь„ -2Ь„ -ьЬр.,)+2 A(b.-2bp. +

. +b.,) A(, + ...+2 - . О

A(b, -2b,fbo )... .

Длительность полутакта определяется временем срабатывания сумматора, передачу множимого А в зависимости 5 от разрядов множителя В можно выполнить с помощью мультиплексоров, а по дачу следующей тройки разрядов В можно организовать с помощью сдвигового регистра.20

Устройство для умножения чисел по модулю (2 -1) работает следующим образом.

Множитель В, представляющий собой число, не превышающее 2- и кодируе- 5 мое двоичным кодом, т.е. представляемое в двоичной системе счисления р- разрядным двоичным числом, подается- на входы D - Dj., сдвигового регистра 1 в следующем порядке: на входы 30

13040186

подаются соответственно разряды а а,..,ар, ; на входы 05 мультиплексоров 2 , 2 ,j ... 2 р подаются соответственно разряды а,а...ар, т.е. сдвинутый на один разряд .прямой код множимого А; на входы D и D мультиплексоров 2 2 .,.2р подаются уровни напряжения, соответствующие логическому О. Первый вход VO выборки канала всех муль типлексоров подсоединен к выходу Q,, регистра 1, второй вход VI управления мультиплексоров подсоединен к выходу Q

Zt-1

регистра 1, третий вход V2 управления всех мультиплексоров- подсоединен к выходу Qit-1 регистра 1. Таким образом, выборка каналов мультиплексоров осуществляется в зависимости от значения трех последовательных разрядов множителей В. В начале работы устройства, на вход 22 блока 6 необходимо подать импульс начальной установки, который сбрасывает (t-H )-разрядный сдвиговый регистр 15 блока 6 в нулевое состояние, что влечет за собой установку RS-триггеров 7 и 9 в состояние логического О. После подачи разрядов множителя. В и множителя А на соответствующие входы устройства для выполнения их перемножения на вход 21 бло ка 6 необходимо подать импульс Пуск, Импульс Пуск с выхода 24 блока 6 подается на вход SO установки режима регистра 1, а также непосредственно - на вход SO установки режима регистра 15 блока 6. Тот же импульс через зле- мент ИЛИ с некоторой задержкой, поз- в оляющей установиться режиму Запись в регистре 1,. поступает с выхода 23 блока 6 на тактовый вход С регистра 1, производя тем самым запись разрядов множителя В в регистр 1, а также через элемент 14 ШШ он поступает на вход С сдвигового регистра 15, производя, тем самым запись единицы в разряд QO и нулей в разряды Q, - Q регистра 15, так как вход D регистра 15 соединен с шиной единичного потенциала, а входы D, - D соединены с шиной нулевого потенциала. С выхода Q регистра 15 единичный потенциал подается на вход R RS-триггера 9, на ВХОД S которого подан потенциал логического О с выхода Q регистра 15, тем самым RS-триггер 9 устанавливается в нулевое состояние и с него через выход 25 блов:а 6 поступает сигнал сброса на регистр 4 хранения,имеС„. D

D подаются все четные

разряды, начиная с Ьр, , затем Ьр и кончая bo ; на входы D, D подаются bo и все нечетные разряды, начиная с Ь, затем Ьр.,, b р и кончая Ь,; на входы Djj. , Djt + i ...D.JJ, подаются вновь все четные разряды, начиная с Ь , затем Ьр , Ь

и кончая b ,

1 Множимое А, представляющее собой

число, не превышающее 2 -1 и кодируемое двоичным кодом, т.е. представляемое в двоичной системе счисления р- разрядным двоичным числом, подается в прямом и обратном кодах на входы группы мультиплексоров 2 в следующем порядке (фиг.2): на входы D, мультиплексоров 2 2 ... 2 подаются соответственно разряды ар а . . .ар , т.е подается поразрядно сдвинутый на один разряд обратный код множимого А; на входы D. мультиплексоров 2-,2...2р подаются соответственно разряды а, а...ар , т.е. подается поразрядно прямой код множимого А; на входы D мультиплексоров 2,,2,...2р подаются соответственно разряды а,а,.,а ; на входы D мультиплексоров 2 2,.,2

ров подсоединен к выходу Q

Zt-1

регистра 1, третий вход V2 управления всех мультиплексоров- подсоединен к выходу Qit-1 регистра 1. Таким образом, выборка каналов мультиплексоров осуществляется в зависимости от значения трех последовательных разрядов множителей В. В начале работы устройства, на вход 22 блока 6 необходимо подать импульс начальной установки, который сбрасывает (t-H )-разрядный сдвиговый регистр 15 блока 6 в нулевое состояние, что влечет за собой установку RS-триггеров 7 и 9 в состояние логического О. После подачи разрядов множителя. В и множителя А на соответствующие входы устройства для выполнения их перемножения на вход 21 блока 6 необходимо подать импульс Пуск Импульс Пуск с выхода 24 блока 6 подается на вход SO установки режима регистра 1, а также непосредственно - на вход SO установки режима регистра 15 блока 6. Тот же импульс через зле- мент ИЛИ с некоторой задержкой, поз- в оляющей установиться режиму Запись в регистре 1,. поступает с выхода 23 блока 6 на тактовый вход С регистра 1, производя тем самым запись разрядов множителя В в регистр 1, а также через элемент 14 ШШ он поступает на вход С сдвигового регистра 15, производя, тем самым запись единицы в разряд QO и нулей в разряды Q, - Q регистра 15, так как вход D регистра 15 соединен с шиной единичного потенциала, а входы D, - D соединены с шиной нулевого потенциала. С выхода Q регистра 15 единичный потенциал подается на вход R RS-триггера 9, на ВХОД S которого подан потенциал логического О с выхода Q регистра 15, тем самым RS-триггер 9 устанавливается в нулевое состояние и с него через выход 25 блов:а 6 поступает сигнал сброса на регистр 4 хранения,име713040188

ющий нулевой уровень активности вхо- 3 (второе срабатывание сумматора 3), да R. Импульс Пуск поступает также на выходах S ... S сумматора 3 на вход S триггера 7 и, включая его появляется двоичный код, равный зна- в единичное состояние, разрешает про- чению суммы по модулю двух сла- хождение инверсной тактовой частоты 5 гаемых на входах сумматора 3.

через элемент 10 И, с выхода которого „,. „

После окончания импульса Пуск

она подается на первый вход элемента-,л ,,., ,,„,,

„.через элемент 10 И и элемент 14 ИЛИ

14 ИЛИ. В результате после подачи им-„

,.„ .,на тактовый вход С регистра 15 поступульса Пуск происходит запись мно- „,4л пает положительный перепад напряжения

жителя В в регистр 1, установка реги- и „

инверсной тактовой частоты, переклю- стра 15 в состояние единицы только на „ в состояние с привыходе Q., сброс регистра 4, а такжесутствием уровня логической 1 только открывается прохождение инверсной так- . Уровень логической 1

ТОБОЙ частоты на тактовый вход С ре- , устанавливает RS-триггер

гистра 15. После окончания импульсаg единичное состояние, снимая тем Пуск регистры 1 и 15 переводятся в„ „

„ „самым режим Сброс с регистра 4 об- режим Сдвиг путем подачи нулевого

„„ „ратной связи, а также устанавливает

потенциала на их входы .50. На вход„

триггер 9 в единичное состояние, отк- группы мультиплексоров 2 поступает

,,,, 7п рывая тем самым путь прохождения пря- уровень логического О , открывая тем „ „

-мои тактовой частоты через элементы самым прохождение информации черезла ,, ,-, т.mi т,

., -16 Ни 17 ИЛИ на выход 23 блока 6. мультиплексоры, а с выходов Q , , , ,,

„. . t-1 с приходом положительного перепада

QOJ , . Q . , регистра 1 подаются со- н,i. м

t-f jt-i t-напряжения прямой тактовой частоты

.ответственно разряды Ь., Ъ, Ь„ множи- .,,-,,

° 2 25 этот перепад через элементы 16 И и

теля на входы выборки канала VU, VI, ,.. „,„

,,„о ,. ИЛИ поступает на входы R сброса

V2 группы мультиплексоров 2, nponyt-7

группы мультиплексоров 2, вход С таккая тем самым значение двоичного кода „. ,,

. ,, товои частоты регистра 1 и вход С соответствующего произведения А(.Ь -„.

„. , .- 1 тактовой частоты регистра 4,.произво-2Ь„+Ь, ) в соответствии с таблицей., г

.п ЗП Дя тем самым запись информации с выС выходов группы мультиплексоров 2

ходов сумматора 3 с учетом цикличесэтот двоичньш код поступает на входы- „,.

,о лкого сдвига на (р-2) разрядов в реВ сумматора 3 на входы А поданы логи-, „

....../ гт с гистр 4, который является регистром

ческие О с выхода регистра 4. Для обе-,,.„. с записью информации по положительно- спечения работы сумматора J по modi,/ -1;

„ .эе му перепаду с целью исключения гонок,

его выход Р переноса соединен с вхо- -s- .„

сброс группы мультиплексоров 2 в ну- дом Р переноса, поскольку на выходе

о „р. „Р левое состояние на выходах, а также появляется число с весом I , а 2.

,,„р ,. „сдвиг на один разряд вправо слова,

1 mod(2 -1). В случае подачи на вход, „, 1

I/. J « записанного в регистре 1. Таким обра- Р переноса единицы с выхода Р перео 4П зом, на выходах 0.,...0 регистра 4

носа еще один перенос принципиально - - о - р., - .появляется двоичный код, соответствувозникнуть не может. Это видно из еле- „-.Р-З ./, , %

ющии произведению 2 A(b,-2b +Ь„),

дующего: максимально возможные по ве-„ „ 1

а на выходах О. , О,, ., Q , реги- личине числа, суммируемые таким сум- , t-i at-c

„Р .стра 1 появляются соответственно разматором, равны 2 -1 , при их сложении ,. t. ,. „

„/Др ,ч4S ряды Ь b , b. множителя В. С приходом

получается число 2(2 -1), представля- « -z з

-следующего положительного перепада емое в двоичном коде Р единицами и„ ±- «

напряжения инверсной тактовой частоты

одним нулем в младшем разряде J .. . 1 j, регистр 15 блока 6 переключается в

состояние с присутствием логической Р 0 1 только на выходе Qg, аотрицательи поэтому при переносе старшей единицы ный перепад прямой тактовой частоты в младший разряд еще один перенос не воз- с выхода 23 блока 6 открывает группу никает. В результате чего интервал вре- мультиплексоров 2 для прохождения, ко- мени, равный сумме времени появления ; да, соответствую-дего произведению сигнала переноса на выходе Р сумматора A(, +b 5) . Этот двоичный код, по- (первое срабатывание), считая от мо- ступающий на входы В сумматора 3, мента подачи слагаемых на входы сум- суммируется с кодом, соответствующим матора 3, и времени появления суммы произведению 2 А(Ь, -2b,j,+b), посту- этих слагаемых на выходах S сумматора пающим с выходов Од...рр.., регистра

913

4 на входы А сумматора 3. С приходом положительного перепада напряжения на тактовый вход С регистра 4 с выхода 23 блока 6 в регистр 4 записывается по фронту двоичный код, соответ- ствующий значению 2 А(Ь , ) +

по этому же

QO.-, Q

+2

tA(b -2bj+bJ и

перепаду на выходах Q, X2t-i 3t-i регистра 1 появляется следующая тройка разрядов множителя А. Аналогично после переключения регистра 15 в состояние с логической 1 только на выходе Q ,, а затем с приходом положительного перепада напряжения прямой тактовой частоты на выходах регистра 4 появляется значение двоичного кода .соответствующего ,2 -Ч А(Ь5-2Ь +Ь,)+2 -ЧА(Ьз-2Ь +Ь,,) +

(Ь,-2Ь,-ьЬ„). , .

Точно так же с приходом положительного перепада напряжения прямой тактовой частоты после переключения регистра 15 в состояние Q..-, 1 на выходах регистра 4 появляется значение двоичного кода, соответствующего значению 2 -4A(b,.-2b.,-Hb p-f2 -4A(b .-2b +

р-г

Р-4

Р-3

+Ъ,., + ...+2 С А(Ь,-2Ь,,+Ь„).., ,

При переключении регистра 15 в состояние Q. 1 открывается группа мультиплексоров 2, Устанавливается через элемент 11 ИЛИ RS-триггер 7 в состояние логического О, блокируя прохождение инверсной тактовой частоты через элементы 10 И и 14 ИЛИ на тактовый вход С регистра 15, блокируя прохождение прямой тактовой частоты через элементы 16 И и 17 ИЛИ на тактовый вход С регистров 1 и 4, а .также на вход сброса группы мультиплексоров С выходов Q.,, Q,jt.,, Qjt-, регистра 1 поступают-значения разрядов 1 р , Ь b(j множителя В соответственно и подаются на входы VO, VI, V2 выборки канала группы мультиплексоров 2, пропуская тем самым значение двоичного кода, соответствующего произведению А(ЬО-2Ьд+Ьр ) на входы В сумматора 3. В результате на входах S ,.. Зр сумматора 3 появляется значение двоичного кода, соответствующего значению произведения , равного А(bo- -2b„- b,.)- 2 -ЧA(bp.,-2b,.,-bp.з)2-.

lA (bp.,-2bp 34-Bp,s)-,..H-2 -4A(b,-2b,+ +ЧЯ,.. .

10 Этот двоичный код с выходов S,

. . .S

р, сумматора 3 поступает на входы блока 5, служащего для устранения неоднозначности представления нуля по mod(2-1), появляющейся из-за того, что 2 -1 0 mod().

При поступлении на входы блока 5 двоичного кода, хотя бы с одним нулем в разрядах, он проходит на выходы

блока 5 без измейения, а при поступлении на входы блока 5 Р. единиц на выходы блока 5 проходят нули.

При необходимости умножить следующие два числа необходимо подать импульс Уст,, затем подать на входы устройства двоичные коды умножаемых Чисел, а после этого подать импульс Пуск. Описанная работа устройства повторяется.

Формула изобретения I

Устройство ДЛ5Р умножения по модулю

2-1 (р - нечетное), содержащее сум- матор, блок коррекции результата, группу элементов И, причем первые входы i-x элементов И группы (где i 1,2.,.р) являются входами (i-l)-x разрядов множимого устройства, выходы суммы сумматора соединены с входом блока коррекции результата, выход которого является выходом результата устройства, отличающееся

турных затрат, в него введены регистр сдвига, регистр хранения и блок синхронизации, причем информационный вход i-ro разряда регистра сдвига является входом (i-l)-ro разряда множителя устройства, выход р-го разряда регистра сдвига соединен с вторыми входами элементов И группы, выходы которых соединены с входами первого слагаемого сумматора, вход второго слагаемого

которого соединен с выходом регистра хранения, информационный вход.первого разряда которого соединен с выходом суммы р-го разряда сумматора, выход j-ro разряда суммы которого (где j

1,2,р-1) соединен с входом (j+1)-ro разряда регистра хранения, выход переноса сумматора соединен с входом переноса сумматора, вход пуска устройства является входом пуска блока

синхронизации, установочный вход которого является входом установки устройства, первый выход блока синхронизации соединен с входами синхронизации регистров сдвига и хранения, вход

разрешения сдвига регистра сдвига и вход сброса регистра хранения соединены соответственно с вторым и третьим выходами блока синхронизации, блок коррекции результата содержит элемент 5 И-НЕ и группу элементов И. примем 1-й вход элемента И-НЕ (где ,2...р)

является входом 1-го разряда блока коррекции результата и соединен с первым входом 1-го элемента И группь, второй вход которого соединен с выходом элемента И-НЕ, выходы элементов И группы являются выходами блока коррекции результата.

,Пуск

фиг.5

Редактор М.Бандура

Составитель Н.Маркелова

Техред М.Ходанич. Корректор М.Самборская

Заказ 1312/49Тираж 673 Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

игЛ

--21 2

-25 18

RG15(Qo} (Qi

К6Г5(из K6r5( Г7(Ц)

те (и)

Т9(а)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Устройство для умножения чисел по произвольному модулю | 2020 |

|

RU2755734C1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для умножения | 1984 |

|

SU1185328A1 |

| УМНОЖИТЕЛЬ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2839987C1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в устройствах для цифровой обработки сигналов (в частности изображений), а также в системах кодирования, принцип действия которых базируется на теории полей Галуа. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит регистр сдвига 1, группу мультиплексоров 2, сумматор 3, регистр хранения 4, блок коррекции результата 5 и блок синхронизации 6. Введенные Зt-paзpядный регистр сдвига 1 и группа мультиплексоров 2 позволяют организовать анализ групп из трех разрядов множителя и последовательно накапливать сумму в регистре хранения. 5 ил., 1 табл. СЛ

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для умножения чисел (его варианты) | 1983 |

|

SU1160398A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-15—Публикация

1985-09-23—Подача