У1

О9

ю i

4

СригЛ

Изобретение относится .к вычислительной технике и может найти применение в измерительных устройствах систем автоматического управления и связи. ,

Цель изобретения - повьшение быстродействия .

Устройство реализует разностные уравнения фильтров 2-го порядка, в том числе полосового (ПФ), фильтра нижних частот (ФНЧ) и фильтра верхних частот (ФВЧ):

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

Изобретение относится к вычислительной технике и может быть использовано в измерительных устройствах систем автоматического управления и связи. Цель изобретения - повьшение быстродействия. Поставленная цель достигается за счет того, что про-, .граммируемый цифровой фильтр содержит регистры 1, 2, сумматор 3, мультиплексор 4, сумматор 5, регистр 6, мультиплексоры 7, 8, 9, сумматор 10, триггер 11, регистр 12, дешифратор 13, регистр константы 14, сдвиговые регистры 15, 16, регистры 17, 18,- блоки умножения 19, 20, блоки элементов НЕ 21, 22, сумматор 23, блок синхронизации 24. 4 ил. (Л

У,(х; + 2х,. + х,.,) Ау (х; - 2х,-,, + х,-.2 ) 2- +

,-С

( + 0. - X f.j) 2 + Ay, + Ву.. для ПФ,

где X., у. - текущие значения входного и выходного сиг- налов;

f-1 1-4 - предшествующие значе- у, У,-.1 ния переменных;

А, В - весовые коэффициенты} .С - константа масштабиро- вания.

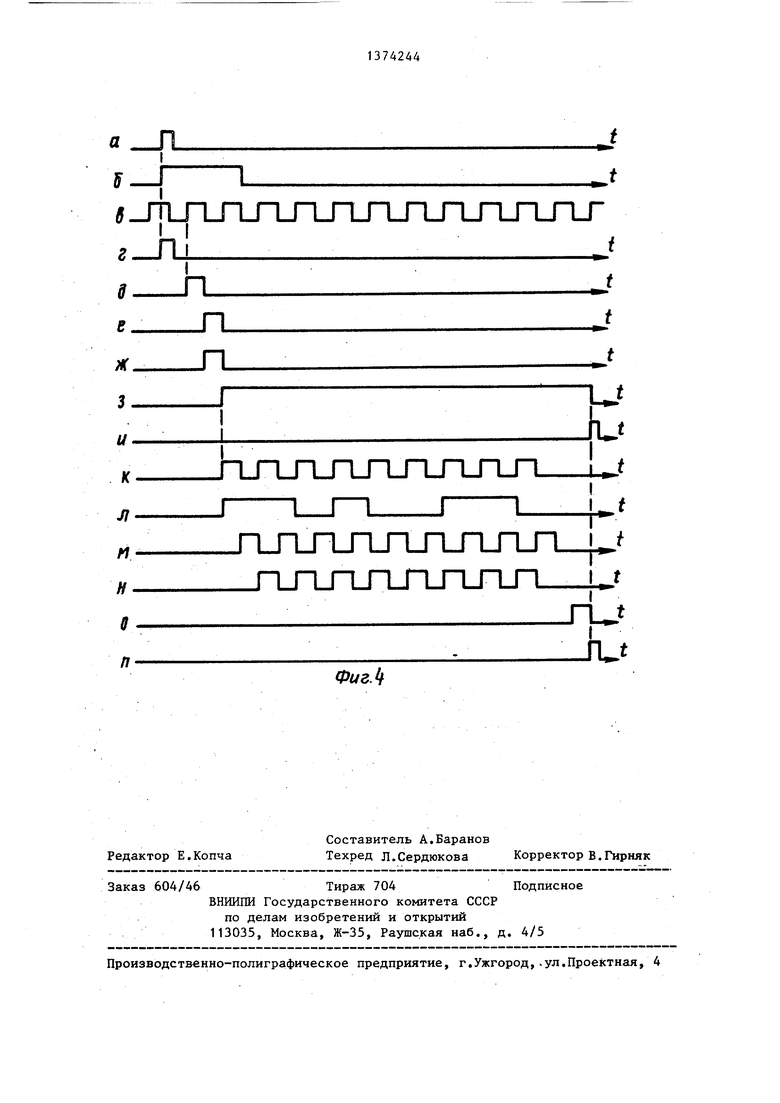

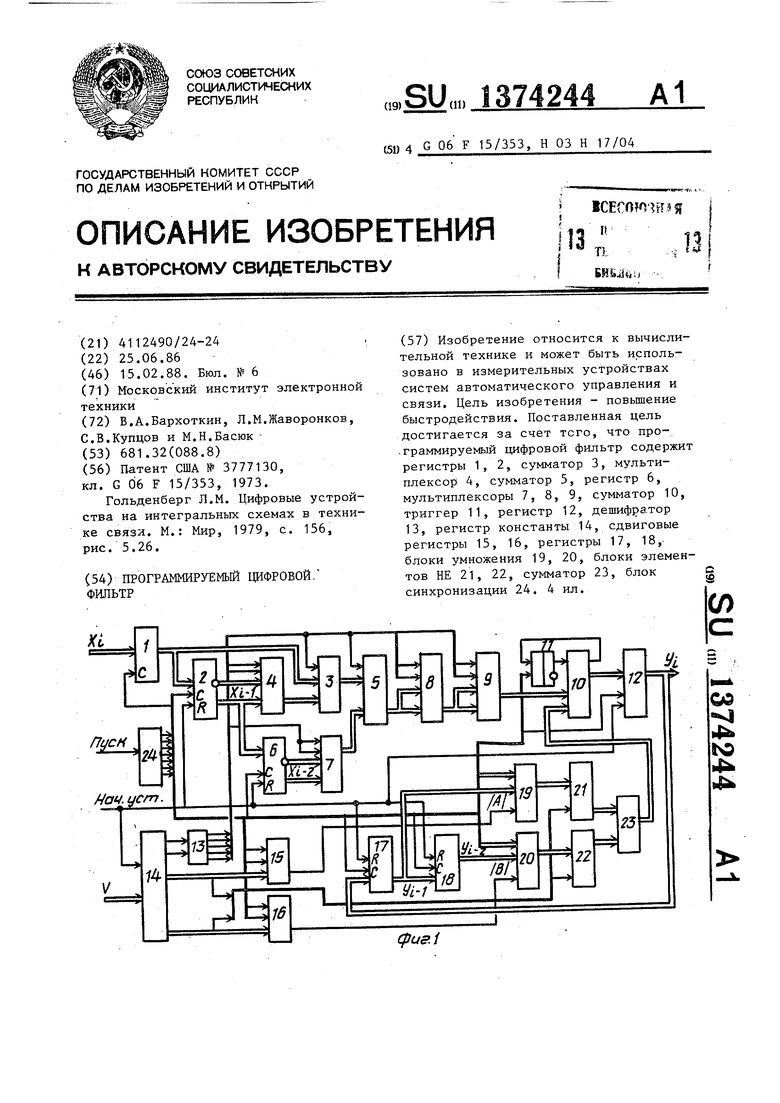

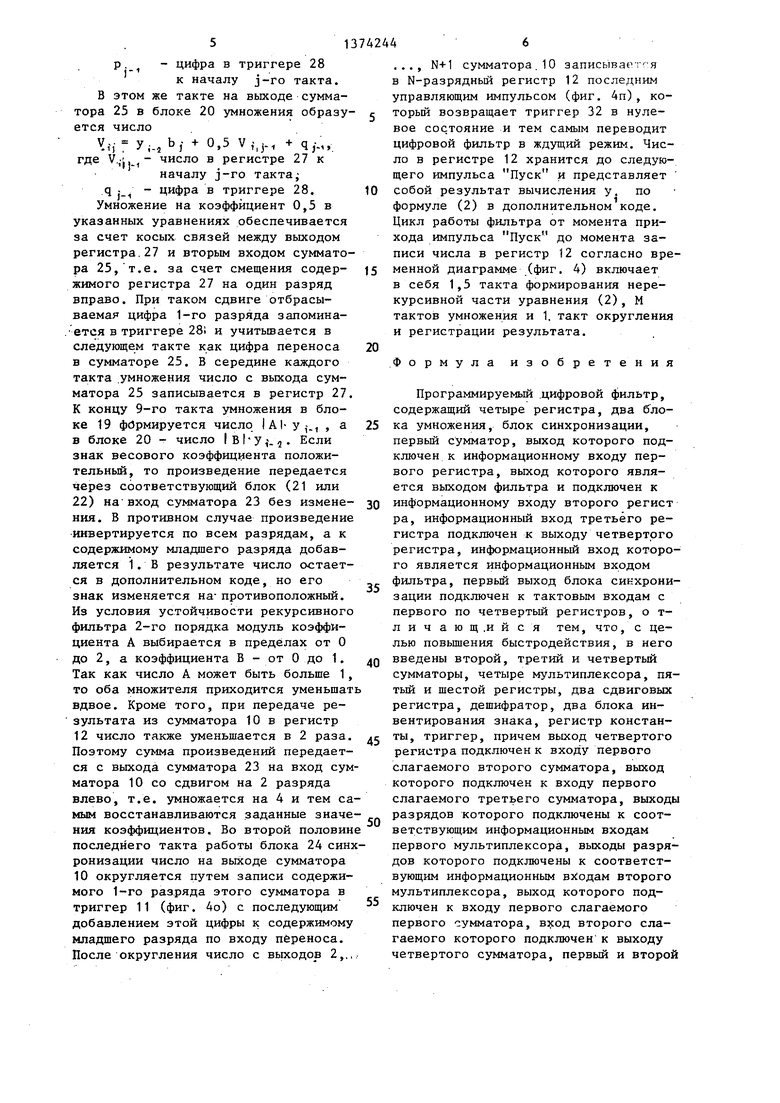

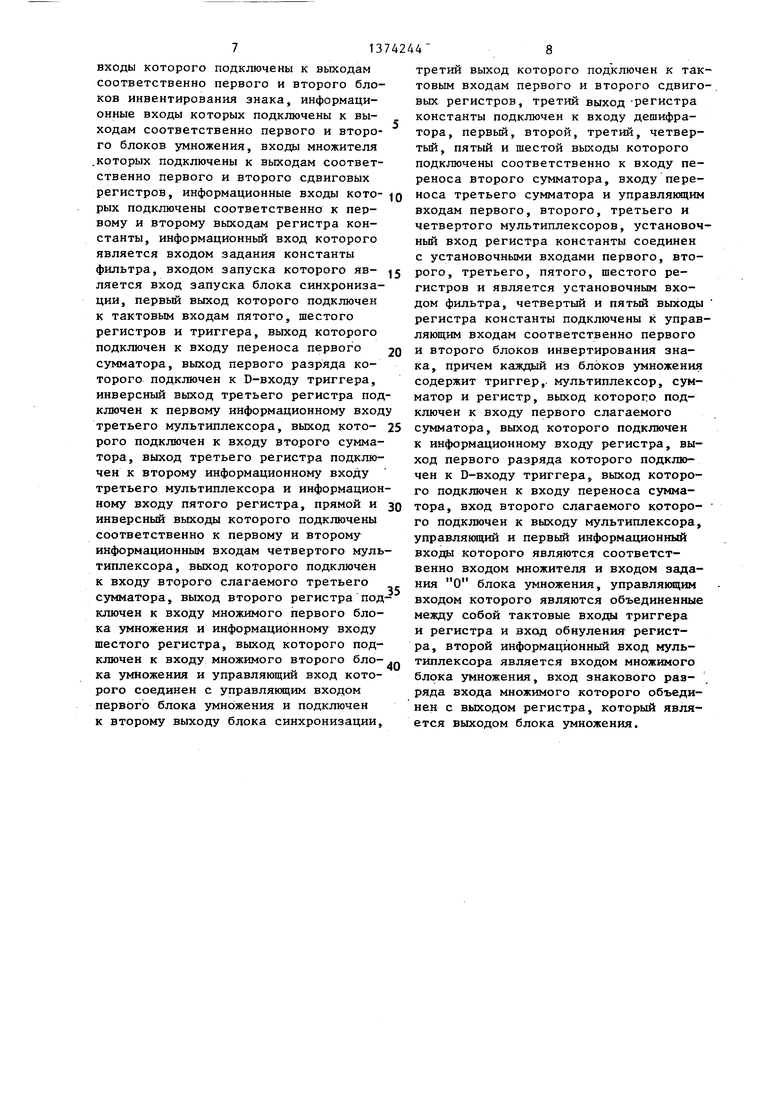

На фиг. 1 изображена функционапь- на я схема программируемого цифрового фильтра, на фиг. 2 - функциональная схема блока умножения;.на фиг. 3 - функциональная схема блока синхронизации, на фиг. временные диаграммы фильтра.

Программируемый цифровой фильтр (фиг. 1) содержит регистры 1 и 2, сумматор 3, мультиплексор 4, сумматор 5, регистр 6, мультиплексоры 7-9, сумматор 10, D-триггер 11, регистр 12, дешифратор 13, регистр 14 константы, сдвиговые регистры 15 и 16, регистры 17 и 13, блоки 19 и 20 умножения, блоки 21 и 22 инвертирования знака, сумматор 23, блок 24 синхронизации.

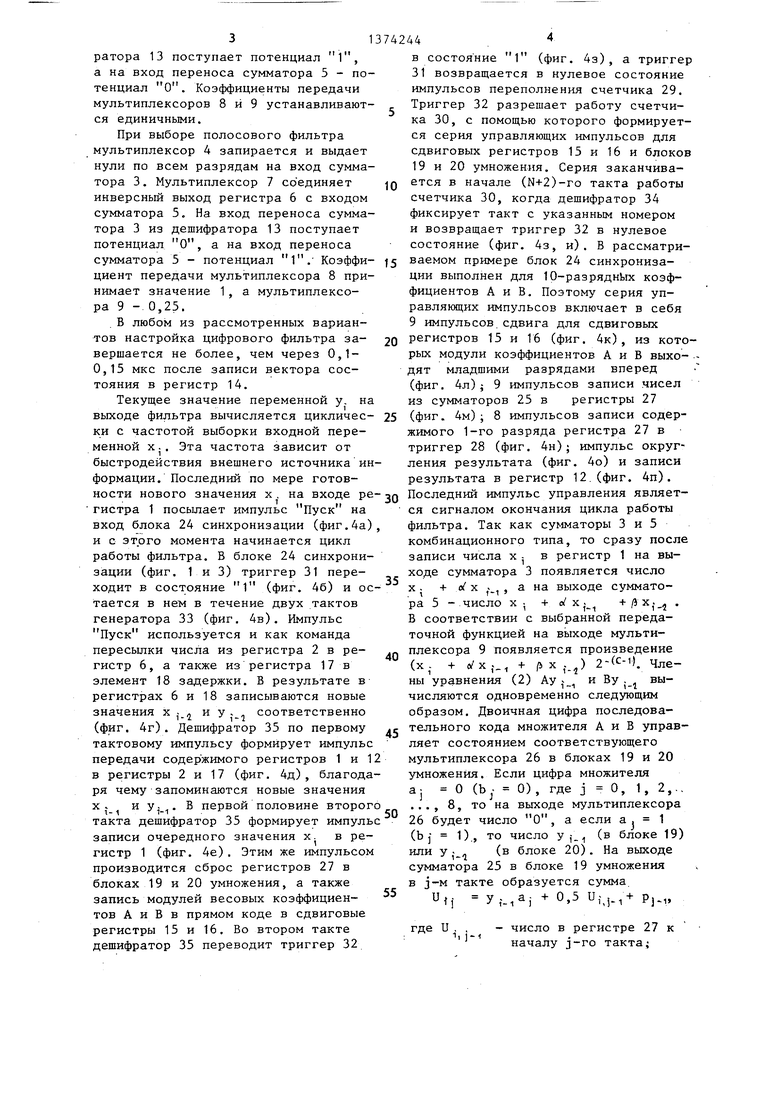

Каждый из блоков 19 и 20 умноже- ния (фиг. 2) содержит N-разрядные (комбинационный) сумматор 25, мультиплексор 26, регистр (аккумулятор) 27 и D-триггер 28.

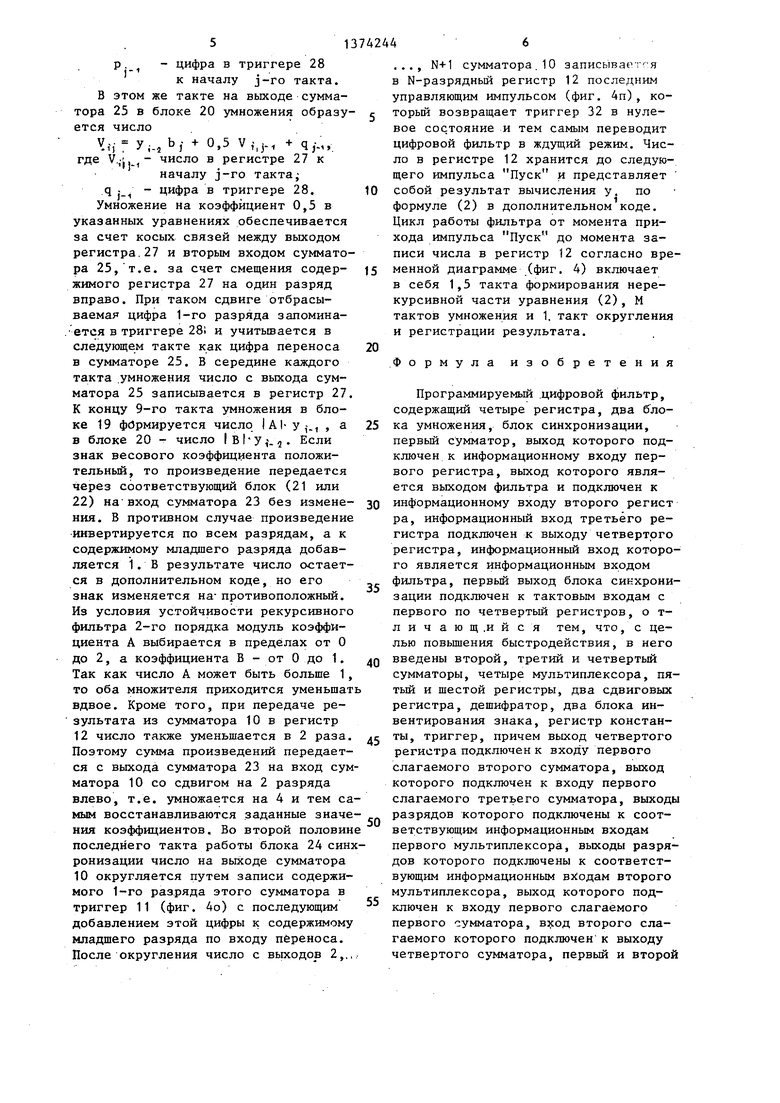

Блок 24 синхронизации (фиг. 3) со держит 2-разрядный счетчик 29, 4-раз рязньй счетчик 30, триггеры 31 и 32, тактовый генератор 33 и дешифраторы 34 и 35.

Программируемый цифровой фильтр работает следующим образом.

Для настройки фильтра на выбран- ную передаточную функцию в регистр 14 (фиг. 1) импульсом Начальная установка вводится вектор состояния V (Р, А, В), где F - 2-разрядный код передаточной функции. Тем же импульсом стирается содержимое регистров .2, 6, 17, 18 и 12. Содержимое регист

,--1 + Ву;. для ФНЧ, Ау,, + By,-.j для ФВЧ, (1)

5

20

25

30 с

Q

.с

0

5

I

ра 14 сохраняется на время работы с заданной передаточной функцией фильтра. Результатом начальной-установки является выбор одного из трех уравнений (1), которые можно записать одной строкой

у. (х .., +АХ,..,) 2- + .- Ау,..,+ By..5(2)

где Hi, - переменные на выходе дешифратора 13, зависящие от кода F, который принимает значение 01 для ФНЧ, 10 - для ФВЧ, 11 - для ПФ.

Дешифратор 13 обеспечивает формирование функций i(F) и /}(F) :

f 2npHF 01,г,1„рнр 01

-2 при F 10, ft 1 и

nt7

0 при F 11,

Константа масштабирования также зависит от кода F:

Г 6 при F 01, С -1 1 при F 10,

L 3 при F 11.

При настройке на фильтр нижних час тот между блоками устройства устанавливаются следующие связи. Мультиплексор 4 соединяет прямой выход регистра 2 с вторым входом сумматора 3.Мультиплексор 7 подключает прямой выход регистра. 6 к второму входу сумматора 5. На входы переноса сумматора 3 и 5 из дешифратора 13 подается потенциал О. Коэффициент передачи мультиплексора 8 устанавливается равным а мультиплексора 9 - равным 1.

При настройке на фильтр верхних частот мультиплексор 4 соединяет инверсный выход регистра 2 с входом сумматора 3, а мультиплексор 7 - прямой выход регистра 6 с входом сумматора 5. На вход первого разряда и вход переноса сумматора 3 из дешиф 1,

ратора 13 поступает потенциал а на вход переноса сумматора 5 - потенциал О. Коэффициенты передачи мультиплексоров 8 и 9 устанавливаются единичными.

При выборе полосового фильтра мультиплексор 4 запирается и выдает нули по всем разрядам на вход сумматора 3. Мультиплексор 7 со единяет инверсный выход регистра 6 с входом сумматора 5, На вход переноса сумматора 3 из дешифратора 13 поступает потенциал О, а на вход переноса сумматора 5 - потенциал 1. Коэффи- циент передачи мультиплексора 8 принимает значение 1, а мультиплексора 9 - 0,25.

. В любом из рассмотренных вариантов настройка цифрового фильтра за- вершается не более, чем через 0,1- 0,15 МКС после записи вектора состояния в регистр 14.

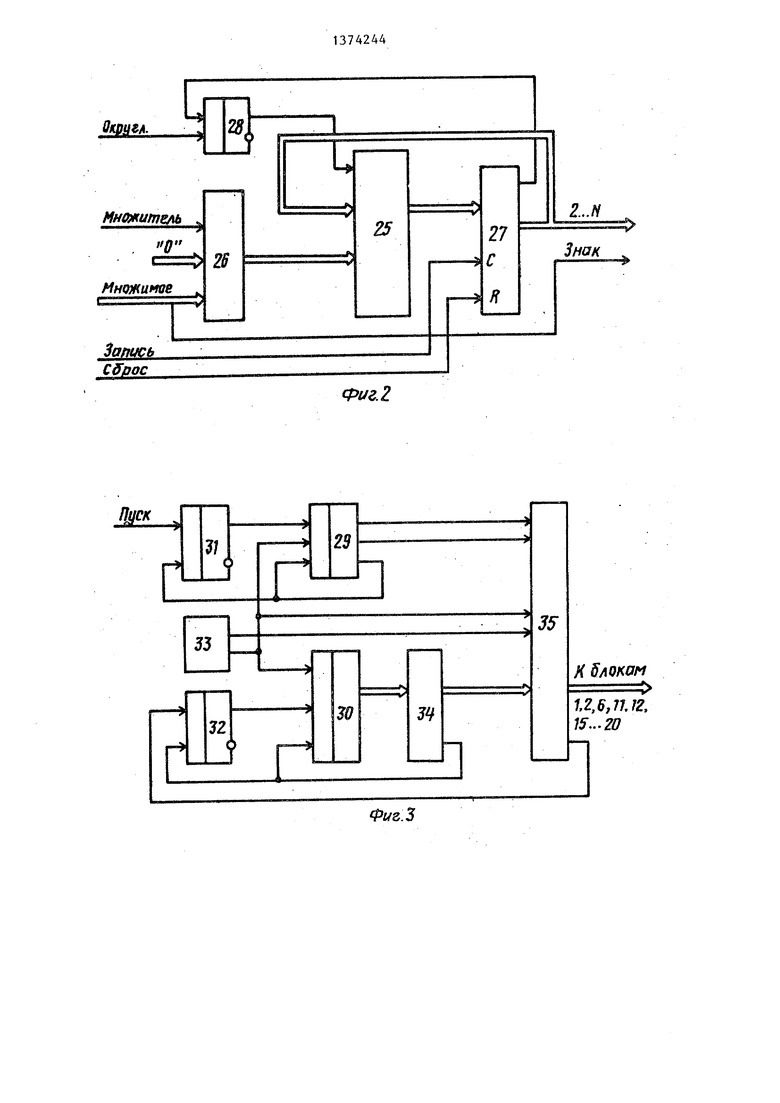

Текущее значение переменной у. на выходе фильтра вычисляется цикличес- ки с частотой выборки входной переменной X.. Эта частота зависит от быстродействия внешнего источника информации. Последний по мере готовности нового значения х , на входе Последний импульс управления являет гистра 1 посьшает импульс Пуск на вход блока 24 синхронизации (фиг.4а), и с этого момента начинается цикл работы фильтра. В блоке 24 синхронизации (фиг. 1 и 3) триггер 31 переходит в состояние 1 (фиг. 46) и остается в нем в течение двух тактов генератора 33 (фиг. 4в). Импульс Пуск используется и как команда пересьшки числа из регистра 2 в регистр 6, а также из регистра 17 в элемент 18 задержки. В результате в регистрах 6 и 18 записываются новые

35

40

ся сигналом окончания цикла работы фильтра. Так как сумматоры 3 и 5 комбинационного типа, то сразу после записи числа х - в регистр 1 на выходе сумматора 3 появляется число X . + V X у, , а на выходе сумматора 5 - число X. + о/х.| . . В соответствии с выбранной передаточной функцией на выходе мультиплексора 9 появляется произведение (х- + о/х., + /5 X .р 2 - (С-1) Члены уравнения (2) Ау и By . вычисляются одновременно следующим образом. Двоичная цифра последовательного кода множителя А и В управляет состоянием соответствующего мультиплексора 26 в блоках 19 и 20 умножения. Если цифра множителя

значения

м

и у

1-1

соответственно

(фиг. 4г). Дешифратор 35 по первому тактовому импульсу формирует имаульс передачи содержимого регистров 1 и 12 в регистры 2 и 17 (фиг. 4д), благодаря чему запоминаются новые значения Х и У.. В первой половине второго такта дешифратор 35 формирует импульс записи очередного значения х. в регистр 1 (фиг. 4е). Этим же импульсом производится сброс регистров 27 в блоках 19 и 20 умножения, а также запись модулей весовых коэффициентов А и В в прямом коде в сдвиговые регистры 15 и 16. Во втором такте дешифратор 35 переводит триггер 32

-JQ520

25 374244

в состоя ние

1 (фиг. 4з), а триггер 31 возвращается в нулевое состояние импульсов переполнения счетчика 29. Триггер 32 разрешает работу счетчика 30, с помощью которого формируется серия управляющих импульсов для сдвиговых регистров 15 и 16 и блоков 19 и 20 умножения. Серия заканчивается в начале (N+2)-ro такта работы счетчика 30, когда дешифратор 34 фиксирует такт с указанным номером и возвращает триггер 32 в нулевое состояние (фиг. 4з, и). В рассматриваемом примере блок 24 синхронизации выполнен для 10-разряднЬгх коэффициентов А и В. Поэтому серия управляющих импульсов включает в себя 9 импульсов, сдвига для сдвиговых регистров 15 и 16 (фиг. 4к), из которых модули коэффициентов А и В выхо- - дят младшими разрядами вперед (фиг. 4л)j 9 импульсов записи чисел из сумматоров 25 в регистры 27 (фиг. 4м); 8 импульсов записи содержимого 1-го разряда регистра 27 в триггер 28 (фиг. 4н); импульс округления результата (фиг. 4о) и записи результата в регистр 12.(фиг. 4п).

Последний импульс управления являет

ся сигналом окончания цикла работы фильтра. Так как сумматоры 3 и 5 комбинационного типа, то сразу после записи числа х - в регистр 1 на выходе сумматора 3 появляется число X . + V X у, , а на выходе сумматора 5 - число X. + о/х.| . . В соответствии с выбранной передаточной функцией на выходе мультиплексора 9 появляется произведение (х- + о/х., + /5 X .р 2 - (С-1) Члены уравнения (2) Ау и By . вычисляются одновременно следующим образом. Двоичная цифра последовательного кода множителя А и В управляет состоянием соответствующего мультиплексора 26 в блоках 19 и 20 умножения. Если цифра множителя

а;

О (Ь . 0), где j О, 1, 2,

..., 8, то на выходе мультиплексора 26 будет число О, а если а, 1 (Ь 1)., то число у,-. (в блоке 19) или у j (в блоке 20). На выходе сумматора 25 в блоке 19 умножения в J-M такте образуется сумма.

и

пгде и

У,-., а,- + 0,5 и,.;+ PJ,,,

- число в регистре 27 к началу j-ro такта;

51374244

р. - цифра в триггере 28

к началу j-ro такта. В этом же такте на вькоде сумматора 25 в блоке 20 умножения образу- с ется число

Y,-,- у..., Ь,- + 0.5 V,-,j-, -ь qy.,, где V,,-j.,- число в регистре 27 к

началу j-ro такта

.q - - цифра в триггере 28. 10 Умножение на коэффициент 0,5 в указанных уравнениях обеспечивается за счет косых связей между выходом регистра.27 и вторым входом сумматора 25, т.е. за счет смещения содер- 5 жимого регистра 27 на один разряд вправо. При таком сдвиге отбрасываемая цифра 1-го разряда запомина- ется в триггере 281 и учитывается в следующем такте как цифра переноса 20 в сумматоре 25. В середине каждого такта умножения число с выхода сумматора 25 записывается в регистр 27. К концу 9-го такта умножения в бло.

ке 19 фбрмируется число lAl у ,-., , в блоке 20 - число 1в1 У{. . Если знак весового коэффициента положительный, то произведение передается через соответствующий блок (21 или 22) на вход сумматора 23 без изменения. В противном случае произведение инвертируется по всем разрядам, а к содержимому младшего разряда добавляется i. В результате число остается в дополнительном коде, но его знак изменяется на- противоположный. Из условия устойчивости рекурсивного фильтра 2-го порядка модуль коэффициента А выбирается в пределах от О до 2, а коэффициента В - от О до 1. Так как число А может быть больше 1, то оба множителя приходится уменьшать вдвое. Кроме того, при передаче ре- зультата из сумматора 10 в регистр 12 число также уменьшается в 2 раза. Поэтому сумма произведений передается с выхода сумматора 23 на вход сумматора 10 со сдвигом на 2 разряда влево, т.е. умножается на 4 и тем самым восстанавливаются заданные значения коэффициентов. Во второй половине последнего такта работы блока 24 синхронизации число на выходе сумматора 10 округляется путем записи содержимого 1-го разряда этого сумматора в триггер 11 (фиг. 4о) с последующим добавлением этой цифры к содержимому младшего разряда по входу переноса. После округления число с выходов 2,.,

..., N+1 сумматора.10 записывается в N-разрядный регистр 12 последним управляющим импульсом (фиг. 4п), который возвращает триггер 32 в нулевое состояние и тем самым переводит цифровой фильтр в ждущий режим. Число в регистре 12 хранится до следующего импульса Пуск и представляет собой результат вычисления у. по формуле (2) в дополнительном коде. Цикл работы фильтра от момента прихода импульса Пуск до момента записи числа в регистр 12 согласно временной диаграмме (фиг, 4) включает в себя 1,5 такта формирования нерекурсивной части уравнения (2), М тактов умножения и 1, такт округления и регистрации результата.

Формула изобретения

Программируемый .цифровой фильтр, содержащий четыре регистра, два блока умножения, блок синхронизации, первый сумматор, выход которого подключен к информационному входу первого регистра, выход которого является выходом фильтра и подключен к информационному входу второго регист ра, информационный вход третьего регистра подключен к выходу четвертого регистра, информационный вход которого является информационным входом фильтра, первьш выход блока синхронизации подключен к тактовым входам с первого по четвертый регистров, о т- личающ.ийся тем, что, с целью повьш1ения быстродействия, в него введены второй, третий и четвертый сумматоры, четыре мультиплексора, пятый и шестой регистры, два сдвиговых регистра, дешифратор, два блока ин- вентирования знака, регистр константы, триггер, причем выход четвертого регистра подключен к входу первого слагаемого второго сумматора, выход которого подключен к входу первого слагаемого третьего сумматора, выходы разрядов которого подключены к соответствующим информационным входам первого мультиплексора, выходы разрядов которого подключены к соответствующим информационным вводам второго мультиплексора, выход которого подключен к входу первого слагаемого первого сумматора, вход второго слагаемого которого подключен к выходу четвертого сумматора, первый и второй

входы которого подключены к выходам соответственно первого и второго блоков инвентирования знака, информационные входы которых подключены к выходам соответственно первого и второго блоков умножения, входы множителя .которых подключены к выходам соответственно первого и второго сдвиговых регистров, информационные входы кото- рых подключены соответственно к первому и второму выходам регистра константы, информационный вход которого является входом задания константы фильтра, входом запуска которого является вход запуска блока синхронизации, первый выход которого подключен к тактовым входам пятого, шестого регистров и триггера, выход которого подключен к входу переноса первого сумматора, выход первого разряда которого подключен к D-входу триггера, инверсный выход третьего регистра подключен к первому информационному вход третьего мультиплексора, выход кото- рого подключен к входу второго сумматора, выход третьего регистра подключен к второму информационному входу третьего мультиплексора и информационному входу пятого регистра, прямой и инверсный выходы которого подключены соответственно к первому и второму информационным входам четвертого мультиплексора, выход которого подключен к входу второго слагаемого третьего сумматора, выход второго регистра под ключен к входу множимого первого блока умножения и информационному входу шестого регистра, выход которого подключен к входу множимого второго блока умножения и управляющий вход которого соединен с управлякяцим входом первого блока умножения и подключен к второму выходу блока синхронизации.

д 0 5 о

третий выход которого подключен к тактовым входам первого и второго сдвиго-. вых регистров, третий выход -регистра константы подключен к входу дешифратора, первый, второй, третий, четвер- тьй, пятый и шестой выходы которого подключены соответственно к входу переноса второго сумматора, входу переноса третьего сумматора и управляющим входам первого, второго, третьего и четвертого мультиплексоров, установоч- ньш вход регистра константы соединен с установочными входами первого, вто- 5 рого, третьего, пятого, шестого регистров и является установочным входом фильтра, четвертый и пятый выходы регистра константы подключены к управляющим входам соответственно первого и второго блоков инвертирования знака, причем каждый из блоков умножения содержит триггер,, мультиплексор, сумматор и регистр, выход которого подключен к входу первого слагаемого сумматора, выход которого подключен к информационному входу регистра, выход первого разряда которого подключен к D-входу триггера, выход которого подключен к входу переноса сумматора, вход второго слагаемого которого подключен к выходу мультиплексора, управляющий и первый информационный входы которого являются соответственно входом множителя и входом задания О блока умножения, управляющим входом которого являются объединенные между собой тактовые входы триггера и регистра и вход обнуления регистра, второй информационный вход мультиплексора является входом множимого блока умножения, вход знакового разряда входа множимого которого объединен с выходом регистра, который является выходом блока умножения.

5

ОкрдеА.

с

j5

MHWutne/л

0

25

Множимое

Запись

Cffooc

29

53

3Z LU

30

27

-

Знак

ф1/г.2

J5

Я SAOKOM

34

1,2,6, JJJZ. 75...2Z7

Фиг.З

аTL

У

I

1

5-JTixuTTiJi-rijnj jajT n

Фиг.

| Патент США № 3777130, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гольденберг Л.М | |||

| Цифровые устройства на интегральных схемах в технике связи | |||

| М.: Мир, 1979, с | |||

| Упругое экипажное колесо | 1918 |

|

SU156A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-02-15—Публикация

1986-06-25—Подача