1

Изобретение относится к устройствам для обработки цифровых данных, частности к устройствам преобразования данных без изменения порядка, их следования или объема информации дл преобразования многоразрядных кодов из одной системы счисления в другую и может быть применено в самых разнообразных областях народного хозяйства, где используется вычислительная техника , например, для связи меду ЭВМ различных типов.

Целью изобретения является повышние быстродействия преобразователя.

На чертеже приведена блок-схема преобразователя табличных кодов.

Преобразователь содержит группу сумматоров по модулю два, элемент НЕ 2, два ключа 3, два шинных формирователя 4, дешифраторы 5 и 6, блок 7 памяти, управляющий вход 8, вход- но-выходные линии 9 и IО первого и второго кодов.

Предлагаемое устройство работает

следующим образом. I

Предварительно определяется сумм по модулю два двух заранее определе ных видов, сформированных из двоичных разрядов кодов одних и тех же символов. Вычисленные суммы по модулю дьа заносятся в блок 7 памяти. Дальнейшее преобразование кодов сводится к суммированию по модулю два полученной суммы с кодом первого вида при прямом преобразовании или с кодом второго вида при обратном преобразовании.

Работу устройства иллюстрирует пример преобразования кодов КОИ-8 и ГОСТ 10859-64, использующихся в ЭВМКод символа А в КОИ-8 Хд 0100000 Код символа А в ГОСТ 10859-64 У„ 00100000. Сумма по модулю два эти

ХА-Y,;

7 А

01100001

двух кодов /

Код Хд поразрядно поступает по входу 9 на вход первого шинного формирователя 4. Одновременно на управляющий вход 8 преобразователя поступает сигнал, которьЕЙ передается на управляющий вход первого шинного формирователя 4, и инверсное значение - на управляющий вход второго шинного формирователя-4, которые всегда работают в противоположных режимах. Под воздействием управляющего сигнала первый ключ 3 включает дешифратор 5, а второй ключ 3 отключает дешифратор 6.

5

0

5

0

5

0

поступает на на сумматоры по

Код Хд поразрядно вход дешифратора 5 и модулю два группы.

На выходе дешифратора 5, соотйет- ствующем символу А, появляется единица, в то время как на остальных выходах дешифратора 5 - нули. Эта единица поступает на соответствующий вход блока 7 памяти, на выходе которого появляется код Z, равный сумме по модулю два кодов Хд и д Z поразрядно поступает на входы сумматоров по модулю два группы 1, на вторые входы которой также поразрядно подается код Хд.

Код Y( с выводов сумматоров группы I поступает на входы второго шинного формирователя 4 и снимается с двунаправленной входно-вы- ходной линии 10.

Таким образом, осуществляется преобразование кода символа А в КОИ-8 в код ГОСТ 10859-64. Аналогично осуществляется преобразование кодов соответствующих другим символам.

При преобразовании из кода ГОСТ 10859-64 в код КОИ-8 информация подается на входно-выходную линию 10, а управляющий сигнал на входе 8 изменяется на противоположный. Включается дешифратор 6 и выключается дешифратор 5.

Код д через второй шинный форми- , рователь 4 выдается на дешифратор 6, на выходах которого формируется пространственный код, поступающей на блок 7 памяти. С блока 7 памяти на первые и с второго шинного формирователя 4 на вторые входы сумматоров по модулю два группы I подаются коды Z и Уд соответственно.

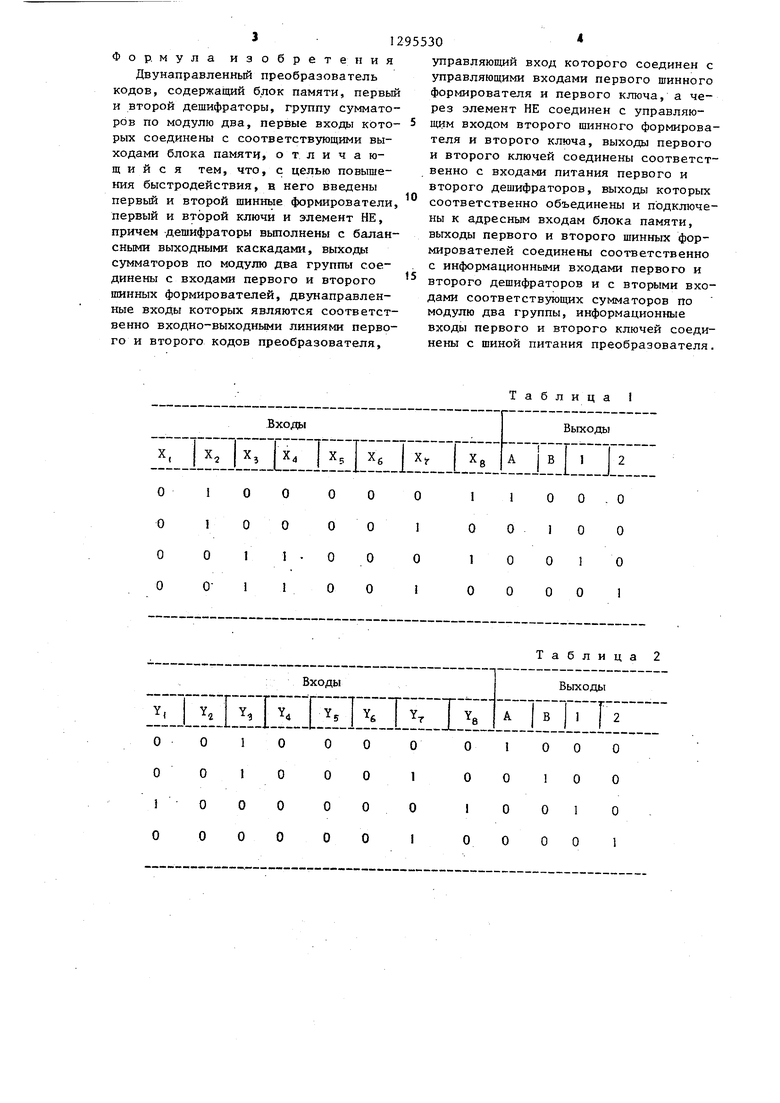

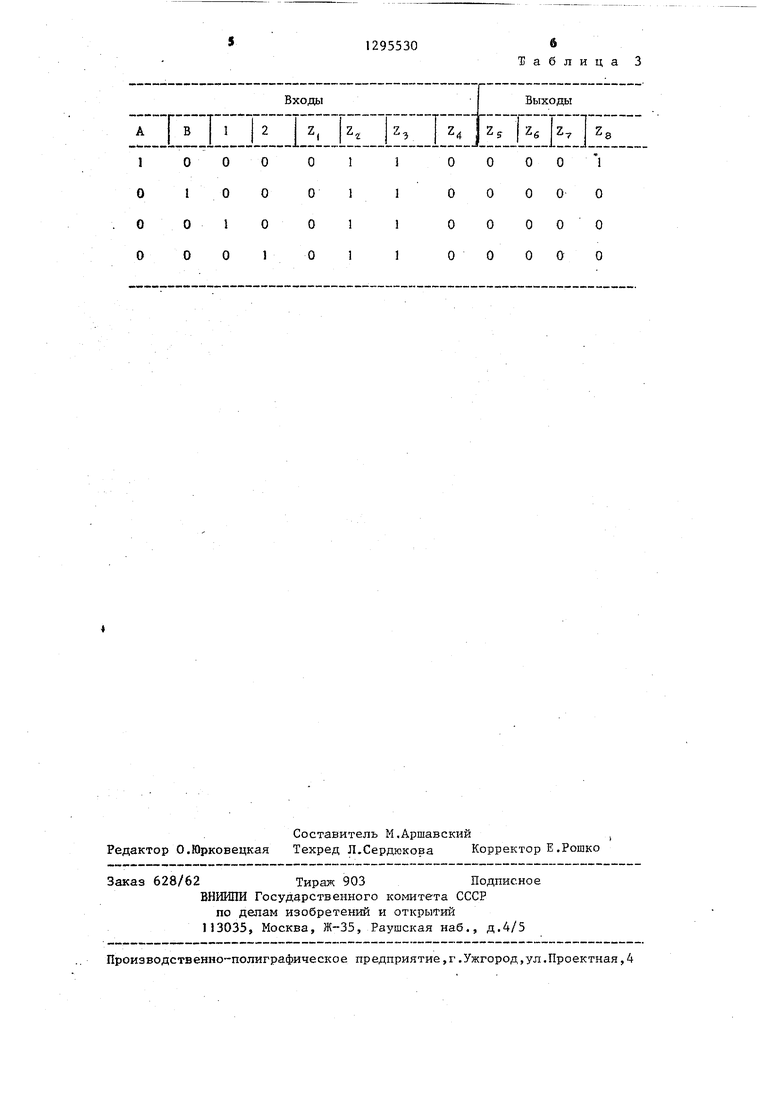

Полученный на. входах сумматоров по модулю два группы I код + Уд через шинный формирователь снимается с двунаправленной входно-выходной линии 9. В табл.1 и 2 приведены дан- нь.е о функционировании дешифраторов 5 и 6 для преобразования кодов КОИ-8 и ГОСТ 10859-64 соответственно; в табл.3 - содержимое блока памяти (данные приведены для четырех символов из существующих 44).

При соответств тощем построении дешифраторов 5 и 6 и блока 7 памяти преобразователь осуществляет другие преобразования кодов.

Формула изобретения

Двунаправленный преобразователь кодов, содержащий блок памяти, первый и второй дешифраторы, группу сумматоров по модулю два, первые входы которых соединены с соответствующими выходами блока памяти, отличающийся тем, что, с целью повышения быстродействия, в него введены первьй и второй шинньш формирователи, первый и второй ключи и элемент НЕ, причем дешифраторы выполнены с балансными выходными каскадами, выходы сумматоров по модулю два группы соединены с входами первого и второго шинных формирователей, двунаправленные входы которых являются соответственно входно-выходными линиями первого и второго кодов преобразователя.

5

управляющий вход которого соединен с управляющими входами первого шинного формирователя и первого ключа, а через элемент НЕ соединен с управляющим входом второго шинного формирователя и второго ключа, выходы первого и второго ключей соединены соответственно с входами питания первого и второго дешифраторов, выходы которых соответственно объединены и подключены к адресным входам блока памяти, выходы первого и второго шинных формирователей соединены соответственно с информационными входами первого и второго дешифраторов и с вторыми входами соответствующих сумматоров по модулю два группы, информационные входы первого и второго ключей соединены с шиной питания преобразователя.

Таблица 2

Таблица 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухнаправленный преобразователь табличных кодов | 1980 |

|

SU896615A1 |

| Двунаправленный преобразователь табличных кодов | 1983 |

|

SU1163480A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1987 |

|

SU1476490A2 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для защиты телеграфных сообщений от ошибок | 1976 |

|

SU636810A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Множительное устройство | 1981 |

|

SU1024909A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей для вычислительных и измерительных устройств. Целью изобретения является увеличение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь, содержащий два дешифратора 5, 6, блок 7 памяти и группу полусумматоров, введены первый и второй блоки 4 шинных формирователей, обеспечивающих обратимый режим работы полусумматоров без введения элементов задержки, два ключа 3, управляющих питанием дешифраторов, и элемент НЕ, причем выходы полусумматоров группы соединены с входами шинных формирователей, выходы которых соединены с входами дешифраторов и сумматоров по модулю два. 1 ил. 3 табл. & (Л

| Патент США № 3461432, - кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Двухнаправленный преобразователь табличных кодов | 1980 |

|

SU896615A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-11—Подача