Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи информации.

Цель изобретения - повышение помехоустойчивости декодирования недвоичных кодов в каналах с многофазной модуляцией.

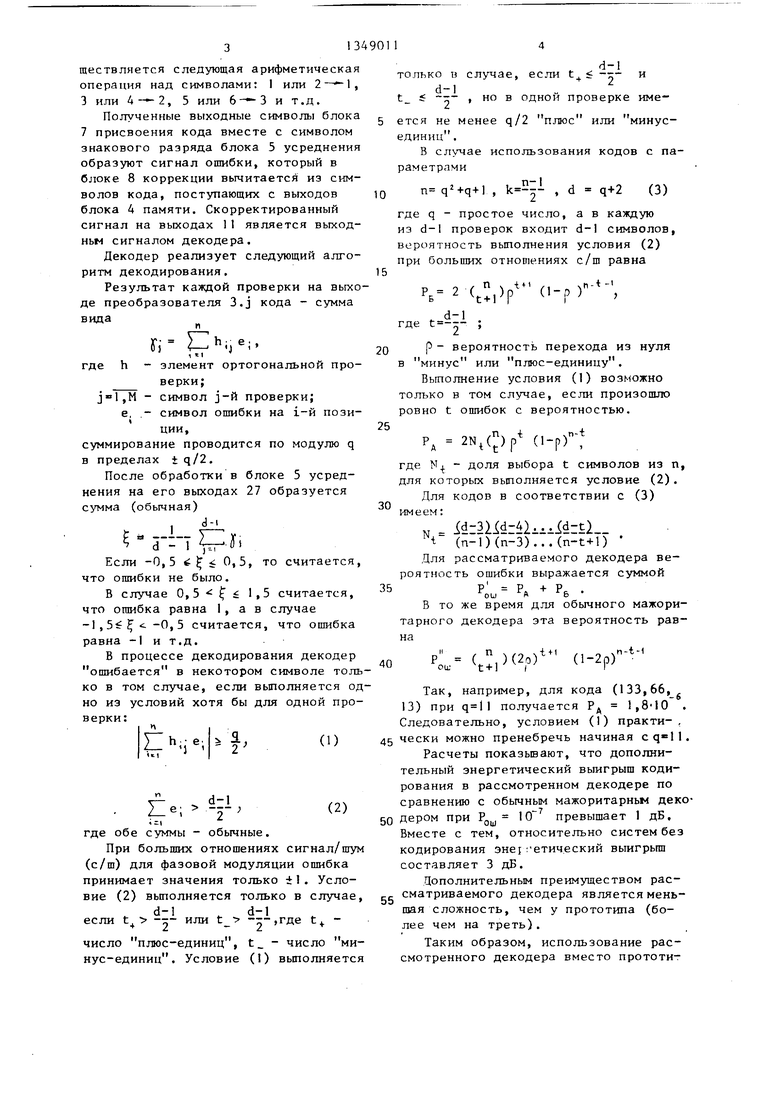

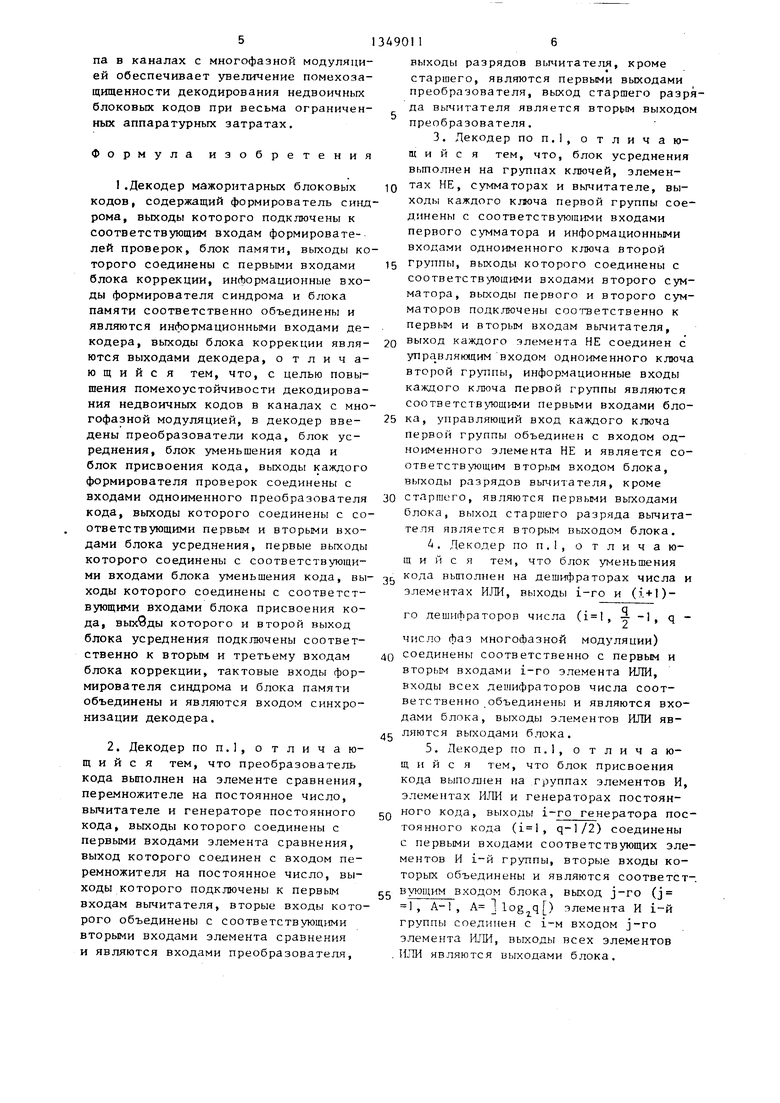

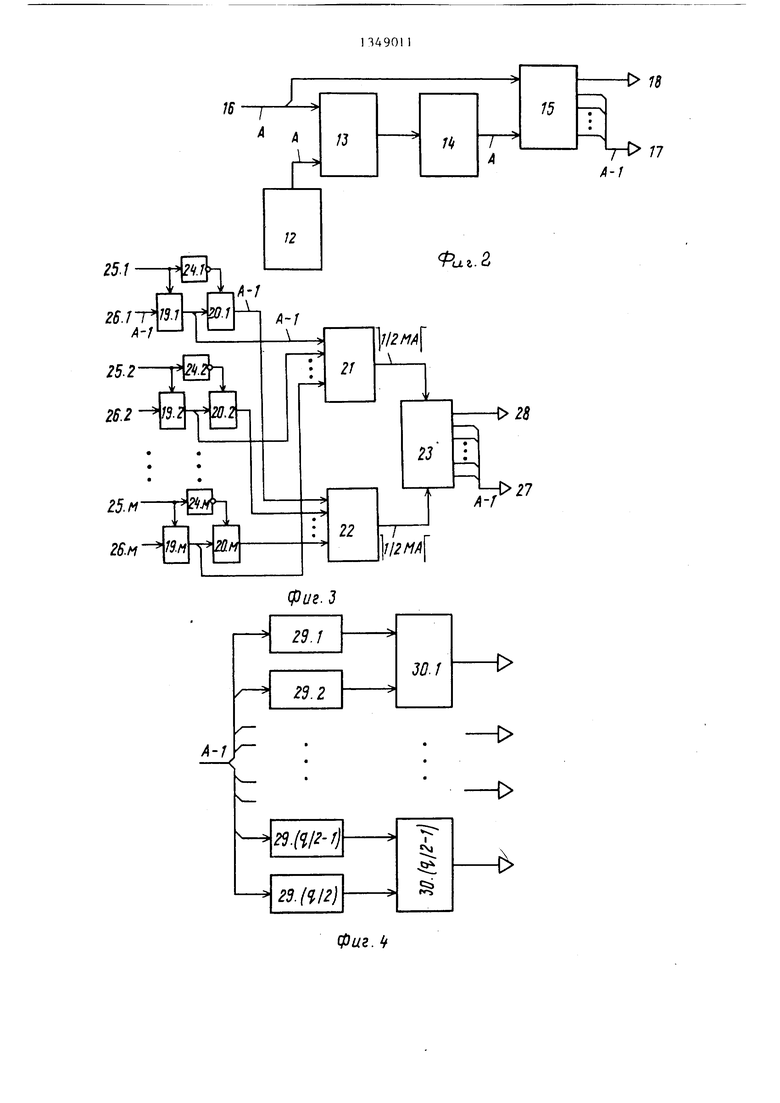

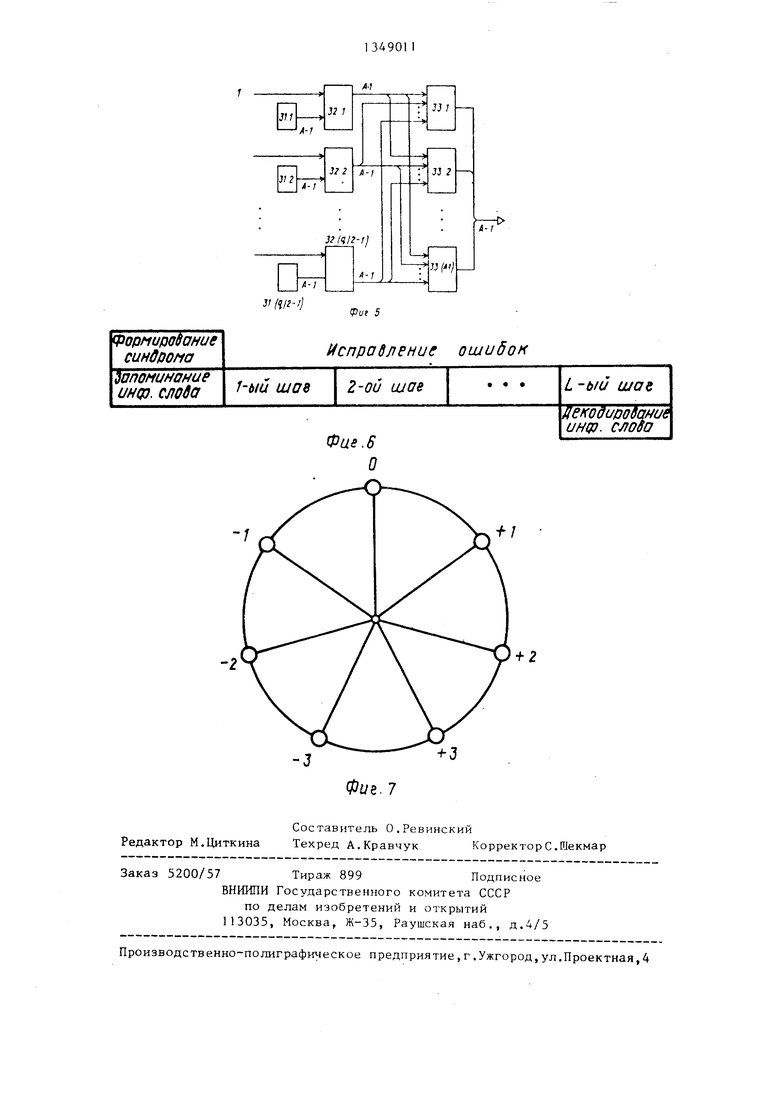

На фиг.1 представлена блок-схема декодера мажоритарных блоковых кодов на фиг.2-5 - функциональные схемы соответственно преобразователя кода, блока усреднения, блока уменьшения кода и блока присвоения; на фиг.6 - временная структура процесса обработки кодов; на фиг.7 - сигнальная диаграмма семифазной модуляции.

Декодер мажоритарных блоковых кодов содержит (фиг.1) формирователь 1 синдрома, М формирователей 2 проверок (, d - расстояние Хэмминга используемого (п,К,ё)-кода, п - число символов в блоке кода, k - число информационных символов в блоке ко- да), М преобразователей 3 кода, блок А памяти, блок 5 усреднения, блок 6 уменьшения кода, блок 7 присвоения кода и блок 8 коррекции. На фиг.1 обозначены информационные входы 9,так товый вход 10, выходы 11, а также указана кратность соединений (пгин) . Здесь А log,jq, q - число фаз многофазной модуляции,ПГ - ближайшее большее целое число (скобки Антье).

Формирователь 1 синдрома представляет собой сумматор по модулю q, выходы которого соединены с информационными входами q-ичного (n-k)-разрядного регистра сдвига с обратными связями, параллельные выходы которого образуют A(n-k) выходов формирователя 1 .

Каждый формирователь 2 m проверок ( ,М) представляет собой с умматор по модулю q.

Преобразователь З.т кода выполнен (фиг. 2) на генера торе 12 постоянного кода, элементе 13 сравнения, перемножителе 14 на постоянное число и вы- читателе 15 (q-ичном сумматоре). На фиг, 2 обознаж НЬ входы 16, первые и вторые 3HaKO jbiii выходы 17, 18.

Блок 4 памяти представляет собой q-ичный (n-k)-paзpядный регистр сдви- га.

Блок 5 усред}шния выполнен (фиг.З) на nepBOs i и второй группах клюле 19,

I 12

20, первом и втором сумматорах 21, 22, вычитателе 23 и элементах НЕ 24. На фиг.З обозначены первые и вторые входы 25, 26, первый (знаковый) и вторые выходы 27, 28. Ключи 19, 20 представляют собой наборы из A-I зле ментов И, первые входы которых объединены в управляющий вход ключа.

Блок 6 уменьшения кода вьшолнен (фиг .4) на q/2 дешифраторах 29 числа и q/2-l элементах ИЛИ 30. Каждый из депп1фраторов 29 предназначен для индикации кода числа, равного порядковому номеру этого деш 1фратора 29.

Блок 7 присвоения кода выполнен (фиг.5) на q/2-l генераторах 31 постоянного кода, группе элементов И 32 и элементах ИЛ 33. Генераторы. 31 формируют на своих выходах q-ичны код числа, равного порядковому номеру этого генератора 31.

Блок 8 коррекции представляет собой сумматор по модулю q.

Лекодер недвоичньгх мажоритарных блоковых кодов (фиг.1) работает сле- д тошим образом.

Входная информация, представляюща собой q-ичные символы (п,k,d)-кoдa в виде чисел 0,1,2..., q-1 поступает с входов 9 по А-кратной шине в формирователь 1 синдрома и одновременно в блок 4 памяти. На выходе блока I формируется синдром принятого слова в ниде n-k q-ичных символов, которые поступают на входы формирователей 2 проверок, на выходах которых появля- ился q-ичных символов значений проверок кода в В1ще чисел 0,1,2,... q-1 кажды ;. Символы значений црове-. рок постчтгают на входь преобразовате 3 кода, на выходах которых каждая проверка представляется в виде чисел О + 1 , i 2, . . . , i q-1 /2, при этом входные символы О,1,2,...,q-1/2 не изменяются, а из остальных вычитается постоянное число q, т.е. остальные ГИМВПЛ1Л изменяются по правилу

, , q-33 и т.д.

С ныходо преоОразователей 3 кода эти симнолы попадают на входы блока . 5 усреднения, в котором определяется их cxT iMa вместе со знаком. Знак суммы с выхода 28 блока 5 направляется на третий вход блока 8 коррекции, а абсолютное значение с выходов 27 - на входы блока 6 уменьшения кода и далее после обработки в блок 7 присвоения кода. В блоках 6, 7 осушествляется следующая арифметическая операция над символами: 1 или 2- 1 , 3 или , 5 или и т.д.

Полученные выходные символы блока 7 присвоения кода вместе с символом знакового разряда блока 5 усреднения образуют сигнал ошибки, который в блоке 8 коррекции вычитается из символов кода, поступающих с выходов блока 4 памяти. Скорректированный сигнал на выходах 11 является выход- ньм сигналом декодера.

Декодер реализует следующий алгоритм декодирования.

Результат каждой проверки на выходе преобразователя 3.J кода - сумма вида

i С hi,

где

- злемент ортогональной про верки;

,M - символ j-й проверки;

е, - символ ошибки на i-й пози- «

ции,

суммирование проводится по модулю q в пределах ± q/2.

После обработки в блоке 5 усреднения на его выходах 27 образуется сумма (обычная)

I

S

Если -О,5 О,5, то считается что ошибки не было.

В случае О, 5 1,5 считается, что ошибка равна 1, а в случае -1,,5 считается, что ошибка равна -I и т.д.

В процессе декодирования декодер опшбается в некотором символе только в том случае, если выполняется одно из условий хотя бы для одной проверки:

Ь.е;

Ч.

- 2

(1)

. d-1 Це; -Г-;

(2)

где обе суммы - обычные.

При больших отношениях сигнал/шум (с/т) для фазовой модуляции ошибка принимает значения только ±1. Условие (2) выполняется только в случае,

d-1 d-1 если t --- или t ---,где t число плюс-единиц, t - число минус-единиц. Условие (I) выполняется

d-1 только в случае, если t --- и

d-1„

t --- , но в одной проверке имеется не менее q/2 плюс или минус- единиц .

В случае использования кодов с параметрами

, , d q+2 (3)

где q - простое число, а в каждую из d-1 проверок входит d-1 символов, вероятность выполнения условия (2) при больших отношениях с/ш равна

по / ч / 1чП- РБ 2 Р

d-1 где ;

р- вероятность перехода из нуля в минус или плюс-единицу.

Выполнение условия (1) возможно только в том случае, если произошло ровно t ошибок с вероятностью.

n-t

Рд 2N,(j)p (1-рг;

где N - доля выбора t символов из п, ля которых выполняется условие (2).

Для кодов в соответствии с (3) имеем:

N - id;3iid;41 id3tl

t (n-l)(n-3)...(n-t+l) Для рассматриваемого декодера вероятность ошибки выражается суммой р р + р

ои 6

В то же время для обычного мажоритарного декодера эта вероятность равна

Р:.. с,)(2р) (1-2р)-

о ц;

Ч + 1

5

0

g

Так, например, для кода (133,66, 13) при получается Рд 1,810 . Следовательно, условием (1) практи- , чески можно пренебречь начиная .

Расчеты показьшают, что дополнительный энергетический выигрыш кодирования в рассмотренном декодере по сравнению с обычным мажоритарньм декодером при Рдщ 10 превышает 1 дБ, Вместе с тем, относительно систем без кодирования энег : етический выигрьш составляет 3 дБ.

Дополнительным преимуществом рассматриваемого декодера является меньшая сложность, чем у прототипа (более чем на треть).

Таким образом, использование рассмотренного декодера вместо прототит

па в каналах с многофазной модуляцией обеспечивает увеличение помехозащищенности декодирования недвоичных блоковых кодов при весьма ограниченных аппаратурных затратах.

Формула изобретения

1.Декодер мажоритарных блоковых кодов, содержащий формирователь синдрома, вькоды которого подключены к соответствующим входам формирователей проверок, блок памяти, выходы которого соединены с первыми входами блока коррекции, информационные входы формирователя синдрома и блока памяти соответственно объединены и являются информационными входами декодера, выходы блока коррекции являются выходами декодера, отличающийся тем, что, с целью повышения помехоустойчивости декодирования недвоичных кодов в каналах с многофазной модуляцией, в декодер введены преобразователи кода, блок усреднения, блок уменьшения кода и блок присвоения кода, выходы каждого формирователя проверок соединены с входами одноименного преобразователя кода, выходы которого соединены с соответствующими первым и вторыми входами блока усреднения, первые выходы которого соединены с соответствутащи- ми входами блока уменьшения кода, выходы которого соединены с соответствующими входами блока присвоения кода, вых9ды которого и второй выход блока усреднения подключены соответ- ствеино к вторым и третьему входам блока коррекции, тактовые входы формирователя синдрома и блока памяти объединены и являются входом синхронизации декодера.

2. Декодер поп.1,отличаю- щ и и с я тем, что преобразователь кода выполнен на элементе сравнения, перемножителе на постоянное число, вычитателе и генераторе постоянного кода, выходы которого соединены с первыми входами элемента сравнения, выход которого соединен с входом перемножителя на постоянное число, выходы которого подключены к первым входам вычитателя, вторые входы которого объединены с соответствующими вторыми входами элемента сравнения и являются входами преобразователя.

выходы разрядов вычитателя, кроме

старшего, являются первыми выходами преобразователя, выход старшего разряда вычитателя является вторьм выходом преобразователя.

3. Декодер поп.1,отличаю- щ и и с я тем, что, блок усреднения вьтолнен на группах ключей, элементах НЕ, сумматорах и вычитателе, выходы каждого ключа первой группы соединены с соответствующими входами первого сумматора и информационными входами одноименного ключа второй

группы, выходы которого соединены с соответствующими входами второго сумматора, вькоды первого и второго сумматоров подключены соответственно к первым и вторым входам вычитателя,

выход каждого элемента НЕ соединен с упра влякяцим входом одноименного ключа второй группы, информационные входы каждого ключа первой группы являются соответствл, ющими первыми входами блока, управляющий вход каждого ключа первой группы объединен с входом одноименного элемента НЕ и является соответствующим вторым входом блока, выходы разрядов вычитателя, кроме

старшего, являются первыми выходами блока, выход CTapuiero разряда вычитателя является вторым выходом блока.

. Декодер по п.1, о т л и ч а ю- щ и и с я тем, что блок уменьшения

кода выполнен на дешифраторах числа и элементах ИДИ, выходы i-ro и (i+1)го дешифраторов числа (, - -1, q число фаз многофазной модуляции)

соединены соответственно с первым и вторым входами i-ro элемента ИЛИ, входы всех дешифраторов числа соответственно объединены и являются входами блока, выходы элементов ИЛИ являются выходами блока.

5. Декодер поп.1,отлича ю- щ и и с я тем, что блок присвоения кода выполнен на группах элементов И, элементах ИДИ и генераторах постоянного кода, выходы i-ro генератора постоянного кода (, q-1/2) соединены с первыми входами соответствующих элементов И i-й группы, вторые входы которых объединены и являются соответствующим входом блока, выход j-ro (j 1, А-1, ) элемента И i-й группы соединен с i-м входом j-ro элемента ИДИ, выходы всех элементов ИДИ являются выходами блока.

16

25. м

26.М

{ 18

ll2MA

фие.З

Фиг. fy

Составитель О.Ревинский Редактор М.ЦиткинаТехред А.КравчукКорректоре.Шекмар

Заказ 5200/57Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

Фие. 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Способ инжекторного декодирования сверточных кодов | 2020 |

|

RU2741062C1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| СПОСОБ РАБОТЫ СИМВОЛЬНОГО ПОРОГОВОГО ЭЛЕМЕНТА В СИМВОЛЬНОМ МАЖОРИТАРНОМ ДЕКОДЕРЕ | 2014 |

|

RU2573741C2 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Кодек мажоритарного блочного кода | 1981 |

|

SU965000A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Кодек каскадного мажоритарного кода | 1984 |

|

SU1185613A1 |

Изобретение относится к автоматике и вычислительной технике. Его испо.пьзование в системах передачи информации позволяет повысить помехоустойчивость декодирования недвоичных кодов в каналах с многофазной модуляцией. Декодер мажоритарных блоковых кодов содержит формирователь 1 синдрома, формирователи 2(-2д, проверок, блок 4 памяти и блок 8 коррекции. Введение преобразователей 3,-3 кода, блока 5 усреднения, блока 6 уменьшения кода и блока 7 присвоения кода обеспечивает достижение энергетического выигрыша кодирования по сравнению с прототипом. 4 з.п, ф-лы, 7 ил. i (Л 00 со

| Труды НИИР, 1983, № 1, с.89-99 | |||

| ВеЦ Systeni Technical Journal, 1966, V.45, 7, p.1045-1055, figil, 2 | |||

| Питерсон У., Уэлдон К | |||

| Коды, исправляющие ошибки | |||

| М.: Мир, 1976, С.371, фиг.10.5. |

Авторы

Даты

1987-10-30—Публикация

1986-06-04—Подача