ход первого элемента ИЛЙ-НЕ соединен с первым входом сумматора по модулю два, второй которого соединен с выходом третьего элемента ИЛИ, а выход является выходом, поразрядной суммы старшего разряда узла кодирования групп, выход первого элемента ИЛИ является выходом поразрядной суммы младшего разряда узла кодирования групп, выход второго элемента ИЛИ соединен с вторым прямым входом первого элемента И-ИЛИ и первым инверсным входом второго элемента И-ИЛИ, выход первого элемента ИЛИ-НЕ соединен с третьим прямым входом первого элемента И-ИЛИ, выход четвертого элемента ИЛИ соединен ,с четвертым прямым и первым инверсным входами первого элемента И-ИЛИ и с вторым инверсным входом второго элемента И-ИЛИ, выход пятого элемента ИЛИ

соединен с третьим прямым входом вто рого элемента И-ИЛИ, выход второго элемента ИЛИ-НЕ соединен с пягым пря.мым входом первого элемента И-ИЛИ.

3. Устройство по п. 1, р т л и чающееся тем, что блок раз ре-, шающих элементов содержит 2и элемен- ТО8 И-ИЛИ, причем первый и второй прямые входы каждого элемента объединены и являются первой группой входов блока разрешающих элементов, третий прямой и первый инверсный входы объединены и являются второй группой входов блока разрешающих элементов, четвертый прямой и второй инверсный входы объединены и являются третьей группой входов блока разрешающих элементов, выходы элементов И-ИЛИ являются выходами блока разрешающих элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для умножения | 1975 |

|

SU555401A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения | 1987 |

|

SU1481744A1 |

1

Изобретение относится к вычислительной технике и предназначено для перемножения И-разрядных двоичных чисел.

Известны множительные ycтpoйcтвa содержащие регистры множимого, множителя, памяти переносов и сумма:тор 1 . . .

Такие устройства, работающие по принципу последовательного суммирования слагаемых, образуемых путем сдвига множимого на 1, 2...П- 1 разрядов, обладают невысоким быстродей-т ствием.

Наиболее близким к изобретению является множительное устройство, содержащее регистры первого и второго сомножителей, регистр памяти поразрядных сумм и регистр памяти перено- сов С23 .

Недостатком данного устройства также является невысокое быстродействие.

Целью изобретения является повышение быстродействия множительного устройства.

. Поставленная цель достигается тем, что 8 устройство, содержащее регистры первого и второго сомножителей, регистр памяти поразрядных

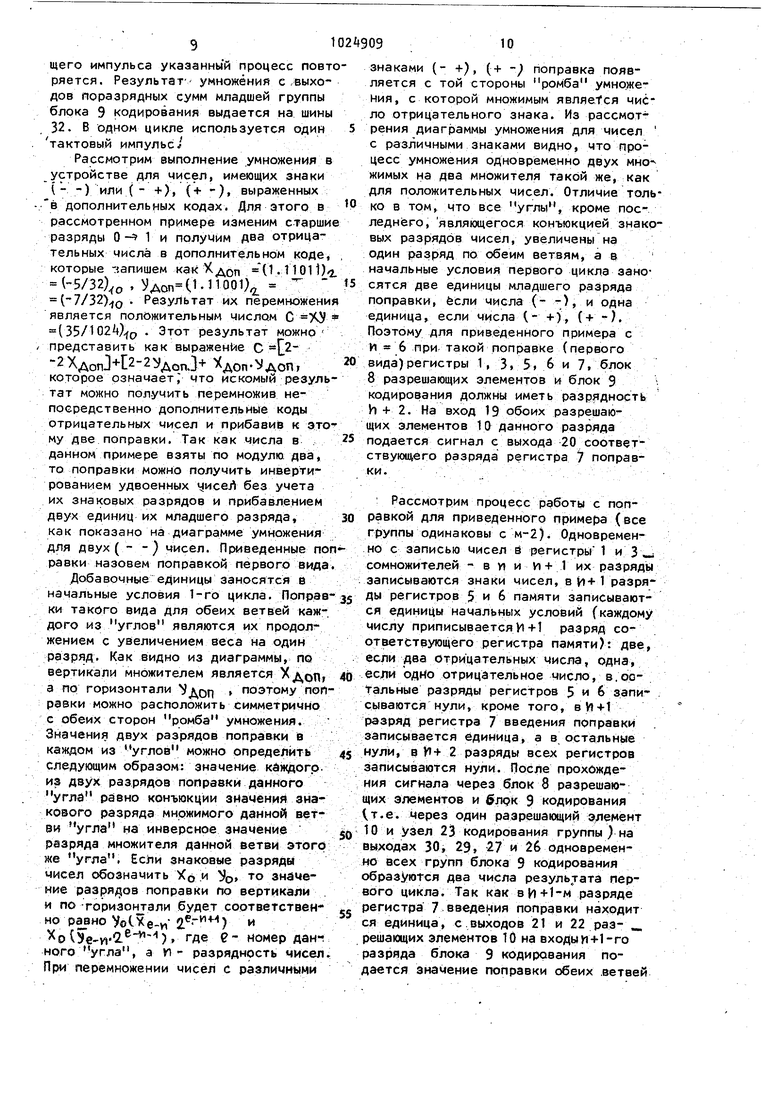

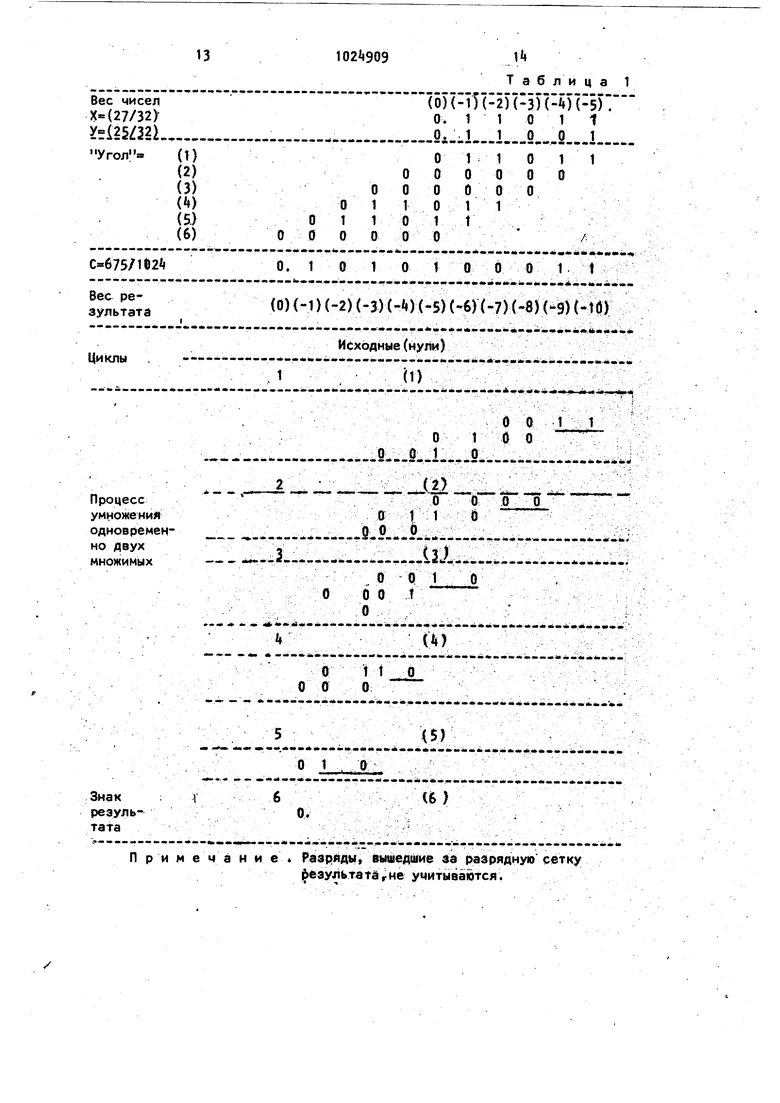

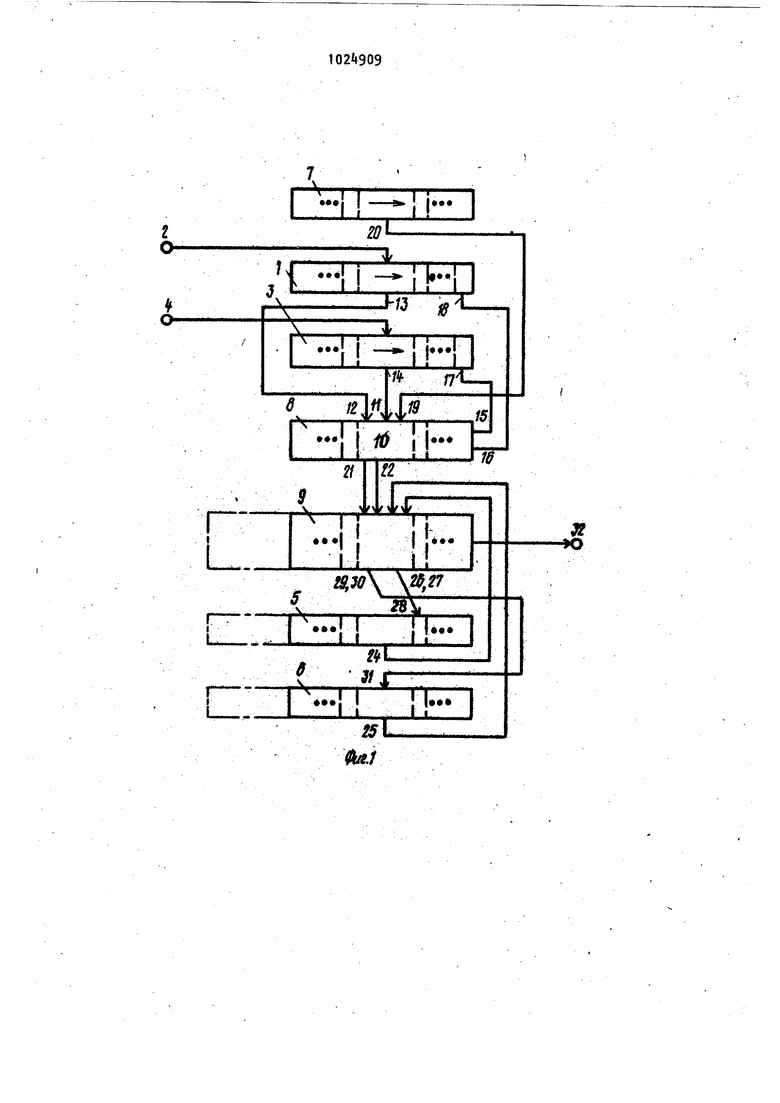

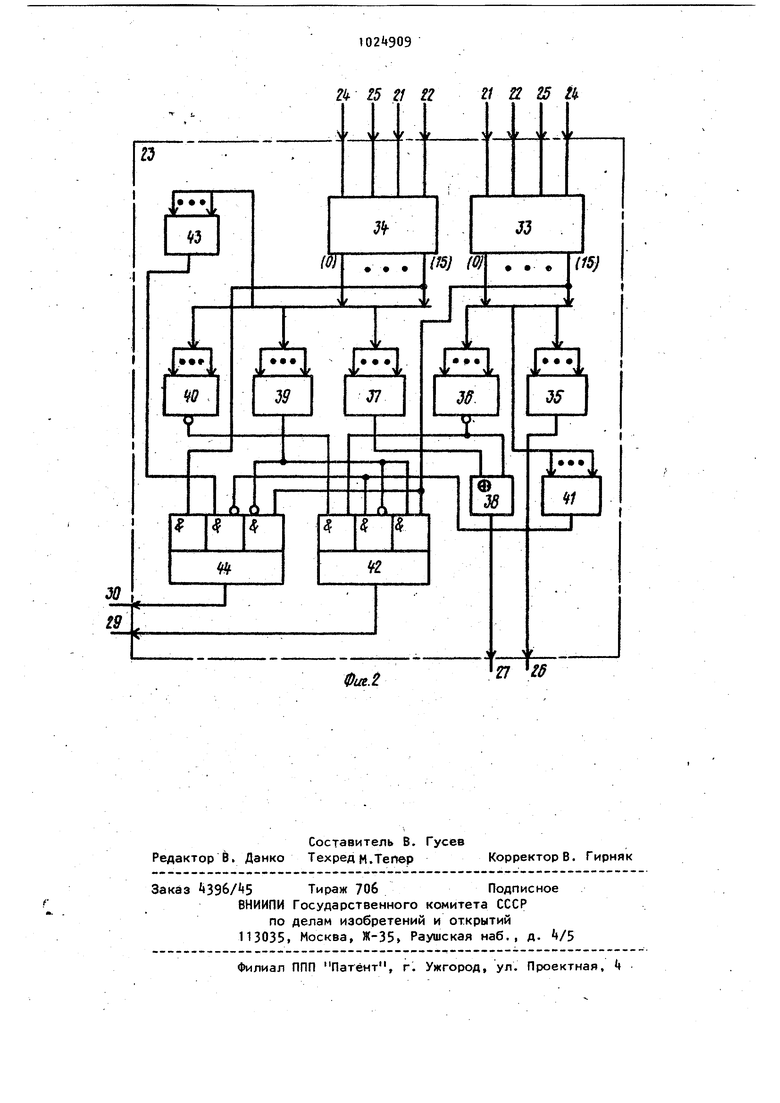

и регистр памяти переносов, введены блок кодирования, регистр поправки .и блок разрешающих элементов, при. чем первая группа входов блока разрешающих элементов соединена с выходами соотстветствующих разрядов регистров первого и второго сомножителей, вторая группа входов блока разрешающих элементов соединена с выходJO ми соответствующих разрядов регистра поправки, а входы третьей группы блока разрешающих элементов объединены и соединены соответственно с выходами младших разрядов регистров пёр15-вого и второго сомножителей, первый вход каждого разряда блока кодирова ния соединен с выходрм соответствующего разряда регистров памяти поразрядных с/мм, второй вход каждого 20 разряда блока кодирования соединен С выходом соответствующего разряда регистра памяти переносов, остальные входы каждого разряда блока кодирования соединены с выходами соответствующего разряда блока разрешающих элементов, выход поразрядной суммы каждого разряда блока кодирования соединен с входом разряда регистра поразрядных сумм более младvj шим, чем данный на количество раз3рядов в одной группе, а каждый выход переноса блока кодирования соединеи с входом.разряда регистра пер носов более младшим, ем данный на количество разрядов в одной группе. Кроме того, блок кодирования содержит п/ 2 узлов кодирования групп, каждый из которых содержит первый и второй дешифраторы, первый, второ третий и четвертый входы которых яв ются соответственно первым, вторым, третьим и четвертым входами узла кодирования гоупп, первый, второй, третей, четвёртый и пятый элементы ИЛИ, первый и второй элементы ИЛИ-Н сумматор по модулю два, первый и вт рой элементы И-ИЛИ, выходы которых являются соответственно младшим и старшим выходами переноса узла коди рования групп, выходы первого дешиф ратора соответственно соединены с входами первого и второго элементов ИЛИ и первого элемента ИЛИ-НЕ, а выход старшего разряда первого дешифратора соединен с первыми прямым входами первого и второго элементов И-ИЛИ, выходы второго дешифратора соответственно соединены с входами третьего четвертого и пятого элеме тов ИЛИ и второго элемента ИЛИ-НЕ, |а выход старшего разряда второго дешифратора соединен с вторым прямым входом второго элемента И-ИЛИ, выход первого элемента ИЛИ-НЕ соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом третьего элемента ИЛИ, а выход является выходом поразрядной суммы старшего разряда узла кодирования групп, выход первого элемента Или является выходом поразрядной суммы младшего разряда узла-кодирования групп, выход второго -элемента ИЛИ соединён с вторым прямым входом первого элемента И-ИЛИ и первым инверсным вхЬдом второго элемента . И-ИЛИ, выход первого элемента ИЛИНЕ соединен с третьим прямым входом первого элемента И-ИЛИ, выход четвертого элемента ИЛИ соединен с четвертым прямым и первым инверсным входами первого элемента И-ИЛИ и с вторым инверсным входом второго элемента И-ИЛИ, выход пятого элемент ИЛИ соединен с tpeтьим прямым входом второго элемента И-ИЛИ, выход второго элемента ИЛИ-НЕ соединен с пятым прямым входом первого элемента И-НЛИ. 09 А При этом блок разрешающих элементов содержит 2п элементов И-ИЛИ, причем первый и второй прямые входы каждого элемента объединены и являются первой группой входов блока разрешающих элементов, третий прямой и первый инверсный входы объединены и являются второй группой входов блока разрешающих элементов, четверууй прямой и второй инве|рсный входы объединены и являются третьей групpQ входов блока разрешающих элеменТОВ, выход элементов И-ИЛИ являются выходами блока разрешающих элементов. На фиг. 1 приведена функциональная схема множительного устройства на фиг. 2 - функциональная схема узла кодирования группы . Множительное устройство содержит регистр 1 первого сомножителя, на параллельные Входы которого по пер§ым числоёым шинам 2 подаются раз- ряды первого числа, регистр 3 второго сомножителя, на параллельные входы которого по вторым числовым шинам k подаются разряды второго числа, регистр 5 памяти поразрядной суммы, ре/истр 6 памяти переносов, регистр 7 введения поправки, блок о разрешающих; элементов, блок 9 кодирования. Для двухразрядной группы в каждом раз ряде блока 8 разрешающих элементов содержится два элемента И-ИЛИ 10. На входы11 и 12 первого и второго элементов И-ИЛИ 10 каждого разряда подаются сигналы с выходов 13 и I соответствующего разряда регистров 1 и 3 первого и второго сомножителей. На входы 15 и 16 первых и вторых элементов И-ИЛИ 10 всех разрядов подаются сигналы с выходов 17 и 18 младших разрядов соответственно регистров 1 и 3 первого и второго сомножителей. На входы 19 обоих элементов И-ИЛИ 10 каждого разряда подается сигнал с выхода 20 соответствующего разряда регистра 7 введения поправки. Каждый элемент И-ИЛИ 10 имеет один выход, а в одном разряде блока В разрешающих элементов образуется два выхода 21и 22, сигналы которых подаются на первый и второй входы соответствующего разряда узла 23 кодирования групп, входящего в состав блока 9 кодирования. На первые входы каждого разряда узла 23 кодирования групп подаются сигналы с выходом 2 соответствующих разрядов регистра 5 памяти поразрядной суммы, а на втор входы - сигналы с выходов 25 соответствующих разрядов регистра 6 памяти переносов, в которых записаны переносы из младшей по весу на один группы по отношению к данной. Сигналы с выходов 26 и 27 поразрядной суммы подаются на входы 28 разрядов регистра 5 поразрядной суммы соответственно младших по весу, мем дан ные выходы, на одну группу. Сигналы с выходов 29 младшего и 30 старшего разрядов переносов подаются на входы 31 разрядов данной группы регист 6 памяти переносов, но так, чтобы различие в весе составляло одну гру пу. Результат получают на выходах 2 и 27 поразрядной суммы самого младшего по весу узла 23 кодирования групп и подают на выходные шины 32. Узел 23 кодирования групп содержит дешифратор .ЗЗмладшего разряда группЫ дешифратор 3 старшего разряда груп пы, элемент ИЛИ 35 на входы которо го подаются сигналы с выходов дешифр тора 33 младшего разряда, элемент ИЛИ-НЕ 36, на входы которого подаютс сигналы с выходов дешифратора 33 младшего разряда, элемент ИЛИ 37i на входы которого подаются сигналы с выходов дешифратора 3 старшего разряда, сумматора 38 по модулю два элемент ИЛИ 39, на входы которого подаются сигналы с выходов дешифратора З старшего разряда, элемент ИЛИ-НЕ ko, на входы которого подают ся сигналы с выходов дешифратора З старшего разряда, элемент ИЛИЛ1 на входы которого подаются сигналы с выходов дешифратора 33 младшего разряда, элемент И-ИЛИ 42, элемент ИЛИ , на входы которого подаются сигналы с выходов дешифратора 3 старшего разряда и элемент И-,ИЛИ kk. : , Устройство работает след1по1дим образом. Рассмотрим в качестве примера перемножение двух положительных шестирядных двоичных чисел, которые являются правильными дробями. Умнож ние производится одновременно иа один разряд множителей в одном цикле. Первый сомножитель Х( 0. f 1011) (27/32){o , второй сомножитель V « (0.11001),. (25/32)0- Первый сомножитель служит одновременно первы множимым и множителем для второго множимого, а второй сомножитель одновременно вторым множимым и множителем дли первого множимого. Схема умножения представлена в табл. 1. Результат умножения С X,N (б75/102()0 . На диаграмме умножения приведенного примера сверху показано /умножение с помощью последовательного суммирования слагаемых при одном множимом и одном множителе, а также вычислен результат. Циклы вычислений процесса умножения двух множимых одновременно на два множителя и результат этого умножения, разряды которого подчеркнуты, представлены в табл. 2. Перед процессом умножения разрядную сетку разбивают на группы с одинаковым количеством разрядов ( м ), рав- ным удвоенному количеству разрядов множителей (к), одновременно используемых в одном цикле (м 2 к). Количество циклов вычислений Г равно ближайшему большему целому к разрядности чисел V , поделенной на количество разрядов множителей к, на которые одновременно производится умножение в одном цикле, . С каждым циклом происходит исключение из вычислений тех разрядов сомножителей7 которые были использованы в данном цикле как множители. В общем случае процесс умножения может быть представлен как процесс образования совокупностей кодов состояний для исходных чисел, разби-. тых на группы содинаковым количеством разрядов и полученных из двух чисел ре- г ультата предыдущего цикла вместе с обоими множимыми, взятыми в конъюкции с соответствующими данному циклу разрядами их множителей. Между разрядами сомножителей одинакового веса образуют-только одну конъюкцию. Разряды младшей группы данного цикла вычислений являются соответствующими разрядами-общего результата умнржеция, а оставшаяся совокупность кодов состояний образует два числа результата данного цикла. Для npивeдeнJиpгo примера в nepaofn цикле исходными четырьмя числами нули, а также первое и второе множимые, взятые в конъюкции с их множителями веса ( -5). Эти два множимых образуйт на диаграмме умножения по форме угол, обозначенный символом (1). Для четырех чисел каждой группы их двух разрядов.onределяют код состояний. В одном цикле для всех групп коды состояния определяют одновременно. В первом цикле разряды младшей группы являются двумя младшими разрядами результата; а остальная еовокупность кодов состояний образует две числа результата цикла. Получаемые разряды ре ультата на диаграмме подчеркнуты. Во BtopOM цикле исходные числа рб разуют из двух чисел результата цикла, а также из первого и второго множимых, взятых в кон-ьюкции с разря дом их множителей веса (- ) Разряд сомножителей беса (-5) больше в умножении не участвует. Эти jsea множимых на диаграмме умножений образую фигуру в виде угла, обозначенйую сймоволом t2). Снова для четырех Уисел каждбй группы из двух разрядов определяют код состояния. Для всех групп в цикле коды состояний определяют, одйовременно. После чего полу чают два следующих разряда резульtdта умножения и два числа результата 2-го . В следующих циклах производятся аналогичные операции по образованию кодов состояний в группах, и за шесть одинаковых циклов получаются разряды результата умножения. Пусть устройство умножает в ка)|щом цикле на один разряд множителей, и перемножаются два положительных числа. В регистры 1 и 3 первого и второго сомножителей по .числовым шинам 2 и соответственно записываются оба перемножаемых числа в прямых кодах. В регистры 5 и 6 памяти записываются нули. После Записи на первых выходах 21 и на вто рых выходах 22 каждого разряда блд ка 8 разрешающих элементов образуются соответственно разряды первого и второго множимых, взятых в конъюкциЦ с младшим разрядом их множителей для приведенного примера веса 5Л так как на входы 12 разрешающих элементо 10 каждого разряда, соответственно Для первого и второго множимых, подаются сигналы с выходов 13 и It соответству|рщих разрядов регистров ;1 и 3 первого и второго сомножителей На входы 15 разрешающего элемента 10 для первого множимого всех раз рядов подается разрешение с выхода 17 младшего разряда регистра 3 сог множителей, а на входы 16 всех разрядов разрешающего элемента 10 для второго множимого - разрешение с вы098хода 18 младшего разряда регистра 1 сомножителей. Для перемножения положительных чисел подача сигналов на входы 19 в разрешающих элементах 10 не требуется. Количество разрядов в блоке 9 кодирования равно для положительных чисел разрядности регистров 1 и 3..В блоке кодирования содержатся одинаковые узлы 23 кодирования групп. На входы одного разряда пода-ются сигналы с выходов 21 и 22 разрешающих элементов to соответствую- / щего разряда ( элементы угла), сигнал с выхода 24 регистра 5 поразрядных сумм данного разряда, сигнал с выхода 25 данного разряда рег истра 6 памяти переносов. Разряды, более младшие по весу, чем данные на одну группу, были записаны в этой группе а предыдущем цикле. На выходах 2б и 27 поразрядной суммы И 29,-30 переж)сов данной группы образуется код состояния дан|;1ой группы. На выходах 26 и 27 поразрядных сумм младшей группы блока 9 кодирования получают разряды общего результата умножения данного цикла. После записи чисел в регистры 1 и 3 на этих выходах получают первую группу разрядов результата, после прихода первого тактового импульса получают вторую группу разрядов результата и т;д. На выходах блока 9 кодирования образуются совокупности кодов состояний, которые связаны кроссировкой с входами раз рядов регистров 5 и 6 памяти и представляют собой два числа результата прошедшего цикла. После прихода очередного тактового импулБса одновременно на все регистры 1, 3 5. 6 и 7 в регистрах 1 и 3 сомножителей производится сдвиг Чисел с выведением младшего разряда чисел (при умножении на один разряд мноясителей в цикле), в регистре 7 сдвигается единица, а в регистры 5 и 6 памяти записываются два числа результата предыдущего цикла со сдвигом на одну, группу в сторону исключения младших разрядов. После этого на входах . блока 9 кодирования образуются элементы следующего угла и двух чисел результата предыдущего цикла, а н его выходах, через время срабатывания блока Ь разрешающих элементов и и блока 9 кодирования, - соответствуюая группа разрядов общего результата умножения и два числа результата анного циклвф После прихода,следую- , щего импульса указанный процесс повт ряется. Результат- умножения с .выходов поразрядных сумм младшей группы блока 9 кодирования выдается на шины 32. В одном цикле используется один тактовый импульс Рассмотрим выполнение умножения в устройстве для чисел, имеющих знаки {--) или (-+),{+ -), выраженных в дополнительных кодах. Для этого в рассмотренном примере изменим старши разряды О- 1 и получим два отрицательных числа в дополнительном коде, которые запишем как Хдоп (1.t10l1)-2 Ь5/32)о. (-7/32)Q . Результат их перемножени является положительным числом С У (35/1C)24)Q . Этот результат можно , представить как выражение С 2-2Хд„ 4.2-2Ь1доп.З+Хдоп.АоП, которое означаетJ что искомый резуль тат можно получить перемножив непосредственно дополнительные коды отрицательных чисел и прибавив к это му две поправки. Так как числа в данном примере взяты по модулю два, то поправки можно получить инвертированием удвоенных уисеЛ без учета их знаковых разрядов и прибавлением двух единиц их младшего разряда, как показано на диаграмме умножения для двух ( - -} чисел. Приведенные по равки назовем поправкой первого вида Добавочные единицы заносятся в начальные условия 1-го цикла. Поправ ки такого вида для обеих ветвей каждого из углов являются их продолжением с увеличением веса на один разряд. Как видно из диаграммы, по вертикали множителем является Хдо11т а по горизонтали Доп поэтому поп равки можно расположить симметрично с обеих сторон ромба умножения. Значения двух разрядов поправки в каждом из углов можно определить следующим образом: значение кйждогр. из двух разрядов поправки данного угла равно кон-ьюкции зйачений знакового разряда множимого данной вет0и угла на инверсное знамение разряда множителя данной ветви этого же угла. Если знаковые разряды чисел обозначить Хб и Vo то значение разрядов поправки по вертикали . и по-горизонтали будет соответственно равно Уо IX е-и ) и о зГе-иО- ) где е- номер дан-г кого угла, а К1 - разрядность чисел При перемножении чисел с различными знаками (- +), (+ ) поправка появляется с той стороны ромба умножения, с которой множимым является чиС ло отрицательного знака. Из рассмотрения диаграммы умножения для чисел с различными знаками видно, что процесс умножения одновременно двух множимых на два множителя такой же, как для положительных чисел. Отличие только в том, что все углы, кроме последнего, являющегося конъюкцией знаковых чисел, увеличены на один разряд по обеим ветвям, а в начальные условия первого цикла заносятся две единицы младшего разряда поправки, если числа (- -), и одна единица, если числа (-+), (+ -). Поэтому для приведенного примера с И - 6 при такой поправке (первого вида)регистры 1, 3, 5, 6 и 7, блок 8 разрешающих элементов и блок 9 кодирования должны иметь разрядность И + 2. На вход 19 обоих разрешающих элементов 10 данного разряда подается сигнал с выхода 20 соответствующего разряда регистра 7 поправки. ;, , . .. : Рассмотрим процесс работы с поправкой для приведенного примера (все группы одинаковы с м-2). Одновременно с записью Чисел б регистры 1 и 3 «сомножителей - в и и И+ 1 их разряды записываются знаки чисел, в и+ 1 разряЯ регистров 5 и 6 памяти записываются единицы начальных условий (каждому числу приписывается И+1 разряд соответствующего регистра памяти): две, если два отрицательных числа, одна, если одно отрицательное число, в.орТальные разряды регистров 5 и 6 записываются нули, кроме того, вИ+1 разряд регистра 7 введения поправки записывается единица, а в остальные нули, в VH- 2 разряды всех регистров записываются нули. После прохождения сигнала через блок 8 разрешающих элементов и 9 кодирования т.е. через один разрешающий элемент 10 и узел 23 кодирования группы ) на выходах 30, 29, 27 И 26 одновременно всех групп блока 9 кодирования образуются два числа результата первого цикла. Так как в И+1-М разряде регистра 7 введения поправки находит ся единица, с,выходов 21 и 22 раз-л., решающих элементов Ю на входыи+1-го разряда блока 9 кодирования подается значение поправки обеих .ветвей первого угла, а с выходов регистров 5 и 6 - начальные условия перво го цикла. После первого тактового импульса одновременно на все регист ры 1, 3 5 6 и 7 в регистрах 1 и 3 числа сдвигаются на один разряд с выводом младшего разряда справа и з писью нулей слева, в регистре 7 еди кица переписывается в И-й разряд, а; в VI Ч-1 -и записывается ноль, в регистры 5 и 6 записываются состояния .выходов блока 9 кодирования со сдви разряда. В освобождающихтом на два и 6 может ся разрядах регистров 5 быть записана любая информация. Работа устройства описывается дЛя группы в два разряда. После первого тактЬвого импульса с выходов 21 и 22 разрешающих элементов VI-го разряд выдается значение поправки второго угла, 9Ь+1 разрядах регистров 1 и 3 записайынули, на выходах блока 9 кодирования образуются два числа результата второго цикла и следующие два разряда общего результата умножения, С каждым циклом после очередного тактового импульса значение поправки смещается,, это смещение управляется единицей, проходящей «. через регистр 7 введения поправки. осталь ом перемножение чисел в дополнительных кодах не отличается от перемножения положительных чисел, ; .это ози,ачает, что процесс умножения одновр1еменно двух множимых на два множителя остается без изменения, количество циклов в обоих случаях ;,,раено-И.. ... . , ;..;.- Если 0 УСТРОЙСТВО с поправкой перемножаются положительные числа, . то в 1-и У1 разрядах регистров 1 м 3 при записи чисел записываются нули и вводимая поправка равна нули по обеим ветвям углов. В предлагае мом устройстве введение поправки 0912 производится автоматически по анализу знаковых разрядов перемножаемых чи сел без каких-либо изменений в процессе умножения. Положительный результат получается в прямом коде, отрицательный в допрлнительном. После того, как единица, проходящая через регистр 7, достигнет разряда на один старше младшего разряда, то это означает окончание цикла умножения. Следующим тактовым импульсом эта единица переписЬ18ается в И+1и разряд регистра 7 в регистре 7 для м-2 должна 6bitb то.пько одна единица), в регистры 1 и 3 записываются новые числа, в регистры 5 и 6 памяти запи .сываются начальные условия первого цикла и ПРОИЗВОДЯТСЯ соответствующие установки в исходное. Регистр 7 вве дения поправки является одновременно счетчиком циклов, так как в начале интервала умножения единица в нем находится в старшем(vi +1Км разряде, а конец ин т ерв ала ум ноже ния оп ред еляется появлением единицы в разряде на один старше младшего разряда регистра 7. Появление единицы в этом разряде регистра 7 дает разрешение на запись Новых чисел и установку устройства в исходное состояние. Установку в исходное можно осуществлять принудительно извне. Таким зом, специального блока управления для предлагаемого устройства не требуется. Таким образом предлагаемое устройство имеет более высокое по сравнению с известным быстродействие , заложенное в принципе работы, та как использование блока кодирования дает выигрыш е быстродействии на величину времени распространения еигнала переноса по всей разрядности :сумматора в известном устройстве,

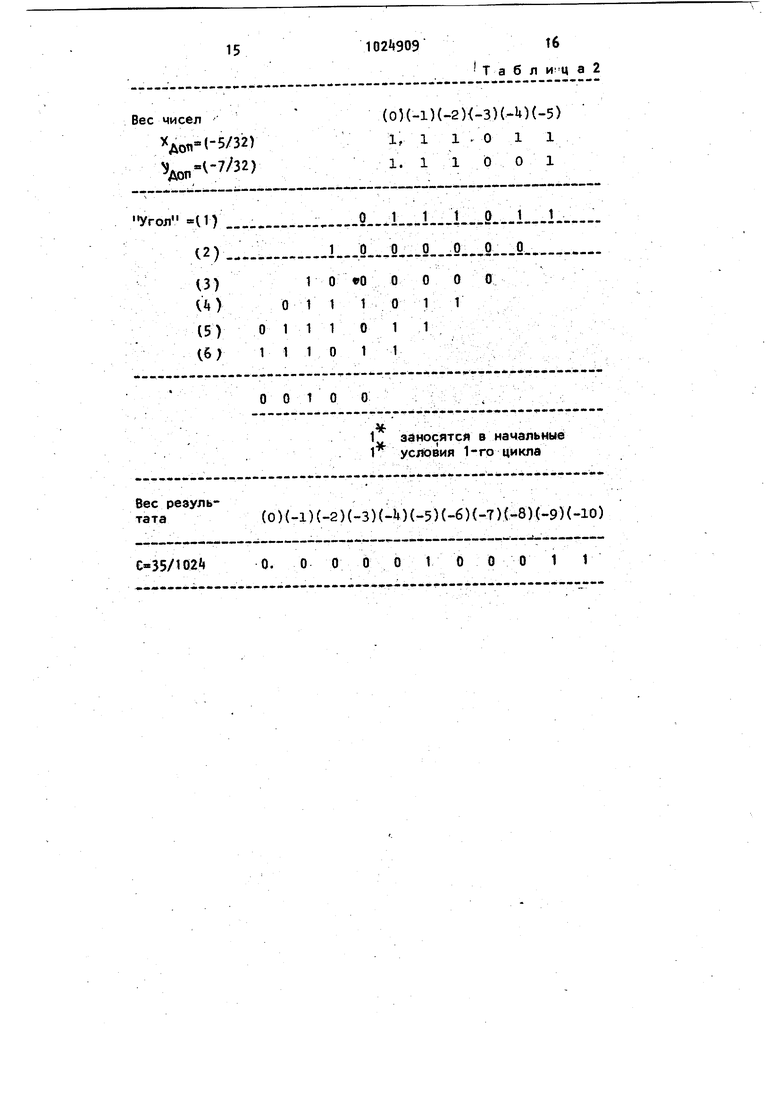

13102«909J

П р и м е ч а ни 04 Разряды вышедшие да разрядную сетку

езух1ьтатагне учитываются.

Таблица 1

15102 909t6

, Та б л а 2

«««.(.

Вес чисел(o)(-l)(-2)-3)(-U)(-5)

Aon(-5/32)1, 1 1 . О 1 1

V -7/32)1. 11 00 1 Вес результата

С-35/102А0. О 00 О 1 О 00 1 1

Л 1 заносятся в начальные

1 условия 1-го цикла (o)(.i)(-2)(3)(-U)(-5)(-6)(-.7)(-8)(-9)(-10) .

2 15 ef t2 Z1 22 W tk

Авторы

Даты

1983-06-23—Публикация

1981-09-03—Подача