Изобретение относится к вычисли тельной технике и мож-ет быть использовано в автоматизированных системах обработки информации при сопряжении устройств перекодировки информации, с периферийными устройствами.

Целью изобретения является повышение быстродействия вычислительной .системы за счет обеспечения сопряжеНИН источника и приемника информации, Ю писаны пятиэлементные коды регистроработающих с семи- и пятиэлементными кодами и обеспечения аппаратной перекодировки информации.

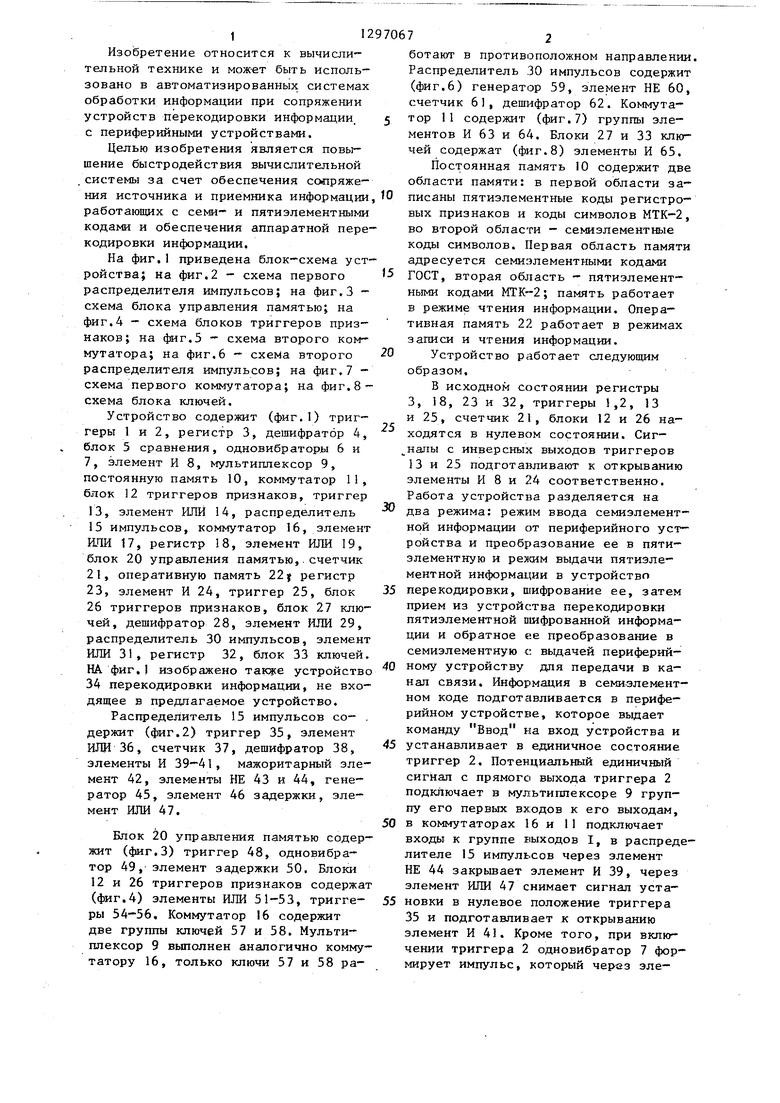

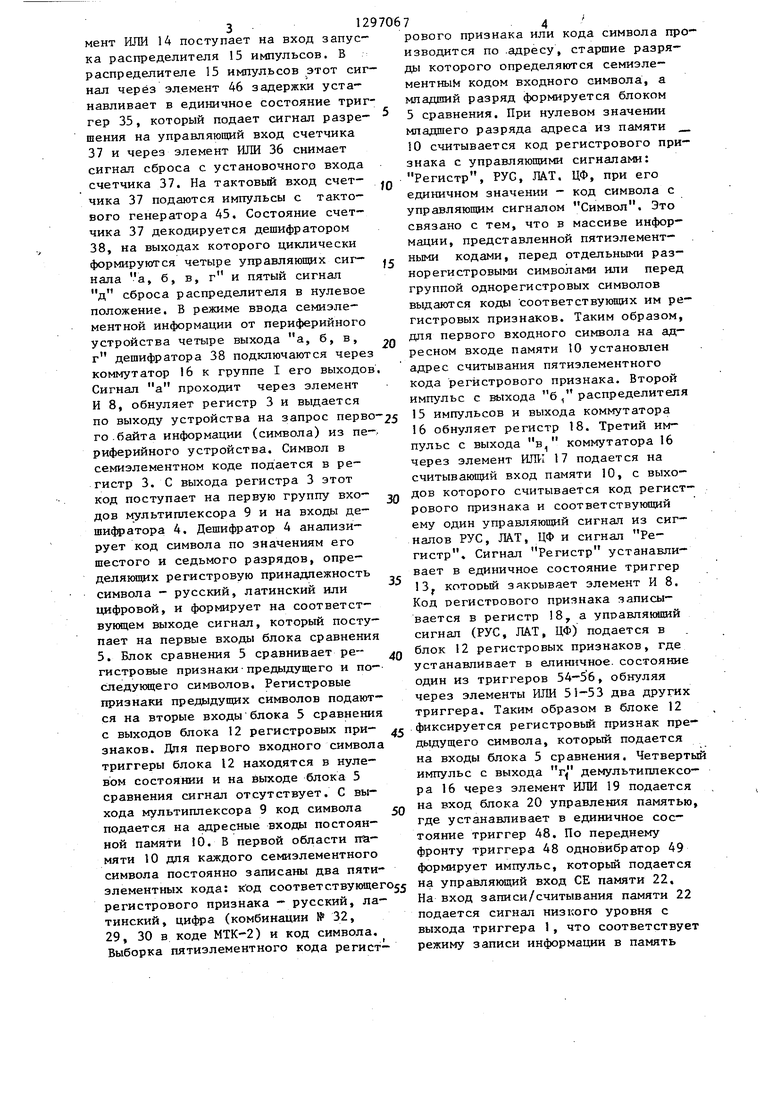

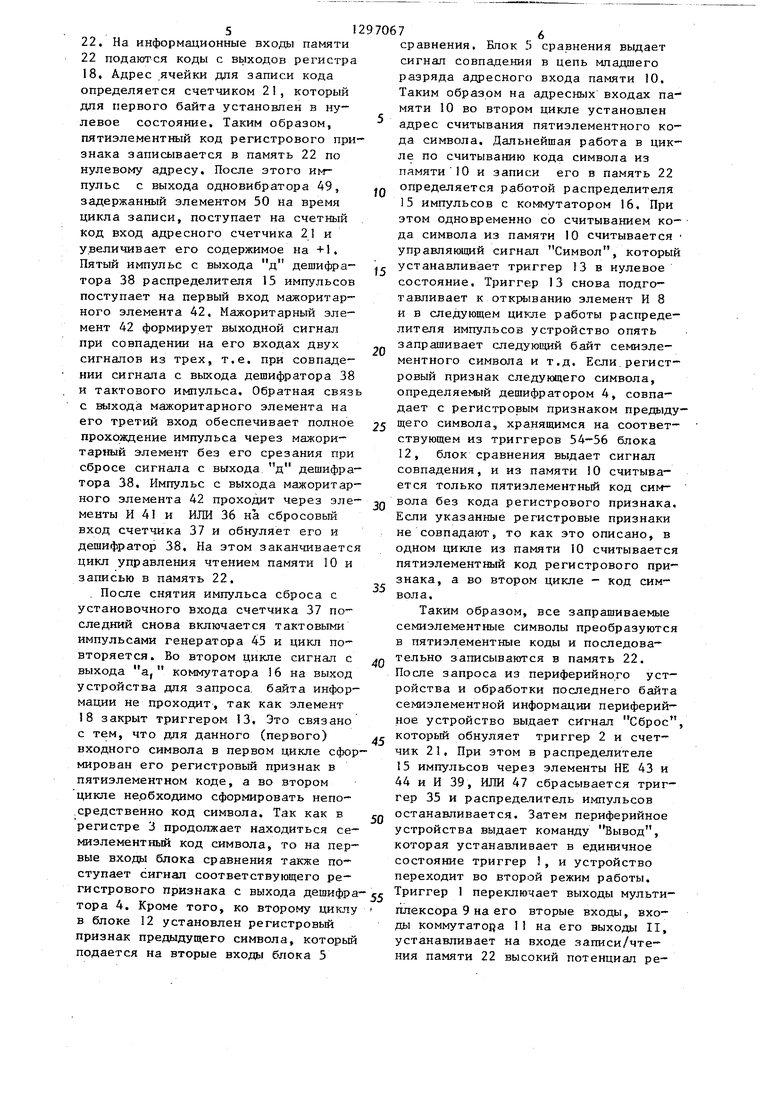

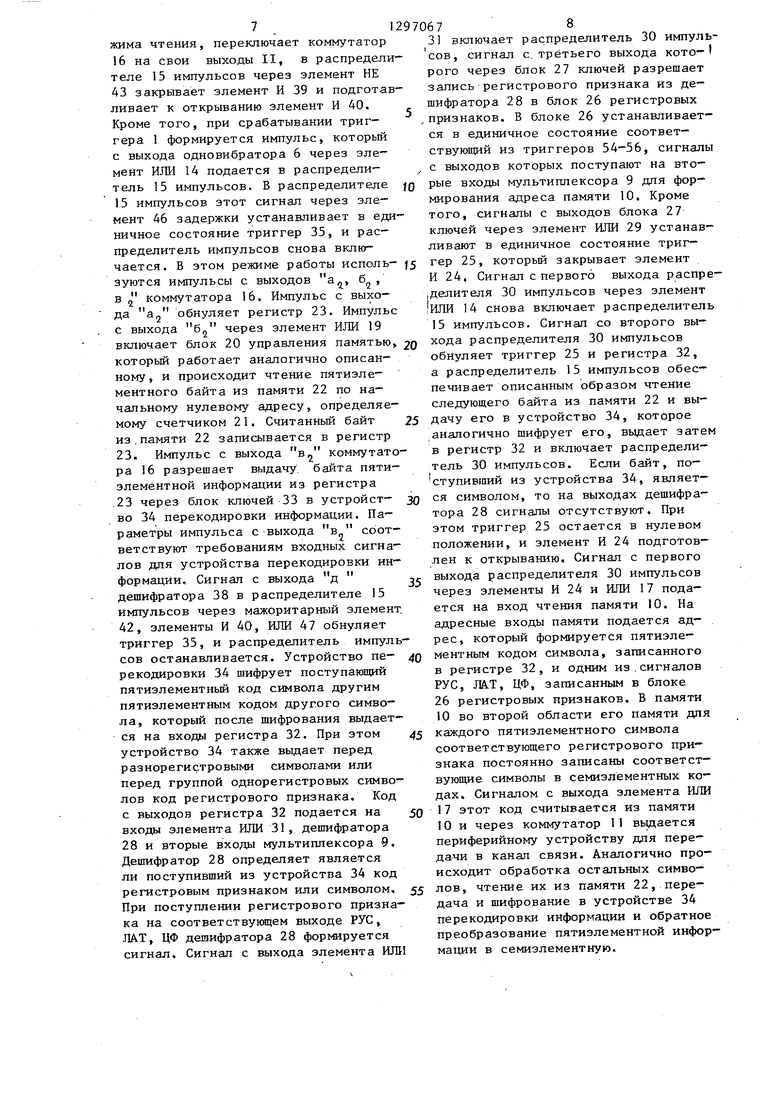

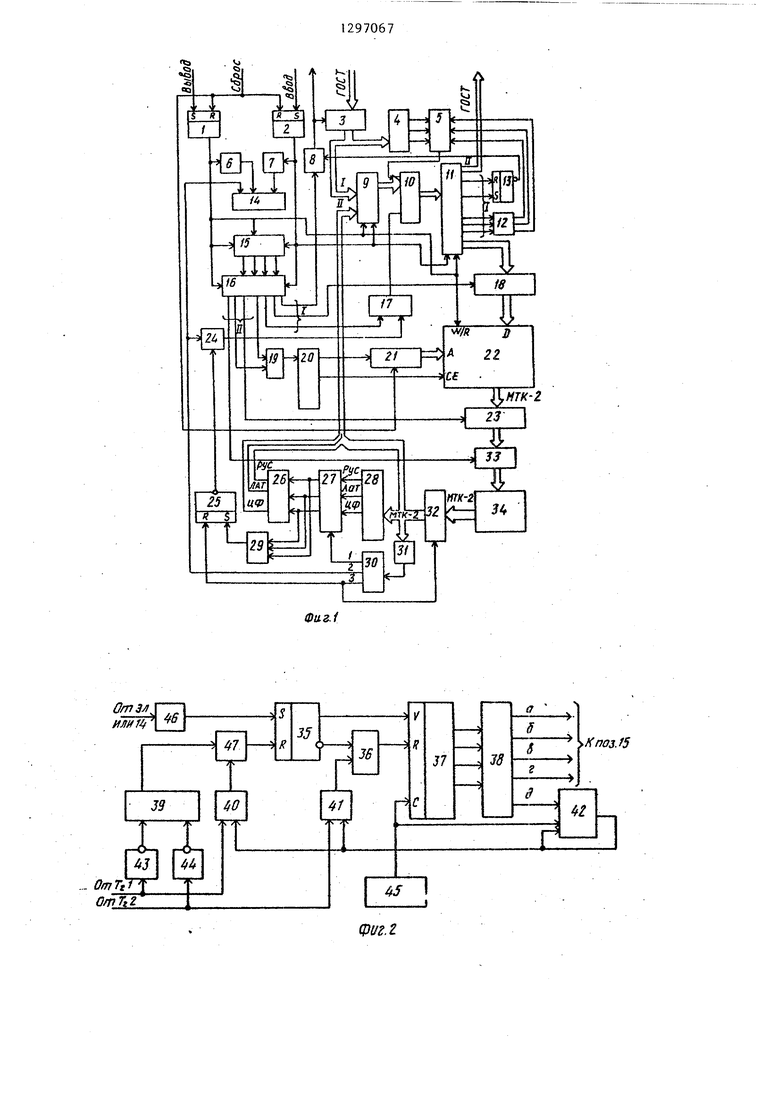

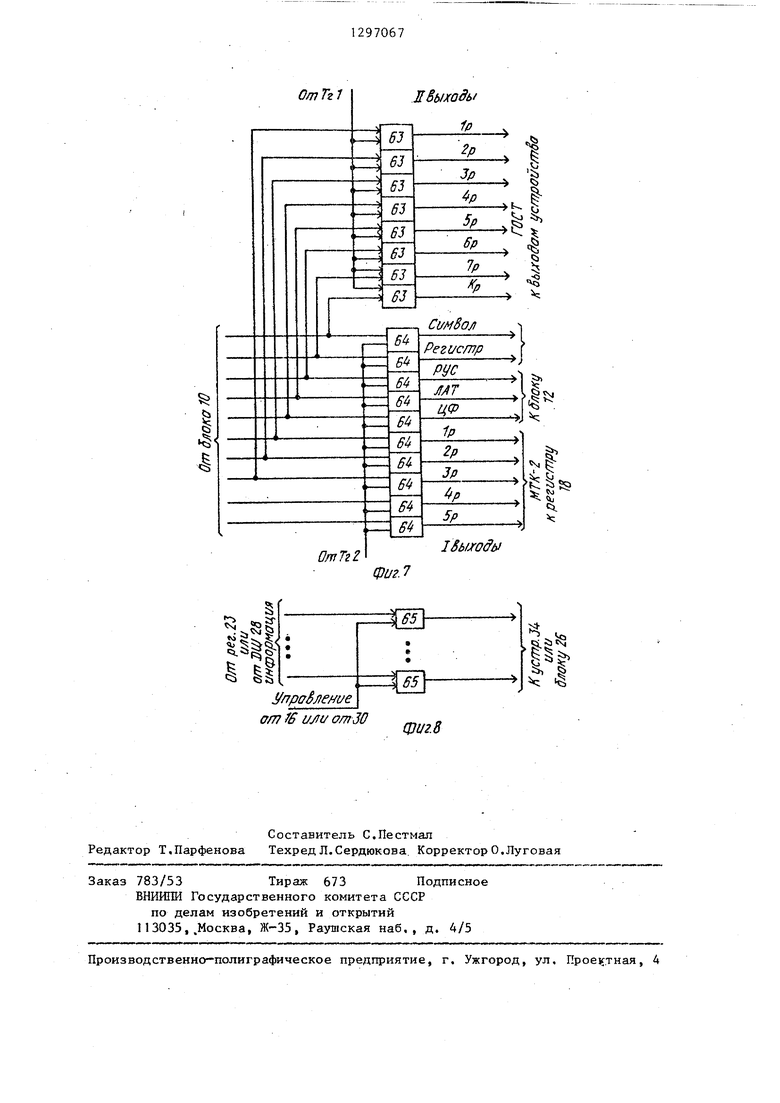

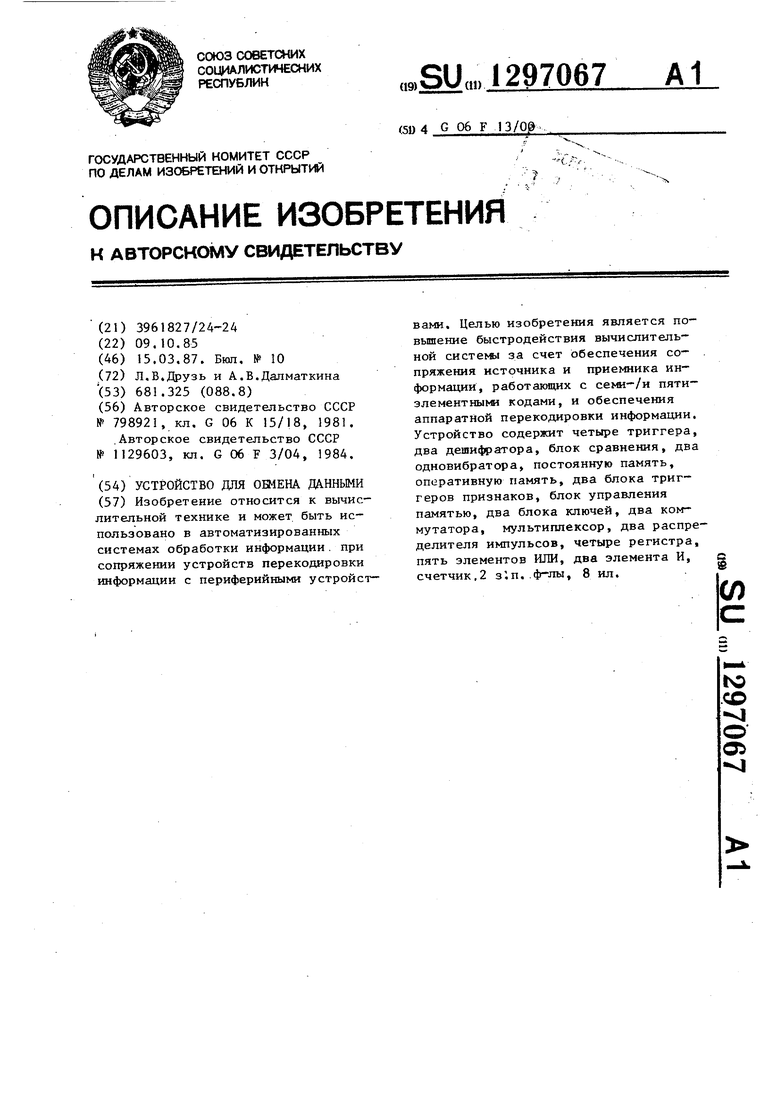

На фиг,1 приведена блок-схема устройства; на фиг.2 - схема первого распределителя импульсов; на фиг.З - схема блока управления памятью; на фиг.4 - схема блоков триггеров признаков; на фиг.5 - схема второго коммутатора; на фиг.6 - схема второго распределителя импульсов; на фиг,7 - схема первого коммутатора; на фиг,8 - схема блока ключей.

Устройство содержит (фиг,1) триггеры 1 и 2, регистр 3, дешифратор 4, блок 5 сравнения, одновибраторы 6 и 7, элемент И 8, мультиплексор 9, постоянную память 10, коммутатор И, блок 12 триггеров признаков, триггер 13, элемент ИЛИ 14, распределитель 15 импульсов, коммутатор 16, элемент ИЛИ 17, регистр 18, элемент ИЛИ 19, блок 20 управления памятью,.счетчик 21, оперативную память 22f регистр 23, элемент И 24, триггер 25, блок 26 триггеров признаков, блок 27 ключей, дешифратор 28, элемент ИЛИ 29, распределитель 30 импульсов, элемент ИЛИ 31, регистр 32, блок 33 кпючей. НА фиг. 1 изображено так|се устройство 34 перекодировки информации, не входящее в предлагаемое устройство.

Распределитель 15 импульсов со- . держит (фиг.2) триггер 35, элемент ИЛИ 36, счетчик 37, дешифратор 38, элементы И 39-41, мажоритарный элемент 42, элементы НЕ 43 и 44, генератор 45, элемент 46 задержки, элемент ИЛИ 47.

Блок 20 управления памятью содержит (фиг,3) триггер 48, одновибра- тор 49,- элемент задержки 50, Блоки 12 и 26 триггеров признаков содержат (фиг,4) элементы ИЛИ 51-53, триггеры 54-56. Коммутатор 16 содержит две группы ключей 57 и 58, Мультиплексор 9 выполнен аналогично коммутатору 16, только ключи 57 и 58 работают в противоположном направлении. Распределитель .30 импульсов содержит (фиг.6) генератор 59, элемент НЕ 60, счетчик 61, дешифратор 62. Коммутатор 11 содержит (фиг.7) группы элементов И 63 и 64. Блоки 27 и 33 ключей содержат (фиг.8) элементы И 65.

Постоянная память 10 содержит две области памяти: в первой области за-

вых признаков и коды символов МТК-2, во второй области - семиэлементные коды символов. Первая область памяти адресуется семиэлементными кодами

ГОСТ, вторая область - пятиэлементными кодами МТК-2; память работает в режиме чтения информации. Оперативная память 22 работает в режимах записи и чтения информации, Устройство работает следующим образом,

В исходном состоянии регистры 3, 18, 23 и 32, триггеры 1,2, 13 и 25, счетчик 21, блоки 12 и 26 находятся в нулевом состоянии. Сигналы с инверсных выходов триггеров 13 и 25 подготавливают к открыванию элементы И 8 и 24 соответственно. Работа устройства разделяется на два режима: режим ввода семиэлемент- ной информации от периферийного устройства и преобразование ее в пяти- элементную и реясим выдачи пятиэле- ментной информации в устройство

перекодировки, шифрование ее, затем прием из устройства перекодировки пятиэлементной пшфрованной информации и обратное ее преобразование в семиэлементную с выдачей периферийному устройству для передачи в канал связи, Шформация в семиэлемент- ном коде подготавливается в периферийном устройстве, которое вьщает команду Ввод на вход устройства и

устанавливает в единичное состояние триггер 2, Потенциальный единичный сигнал с прямого выхода триггера 2 подключает в мультиплексоре 9 группу его nepBiiix входов к его выходам,

в коммутаторах 16 и 11 подключает

входы к группе выходов I, в распределителе 15 импульсов через элемент НЕ 44 закрывает элемент И 39, через элемент ИЛИ 47 снимает сигнал установки в нулевое положение триггера 35 и подготавливает к открыванию элемент И 41, Кроме того, при включении тригг€фа 2 одновибратор 7 формирует импульс, который через зле-

мент ИЛИ 14 поступает на вход запуска распределителя 15 импульсов. В распределителе 15 импульсов этот сигнал через элемент 46 задержки устанавливает в единичное состояние триггер 35, который подает сигнал разре- шения на управляющий вход счетчика 37 и через элемент ИЛИ 36 снимает сигнал сброса с установочного входа счетчика 37. На тактовый вход счетчика 37 подаются импульсы с тактового генератора 45, Состояние счетчика 37 декодируется дешифратором 38, на выходах которого циклически формируются четыре управляющих сиг-

нала а, д

б, в, г и пятый сигнал

сброса распределителя в нулевое положение. В режиме ввода самиэле- ментной информации от периферийного устройства четыре выхода а, б, в, г дешифратора 38 подключаются через коммутатор 16 к группе I его выходов Сигнал а проходит через элемент И 8, обнуляет регистр 3 и выдается

30

по выходу устройства на запрос перво-25 15 импульсов и выхода коммутатора го.байта информации (символа) из пе-, риферийного устройства. Символ в семиэлементном коде подается в регистр 3. С выхода регистра 3 этот код поступает на первую группу входов ьгультигшексора 9 и на входы де- ши Ч атора 4. Дешифратор 4 анализирует код символа по значениям его шестого и седьмого разрядов, опре- деляюпщх регистровую принадогежность символа - русский, латинский или цифровой, и формирует на соответствующем выходе сигнал, который поступает на первые входы блока сравнения 5. Блок сравнения 5 сравнивает регистровые признаки-предыдущего и последующего символов. Регистровые признаки предыдущих символов подаются на вторые входы блока 5 сравнения с выходов блока 12 регистровых признаков. Для первого входного символа триггеры блока 12 находятся в нулевом состоянии и на выходе блока 5 сравнения сигнал отсутствует. С выхода мультиплексора 9 код символа подается на адресные входы постоянной памяти 10. В первой области памяти 10 для каждого семиэлементного символа постоянно записаны два пяти16 обнуляет регистр 18. Третий импульс с выхода в, коммутатора 16 через элемент ИЛИ 17 подается на считывающий вход памяти 10, с выходов которого считывается код регистрового признака и соответствующий ему один управляющий сигнал из сигналов РУС, ЛАТ, ЦФ и сигнал Регистр. Сигнал Регистр устанавливает в единичное состояние триггер 13j КОТОРЫЙ закрывает элемент И 8. Код регистрового признака записывается в регистр 18, а управляющий сигнал (РУС, ЛАТ, ЦФ) подается в блок 12 регистровых признаков, где устанавливает в елиничное. состояние один из триггеров 54-56, обнуляя через элементы ИЛИ 51-53 два других триггера. Таким образом в блоке 12 .фиксируется регистровьй признак предыдущего символа, который подается на входы блока 5 сравнения. Четвертый импульс с выхода демультиппексо- ра 16 через элемент ИЛИ 19 подается на вход блока 20 управления памятью, где устанавливает в единичное состояние триггер 48. По переднему фронту триггера 48 одновибратор 49

35

40

45

формирует импульс, который подается элементных кода: к од соответствующего55 управлякидий вход СЕ памяти 22. регистрового признака - русский, ла- На вход записи/считывания памяти 22 тинский, цифра (комбинации № 32,подается сигнал низкого уровня с

29, 30 в коде МТК-2) и код символа.выхода триггера 1, что соответствует

Выборка пятиэлементного кода регист- режиму записи информации в память

7067

4

5

0

рового признака или кода символа производится по .адресу, старшие разряды которого определяются семиэле- ментныМ кодом входного символа, а младший разряд формируется блоком 5 сравнения. При нулевом значении

мпадшего разряда адреса из памяти

10 считывается код регистрового признака с управляющими сигналами: Регистр, РУС, ЛАТ. ЦФ, при его единичном значении - код символа с управляющим сигналом Символ. Это связано с тем, что в массиве информации, представленной пятиэлемент- ными кодами, перед отдельными раз- нор егистровыми символами или перед группой однорегистровых символов выдаются коды соответствующих им регистровых признаков. Таким образом, для первого входного символа на адресном входе памяти 10 установлен адрес считывания пятиэлементного кода регистрового признака. Второй импульс с

выхода б / распределителя

15 импульсов и выхода коммутатора

16 обнуляет регистр 18. Третий импульс с выхода в, коммутатора 16 через элемент ИЛИ 17 подается на считывающий вход памяти 10, с выходов которого считывается код регистрового признака и соответствующий ему один управляющий сигнал из сигналов РУС, ЛАТ, ЦФ и сигнал Регистр. Сигнал Регистр устанавливает в единичное состояние триггер 13j КОТОРЫЙ закрывает элемент И 8. Код регистрового признака записывается в регистр 18, а управляющий сигнал (РУС, ЛАТ, ЦФ) подается в блок 12 регистровых признаков, где устанавливает в елиничное. состояние один из триггеров 54-56, обнуляя через элементы ИЛИ 51-53 два других триггера. Таким образом в блоке 12 .фиксируется регистровьй признак предыдущего символа, который подается на входы блока 5 сравнения. Четвертый импульс с выхода демультиппексо- ра 16 через элемент ИЛИ 19 подается на вход блока 20 управления памятью, где устанавливает в единичное состояние триггер 48. По переднему фронту триггера 48 одновибратор 49

22. На информационные входа памяти 22 подаются коды с выходов регистра 18. Адрес ячейки для записи кода определяется счетчиком 21, который для первого байта установлен в нулевое состояние. Таким образом, пятиэлементный код регистрового признака записывается в память 22 по нулевому адресу. После этого импульс с выхода одновибратора 49, задержанный элементом 50 на время цикла записи, поступает на счетный код вход адресного счетчика 21 и увеличивает его содержимое на +1. Пятый импульс с выхода д дешифратора 38 распределителя 15 импульсов поступает на первый вход мажоритарного элемента 42. Мажоритарный элемент 42 формирует выходной сигнал при совпадении на его входах двух сигналов из трех, т.е. при совпадении сигнала с выхода дешифратора 38 и тактового импульса. Обратная связь с выхода мажоритарного элемента на его третий вход обеспечивает полное прохождение импульса через мажоритарный элемент без его срезания при сбросе сигнала с выхода д дешифратора 38. Импульс с выхода мажоритарного элемента 42 проходит через элементы И 41 и ИЛИ 36 на сбросовый вход счетчика 37 и обнуляет его и дешифратор 38. На этом заканчивается цикл управления чтением памяти 10 и записью в память 22.

После снятия импульса сброса с установочного входа счетчика 37 последний снова включается тактовыми импульсами генератора 45 и цикл повторяется. Во втором цикле сигнал с выхода а, коммутатора 16 на выход устройства для запроса, байта информации не проходит, так как элемент 18 закрыт триггером 13. Это связано с тем, что для данного (первого) входного символа в первом цикле сформирован его регистровый признак в пятиэлементном коде, а во втором цикле необходимо сформировать непо- .средственно код символа. Так как в регистре 3 продолжает находиться се- мизлементный код символа, то на первые входы блока сравнения также поступает сигнал соответствующего ре-

гистрового признака с выхода дешифра- сгТриггер 1 переключает выходы мультитора 4. Кроме того, ко второму циклу плексора9 на его вторые входы, вхов блоке 12 установлен регистровыйды коммутатора II на его выходы II,

признак предыдущего символа, которыйустанавливает на входе записи/чте-

подается на вторые входы блока 5ния памяти 22 высокий потенциал ре

5

0

сравнения, Кпок 5 сравнения выдает сигнал совпа,цения в цепь младшего разряда адресного входа памяти 10. Таким образом на адресных входах па- мяти 10 во втором цикле установлен адрес считывания пятиэлементного кода символа. Дальнейшая работа в цикле по считыванию кода символа из памяти 10 и записи его в память 22 определяется работой распределителя 15 импульсов с коммутатором 16. При этом одновременно со считыванием кода символа из памяти 10 считывается управляющий сигнал Символ, который устанавливает триггер 13 в нулевое состояние. Триггер 13 снова подготавливает к открыванию элемент И 8 и в следующем цивле работы распределителя импульсов устройство опять запрашивает следующий байт семиэле- ментного символа и т.д. Если.регистровый признак следующего символа, определяемз1й дешифратором 4, совпадает с регистровым Признаком предыду- 5 щего символа, храняпщмся на соответствующем из триггеров 54-56 блока 12, блок сравнения выдает сигнал совпадения, и из памяти 10 считывается только пятизлементньй код символа без кода регистрового признака. Если указанные регистровые признаки не совпадают, то как это описано, в одном цикле из памяти 10 считывается пятиэлементшзй код регистрового признака, а во втором цикле - код символа.

Таким образом, все запрашиваемые семиэлементные символы преобразуются в пятиэлементные коды и последовательно записываются в память 22. После запроса из периферийно.го устройства и обработки последнего байта семиэлементной информации периферийное устройство выдает сигнал Сброс, который обнуляет триггер 2 и счетчик 21. При этом в распределителе 15 импульсов через элементы НЕ 43 и 44 и И 39, ИЛИ 47 сбрасывается триггер 35 и распреда1итель импульсов останавливается. Затем периферийное устройства выдает команду Вывод, которая устанавливает в единичное состояние триггер 1, и устройство переходит во второй режим работы.

0

5

0

5

0

жима чтения, переключает коммутатор 16 на свои выходы II, в распределителе 15 импульсов через элемент НЕ 43 закрывает элемент И 39 и подготавливает к открыванию элемент И 40. Кроме того, при срабатывании триггера 1 формируется импульс, который с выхода одновибратора 6 через эле мент ИЛИ 14 подается в распределитель 15 импульсов, В распределителе 15 импульсов этот сигнал через эле мент 46 задержки устанавливает в единичное состояние триггер 35, и распределитель импульсов снова вклю

чается. В этом режиме работы исполь- jf Р 5 который закрывает элемент

3уютен импульсы с выходов

Ч

в „ коммутатора 16. Импульс с выхоII

п

да

с выхода

а обнуляет регистр 23. Импульс

через элемент ИЛИ 19

включает блок 20 управления памятью, 20 °ДЗ распределителя 30 импульсов который работает аналогично описанобнуляет триггер 25 и регистра 32 а распределитель 15 импульсов обе печивает описанным образом чтение следующего байта из памяти 22 и в дачу его в устройство 34, которое аналогично шифрует его, вьщает за в регистр 32 и включает распредел тель 30 импульсов. Если байт, по ступивший из устройства 34, являе ся символом, то на выходах дешифр тора 28 сигналы отсутствуют. При этом триггер 25 остается в нулево положении, и элемент И 24 подгото лен к открыванию. Сигнал с первог

ному, и происходит чтение пятиэле- ментного байта из памяти 22 по начальному нулевому адресу, определяемому счетчиком 21. Считанный байт 25 из.памяти 22 записывается в регистр 23. Импульс с выхода в коммутатора 16 разрешает выдачу, байта пяти- элементной информации из регистра .23 через блок ключей 33 в устройст- ЗО во 34 перекодировки информации. Параметры импульса с выхода ЕП соответствуют требованиям входных сигналов для устройства перекодировки информации. Сигнал с выхода д

обнуляет триггер 25 и регистра 32, а распределитель 15 импульсов обес печивает описанным образом чтение следующего байта из памяти 22 и вы дачу его в устройство 34, которое аналогично шифрует его, вьщает зат в регистр 32 и включает распределитель 30 импульсов. Если байт, по- ступивший из устройства 34, является символом, то на выходах дешифратора 28 сигналы отсутствуют. При этом триггер 25 остается в нулевом положении, и элемент И 24 подготовлен к открыванию. Сигнал с первого

эг выхода распределителя 30 импульсов дешифратора 38 в распределителе 15 импульсов через мажоритарный элемент. 42, элементы И 40, ИЛИ 47 обнуляет триггер 35, и распределитель импульсов останавливается. Устройство пе- 0 рекодировки 34 шифрует поступающей пятиэлементный код символа другим пятиэлементным кодом другого символа, который после шифрования выдается на входы регистра 32. При этом 45 устройство 34 также вьщает перед разнорегистровыми символами или перед группой однорегистровых символов код регистрового признака. Код

50

с выходов регистра 32 подается на входы элемента ИЛИ 31, дешифратора 28 и вторые входы мультиплексора 9. Дешифратор 28 определяет является ли поступивший из устройства 34 код регистровым признаком или символом. При поступлении регистрового признака на соответствующем выходе РУС, ЛАТ, ЦФ дешифратора 28 формируется сигнал. Сигнал с выхода элемента ИЛИ

через элементы И 24 и ИЛИ 17 подается на вход чтения памяти 10. На адресные входы памяти подается адрес, который формируется пятиэле- ментным кодом символа, записанного в регистре 32, и одним из.сигналов РУС, ЛА.Т, ЦФ, записанным в блоке 26 регистровых признаков. В памяти 10 во второй области его памяти для каждого пятиэлементного символа соответствующего регистрового признака постоянно записаны соответствующие символы в семиэлёментных кодах. Сигналом с выхода элемента ИЛИ 17 этот код считывается из памяти 10 и через коммутатор 11 вьщается периферийному устройству для передачи в канал связи. Аналогично происходит обработка остальных симво- 55 лов, чтение их из памяти 22, передача и шифрование в устройстве 34 перекодировки информации и обратное преобразование пятиэлементной инфор ма1щи в семиэлементную.

31 включает распределитель 30 импуль- сов, сигнал с. третьего выхода кото- рого через блок 27 ключей разрешает запись регистрового признака из дешифратора 28 в блок 26 регистровых ,признаков. В блоке 26 устанавливается в единичное состояние соответствующий из триггеров 54-56, сигналы с выходов которых поступают на вторые входы мультиплексора 9 для формирования адреса памяти 10. Кроме того, сигналы с выходов блока 27 ключей через элемент ИЛИ 29 устанавливают в единичное состояние тригИ 24. Сигнал с первого выхода распре- |Делителя 30 импульсов через элемент ЬшИ 14 снова включает распределитель 15 импульсов. Сигнал со второго вы-

°ДЗ распределителя 30 импульсов

обнуляет триггер 25 и регистра 32, а распределитель 15 импульсов обеспечивает описанным образом чтение следующего байта из памяти 22 и выдачу его в устройство 34, которое аналогично шифрует его, вьщает зате в регистр 32 и включает распределитель 30 импульсов. Если байт, по- ступивший из устройства 34, является символом, то на выходах дешифратора 28 сигналы отсутствуют. При этом триггер 25 остается в нулевом положении, и элемент И 24 подготовлен к открыванию. Сигнал с первого

выхода распределителя 30 импульсов

через элементы И 24 и ИЛИ 17 подается на вход чтения памяти 10. На адресные входы памяти подается адрес, который формируется пятиэле- ментным кодом символа, записанного в регистре 32, и одним из.сигналов РУС, ЛА.Т, ЦФ, записанным в блоке 26 регистровых признаков. В памяти 10 во второй области его памяти для каждого пятиэлементного символа соответствующего регистрового признака постоянно записаны соответствующие символы в семиэлёментных кодах. Сигналом с выхода элемента ИЛИ 17 этот код считывается из памяти 10 и через коммутатор 11 вьщается периферийному устройству для передачи в канал связи. Аналогично происходит обработка остальных симво- лов, чтение их из памяти 22, передача и шифрование в устройстве 34 перекодировки информации и обратное преобразование пятиэлементной инфор- ма1щи в семиэлементную.

ормула

и

9

3 о

1297067

бретения

вт со с ти с ра уп то ко .пе вх хо вх хо со та вы вы ни ны по гр го во ны хо гр хо вх фо на пе ин ди

1. Устройство для обмена данными, содержащее два дешифратора, оперативную память, постоянную память, четыре триггера, первый распределитель иМпульсов, блок- сравнения, счетчик, первый коммутатор, первый элемент И, первый регистр, отличающееся тем, что, с целью повышения быстродействия, в него введены мультиплексор, второй коммутатор, второй распределитель импульсов, два блока триггеров признаков, три регистра, два блока ключей, блок управления памятью, второй элемент И, пять элементов ИЛИ, два одновибратора, причем единичные входы первого и второго триггеров являются входами вывода и ввода устройства дпя подключения к выходам вывода и ввода периферийного устройства соответственно, нулевой вход первого триггера соединен с нулевым входом второго триггера, с установочным входом счетчика и является установочным входом устройства дпя подключения к установочному выходу периферийного устройства, выход первого элемента И соединен с установочным входом первого регисра и является выходом запроса устроства для подключения к входу запроса периферийного устройства, группа

информационных входов первого регист-,, первого блока триггеров признаков.

ра и первая группа информационных выходов первого коммутатора образуют первые группы информационных входов и выходов устройства для подключения к группам информационных выходов и Q входов периферийного ус,тройства соответственно, группа выходов первого блока ключей и группа информационных входов второго регистра образуют вторые группы информационных 5 выходов и входов устройства для подключения к группам информационных входов и выходов источника информации соответственно, при этом выход первого триггера соединен с первыми 50 управ-пяющими входами мультиплексора, первого и второго коммутаторов, с первым разрещающим входом первого распределителя импульсов, с входом записи/чтения оперативной памяти, 55 с входом первого одновибратора, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом

группа информационных выходов кото го соединена с второй вход блока сравнения, первый выход второго коммутатора соединен с первым входом первого элемента И, второй вход которого с выходом т тьего триггера, нулевой и единичньш входы которого соединены с первым и вторым информационными выходами первого коммутатора, третья группа информационных выходов которого со динена с группой информационных вх дов третьего регистра, установочны вход которого соерднен с вторым вы ходом второго коммутатора, третий выход которого соединен с вторым входом второго элемента ИЛИ, четве тый и пятый выходы второго коммута ра соединены с первым и вторым вхо дами третьего элемента ИЛИ, выход которого соединен с входом запуска блока управления памятью, первый и второй выходы которого соединены с счетным : входом счетчика ц разре067

10

5

0

5

0

второго одновибратора, вход которого соединен с выходом второго триггера, с вторыми управляющими входами мультиплексора и первого коммутатора, с вторым разрешаю1цим входом первого распределителя импульсов, вторым управляющим входом второго коммутатора, группа информационных входов которого соединена с группой выходов .первого распределителя импульсов, вход запуска которого соединен с выходом первого элемента ИЛИ, третий вход которого соединен с первым выходом второго распределителя импульсов, с первым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом чтения постоянной памяти, группа адресных входов которой соединена с группой выходов мультиплексора, первая группа информационных входов которого соединена с группой выходов первого регистра и группой информационных входов дешифратора, группа выходов которого соединена с первой группой входов блока сравнения,.выход которого соединен с адресным входом постоянной памяти, группа ин- формационных выходов которой соединена с группой информационных входов первого коммутатора, вторая группа информационных выходов которого соединена с группой установочных входов

группа информационных выходов которого соединена с второй входов блока сравнения, первый выход второго коммутатора соединен с первым входом первого элемента И, второй вход которого с выходом третьего триггера, нулевой и единичньш входы которого соединены с первым и вторым информационными выходами первого коммутатора, третья группа информационных выходов которого соединена с группой информационных входов третьего регистра, установочный вход которого соерднен с вторым выходом второго коммутатора, третий выход которого соединен с вторым входом второго элемента ИЛИ, четвертый и пятый выходы второго коммутатора соединены с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с входом запуска блока управления памятью, первый и второй выходы которого соединены со счетным : входом счетчика ц разрешакадим входом оперативной памяти соответственно, группы выходов счетчика и третьего регистра соединены с группами адресных и информационных входов оперативной памяти соот- ветственно, группа информационных выходов которой соединены с группой информационных входов четвертого регистра, группа выходов которого соединена с группой информационных вхо- дов первого блока ключей, управляю- 1ций вход которого соединен с шестым выходом второго коммутатора, седьмой выход которого соединен с установочным входом четвертого регистра, груп па выходов второго регистра соединена с второй группой информационшлх входов мультиплексора, с группой информационных входов второго дешифратора и группой входов четвертого элемента ИЛИ, выход которого соединен с входом запуска второго распределителя импульсов, второй выход которого соединен с установочным входом второго регистра и с нулевым входом четвертого триггера:, выход которого соединен с вторым входом второго элемента И, группа выходов второго дешифратора соединена с группой информационных входов второго блока ключей, группа выходов которого соединена с группой входов пятого элемента ИЛИ и с группой установочных входов второго блока триггеров признаков, группа информационных выходов которого соединена с второй группой информационных входов мультиплексора, выход пятого элемента ИЛИ соединен с единичным входом четвертого триггера, третий выход вто-

рого распределителя импульсов соединен с управляющим входом второго блока ключей.

2.Устройство по п.1, отличающееся тем, что блок управления памятью содержит триггер, одновибратор и элемент задержки, причем единичный вход триггера является входом запуска блока управления памятью, выход элемента задержки соединен с нулевым входом триггера и является первым выходом блока управления памятью, выход одновибрато- ра соединен с входом элемента задержки и является вторым выходом блока управления памятью, выход триггера соединен с входом одновибратора,

3.Устройство по п,1, отличающееся тем, что блок триггеров признаков содержит три триггера и три элемента ИЛИ, причем выходы первого, второго и третьего триггеров образуют группу информационных выходов блока, единичные входы первого, второго и третьего триггеров образуют группу установочных входов блока, при этом в блоке нулевые входы первого, второго и третьего триггеров соединены с выходами первого, второго и третьего элементов ИЛИ соответственно, ничный вход первого триггера соединен с первыми входами второго и третьего элементов ИЛИ, единичный вход второго триггера соединен с первым входом первого элемента ИЛИ

и вторым входом третьего элемента ИЛИ, единичный вход третьего триггера соединен с вторыми входами первого и второго элементов ИЛИ,

От Tzi

V5 S

фиг.5

фиг. 6

OmTzl

5j

ЛВшоды 1P

63

S3

63

63

63

63

63

3p

P

5p

6p

7p

i - I

- I --I

1 - I

с

i

OmTzZ

6

6

6

ff

6

6

6

6

54

S4

иг.7

Регистр

С(/м8ол

рус

ЛАТ

ЦФ

1р

2р

ЗР

р

5р

о и

TSbiwffbi

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для приема и обработки информации | 1987 |

|

SU1444856A1 |

| Устройство для ввода информации | 1984 |

|

SU1238258A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации . при сопряжении устройств перекодировки информации с периферийными устройствами. Целью изобретения является повышение быстродействия вычислительной систеьы за счет обеспечения со- . пряжения источника и приемника информации, работающих с сеьм-/и пяти- элементным кодами, и обеспечения аппаратной перекодировки информации. Устройство содержит четыре триггера, два дешифратора, блок сравнения, два одновибратора, постоянную память, оперативную память, два блока трит- геров признаков, блок управления памятью, два блока ключей, два коммутатора, мультиплексор, два распределителя импульсов, четыре регистра, пять элементов ИЛИ, два элемента И, счетчик,2 з1п..ф-лы, 8 ил. (Л ю .;о о

(7/77 f6 от JO

Составитель С.Пестмал Редактор Т.Парфенова Техред Л.Сердюкова. Корректор О.Луговая

Заказ 783/53Тираж 673Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035,.Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Прое|гтная, 4

В Р I ч i

фиг.8

| Устройство для индикации | 1979 |

|

SU798921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| I | |||

Авторы

Даты

1987-03-15—Публикация

1985-10-09—Подача