та и, а выход первого дополнительного элемента ИЛИ подсоединен к втором входу второго дополнительного элемента ИЛИ, выходы сигнала Русский и сигнала Латинский второго дополнительного дешифратора подсоединены соответственно к второму входу первого элемента И и четвертому входу блока сравнения, пятьй и шестой входы которого подключены соответственно к выходам первого и второго элементов И, выход генератора импульсов подсоединен к второму входу третьего

элемента И и первому входу пятого элемента И, второй вход которого подключен к инверсному выходу первого триггера, а выход пятого элемента И подсоединен к второму входу третьего дополнительного элемента ИЛИ, выход первого блока задержки подсоединен через второй блок задержки к управляющему входу коммутатора, причем выходы первого элемента ИЛИ и выход пятого элемента И являются соответственно информационными и управляющим выходами устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления ленточным перфоратором | 1981 |

|

SU970402A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для преобразования последовательныхМНОгОРЕгиСТРОВыХ КОдОВ B пАРАллЕльНыЕ СКОНТРОлЕМ | 1979 |

|

SU840877A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для приема и обработки информации | 1987 |

|

SU1444856A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444782A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

УСТРОЙСТВО ДНЯ ПРЕОБРАЗОВАНИЯ КОДОВ, содержащее последовательно соединенные дешифратор и шифратор, а также регистр, блок сравнения, коммутатор, блок контроля по четности, генератор импульсов и элемент ИЛИ, причем информационные входы регистра являются информационньми входами устройства, отличающееся тем, что, с целью повышения достоверности преобразования кодов, в него введены последовательно соединенные первьй дополнительный дешифратор, первый дополнительный элемент ИЛИ, первый элемент НЕ и первый элемент И, последовательно соединенные второй дополнительный дешифратор, второй дополнительньй элемент ИЛИ и второй элемент И, последовательно соединенные третий дополнительный дешифратор, первый триггер, третий элемент И, третий дополнительный элемент ИЛИ, второй триггер, формирователь импульсов, первый блок задержки, четвертый элемент И и третий триггер, последовательно соединенные четвертый элемен г ИЛИ и четвертый триггер,: последовательно соединенные пятый .. элемент ИЛИ и пятый триггер, последовательно соединенные шестой элемент ИЛИ и шестой триггер, а также второй блок задержки, второй элемент НЕ и пятый элемент И, при этом выходы регистра подсоединены к объединенным соответствующим входам дешифратора, первого и второго допЪлнительных дешифраторов и блока контроля по четности, выход которого подсоединен к единичному входу второго триггера, выходы шифратора через коммутатор и первый элемент ИЛИ подсоединены к соответствующим входам третьего дополнительного дешифратора, выходы сигнала Русский, сигнала Цифра и сигнала Латинский третьего дополнительного дешифратора подсоединены соответственно к единичным входам четвертого, пятого и шестого триггеров, а выходы сигнала Русский и сигнала Цифра, выходы сигнала Русский и сигнала Латинский и выходы сигнала Цифра и сигнала Латинский третьего дополнительного дешифратора подсоеСАЭ динены соответственно к входам четвертого, пятого и шестого элементов ИЛИ, прямые выходы четвертого, пяСО ОО того и шестого триггеров подсоединены соответственно к первому, второму и третьему входам блока сравнения, выход которого подсоединен к второму входу четвертого элемента И, выход третьего дополнительного элемента ИЛИ подсоединен к сбросовому входу регистра и нулевому входу первого триггера, прямой выход которого подсоединен к дополнительному входу дешифратора, выход сигнала Пробел первого дополнительного дешифратора подсоединен через второй элемент НЕ к второму входу второго элемен

1

. Изобретение относится к технике передачи данных и может быть использовано в преобразователях данных

Известно устройство для преобразования кодов, содержащее последовательно соединенные дешифратор кодовых комбинаций и шифратор буквенных комбинаций, последовательно соединенные блок управления, блок анализа регистрового признака и шифратор цифровых комбинаций, второй вход которого подключен к выходу дешифратора кодовых комбинаций, второй выход которого подсоединен к второму входу блока управления,второй и тpeтий выходы блока управления подсоединены соответственно к вторым входам шифратора буквенных комбинаций и шифратора цифровых комбинаций l 3.

Недостатком данного устройства для преобразования кодов является низкая достоверность преобразования кодов.

Наиболее близким техническим решением к изобретению является устройство дпя преобразования кодов, содержащее последовательно соединенные дешифратор и шифратор, а также регистр, блок сравнения, коммутатор блок контроля по четности, генератор импульсов и элемент ИЛИ, причем информационные входы регистра являются информационными входами устройства, выход шифратора через блок контроля по четности и реверсивный счетчик подсоединен к информационному входу блока формирования ошибки, выход которого подсоединен к объединенным управляющим входам, коммутатора и дешифратора, .первьм

и второй вхойы блока сравнения . подсоединены соответственно к информационным входам и выходу регистра, первый и второй выходы блока сравнения подсоединены к первому и второму дополнительным управлякшщм входам коммутатора, первый, второй и третий тактовые входы которого подключены к соответствующим выходам генератора импульсов, дополнительный

выход которого подсоединен к тактовому входу реверсивного счетчика, второй управляющий вход которого подключен к выходу элемента ИЛИ, первый вход которого подключен к

второму выходу дешифратора, первый выход коммутатора подсоединен к объединенным входам Символ шифратора и блока формирования ошибки, второй выход коммутатора подсрединен к второму входу элемента ИЛИ, управляющему входу регистра и входу Регистр шифратора, а информационные входы регистра подключены к соответствующим информационным входам дешифратора,дПричем выход шифратора и третий выход коммгутатора являются соответственно информационным и управляющими выходами устройстваП23.

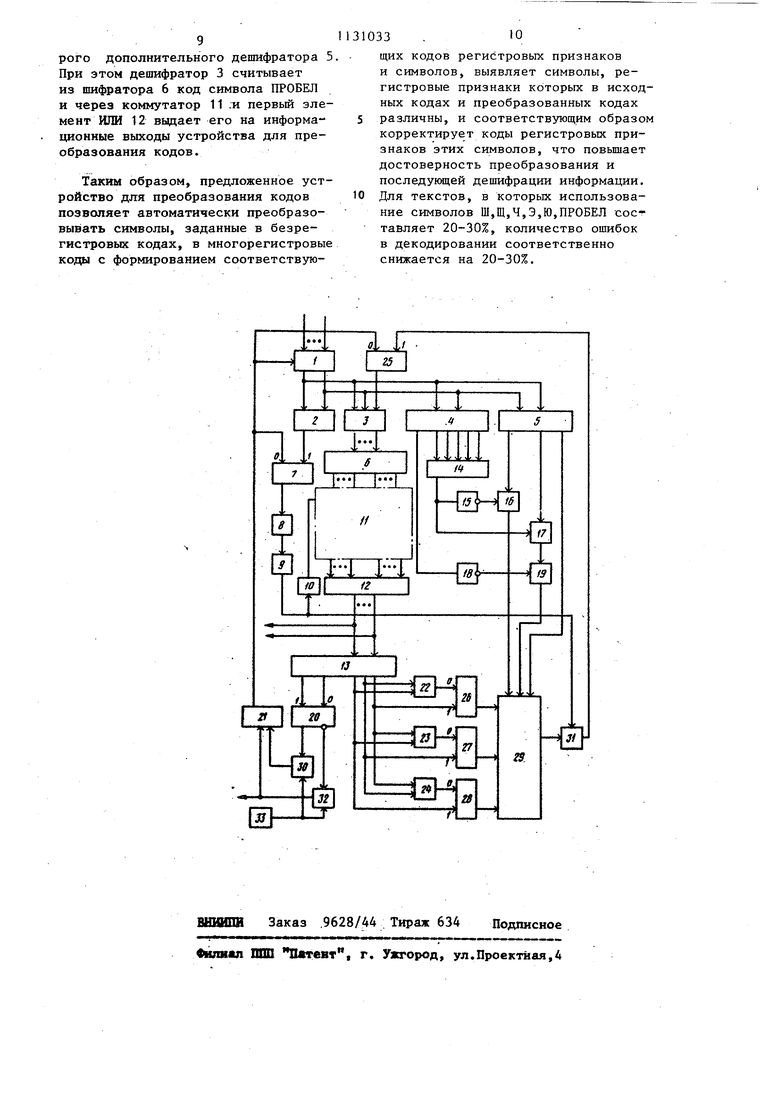

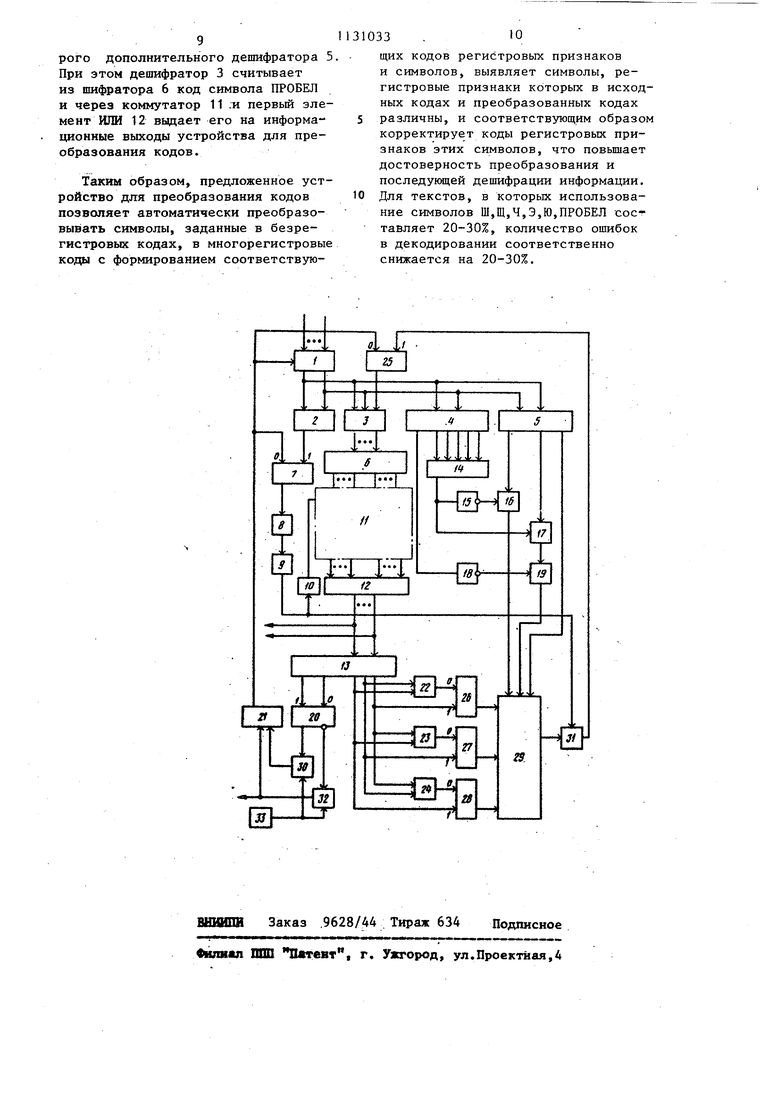

Недостатком известного устройства для преобразования кодов является низкая достоверность преобразова3ния кодов вследствие отсутствия ан лиза входного кода для выявления символов Ш,1Ц,Э,Ю,Ч и ПРОБЕЛ. Цель изобретения - повьпиение до верности преобразования кодов, Цель достигается тем, что в уст ройство для преобразования кодов, содержащ1ее последовательно соединенные дешифратор и шифратор, а также регистр, блок сравнения. коммутатор, блок контроля по четно ти, генератор импульсов и элемент ИЛИ, причем информационные входы регистра являются информационными входами устройства, введены последовательно соединенные, первый дополнительный дешифратор, первый дополнительный элемент ИЛИ, первый элемент НЕ и первый -элемент И, последовательно соединенные второй дополнительный дешифратор, второй дополнительней элемент ИЛИ и второй элемент И, последовательно соединенные третий дополнительный дешифратор, первый триггер, третий элемент И, третий дополнительный элемент ИЛИ, второй триггер, формирователь импульсов, первый блок задержки, четвертый элемент И и третий триггер, последовательно соединенные четвертый элемент ШШ и четвертый триггер, последователь но соединенные пятьй элемент ИЛИ и пятый триггер, последовательно соединенные шестой элемент ИЛИ и шестой триггер, а также второй бло задержки, второй элемент НЕ и пяты элемент И, при этом выходы регистр подсоединены к объединенным соответствующим входам дешифратора, пе вого и второго дополнительных деши раторов и блока контроля по четно ти, выход которого подсоединен к единичному входу второго триггера выходы шифратора через коммутатор и первый элемент ИЛИ подсоединены соответствующим входам третьего до полнительного дешифратора, выходы сигнала Русский, сигнала Цифра и сигнала Латинский третьего доп нительного дешифратора подсоединен соответственно к единичным входам четвертого, пятого и шестого триггерое, а выходы сигнала Русский .и сигнала Цифра, выходы сигнала Русский и сигнала Латинский и выходы сигнала Цифра и сигнала Латинский третьего дополнитрльно го дешифратора подсоединены соот3ветственно к входам четвертого, пятого и шестого элементов ИЛИ, прямые выходы четвертого, пятого и шестого триггеров подсоединены соответственно к первому, второму и третьему входам блока сравнения, выход которого подсоединен к второму входу четвертого элемента И, выход-третьего дополнительного элемента ИЛИ подсоединен к сбросовому входу регистра и нулевому входу первого триггера, прямой которого подсоединен к дополнительному входу дешифратора, выход сигнала Пробел первого дополнительт ного дешифратора подсоединен через второй элемент НЕ к второму входу второго элемента И, а выход первого дополнительного элемента ИЛИ подсоединен к второму входу второго дополнительного элемента ИЛИ, выходы сигнала Русский и сигнала Латинский второго дополнитель- . ного дешифратора подсоединены соответственно к второму входу первого элемента И и четвертому входу блока сравнения, пятый и шестой входы ко-, торого подключены соответственно к выходам первого и второго элементов И, выход генератора импульсов подсоединен к второму входу третьего элемента И и первому входу пятого элемента И, второй вход которого подключен к инверсному выходу первого триггера, а выход пятого элемента И подсоединен к второму входу третьего дополнительного элемента ИЛИ, выход первого блока задержки подсоединен через второй блок задержки к управляннцему входу коммутатора, причем выходы первого элемента ИЛИ и.выход пятого элемента И являются соответственно информационными и управляюоцш :выходами устройства. На чертеже приведена структурная электрическая схема устройства для преобразования кодов. Устройство для преобразования кодов содержит регистр 1, блок 2 контроля по четности, дешифратор 3, первый дополнительный дешифратор 4, вто-, oй дополнительный дешифратор 5, шифратор 6, второй триггер 7, формирователь 8 имщшьсов, первый блок 9 задержки, второй блок 10 задержки, коммутатор 11, первый элемент ИЛИ 12, третий дополнительный дешифратор 13, первый дополнительный элемент ИЛИ 14, первый элемент НЕ 15, первый элемент И 16, второй дополнительньм элемент ИЛИ второй.элемент НЕ 18, второй элемент И 19, первый триггер 20, трети дополнительный элемент ИЛИ 21, четвертый элемент ИЛИ 22, пятьй элемент ИЛИ 23, шестой элемент ИЛИ 24, третий триггер 25, четвертьй триггер 26, пятый триггер 27, шестой триггер 28, блок 29 сравнения, третий элемент И 30, четвертый элемент И 31, пятый элемент И 32, генератор 33 импульсов. Устройство для преобразования ко дов работает следующим образом. В исходном состоянии регистр 1, первый триггер 20, второй триггер 7 третий триггер 25, четвертый; пятый и шестой триггеры 26-28 обнулены , Первый триггер 20 подготавливает к открыванию пятый элемент И 32. Пр включении генератора 33 импульсов п вый его импульс открывает пятый эле мент И 32 и вьщает по управляющему выходу устройства для преобразования кодов сигнал запроса информации во внешнее устройство и через трети . дополнительньй элемент ИЛИ 21 под тверждает нулевое состояние регистра 1 второго триггера 7 и третьего триггера. 25. По запросу информации в регистр 1 поступает код символа в безрегистровом коде (например,по ГОСТ 13052-74). Этот код удерживает ся внешним устройством на входах регистра 1 до вьщачи следующего -импульса запроса информации. С выхо дов регистра 1 этот код подается на входы блока 2 контроля по четности и входы дешифратора 3 и первого и второго дополнительных дешифраторов 4 и 5. В блоке 2 контроля по четности комбинация входного символа проверяется по четности и при пра ильной четности сигналом с выхода блока 2 контроля по четности, второй триггер 7 устанавливается в единично состояние. Дешифратор 3 при нулевом состоянии третьего триг гера 25, т.е. при нулевом значении младшего разряда адреса, выбирает из шифратора 6 код регистрового признака« который подается с выход шиф|)атора 6 на входы коммутатора 1 Первый дополнительный дешифратор 4 аналиэирует входной, код для выявления символов Ш,Щ,Ч,Э,Ю,ПРОВЕЛ.Вто рой дополнительный дешифратор 5 анализирует входной код по значениям его разрядов, определяющих регистровую принадлежность преобразуемого символа, и формирует соответствующий сигнал Русский, Цифра, Латинский на выходах Русский, Циф,ра и Латинский. Если преобразуемьй символ не является символом из группы Ш,Щ,Ч,Э,Ю,ПРОБЕЛ, то на выходах первого дополнительного дешифратора 4 и первого дополнительного элемента ИЛИ 14 сигналы не формируются, первьй элемент НЕ 15 и второй элемент НЕ 18 остаются открытыми и подготавливают к открыванию первьй элемент И 16 и второй элемент И 19. При этом с выходов второго дополнительного дешифратора 5 сигнал Русский через первый элемент И 16 или сигнал Цифра через второй дополнительньй элемент ИЛИ 17 и второй элемент И 19, или сигнал Латинский непосредственно подаются в блок 29 сравнения. При срабатьшании второго триггера 7 потенциальньй сигнал с его прямого выхода преобразуется формирователем 8 импульсов в импульс, которьй через первьй блок 9 задержки подается на четвертый элемент И 31 для считывания из блока 29 сравнения сигнала результата сравнения регистровых признаков предьщущего и последукндего символов преобразуемого кода. Первьй и второй блоки 9 и 10 задержки, учитьшают время переходных процессов сигнала при преобразовании кода. Так как четвертьй, пятый и шестой триггеры 26-28 находятся в нулевом состоянии, то блок 29 сравнения не вьщает сигнал совпадения на вход четвертого элемента И 31, а третий триггер 35 остается в нулевом остоянии. Далее импульс, с вьгхода первого блока 9 задержки через второй блок 10 задержки подается на управляющий вход коммутатора 11 и осзтцествляет считьтание кода регистрового признака на входы первого элемента ИЛИ 12. С выходов первого элемента ИПИ 12 этот код поступает на информационные выходы устройства для преобразования кодов и на входы третьего дополнительного дешифратора 13. - В третьем дополнительном дешиф-раторе 13 сигнал на одном из выхоов, подключенных к -первому тригге7- n py 20, определяет соответственно вывод из выходов, подключенньгк к первому триггеру 20, определяет соот ветственно вывод из шифратора 6 кода регистрового признака или символа, а выходы Русский, Цифра и Латинский формируют сигналы Русский, Цифра, Латинский в случае вывода кода соответствующего регистрового признака. Таким образом, при выводе регистрового призндка в третьем дополнительном дешиф раторе 13 формируется сигнал на выходе, подсоединенном к единичному входу первого триггера 20. При это в единичное состояние устанавливается первый триггер 20, которьй закрывает пятьш элемент И 32 и подг тавливает к открыванию трефий элемент И 30. Кроме того, сигнал на одном из выходов Русский, Циф ра и Латинский третьего дополни тельного дешифратора 13 устанавлива ет в единичное состояние соответствующий четвертьй, пятый или шесто триггер 26-28 и обнуляет через соот ветствующие четвертый, пятый, шестой элементы ИЛИ 22-24 два из трех: четвертый, пятьш и шестой триггеры 26-28. Следующий импульс с выход генератора 33 импульсов через трети элемент И 30 и третий дополнительный элемент ИЛИ 21 обнуляет второй триггер 7, третий триггер 25 и регистр 1. По окончании действия этог импульса в регистре 1 вновь восстанавливается код входного символа поступившего в предыдущем цикле, та как внешнее устройство удерживает этот код на входах регистра 1 до по ступления следующего сигнала запроса информации, и описанный процесс повторяется. При этом на входах бло ка 29 сравнения совпадают сигналы, соответствукщие регистровым признакам, вследствие чего, с его выхода через четвертый элемент И 31 считывается сигнал совпадения, который устанавливает третий триггер 25 в единичное состояние. В этом случае шифратор 6 формирует символ в преобразованном коде, который считы вается с выходов шифратора 6 через коммутатор 11 на соответствукщие входы первого элемента ИПИ 12. При выводе с выходов первого элемен та ИЛИ 12 символа в преобразованном коде в третьем дополнительном дешиф раторе 13 формируется сиграл, при 38 котором первый триггер 20 устанавливается в нулевое положение, третий элемент И 30 закрьгоается, пятый элемент И 32 подготавливается к открыванию. В следующем цикле импульс генератора 33 импульсов через пятый элемент И 32 вновь вьвдает сигнал запроса во внешнее устройство, которое сбрасывает предыдущий код символа с входов регистра 1 и подает на эти входы код следукядего символа, описанный процесс повторяется. Если регистровый признак следующего поступившего символа, определяемый вторым дополнительным дешифратором 5, совпадает с регистровым признаком предыдущего символа, нящимся в четвертом триггере 26, пятом триггере 27 или шестом триг- , гере 28, блок 29 сравнения вьщает сигнал совпадения и из шифратора 6 считьгеается только символ преобразованного кода без кода регистрового признака. Если указанные регистро1зые признаки не совпадают, то сначала, в одном цикле входной код преобразуется в код регистрового признака, а затем во втором цикле - в код символа преобразованного кода. В случае, если входной символ явлается одним из символов Щ,Щ,Ч,Э,Ю на соответствующем выходе первого дополнительного дешифратора 4 формируется сигнал, которьй через элемент ИЛИ 14 и первый элемент НЕ 15 закрывает первый элемент И 16. При этом блокируется выход Русский второго дополнительного дешифратора 5, а через второй дополнительный элемент ИЛИ 17 и второй элемент И 19 на шестой вход блока 29 сравнения поступает сигнал Цифра. Это соответствует принадпежности символов Ш,Щ,Ч,Э,Ю цифровому регистру в преобразованном коде. Если перед этими символами следования русские символы, то произойдет смена регистровых признаков Русский на Цифра,выводимых из устройства, и указанные символы будут правильно декодированы в преобразованных кодах. В слзгчае, когда входной символ является символом ПРОБЕЛ, принадлежащий цифровому регистру, на выходе Пробел первого дополнительного дешифратора 4 формируется . сигнал, который закрывает через втог рой элемент НЕ 18 второй элемент И 19 и блокирует выход Цифра второго дополнительного дешифратора При этом дешифратор 3 считывает из шифратора 6 код символа ПРОБЕЛ и через коммутатор 11 .и первый эле мент ИЛИ 12 вьадает его на информационные выходы устройства для преобразования кодов. Таким образом, предложенное уст ройство для преобразования кодов позволяет автоматически преобразовывать символы, заданные в безрегистровых кодах, в многорегистровы коды с формированием соответствую3 . 10 щих кодов регистровых признаков и символов, выявляет символы, регистровые признаки которых в исходных кодах и преобразованных кодах различны, и соответствующим образом корректирует коды регистровых признаков этих символов, что повышает достоверность преобразования и последующей дешифрации информации. Для текстов, в которых использование символов Ш,Щ,Ч,Э,Ю,ПРОБЕЛ составляет 20-30%, количество ошибок в декодировании соответственно снижается на 20-30%,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования кодов | 1972 |

|

SU480075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для преобразования последовательныхМНОгОРЕгиСТРОВыХ КОдОВ B пАРАллЕльНыЕ СКОНТРОлЕМ | 1979 |

|

SU840877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-07-12—Подача