(Л

так и по телеграфным линиям связи. Целью изобретения является расширение области применения устройства за счет обеспечения возможности записи массивов информации в безрегистровых и многорегистровых кодах. Устройство содержит два блока I и 15 памяти, триггеры 4,5,9,17 и 20, счетчики 7 и 21, дешифратор 13, формирователи 2,6,16 и 22, преобразователь I1 семиэлементного кода символа в пятиэлементный, регистры 8 и 12 данных, регистр 10 признаков, блок 14 сравнения, распределитель 27 импульсов, элементы И 25 и 26, элементы 3 и 1 9 задержки и элементы ИЛИ 23 и 24. В блок 15 памяти записывается информация в семиэлементном коде сим

74279

волов, которая при считывании из блока 15 преобразуется с помощью преобразователя 11 и записывается в блок 1 памяти в пятизлементном коде сим-, волов. В процессе преобразования формируются регистровые признаки (русский, латинский или цифра), которые содержатся в регистре 10 признаков и записываются вместе с кодом символа в блок I памяти, с выходов которого информация считывается. Формируемые преобразователем 11 сигналы Регистр и Символ, а также сигналы с выходов распределителя 27 импульсов управляют циклами чтения из блока 15 и записи в блок 1. Конец преобразования кода символа фиксируется дешифратором 13. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для приема и обработки информации | 1987 |

|

SU1444856A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444782A1 |

| Устройство для управления ленточным перфоратором | 1981 |

|

SU970402A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства в системах сбора и регистрации информации как по линиям стандартного интерфейса.

1

Изобретение относится к вычислительной технике и может быть использовано Б качестве буферного запоминающего устройства в системах сбора и регистрации информации как по линиям стандартного интерфейса, так и по телеграфным линиям связи.

Цепью изобретения является расширение области применения устройства путем обеспечения возможности записи массивов информации в безрегистровых и многорегистровых кодах.

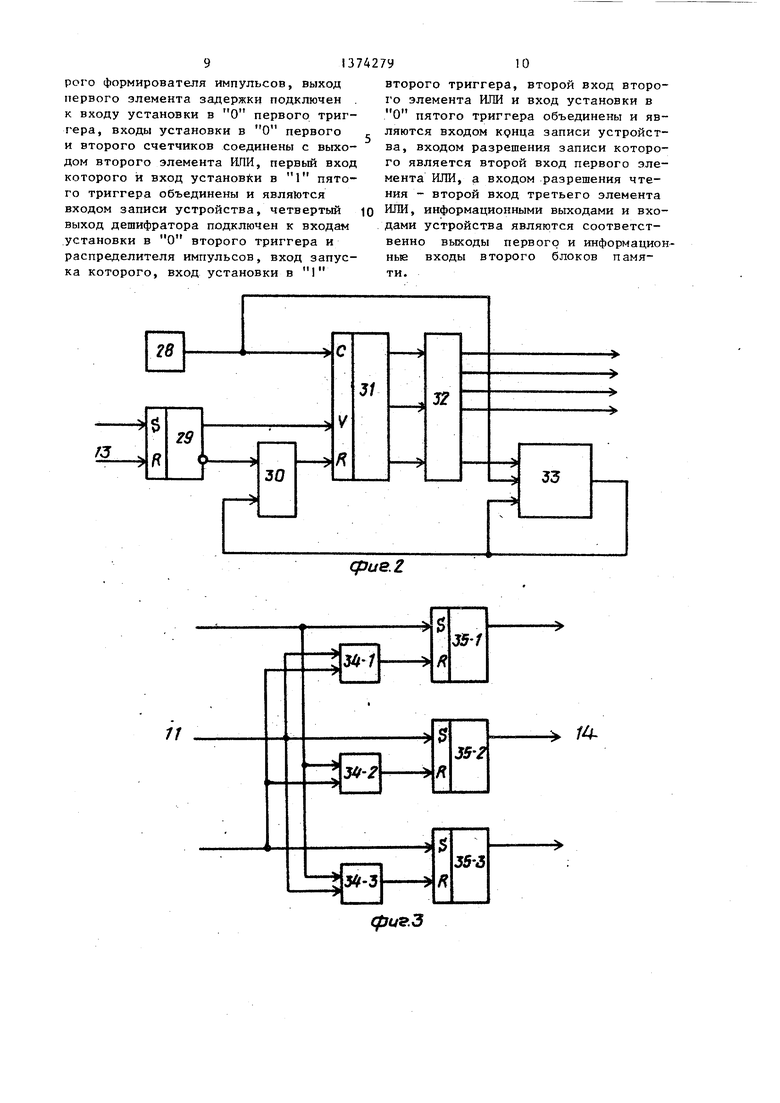

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - 4 - функциональные схемы соответственно распределителя импульсов, блока памяти регистровых признаков и блока сравнения.

Устройство содержит (фиг.1) блок I памяти, первый формирователь 2 импульсов, первый элемент 3 задержки, первый 4 и второй 5 триггеры, второй формирователь 6 импульсов, первый счетчик 7, первый регистр 8 данных, третий триггер 9, регистр 10 признаков, преобразователь II семиэлементного кода символа в пятиэлементный, второй регистр 12 данных, дешифратор 13, блок 14 сравнения, втЬрой блок 15 памяти, третий формирователь 16 импульсов, четвертый триггер 17, первый элемент ИЛИ 18, второй элемент

19 задержки, пятый триггер 20, второй счетчик 21, четвертый формирователь 22 импульсов, второй 23 и третий 24 элементы ИЛИ, первый 25 и второй 26 элементы И и распределитель 27 импульсов.

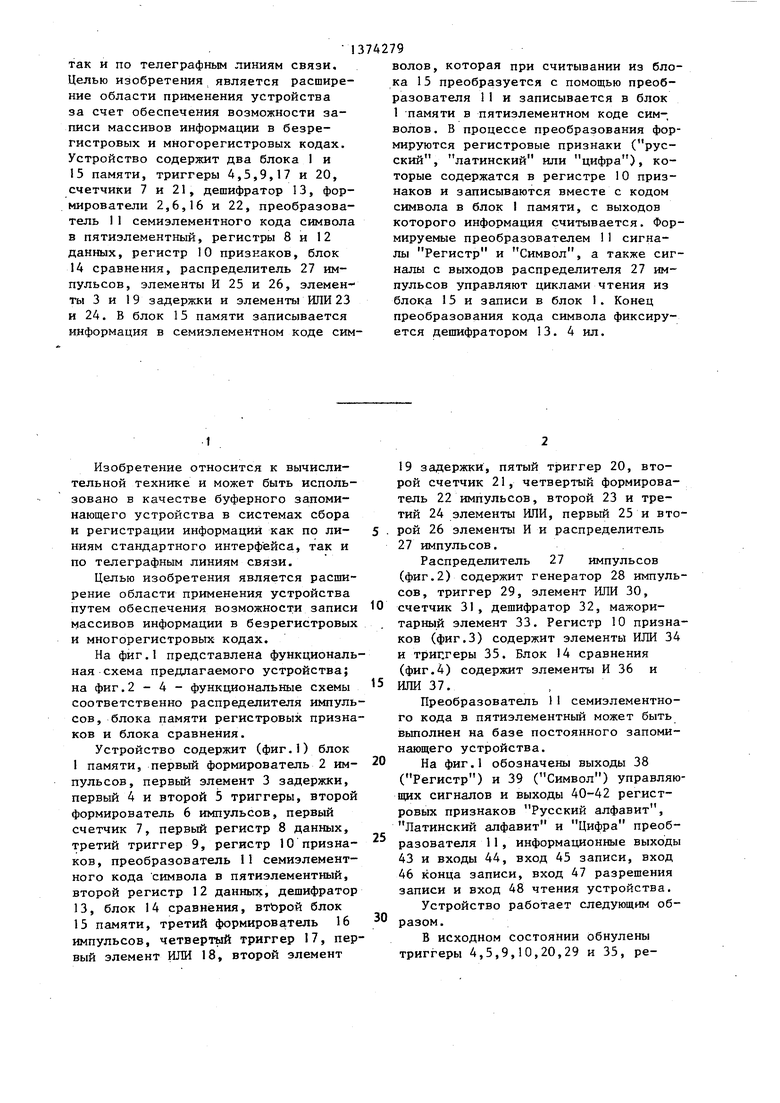

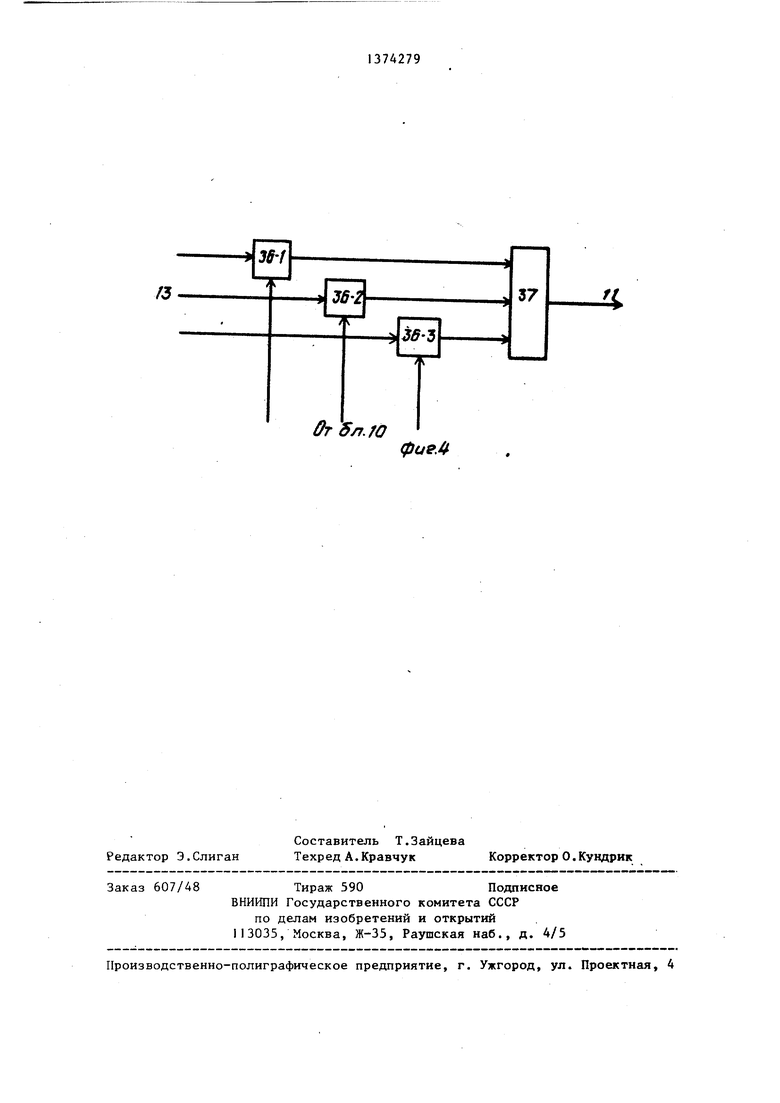

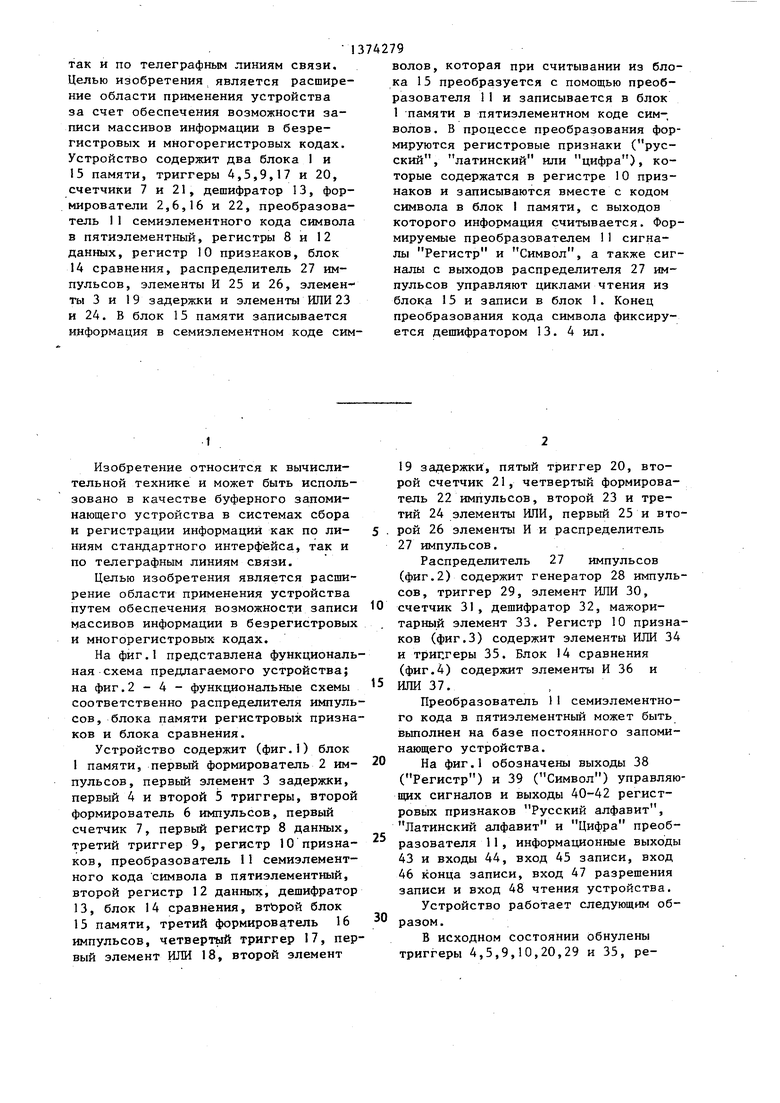

Распределитель 27 импульсов (фиг.2) содержит генератор 28 импульсов, триггер 29, элемент ИЛИ 30,

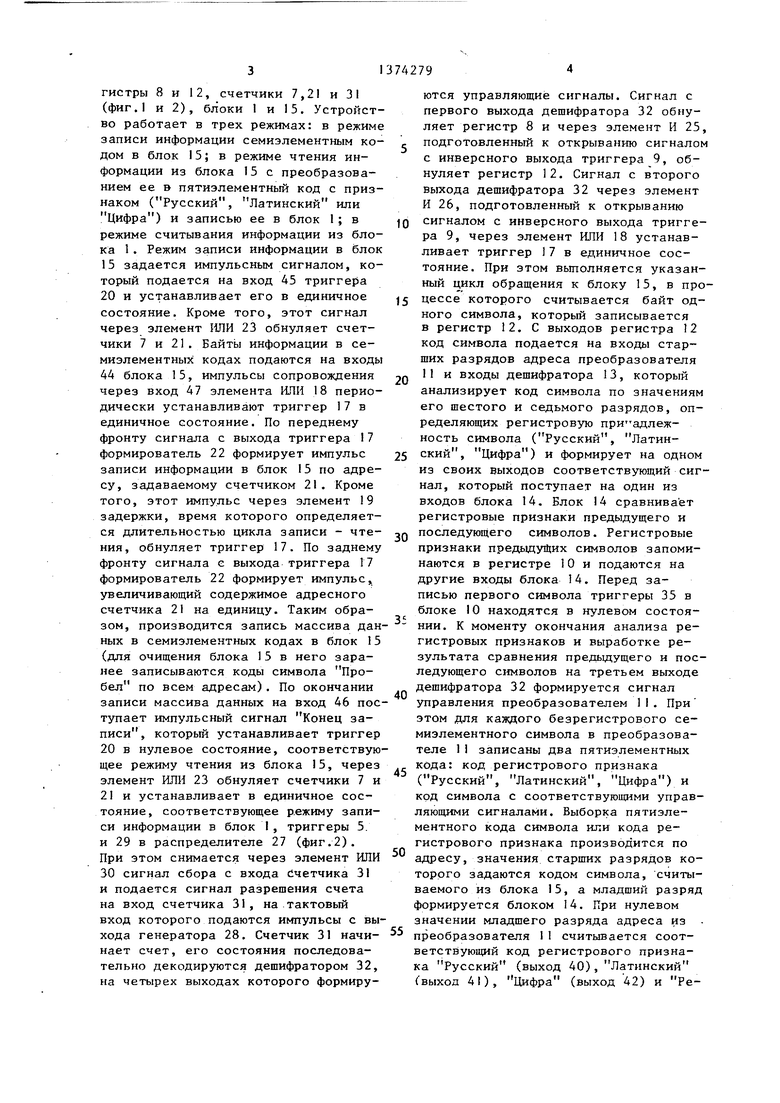

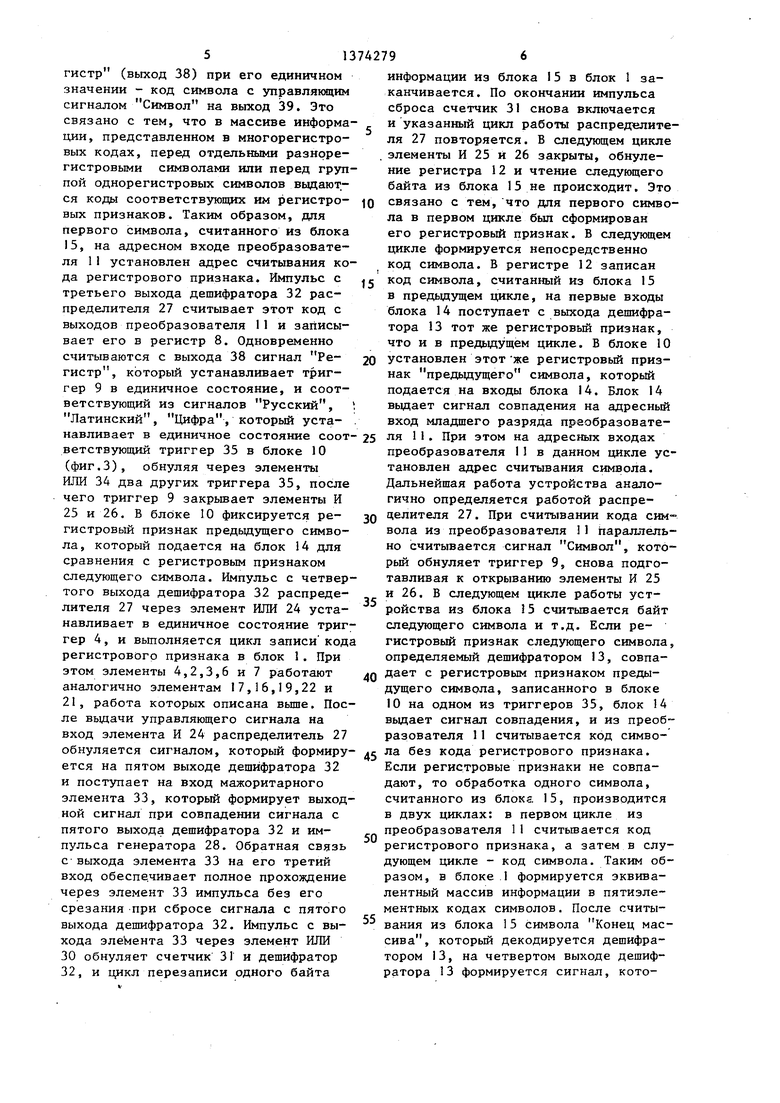

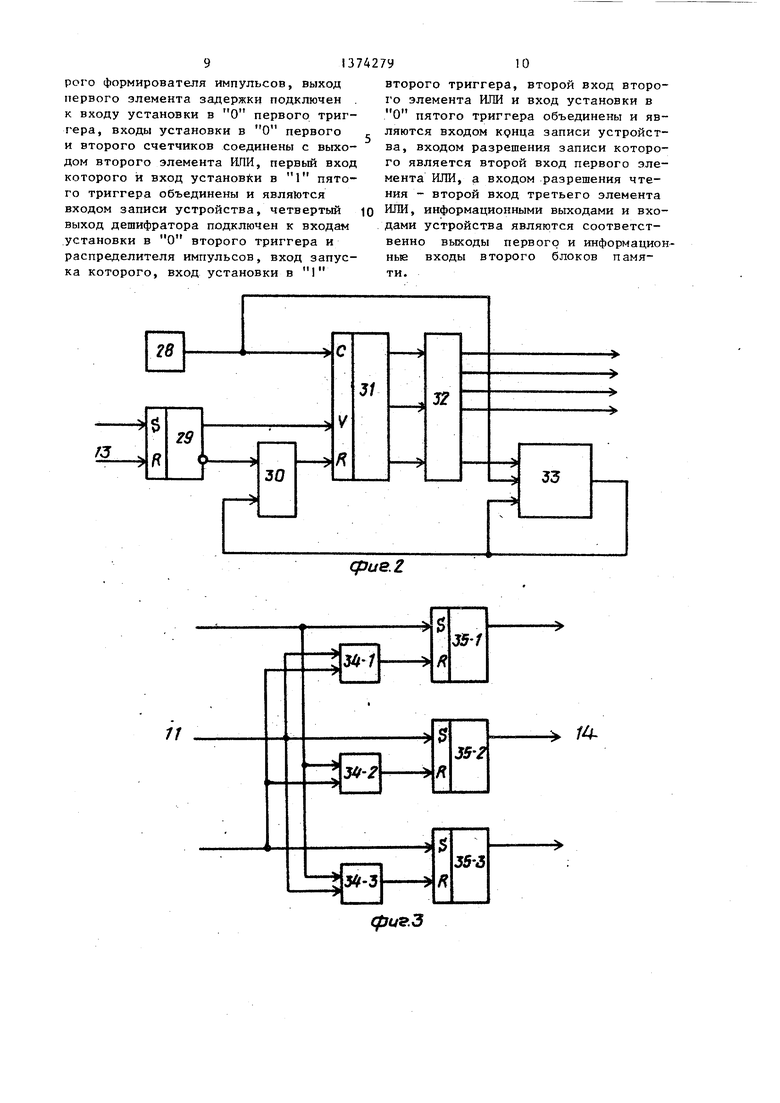

счетчик 31, дешифратор 32, мажоритарный элемент 33. Регистр 10 признаков (фиг.З) содержит элементы ИЛИ 34 и триггеры 35. Блок 14 сравнения (фиг.4) содержит элементы И 36 и

ИЛИ 37.

Преобразователь I семиэлементного кода в пятиэлементньш может быть выполнен на базе постоянного запоминающего устройства.

На фиг.1 обозначены выходы 38

(Регистр) и 39 (Символ) управляющих сигналов и выходы 40-42 регистровых признаков Русский алфавит, Латинский алфавит и Цифра преобразователя 11, информационные выходы 43 и входы 44, вход 45 записи, вход 46 конца записи, вход 47 разрешения записи и вход 48 чтения устройства. Устройство работает следующим образом.

В исходном состоянии обнулены триггеры 4,5,9,10,20,29 и 35, регистры 8 и 12, счетчики 7,21 и 31 (фиг.1 и 2), блоки 1 и 15. Устройство работает в трех режимах: в режиме записи информации семиэлементным кодом в блок 15; в режиме чтения информации из блока 15 с преобразованием ее в пятиэлементный код с признаком (Русский, Латинский или Цифра) и записью ее в блок 1; в режиме считывания информации из блока 1. Режим записи информации в блок 15 задается импульсным сигналом, который подается на вход 45 триггера 20 и устанавливает его в единичное состояние. Кроме того, этот сигнал через элемент ИЛИ 23 обнуляет счетчики 7 и 21. Байты информации в се- миэлементных кодах подаются на входы 44 блока 15, импульсы сопровождения через вход 47 элемента ИЛИ 18 периодически устанавливают триггер 17 в единичное состояние. По переднему фронту сигнала с выхода триггера I7 формирователь 22 формирует импульс записи информации в блок 15 по адресу, задаваемому счетчиком 21. Кроме того, этот импульс через элемент 19 задержки, время которого определяется длительностью цикла записи - чтения, обнуляет триггер 17. По заднему фронту сигнала с выхода триггера 17 формирователь 22 формирует импульс,, увеличивающий содержимое адресного счетчика 21 на единицу. Таким образом, производится запись массива данных в семиэлементных кодах в блок 15 (для очищения блока 15 в него заранее записываются коды символа Пробел по всем адресам). По окончании записи массива данных на вход 46 поступает импульсный сигнал Конец записи , которьй устанавливает триггер

20в нулевое состояние, соответствующее режиму чтения из блока 15, через элемент ИЛИ 23 обнуляет счетчики 7 и

21и устанавливает в единичное состояние, соответствующее режиму записи информации в блок 1, триггеры 5.

и 29 в распределителе 27 (фиг.2). При этом снимается через элемент ИЛИ 30 сигнал сбора с входа Счетчика 31 и подается сигнал разрешения счета на вход счетчика 31, на тактовый вход которого подаются импульсы с выхода генератора 28. Счетчик 31 начинает счет, его состояния последовательно декодируются дешифратором 32, на четырех выходах которого формиру0

5

0

5

0

;

0

5

0

5

ются управляющие сигналы. Сигнал с первого выхода дешифратора 32 обнуляет регистр 8 и через элемент И 25, подготовленный к открыванию сигналом с инверсного выхода триггера 9, обнуляет регистр 12. Сигнал с второго выхода дешифратора 32 через элемент И 26, подготовленный к открыванию сигналом с инверсного выхода триггера 9, через элемент ИЛИ 18 устанавливает триггер 17 в единичное состояние. При этом вьтолняется указанный цикл обращения к блоку 15, в процессе которого считывается байт одного символа, который записывается в регистр 12. С выходов регистра 12 код символа подается на входы старших разрядов адреса преобразователя 11 и входы дешифратора 13, который анализирует код символа по значениям его шестого и седьмого разрядов, определяющих регистровую при адлеж- ность символа (Русский, Латинский, Цифра) и формирует на одном из своих выходов соответствующий сигнал, который поступает на один из входов блока 14. Блок 14 сравнивает регистровые признаки предыдущего и последующего символов. Регистровые признаки предыдущих символов запоминаются в регистре 10 и подаются на другие входы блока 14. Перед записью первого символа триггеры 35 в блоке IО находятся в нулевом состоянии. К моменту окончания анализа регистровых признаков и выработке результата сравнения предьщущего и последующего символов на третьем выходе дешифратора 32 формируется сигнал управления преобразователем 1I. При этом для каждого безрегистрового се- миэлементного символа в преобразователе 11 записаны два пятиэлементных кода: код регистрового признака (Русский, Латинский, Цифра) и код символа с соответствующими управляющими сигналами. Выборка пятиэле- ментного кода символа или кода регистрового признака производится по адресу, значения старших разрядов которого задаются кодом символа, считываемого из блока 15, а младший разряд формируется блоком 14. При нулевом значении младшего разряда адреса из - преобразователя II считывается соответствующий код регистрового признака Русский (выход 40),Латинский ( выход 41), Цифра (выход 42) и Регистр (выход 38) при его единичном значении - код символа с управлякхдим сигналом Символ на выход 39. Это связано с тем, что в массиве информации, представленном в многорегистровых кодах, перед отдельными разнрре- гистровыми символами или перед группой однорегистровых символов выдаются коды соответствующих им регистровых признаков. Таким образом, для первого символа, считанного из блока 15, на адресном входе преобразователя 11 установлен адрес считывания кода регистрового признака. Импульс с третьего выхода дешифратора 32 распределителя 27 считывает этот код с выходов преобразователя 11 и записывает его в регистр 8. Одновременно считываются с выхода 38 сигнал Регистр, который устанавливает триггер 9 в единичное состояние, и соответствующий из сигналов Русский, Латинский, Цифра, который устанавливает в единичное состояние соот- 25 При этом на адресных входах

ветствующий триггер 35 в блоке 10 (фиг.З), обнуляя через элементы ИЛИ 34 два других триггера 35, после чего триггер 9 закрьшает элементы И 25 и 26. В блоке 10 фиксируется регистровый признак предыдущего символа, который подается на блок 14 для сравнения с регистровым признаком следующего символа. Импульс с четвертого выхода дешифратора 32 распределителя 27 через элемент ИЛИ 24 устанавливает в единичное состояние триггер 4, и вьтолняется цикл записи кода регистрового признака в блок 1. При этом элементы 4,2,3,6 и 7 работают аналогично элементам 17,16,19,22 и 21, работа которых описана выше. После выдачи управляющего сигнала на вход элемента И 24 распределитель 27

50

обнуляется сигналом, который формиру- АС ла без кода регистрового признака, ется на пятом выходе дешифратора 32 Если регистровые признаки не совпа- и поступает на вход мажоритарного элемента 33, который формирует выходной сигнал при совпадении сигнала с пятого выхода дешифратора 32 и импульса генератора 28. Обратная связь с выхода элемента 33 на его третий вход обеспечивает полное прохождение через элемент 33 импульса без его срезания при сбросе сигнала с пятого выхода дешифратора 32. Импульс с выхода элемента 33 через элемент ИЛИ 30 обнуляет счетчик ЗГ и дешифратор 32, и цикл перезаписи одного байта

дают, то обработка одного символа, считанного из блоке. 15, производится в двух циклах: в первом цикле из преобразователя 11 считьшается код регистрового признака, а затем в слу дующем цикле - код символа. Таким об разом, в блоке 1 формируется эквивалентный массив информации в пятиэле- ментных кодах символов. После считы- 5 вания из блока 15 символа Конец мас сива, который декодируется дешифратором 13, на четвертом выходе дешифратора 13 формируется сигнал, котоинформации из блока 15 в блок 1 заканчивается. По окончании импульса сброса счетчик 31 снова включается и указанный цикл работы распределителя 27 повторяется. В следующем цикле элементы И 25 И 26 закрыты, обнуление регистра 12 и чтение следующего байта из блока 15 не происходит. Это

связано с тем, что для первого символа в первом цикле был сформирован его регистровый признак. В следующем цикле формируется непосредственно код символа. В регистре 12 записан

код символа, считанный из блока 15 в предьщущем цикле, на первые входы блока 14 поступает с выхода дешифратора 13 тот же регистровый признак, что и в предьщущем цикле. Б блоке 10

установлен этот же регистровый признак предьщущего символа, который подается на входы блока 14. Блок 14 вьщает сигнал совпадения на адресный вход младшего разряда преобразовате0

5

0

преобразователя 11 в данном цикле установлен адрес считывания символа. Дальнейшая работа устройства аналогично определяется работой распределителя 27. При считывании кода символа из преобразователя 11 параллельно считывается сигнал Символ, кото- рьй обнуляет триггер 9, снова подготавливая к открыванию элементы И 25 и 26. В следующем цикле работы устройства из блока 15 считывается байт следующего символа и т.д. Если регистровый признак следующего символа, определяемый дешифратором 13, совпадает с регистровым признаком предыдущего символа, записанного в блоке 10 на одном из триггеров 35, блок 14 выдает сигнал совпадения, и из преобразователя 11 считывается код симво

ла без кода регистрового признака, Если регистровые признаки не совпа-

дают, то обработка одного символа, считанного из блоке. 15, производится в двух циклах: в первом цикле из преобразователя 11 считьшается код регистрового признака, а затем в слу- дующем цикле - код символа. Таким образом, в блоке 1 формируется эквивалентный массив информации в пятиэле- ментных кодах символов. После считы- вания из блока 15 символа Конец массива, который декодируется дешифратором 13, на четвертом выходе дешифратора 13 формируется сигнал, кото10

1374279

9 распределиего, и обнуляивая режим считьшания регистровых коя импульсы чтеэтом периодигер 4 и элеменоторых описана 1 коды регистолов выдаются

лагаемое устормированиесемиэлементных иэлементных ах, что позвос его выходов ва как по липо телеграфрасширяет об

15

20

по бл мо по му ма да вх да се эл вх бл ро тр бл .ре со пр ме ны вы че го да ус пе со И, кл но к ра И, ди до вы тр по чт го пе вы та мо да ро .фо вх вх па фо ре ды но ве вы вх

Формула изобретения 25

Буферное запоминающее устройство, содержащее первый и второй блоки памяти, с первого по пятый триггеры, .первый и второй счетчики, дешифратор первый и второй элементы И, первый формирователь импульсов, первый и второй элементы задержки, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения возможности записи массивов информации в безрегистровых и многорегистровых кодах в него введены преобразователь семи- элементного кода символа в пятиэле- ментный, регистр признаков, первый и второй регистры данных, блок сравнения, с второго по четвертый формирователи импульсов, распределитель импульсов и с первого по третий элементы ИЛИ, причем выход первого элемента ИЛИ соединен с входом установки в 1 четвертого триггера, прямой выход которого подключен к входам запуска третьего и четвертого формирователей импульсов, выход первого формирователя импульсов соединен с входом записи-чтения второго блока памяти и входом второго элемента задержки, выход которого подключен к входу установки в О четвертого триггера, выход четвертого формирователя импульсов соединен со счетным входом второго счетчика, выходы которого

5

0

0

5

0

5

5

0

5

подключены к адресным входам второго блока памяти, вход управления режимом записи-чтения и выходы которого подключень соответственно к инверсному выходу пятого триггера и к информационным входам второго регистра данных, выходы которого соединены с входами дешифратора и старшими разрядами адресных входов преобразователя семиэлементного кода символа в пяти- элементный, младший разряд адресных входов которого подключен к выходу блока сравнения, одни из входов которого соединены с выходами первого по третий дешифраторов, другие входы блока сравнения подключены к выходам .регистра признаков, входы которого соединены с выходами регистровых признаков преобразователя семиэлементного кода символа в пятиэлёмент- ный, выходы управляющих сигналов и выходы кода символа которого подключены соответственно к входам третьего триггера и к информационным входам первого регистра данных, вход установки в О которого соединен с первым выходом распределителя импульсов и первым входом первого элемента И, выход и второй вход которого подключены соответственно к установки в О второго регистра данных, к инверсному выходу третьего триггера и первому входу второго элемента И, выход и второй вход которого сое динены соответственно с первьт входом первого элемента ИЛИ и с вторым выходом распределителя импульсов, третий и четвертый выходы которого подключены соответственно к входу чтения преобразователя семиэлементного кода символа в пятиэлементный и к первому входу третьего элемента Ш1И, выход которого соединен с входом установки в 1 первого триггера, прямой выход которого подключен к входам запуска первого и второго формирователей импульсов,tвыход первого .формирователя импульсов соединен с входом первого элемента задержки и входом записи-чтения первого блока памяти информационных символов, информационные входы, вход управления режимом записиг-чтения и адресные входы которого подключены соответственно к выходам первого регистра, к инверсному выходу второго триггера и к, выходам первого счетчика, счетный вход которого соединен с выходом вто913

рого формирователя импульсов, выход первого элемента задержки подключен к входу установки в О первого триггера, входы установки в О первого и второго счетчиков соединены с выходом второго элемента И.ПИ, первый вход которого и вход установки в 1 пятого триггера объединены и являются входом записи устройства, четвертый выход дешифратора подключен к входам установки в О второго триггера и распределителя импульсов, вход запуска которого, вход установки в I

У

10

второго триггера, второй вход второго элемента ИЛИ и вход установки в О пятого триггера объединены и являются входом кднца записи устройства, входом разрешения записи которого является второй вход первого элемента ИЛИ, а входом разрешения чтения - второй вход третьего элемента ИЛИ, информационными выходами и входами устройства являются соответственно выходы первого и информационные входы второго блоков памяти.

q3ue.Z

фи.З

фие.

| ПРИБОР ДЛЯ РАЗМЕТКИ ФЛЯНЦЕВ ПАРООТВОДНЫХ ТРУБ В ДЫМОВОЙ КОРОБКЕ ПАРОВОЗОВ И Т. П. РАБОТ | 1921 |

|

SU1111A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-02-15—Публикация

1986-06-16—Подача